#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 64MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 30x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f43k22-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

| BOR Con | figuration | Status of           |                                                                                    |

|---------|------------|---------------------|------------------------------------------------------------------------------------|

| BOREN1  | BOREN0     | SBOREN<br>(RCON<6>) | BOR Operation                                                                      |

| 0       | 0          | Unavailable         | BOR disabled; must be enabled by reprogramming the Configuration bits.             |

| 0       | 1          | Available           | BOR enabled by software; operation controlled by SBOREN.                           |

| 1       | 0          | Unavailable         | BOR enabled by hardware in Run and Idle modes, disabled during Sleep mode.         |

| 1       | 1          | Unavailable         | BOR enabled by hardware; must be disabled by reprogramming the Configuration bits. |

#### TABLE 4-1:BOR CONFIGURATIONS

#### 4.6 Device Reset Timers

PIC18(L)F2X/4XK22 devices incorporate three separate on-chip timers that help regulate the Poweron Reset process. Their main function is to ensure that the device clock is stable before code is executed. These timers are:

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- PLL Lock Time-out

#### 4.6.1 POWER-UP TIMER (PWRT)

The Power-up Timer (PWRT) of PIC18(L)F2X/4XK22 devices is an 11-bit counter which uses the LFINTOSC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the LFINTOSC clock and will vary from chip-to-chip due to temperature and process variation.

The PWRT is enabled by clearing the PWRTEN Configuration bit.

#### 4.6.2 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or on exit from all power-managed modes that stop the external oscillator.

#### 4.6.3 PLL LOCK TIME-OUT

With the PLL enabled, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A separate timer is used to provide a fixed timeout that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

#### 4.6.4 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- 1. After the POR pulse has cleared, PWRT time-out is invoked (if enabled).

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and the status of the PWRT. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 all depict time-out sequences on power-up, with the Power-up Timer enabled and the device operating in HS Oscillator mode. Figures 4-3 through 4-6 also apply to devices operating in XT or LP modes. For devices in RC mode and with the PWRT disabled, on the other hand, there will be no time-out at all.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, all time-outs will expire, after which, bringing  $\overline{\text{MCLR}}$  high will allow program execution to begin immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC<sup>®</sup> MCU device operating in parallel.

| R/W-1           | R/W-1                                                                         | R/W-1                                        | R/W-1            | U-0              | R/W-1             | U-0            | R/W-1          |  |  |

|-----------------|-------------------------------------------------------------------------------|----------------------------------------------|------------------|------------------|-------------------|----------------|----------------|--|--|

| RBPU            | INTEDG0                                                                       | INTEDG1                                      | INTEDG2          | —                | TMR0IP            | _              | RBIP           |  |  |

| bit 7           | •<br>•                                                                        |                                              |                  |                  |                   |                | bit            |  |  |

|                 |                                                                               |                                              |                  |                  |                   |                |                |  |  |

| Legend:         |                                                                               |                                              |                  |                  |                   |                |                |  |  |

| R = Readable    |                                                                               | W = Writable                                 |                  | -                | mented bit, read  |                |                |  |  |

| -n = Value at F | POR                                                                           | '1' = Bit is set                             |                  | '0' = Bit is cle | eared             | x = Bit is unk | nown           |  |  |

|                 |                                                                               |                                              |                  |                  |                   |                |                |  |  |

| bit 7           |                                                                               | TB Pull-up Ena                               |                  |                  |                   |                |                |  |  |

|                 |                                                                               | FB pull-ups are                              |                  | that the nin i   | s an input and th | e correspondi  | na WPLIB bit i |  |  |

|                 | set.                                                                          |                                              |                  |                  | s an input and t  | ie concoponali |                |  |  |

| bit 6           | INTEDG0: E>                                                                   | kternal Interrup                             | t 0 Edge Sele    | ct bit           |                   |                |                |  |  |

|                 | 1 = Interrupt on rising edge                                                  |                                              |                  |                  |                   |                |                |  |  |

|                 | 0 = Interrupt on falling edge                                                 |                                              |                  |                  |                   |                |                |  |  |

| bit 5           |                                                                               | NTEDG1: External Interrupt 1 Edge Select bit |                  |                  |                   |                |                |  |  |

|                 |                                                                               | on rising edge<br>on falling edge            |                  |                  |                   |                |                |  |  |

| bit 4           | •                                                                             | 0 0                                          |                  | ot hit           |                   |                |                |  |  |

| DIL 4           | INTEDG2: External Interrupt 2 Edge Select bit<br>1 = Interrupt on rising edge |                                              |                  |                  |                   |                |                |  |  |

|                 | 0 = Interrupt on falling edge                                                 |                                              |                  |                  |                   |                |                |  |  |

| bit 3           | Unimplemen                                                                    | ted: Read as '                               | 0'               |                  |                   |                |                |  |  |

| bit 2           | TMROIP: TMI                                                                   | R0 Overflow In                               | terrupt Priority | / bit            |                   |                |                |  |  |

|                 | 1 = High priority                                                             |                                              |                  |                  |                   |                |                |  |  |

|                 | 0 = Low prior                                                                 | rity                                         |                  |                  |                   |                |                |  |  |

| bit 1           | Unimplemen                                                                    | ted: Read as '                               | 0'               |                  |                   |                |                |  |  |

| bit 0           | RBIP: RB Po                                                                   | rt Change Inte                               | rrupt Priority b | it               |                   |                |                |  |  |

|                 | 1 = High prio                                                                 | 2                                            |                  |                  |                   |                |                |  |  |

|                 | 0 = Low prior                                                                 | P1+1/                                        |                  |                  |                   |                |                |  |  |

#### REGISTER 9-2: INTCON2: INTERRUPT CONTROL 2 REGISTER

| Note: | Interrupt flag bits are set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs, regardless of the state of  |

|       | its corresponding enable bit or the global    |

|       | enable bit. User software should ensure       |

|       | the appropriate interrupt flag bits are clear |

|       | prior to enabling an interrupt. This feature  |

|       | allows for software polling.                  |

| U-0          | R/W-0                             | R-0                                                         | R-0              | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |

|--------------|-----------------------------------|-------------------------------------------------------------|------------------|------------------|------------------|-----------------|--------|--|

| —            | ADIF                              | RC1IF                                                       | TX1IF            | SSP1IF           | CCP1IF           | TMR2IF          | TMR1IF |  |

| bit 7        |                                   |                                                             |                  |                  |                  |                 | bit (  |  |

| 1            |                                   |                                                             |                  |                  |                  |                 |        |  |

| Legend:      | 1- 1-14                           |                                                             | L.14             |                  |                  | 1 (0)           |        |  |

| R = Readab   |                                   | W = Writable                                                |                  | -                | mented bit, read |                 |        |  |

| -n = Value a | IT POR                            | '1' = Bit is se                                             | t                | '0' = Bit is cle | ared             | x = Bit is unkr | lown   |  |

| bit 7        | Unimpleme                         | nted: Read as                                               | ʻ0'.             |                  |                  |                 |        |  |

| bit 6        | ADIF: A/D C                       | Converter Interre                                           | upt Flag bit     |                  |                  |                 |        |  |

|              |                                   | conversion con                                              |                  |                  |                  |                 |        |  |

|              |                                   | ) conversion is                                             | -                |                  | n started        |                 |        |  |

| bit 5        |                                   | SART1 Receive                                               |                  |                  |                  |                 |        |  |

|              |                                   | SART1 receive<br>SART1 receive                              |                  |                  | red when RCR     | EG1 is read)    |        |  |

| bit 4        |                                   | ART1 Transmit                                               | -                | -                |                  |                 |        |  |

|              |                                   |                                                             |                  |                  | cleared when T   | XREG1 is writte | en)    |  |

|              |                                   | SART1 transmi                                               |                  |                  |                  |                 |        |  |

| bit 3        |                                   | SSP1IF: Master Synchronous Serial Port 1 Interrupt Flag bit |                  |                  |                  |                 |        |  |

|              |                                   | nsmission/receptor to transmit/receptor                     | •                | ete (must be cle | eared by softwa  | re)             |        |  |

| bit 2        | CCP1IF: CC                        | P1 Interrupt Fl                                             | ag bit           |                  |                  |                 |        |  |

|              |                                   | <u>de:</u><br>register capture<br>R register captu          |                  | ist be cleared b | oy software)     |                 |        |  |

|              | Compare me                        |                                                             |                  |                  |                  |                 |        |  |

|              |                                   |                                                             |                  |                  | cleared by softw | are)            |        |  |

|              | <u>PWM mode</u>                   | R register comp                                             | are match occ    | unea             |                  |                 |        |  |

|              | Unused in th                      |                                                             |                  |                  |                  |                 |        |  |

| bit 1        | TMR2IF: TM                        | IR2 to PR2 Mat                                              | tch Interrupt Fl | ag bit           |                  |                 |        |  |

|              |                                   | o PR2 match o<br>R2 to PR2 matc                             |                  | be cleared by s  | software)        |                 |        |  |

| bit 0        | TMR1IF: TM                        | IR1 Overflow Ir                                             | terrupt Flag b   | it               |                  |                 |        |  |

|              |                                   | egister overflov<br>egister did not (                       |                  | leared by softw  | vare)            |                 |        |  |

|              |                                   |                                                             |                  |                  |                  |                 |        |  |

| Note 1:      | Interrupt flag I                  | oits are set                                                | when an          |                  |                  |                 |        |  |

|              | interrupt condition               |                                                             |                  |                  |                  |                 |        |  |

|              | the state of its of the Global Ir |                                                             |                  |                  |                  |                 |        |  |

|              | GIEH of the INT                   |                                                             | bit, Gi∟/        |                  |                  |                 |        |  |

|              |                                   | 0                                                           |                  |                  |                  |                 |        |  |

#### REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

Note: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

| REGISTER      |                                        |                                                                                                                                 |                 |                  |                  | <b>D</b> # • • • •           | <b>D</b> 4 + 1 - 2 |  |  |

|---------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|------------------------------|--------------------|--|--|

| R/W-0         | R/W-0                                  | R/W-0                                                                                                                           | R/W-0           | R/W-0            | R/W-0            | R/W-0                        | R/W-0              |  |  |

| SSP2IF        | BCL2IF                                 | RC2IF                                                                                                                           | TX2IF           | CTMUIF           | TMR5GIF          | TMR3GIF                      | TMR1GIF            |  |  |

| bit 7         |                                        |                                                                                                                                 |                 |                  |                  |                              | bit 0              |  |  |

| Legend:       |                                        |                                                                                                                                 |                 |                  |                  |                              |                    |  |  |

| R = Readabl   | e bit                                  | W = Writable                                                                                                                    | bit             | U = Unimplei     | mented bit, read | d as '0'                     |                    |  |  |

| -n = Value at | POR                                    | '1' = Bit is set                                                                                                                |                 | '0' = Bit is cle | eared            | x = Bit is unkr              | nown               |  |  |

| bit 7         | SSP2IF: Svn                            | chronous Seria                                                                                                                  | l Port Interrup | ot Flag bit      |                  |                              |                    |  |  |

|               | 1 = The trans                          |                                                                                                                                 | tion is comple  | •                | eared in softwa  | re)                          |                    |  |  |

| bit 6         | BCL2IF: MSS                            | SP2 Bus Collis                                                                                                                  | ion Interrupt F | lag bit          |                  |                              |                    |  |  |

|               | (must be                               | cleared in soft                                                                                                                 | ware)           | e SSP2 modu      | le configured ir | n I <sup>2</sup> C master wa | as transmitting    |  |  |

|               |                                        | collision occurre                                                                                                               |                 |                  |                  |                              |                    |  |  |

| bit 5         |                                        | <b>RC2IF:</b> EUSART2 Receive Interrupt Flag bit<br>1 = The EUSART2 receive buffer, RCREG2, is full (cleared by reading RCREG2) |                 |                  |                  |                              |                    |  |  |

|               |                                        | SART2 receive                                                                                                                   |                 |                  | red by reading   | RGREGZ)                      |                    |  |  |

| bit 4         |                                        | <b>X2IF:</b> EUSART2 Transmit Interrupt Flag bit                                                                                |                 |                  |                  |                              |                    |  |  |

|               |                                        | SART2 transmit<br>SART2 transmit                                                                                                |                 | G2, is empty (   | cleared by writi | ng TXREG2)                   |                    |  |  |

| bit 3         | CTMUIF: CT                             | MU Interrupt F                                                                                                                  | ag bit          |                  |                  |                              |                    |  |  |

|               |                                        | terrupt occurre<br>U interrupt occ                                                                                              |                 | eared in softwa  | are)             |                              |                    |  |  |

| bit 2         | TMR5GIF: TMR5 Gate Interrupt Flag bits |                                                                                                                                 |                 |                  |                  |                              |                    |  |  |

|               | 0                                      | e interrupt occ<br>gate occurred                                                                                                | urred (must be  | e cleared in sof | ftware)          |                              |                    |  |  |

| bit 1         | TMR3GIF: T                             | TMR3GIF: TMR3 Gate Interrupt Flag bits                                                                                          |                 |                  |                  |                              |                    |  |  |

|               |                                        | e interrupt occ<br>gate occurred                                                                                                | urred (must be  | e cleared in sof | itware)          |                              |                    |  |  |

| bit 0         | TMR1GIF: T                             | MR1 Gate Inter                                                                                                                  | rupt Flag bits  |                  |                  |                              |                    |  |  |

|               | 1 = TMR gat<br>0 = No TMR              |                                                                                                                                 | urred (must be  | e cleared in sof | ftware)          |                              |                    |  |  |

#### REGISTER 9-6: PIR3: PERIPHERAL INTERRUPT (FLAG) REGISTER 3

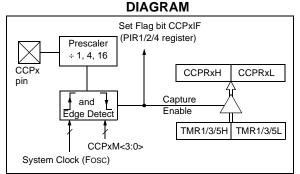

#### 14.1 Capture Mode

The Capture mode function described in this section is identical for all CCP and ECCP modules available on this device family.

Capture mode makes use of the 16-bit Timer resources, Timer1, Timer3 and Timer5. The timer resources for each CCP capture function are independent and are selected using the CCPTMRS0 and CCPTMRS1 registers. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMRxH:TMRxL register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the corresponding Interrupt Request Flag bit CCPxIF of the PIR1, PIR2 or PIR4 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH:CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

#### TABLE 14-2: CCP PIN MULTIPLEXING

Figure 14-1 shows a simplified diagram of the Capture operation.

FIGURE 14-1:

## CAPTURE MODE OPERATION BLOCK

#### 14.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Some CCPx outputs are multiplexed on a couple of pins. Table 14-2 shows the CCP output pin multiplexing. Selection of the output pin is determined by the CCPxMX bits in Configuration register 3H (CONFIG3H). Refer to Register 24-4 for more details.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

| CCP OUTPUT | CONFIG 3H Control Bit | Bit Value | PIC18(L)F2XK22 I/O pin | PIC18(L)F4XK22 I/O pin |

|------------|-----------------------|-----------|------------------------|------------------------|

| CCP2       | CCP2MX                | 0         | RB3                    | RB3                    |

| CCP2       | CCPZIVIA              | 1(*)      | RC1                    | RC1                    |

| CCP3       | ССРЗМХ                | 0(*)      | RC6                    | RE0                    |

| CCP3       | CCP3IVIX              | 1         | RB5                    | RB5                    |

Legend: \* = Default

#### 14.1.2 TIMER1 MODE RESOURCE

The 16-bit Timer resource must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 12.0 "Timer1/3/5 Module with Gate Control" for more information on configuring the 16-bit Timers.

#### 14.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIE1, PIE2 or PIE4 register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIR1, PIR2 or PIR4 register following any change in Operating mode.

Note: Clocking the 16-bit Timer resource from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, the Timer resource must be clocked from the instruction clock (Fosc/4) or from an external clock source.

| R/W-0           | R/W-0                       | U-0                                                               | R/W-0          | R/W-0          | U-0              | R/W-0            | R/W-0        |  |

|-----------------|-----------------------------|-------------------------------------------------------------------|----------------|----------------|------------------|------------------|--------------|--|

| C3TSEL<1:0>     |                             | —                                                                 | C2TS           | EL<1:0>        | —                | C1TSE            | L<1:0>       |  |

| bit 7           |                             |                                                                   |                |                |                  |                  | bit C        |  |

|                 |                             |                                                                   |                |                |                  |                  |              |  |

| Legend:         |                             |                                                                   |                |                |                  |                  |              |  |

| R = Readab      | le bit                      | W = Writable                                                      | bit            | U = Unimpler   | nented bit, read | l as '0'         |              |  |

| u = Bit is un   | changed                     | x = Bit is unkr                                                   | iown           | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |

| '1' = Bit is se | et                          | '0' = Bit is clea                                                 | ared           |                |                  |                  |              |  |

|                 |                             |                                                                   |                |                |                  |                  |              |  |

| bit 7-6         | C3TSEL<1:0                  | >: CCP3 Timer                                                     | Selection bits | 6              |                  |                  |              |  |

|                 | 00 = CCP3 -                 | Capture/Comp                                                      | are modes us   | e Timer1, PWN  | 1 modes use Tir  | mer2             |              |  |

|                 |                             | = CCP3 – Capture/Compare modes use Timer3, PWM modes use Timer4   |                |                |                  |                  |              |  |

|                 |                             | P3 – Capture/Compare modes use Timer5, PWM modes use Timer6       |                |                |                  |                  |              |  |

|                 | 11 = Reserve                | ed                                                                |                |                |                  |                  |              |  |

| bit 5           | Unused                      |                                                                   |                |                |                  |                  |              |  |

| bit 4-3         | C2TSEL<1:0                  | >: CCP2 Timer                                                     | Selection bits | 6              |                  |                  |              |  |

|                 |                             | = CCP2 – Capture/Compare modes use Timer1, PWM modes use Timer2   |                |                |                  |                  |              |  |

|                 |                             | 1 = CCP2 – Capture/Compare modes use Timer3, PWM modes use Timer4 |                |                |                  |                  |              |  |

|                 |                             | 0 = CCP2 - Capture/Compare modes use Timer5, PWM modes use Timer6 |                |                |                  |                  |              |  |

|                 | 11 = Reserve                | ed                                                                |                |                |                  |                  |              |  |

| bit 2           | Unused                      |                                                                   |                |                |                  |                  |              |  |

| bit 1-0         | C1TSEL<1:0                  | >: CCP1 Timer                                                     | Selection bits | 6              |                  |                  |              |  |

|                 |                             |                                                                   |                | se Timer1, PWM |                  |                  |              |  |

|                 |                             |                                                                   |                | se Timer3, PWN |                  |                  |              |  |

|                 | 10 = CCP1 -<br>11 = Reserve |                                                                   | are modes us   | se Timer5, PWM | 1 modes use Tir  | mer6             |              |  |

|                 |                             |                                                                   |                |                |                  |                  |              |  |

#### REGISTER 14-3: CCPTMRS0: PWM TIMER SELECTION CONTROL REGISTER 0

#### REGISTER 14-4: CCPTMRS1: PWM TIMER SELECTION CONTROL REGISTER 1

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0  |

|-------|-----|-----|-----|-------|--------|-------|--------|

| —     | —   | —   | —   | C5TSE | L<1:0> | C4TSE | L<1:0> |

| bit 7 |     |     |     |       |        |       | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| נ' |

|----|

| )  |

| bit 3-2 | <b>C5TSEL&lt;1:0&gt;:</b> CCP5 Timer Selection bits<br>00 = CCP5 - Capture/Compare modes use Timer1, PWM modes use Timer2<br>01 = CCP5 - Capture/Compare modes use Timer3, PWM modes use Timer4<br>10 = CCP5 - Capture/Compare modes use Timer5, PWM modes use Timer6<br>11 = Reserved |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1-0 | <b>C4TSEL&lt;1:0&gt;:</b> CCP4 Timer Selection bits<br>00 = CCP4 - Capture/Compare modes use Timer1, PWM modes use Timer2<br>01 = CCP4 - Capture/Compare modes use Timer3, PWM modes use Timer4<br>10 = CCP4 - Capture/Compare modes use Timer5, PWM modes use Timer6<br>11 = Reserved |

| R/W-0                                                | R/W-0                                                                                                                            | R/W-0             | R/W-0                                                     | R/W-0              | R/W-0            | R/W-0         | R/W-0        |  |  |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------|--------------------|------------------|---------------|--------------|--|--|

| PxRSEN                                               |                                                                                                                                  |                   |                                                           | PxDC<6:0>          |                  |               |              |  |  |

| bit 7                                                |                                                                                                                                  |                   |                                                           |                    |                  |               | bit 0        |  |  |

|                                                      |                                                                                                                                  |                   |                                                           |                    |                  |               |              |  |  |

| Legend:                                              |                                                                                                                                  |                   |                                                           |                    |                  |               |              |  |  |

| R = Readable bit $W = Writable bit$                  |                                                                                                                                  |                   | bit                                                       | U = Unimpler       | nented bit, read | d as '0'      |              |  |  |

| u = Bit is unchanged x = E                           |                                                                                                                                  | x = Bit is unkr   | x = Bit is unknown -n/n = Value at POR and BOR/Value at a |                    |                  |               | other Resets |  |  |

| '1' = Bit is set                                     | t                                                                                                                                | '0' = Bit is clea | '0' = Bit is cleared                                      |                    |                  |               |              |  |  |

|                                                      |                                                                                                                                  |                   |                                                           |                    |                  |               |              |  |  |

| bit 7                                                | PxRSEN: P                                                                                                                        | WM Restart Ena    | able bit                                                  |                    |                  |               |              |  |  |

|                                                      | 1 = Upon auto-shutdown, the CCPxASE bit clears automatically once the shutdown event goes away<br>the PWM restarts automatically |                   |                                                           |                    |                  |               |              |  |  |

|                                                      | 0 = Upon a                                                                                                                       | uto-shutdown, C   | CPxASE mus                                                | st be cleared in s | software to rest | tart the PWM  |              |  |  |

| bit 6-0 <b>PxDC&lt;6:0&gt;:</b> PWM Delay Count bits |                                                                                                                                  |                   |                                                           |                    |                  |               |              |  |  |

|                                                      | PxDCx = N                                                                                                                        | umber of Fosc/    | 4 (4 * Tosc)                                              | cycles between     | the scheduled    | d time when a | a PWM signal |  |  |

#### REGISTER 14-6: PWMxCON: ENHANCED PWM CONTROL REGISTER

#### REGISTER 14-7: PSTRxCON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-1 |

|-------|-----|-----|----------|-------|-------|-------|-------|

| —     | —   | —   | STRxSYNC | STRxD | STRxC | STRxB | STRxA |

| bit 7 |     |     |          |       |       |       | bit 0 |

should transition active and the actual time it transitions active

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                         |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <b>STRxSYNC:</b> Steering Sync bit<br>1 = Output steering update occurs on next PWM period<br>0 = Output steering update occurs at the beginning of the instruction cycle boundary |

| bit 3   | <b>STRxD:</b> Steering Enable bit D<br>1 = PxD pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxD pin is assigned to port pin                               |

| bit 2   | <b>STRxC:</b> Steering Enable bit C<br>1 = PxC pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxC pin is assigned to port pin                               |

| bit 1   | <b>STRxB:</b> Steering Enable bit B<br>1 = PxB pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxB pin is assigned to port pin                               |

| bit 0   | <b>STRxA:</b> Steering Enable bit A<br>1 = PxA pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxA pin is assigned to port pin                               |

| Note 1. | The DWM Steering mode is evoluble only when the CCDyCON register hits CCDyM (20) 11.0                                                                                              |

**Note 1:** The PWM Steering mode is available only when the CCPxCON register bits CCPxM<3:2> = 11 and PxM<1:0> = 00.

| R/W-0                                                                                        | R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0        |  |  |

|----------------------------------------------------------------------------------------------|-------|----------------------|-------|-------|-------|-------|--------------|--|--|

| ADD<7:0>                                                                                     |       |                      |       |       |       |       |              |  |  |

| bit 7                                                                                        |       |                      |       |       |       |       | bit 0        |  |  |

|                                                                                              |       |                      |       |       |       |       |              |  |  |

| Legend:                                                                                      |       |                      |       |       |       |       |              |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                         |       |                      |       |       |       |       |              |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Reset |       |                      |       |       |       |       | other Resets |  |  |

| '1' = Bit is set                                                                             |       | '0' = Bit is cleared | ł     |       |       |       |              |  |  |

#### REGISTER 15-7: SSPxADD: MSSPx ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

#### Master mode:

bit 7-0 ADD<7:0>: Baud Rate Clock Divider bits SCLx pin clock period = ((ADD<7:0> + 1) \*4)/Fosc

#### <u>10-Bit Slave mode — Most Significant Address byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### <u>10-Bit Slave mode — Least Significant Address byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

| U-0           | U-0                    | R/P-1            | R/P-1             | R/P-1             | R/P-1               | R/P-1           | R/P-1  |

|---------------|------------------------|------------------|-------------------|-------------------|---------------------|-----------------|--------|

| _             | —                      |                  | WDTI              | PS<3:0>           |                     | WDTE            | N<1:0> |

| bit 7         |                        |                  |                   |                   |                     |                 | bit    |

|               |                        |                  |                   |                   |                     |                 |        |

| Legend:       |                        |                  |                   |                   |                     |                 |        |

| R = Readable  | e bit                  | P = Programma    | ble bit           | U = Unimpleme     | nted bit, read as ' | 0'              |        |

| -n = Value wh | nen device is unprogra | ammed            |                   | x = Bit is unknow | wn                  |                 |        |

|               |                        |                  |                   |                   |                     |                 |        |

| bit 7-6       | Unimplemented          | I: Read as '0'   |                   |                   |                     |                 |        |

| bit 5-2       | WDTPS<3:0>: V          | Vatchdog Timer   | Postscale Selec   | t bits            |                     |                 |        |

|               | 1111 = 1:32,768        | •                |                   |                   |                     |                 |        |

|               | 1110 = 1:16,384        | Ļ                |                   |                   |                     |                 |        |

|               | 1101 = 1:8,192         |                  |                   |                   |                     |                 |        |

|               | 1100 = 1:4,096         |                  |                   |                   |                     |                 |        |

|               | 1011 = 1:2,048         |                  |                   |                   |                     |                 |        |

|               | 1010 = 1:1,024         |                  |                   |                   |                     |                 |        |

|               | 1001 = <b>1:512</b>    |                  |                   |                   |                     |                 |        |

|               | 1000 <b>= 1:256</b>    |                  |                   |                   |                     |                 |        |

|               | 0111 = <b>1:128</b>    |                  |                   |                   |                     |                 |        |

|               | 0110 = 1:64            |                  |                   |                   |                     |                 |        |

|               | 0101 = 1:32            |                  |                   |                   |                     |                 |        |

|               | 0100 = 1:16            |                  |                   |                   |                     |                 |        |

|               | 0011 = 1:8             |                  |                   |                   |                     |                 |        |

|               | 0010 = 1:4             |                  |                   |                   |                     |                 |        |

|               | 0001 = 1:2             |                  |                   |                   |                     |                 |        |

|               | 0000 = 1:1             |                  |                   |                   |                     |                 |        |

| bit 1-0       | WDTEN<1:0>: \          | Vatchdog Timer   | Enable bits       |                   |                     |                 |        |

|               | 11 = WDT enabl         | led in hardware; | SWDTEN bit dis    | abled             |                     |                 |        |

|               | 10 = WDT control       |                  |                   |                   |                     |                 |        |

|               | 01 = WDT enab          | led when device  | is active, disabl | ed when device is | in Sleep; SWDTE     | EN bit disabled |        |

|               |                        | led in hardware; |                   |                   | 1,7 -               |                 |        |

### REGISTER 24-3: CONFIG2H: CONFIGURATION REGISTER 2 HIGH

# PIC18(L)F2X/4XK22

| XORWF                   | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                      |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|--|--|--|--|--|

| Syntax:                 | XORWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | f {,d {,a}}            |                      |  |  |  |  |  |

| Operands:               | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | d ∈ [0,1]              |                      |  |  |  |  |  |

| Operation:              | (W) .XOR. (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (f) $\rightarrow$ dest |                      |  |  |  |  |  |

| Status Affected:        | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |                      |  |  |  |  |  |

| Encoding:               | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10da fff               | f ffff               |  |  |  |  |  |

| Description:            | Exclusive OR the contents of W with<br>register 'f'. If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored back<br>in the register 'f' (default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                        |                      |  |  |  |  |  |

| Words:                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        |                      |  |  |  |  |  |

| Cycles:                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        |                      |  |  |  |  |  |

| Q Cycle Activity:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |                      |  |  |  |  |  |

| Q1                      | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q3                     | Q4                   |  |  |  |  |  |

| Decode                  | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Process<br>Data        | Write to destination |  |  |  |  |  |

| Example:                | XORWF I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | REG, 1, 0              |                      |  |  |  |  |  |

| Before Instruct         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |                      |  |  |  |  |  |

| REG<br>W                | = AFh<br>= B5h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                        |                      |  |  |  |  |  |

| VV<br>After Instruction |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |                      |  |  |  |  |  |

| REG                     | = 1Ah                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                      |  |  |  |  |  |

B5h

=

$\ensuremath{\textcircled{}^{\odot}}$  2010-2016 Microchip Technology Inc.

W

# 25.2.5 SPECIAL CONSIDERATIONS WITH MICROCHIP MPLAB<sup>®</sup> IDE TOOLS

The latest versions of Microchip's software tools have been designed to fully support the extended instruction set of the PIC18(L)F2X/4XK22 family of devices. This includes the MPLAB C18 C compiler, MPASM assembly language and MPLAB Integrated Development Environment (IDE).

When selecting a target device for software development, MPLAB IDE will automatically set default Configuration bits for that device. The default setting for the XINST Configuration bit is '0', disabling the extended instruction set and Indexed Literal Offset Addressing mode. For proper execution of applications developed to take advantage of the extended instruction set, XINST must be set during programming.

To develop software for the extended instruction set, the user must enable support for the instructions and the Indexed Addressing mode in their language tool(s). Depending on the environment being used, this may be done in several ways:

- A menu option, or dialog box within the environment, that allows the user to configure the language tool and its settings for the project

- A command line option

- A directive in the source code

These options vary between different compilers, assemblers and development environments. Users are encouraged to review the documentation accompanying their development systems for the appropriate information.

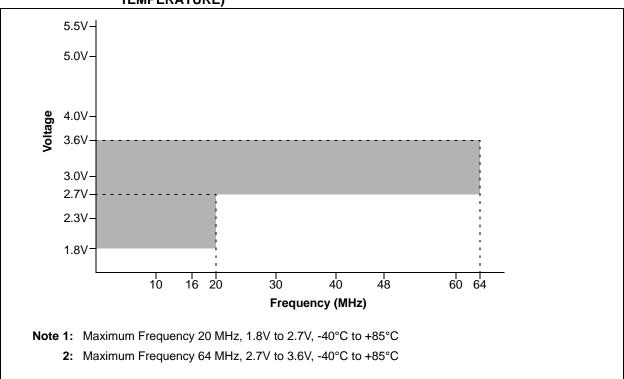

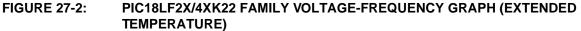

# FIGURE 27-1: PIC18LF2X/4XK22 FAMILY VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL TEMPERATURE)

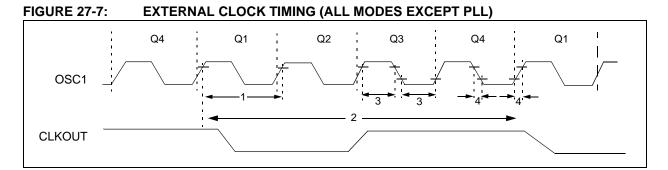

#### 27.11.3 TIMING DIAGRAMS AND SPECIFICATIONS

#### TABLE 27-7: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic                             | Min         | Max       | Units      | Conditions                                                                                                               |

|---------------|--------|--------------------------------------------|-------------|-----------|------------|--------------------------------------------------------------------------------------------------------------------------|

| 1A            | Fosc   | External CLKIN<br>Frequency <sup>(1)</sup> | DC<br>DC    | 0.5<br>16 | MHz<br>MHz | EC, ECIO Oscillator mode (low power)<br>EC, ECIO Oscillator mode (medium power)<br>EC, ECIO Oscillator mode (high power) |

|               |        |                                            | DC          | 64        | MHz        |                                                                                                                          |

|               |        | Oscillator Frequency <sup>(1)</sup>        | DC          | 4         | MHz        | RC Oscillator mode                                                                                                       |

|               |        |                                            | 5           | 200       | kHz        | LP Oscillator mode                                                                                                       |

|               |        |                                            | 0.1         | 4         | MHz        | XT Oscillator mode                                                                                                       |

|               |        |                                            | 4           | 4         | MHz        | HS Oscillator mode, VDD < 2.7V                                                                                           |

|               |        |                                            | 4           | 16        | MHz        | HS Oscillator mode, $VDD \ge 2.7V$ ,<br>Medium-Power mode (HSMP)                                                         |

|               |        |                                            | 4           | 20        | MHz        | HS Oscillator mode, $VDD \ge 2.7V$ ,<br>High-Power mode (HSHP)                                                           |

| 1             | Tosc   | External CLKIN Period <sup>(1)</sup>       | 2.0<br>62.5 |           | μs<br>ns   | EC, ECIO Oscillator mode (low power)<br>EC, ECIO Oscillator mode (medium power)<br>EC, ECIO Oscillator mode (high power) |

|               |        |                                            | 15.6        | —         | ns         | ,                                                                                                                        |

|               |        | Oscillator Period <sup>(1)</sup>           | 250         | _         | ns         | RC Oscillator mode                                                                                                       |

|               |        |                                            | 5           | 200       | μs         | LP Oscillator mode                                                                                                       |

|               |        |                                            | 0.25<br>250 | 10<br>250 | μs<br>ns   | XT Oscillator mode<br>HS Oscillator mode, VDD < 2.7V                                                                     |

|               |        |                                            | 62.5        | 250       | ns         | HS Oscillator mode, $VDD \ge 2.7V$ ,<br>Medium-Power mode (HSMP)                                                         |

|               |        |                                            | 50          | 250       | ns         | HS Oscillator mode, $VDD \ge 2.7V$ ,<br>High-Power mode (HSHP)                                                           |

| 2             | Тсү    | Instruction Cycle Time <sup>(1)</sup>      | 62.5        | _         | ns         | Tcy = 4/Fosc                                                                                                             |

| 3             | TosL,  | External Clock in (OSC1)                   | 2.5         | —         | μs         | LP Oscillator mode                                                                                                       |

|               | TosH   | High or Low Time                           | 30          | —         | ns         | XT Oscillator mode                                                                                                       |

|               |        |                                            | 10          | _         | ns         | HS Oscillator mode                                                                                                       |

| 4             | TosR,  | External Clock in (OSC1)                   | _           | 50        | ns         | LP Oscillator mode                                                                                                       |

|               | TosF   | Rise or Fall Time                          | —           | 20        | ns         | XT Oscillator mode                                                                                                       |

|               |        |                                            | —           | 7.5       | ns         | HS Oscillator mode                                                                                                       |

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period for all configurations except PLL. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

#### TABLE 27-22: A/D CONVERSION REQUIREMENTS PIC18(L)F2X/4XK22

| Standard Operating Conditions (unless otherwise stated)   Operating temperature Tested at +25°C |        |                                                                     |     |     |          |       |                           |  |  |

|-------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------|-----|-----|----------|-------|---------------------------|--|--|

| Param.<br>No.                                                                                   | Symbol | Characteristic                                                      | Min | Тур | Мах      | Units | Conditions                |  |  |

| 130                                                                                             | TAD    | A/D Clock Period                                                    | 1   | _   | 25       | μS    | -40°C to +85°C            |  |  |

|                                                                                                 |        |                                                                     | 1   | _   | 4        | μS    | +85°C to +125°C           |  |  |