Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 30x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f43k22t-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 2: | PIC18(L)F2XK22 PIN SUMMARY |

|----------|----------------------------|

|----------|----------------------------|

| IAD                       |              |     |        | FZANZZ     | 1 114 50 |          |                 |                                                  |         |              |                                               |            |         |              |

|---------------------------|--------------|-----|--------|------------|----------|----------|-----------------|--------------------------------------------------|---------|--------------|-----------------------------------------------|------------|---------|--------------|

| 28-SSOP, SOIC<br>28-SPDIP | 28-QFN, UQFN | 0/1 | Analog | Comparator | СТМИ     | SR Latch | Reference       | (E)CCP                                           | EUSART  | MSSP         | Timers                                        | Interrupts | dn-lluq | Basic        |

| 2                         | 27           | RA0 | AN0    | C12IN0-    |          |          |                 |                                                  |         |              |                                               |            |         |              |

| 3                         | 28           | RA1 | AN1    | C12IN1-    |          |          |                 |                                                  |         |              |                                               |            |         |              |

| 4                         | 1            | RA2 | AN2    | C2IN+      |          |          | VREF-<br>DACOUT |                                                  |         |              |                                               |            |         |              |

| 5                         | 2            | RA3 | AN3    | C1IN+      |          |          | VREF+           |                                                  |         |              |                                               |            |         |              |

| 6                         | 3            | RA4 |        | C1OUT      |          | SRQ      |                 | CCP5                                             |         |              | TOCKI                                         |            |         |              |

| 7                         | 4            | RA5 | AN4    | C2OUT      |          | SRNQ     | HLVDIN          |                                                  |         | SS1          |                                               |            |         |              |

| 10                        | 7            | RA6 |        |            |          |          |                 |                                                  |         |              |                                               |            |         | OSC2<br>CLKO |

| 9                         | 6            | RA7 |        |            |          |          |                 |                                                  |         |              |                                               |            |         | OSC1<br>CLKI |

| 21                        | 18           | RB0 | AN12   |            |          | SRI      |                 | CCP4<br>FLT0                                     |         | SS2          |                                               | INT0       | Y       |              |

| 22                        | 19           | RB1 | AN10   | C12IN3-    |          |          |                 | P1C                                              |         | SCK2<br>SCL2 |                                               | INT1       | Y       |              |

| 23                        | 20           | RB2 | AN8    |            | CTED1    |          |                 | P1B                                              |         | SDI2<br>SDA2 |                                               | INT2       | Y       |              |

| 24                        | 21           | RB3 | AN9    | C12IN2-    | CTED2    |          |                 | CCP2<br>P2A <sup>(1)</sup>                       |         | SDO2         |                                               |            | Y       |              |

| 25                        | 22           | RB4 | AN11   |            |          |          |                 | P1D                                              |         |              | T5G                                           | IOC        | Υ       |              |

| 26                        | 23           | RB5 | AN13   |            |          |          |                 | CCP3<br>P3A <sup>(4)</sup><br>P2B <sup>(3)</sup> |         |              | T1G<br>T3CKI <sup>(2)</sup>                   | IOC        | Y       |              |

| 27                        | 24           | RB6 |        |            |          |          |                 |                                                  | TX2/CK2 |              |                                               | IOC        | Y       | PGC          |

| 28                        | 25           | RB7 |        |            |          |          |                 |                                                  | RX2/DT2 |              |                                               | IOC        | Y       | PGD          |

| 11                        | 8            | RC0 |        |            |          |          |                 | P2B <sup>(3)</sup>                               |         |              | SOSCO<br>T1CKI<br>T3CKI <sup>(2)</sup><br>T3G |            |         |              |

| 12                        | 9            | RC1 |        |            |          |          |                 | CCP2<br>P2A <sup>(1)</sup>                       |         |              | SOSCI                                         |            |         |              |

| 13                        | 10           | RC2 | AN14   |            | CTPLS    |          |                 | CCP1<br>P1A                                      |         |              | T5CKI                                         |            |         |              |

| 14                        | 11           | RC3 | AN15   |            |          |          |                 |                                                  |         | SCK1<br>SCL1 |                                               |            |         |              |

| 15                        | 12           | RC4 | AN16   |            |          |          |                 |                                                  |         | SDI1<br>SDA1 |                                               |            |         |              |

| 16                        | 13           | RC5 | AN17   |            |          |          |                 |                                                  |         | SDO1         |                                               |            |         |              |

| 17                        | 14           | RC6 | AN18   |            |          |          |                 | CCP3<br>P3A <sup>(4)</sup>                       | TX1/CK1 |              |                                               |            |         |              |

| 18                        | 15           | RC7 | AN19   |            |          |          |                 | P3B                                              | RX1/DT1 |              |                                               |            |         |              |

| 1                         | 26           | RE3 |        |            |          |          |                 |                                                  |         |              |                                               |            |         | MCLR<br>VPP  |

| 8, 19<br>19               | 5, 16<br>16  | Vss |        |            |          |          |                 |                                                  |         |              |                                               |            |         | Vss          |

| 20                        | 17           | Vdd |        |            |          |          |                 |                                                  |         |              |                                               |            |         | Vdd          |

|                           |              |     |        |            |          |          |                 |                                                  |         |              |                                               |            |         |              |

CCP2/P2A multiplexed in fuses.

T3CKI multiplexed in fuses.

P2B multiplexed in fuses.

CCP3/P3A multiplexed in fuses. Note 1:

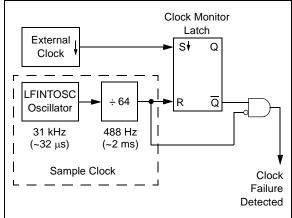

### 2.13 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the CONFIG1H Configuration register. The FSCM is applicable to all external oscillator modes (LP, XT, HS, EC, RC and RCIO).

FIGURE 2-10: FSCM BLOCK DIAGRAM

#### 2.13.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64 (see Figure 2-10). Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the primary clock goes low.

#### 2.13.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSCFIF of the PIR2 register. The OSCFIF flag will generate an interrupt if the OSCFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation. An automatic transition back to the failed clock source will not occur.

The internal clock source chosen by the FSCM is determined by the IRCF<2:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

#### 2.13.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared by either one of the following:

- Any Reset

- · By toggling the SCS1 bit of the OSCCON register

Both of these conditions restart the OST. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device automatically switches over to the external clock source. The Fail-Safe condition need not be cleared before the OSCFIF flag is cleared.

# 2.13.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed.

| Note: | Due to the wide range of oscillator start-up<br>times, the Fail-Safe circuit is not active<br>during oscillator start-up (i.e., after exiting |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|       | •                                                                                                                                             |

|       | Reset or Sleep). After an appropriate                                                                                                         |

|       | amount of time, the user should check the                                                                                                     |

|       | OSTS bit of the OSCCON register to verify                                                                                                     |

|       | the oscillator start-up and that the system                                                                                                   |

|       | clock switchover has successfully                                                                                                             |

|       | completed.                                                                                                                                    |

**Note:** When the device is configured for Fail-Safe clock monitoring in either HS, XT, or LS Oscillator modes then the IESO configuration bit should also be set so that the clock will automatically switch from the internal clock to the external oscillator when the OST times out.

### 4.5 Brown-out Reset (BOR)

PIC18(L)F2X/4XK22 devices implement a BOR circuit that provides the user with a number of configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> bits of the CONFIG2L Configuration register. There are a total of four BOR configurations which are summarized in Table 4-1.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below VBOR for greater than TBOR will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT. If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

BOR and the Power-on Timer (PWRT) are independently configured. Enabling BOR Reset does not automatically enable the PWRT.

The BOR circuit has an output that feeds into the POR circuit and rearms the POR within the operating range of the BOR. This early rearming of the POR ensures that the device will remain in Reset in the event that VDD falls below the operating range of the BOR circuitry.

#### 4.5.1 DETECTING BOR

When BOR is enabled, the  $\overline{\text{BOR}}$  bit always resets to '0' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of  $\overline{\text{BOR}}$  alone. A more reliable method is to simultaneously check the state of both POR and  $\overline{\text{BOR}}$ . This assumes that the POR and  $\overline{\text{BOR}}$  bits are reset to '1' by software immediately after any POR event. If  $\overline{\text{BOR}}$  is '0' while  $\overline{\text{POR}}$  is '1', it can be reliably assumed that a BOR event has occurred.

#### 4.5.2 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the SBOREN control bit of the RCON register. Setting SBOREN enables the BOR to function as previously described. Clearing SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise it is read as '0'.

Placing the BOR under software control gives the user the additional flexibility of tailoring the application to the environment without having to reprogram the device to change BOR configuration. It also allows the user to tailor device power consumption in software by eliminating the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note: | Even                                          | when | BOR | is | under | software |  |  |

|-------|-----------------------------------------------|------|-----|----|-------|----------|--|--|

|       | control, the BOR Reset voltage level is still |      |     |    |       |          |  |  |

|       | set by the BORV<1:0> Configuration bits.      |      |     |    |       |          |  |  |

|       | It cannot be changed by software.             |      |     |    |       |          |  |  |

#### 4.5.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, the BOR remains under hardware control and operates as previously described. Whenever the device enters Sleep mode, however, the BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

#### 4.5.4 MINIMUM BOR ENABLE TIME

Enabling the BOR also enables the Fixed Voltage Reference (FVR) when no other peripheral requiring the FVR is active. The BOR becomes active only after the FVR stabilizes. Therefore, to ensure BOR protection, the FVR settling time must be considered when enabling the BOR in software or when the BOR is automatically enabled after waking from Sleep. If the BOR is disabled, in software or by reentering Sleep before the FVR stabilizes, the BOR circuit will not sense a BOR condition. The FVRST bit of the VREFCON0 register can be used to determine FVR stability.

| U-0                                                                                | U-0                                                                          | U-0              | U-0 | U-0              | R/W-0            | R/W-0           | R/W-0  |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------|-----|------------------|------------------|-----------------|--------|

| —                                                                                  | —                                                                            | —                | —   | —                | CCP5IP           | CCP4IP          | CCP3IP |

| bit 7                                                                              |                                                                              |                  |     | ·                |                  |                 | bit (  |

| Legend:                                                                            |                                                                              |                  |     |                  |                  |                 |        |

| R = Readable                                                                       | e bit                                                                        | W = Writable     | bit | U = Unimpler     | mented bit, read | as '0'          |        |

| -n = Value at                                                                      | POR                                                                          | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 2                                                                              | 1 = High prior<br>0 = Low prior                                              | ity              |     |                  |                  |                 |        |

| bit 1                                                                              | CCP4IP: CCP4 Interrupt Priority bit<br>1 = High priority<br>0 = Low priority |                  |     |                  |                  |                 |        |

| bit 0 CCP3IP: CCP3 Interrupt Priority bit<br>1 = High priority<br>0 = Low priority |                                                                              |                  |     |                  |                  |                 |        |

#### REGISTER 9-17: IPR4: PERIPHERAL INTERRUPT PRIORITY REGISTER 4

# REGISTER 9-18: IPR5: PERIPHERAL INTERRUPT PRIORITY REGISTER 5

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| —     | _   | —   | —   | —   | TMR6IP | TMR5IP | TMR4IP |

| bit 7 |     |     |     |     |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-3 | Unimplemented: Read as '0'                                   |

|---------|--------------------------------------------------------------|

| bit 2   | TMR6IP: TMR6 to PR6 Match Interrupt Priority bit             |

|         | <ul><li>1 = High priority</li><li>0 = Low priority</li></ul> |

| bit 1   | TMR5IP: TMR5 Overflow Interrupt Priority bit                 |

|         | <ul><li>1 = High priority</li><li>0 = Low priority</li></ul> |

| bit 0   | TMR4IP: TMR4 to PR4 Match Interrupt Priority bit             |

|         | 1 = High priority<br>0 = Low priority                        |

#### TABLE 10-5: PORTB I/O SUMMARY (CONTINUED)

| Pin                         | Function              | TRIS<br>Setting | ANSEL<br>Setting | Pin<br>Type | Buffer<br>Type   | Description                                                 |

|-----------------------------|-----------------------|-----------------|------------------|-------------|------------------|-------------------------------------------------------------|

| RB2/INT2/CTED1/             | RB2                   | 0               | 0                | 0           | DIG              | LATB<2> data output; not affected by analog input.          |

| P1B/SDI2/SDA2/<br>AN8       |                       | 1               | 0                | I           | TTL              | PORTB<2> data input; disabled when analog input enabled.    |

|                             | INT2                  | 1               | 0                | I           | ST               | External interrupt 2.                                       |

|                             | CTED1                 | 1               | 0                | I           | ST               | CTMU Edge 1 input.                                          |

|                             | P1B <sup>(3)</sup>    | 0               | 0                | 0           | DIG              | Enhanced CCP1 PWM output 2.                                 |

|                             | SDI2 <sup>(3)</sup>   | 1               | 0                | I           | ST               | MSSP2 SPI data input.                                       |

|                             | SDA2 <sup>(3)</sup>   | 0               | 0                | 0           | DIG              | MSSP2 I <sup>2</sup> C data output.                         |

|                             |                       | 1               | 0                | I           | l <sup>2</sup> C | MSSP2 I <sup>2</sup> C data input.                          |

|                             | AN8                   | 1               | 1                | I           | AN               | Analog input 8.                                             |

| RB3/CTED2/P2A/              | RB3                   | 0               | 0                | 0           | DIG              | LATB<3> data output; not affected by analog input.          |

| CCP2/SDO2/<br>C12IN2-/AN9   |                       | 1               | 0                | I           | TTL              | PORTB<3> data input; disabled when analog input<br>enabled. |

|                             | CTED2                 | 1               | 0                | Ι           | ST               | CTMU Edge 2 input.                                          |

|                             | P2A                   | 0               | 0                | 0           | DIG              | Enhanced CCP1 PWM output 1.                                 |

|                             | CCP2 <sup>(2)</sup>   | 0               | 0                | 0           | DIG              | Compare 2 output/PWM 2 output.                              |

|                             |                       | 1               | 0                | I           | ST               | Capture 2 input.                                            |

|                             | SDO2 <sup>(2)</sup>   | 0               | 0                | 0           | DIG              | MSSP2 SPI data output.                                      |

|                             | C12IN2-               | 1               | 1                | I           | AN               | Comparators C1 and C2 inverting input.                      |

|                             | AN9                   | 1               | 1                | I           | AN               | Analog input 9.                                             |

| RB4/IOC0/P1D/               | RB4                   | 0               | 0                | 0           | DIG              | LATB<4> data output; not affected by analog input.          |

| T5G/AN11                    |                       | 1               | 0                | -           | TTL              | PORTB<4> data input; disabled when analog input enabled.    |

|                             | IOC0                  | 1               | 0                | I           | TTL              | Interrupt-on-change pin.                                    |

|                             | P1D                   | 0               | 0                | 0           | DIG              | Enhanced CCP1 PWM output 4.                                 |

|                             | T5G                   | 1               | 0                | I           | ST               | Timer5 external clock gate input.                           |

|                             | AN11                  | 1               | 1                | -           | AN               | Analog input 11.                                            |

| RB5/IOC1/P2B/               | RB5                   | 0               | 0                | 0           | DIG              | LATB<5> data output; not affected by analog input.          |

| P3A/CCP3/T3CKI/<br>T1G/AN13 |                       | 1               | 0                | ļ           | TTL              | PORTB<5> data input; disabled when analog input enabled.    |

|                             | IOC1                  | 1               | 0                | I           | TTL              | Interrupt-on-change pin 1.                                  |

|                             | P2B <sup>(1)(3)</sup> | 0               | 0                | 0           | DIG              | Enhanced CCP2 PWM output 2.                                 |

|                             | P3A <sup>(1)</sup>    | 0               | 0                | 0           | DIG              | Enhanced CCP3 PWM output 1.                                 |

|                             | CCP3 <sup>(1)</sup>   | 0               | 0                | 0           | DIG              | Compare 3 output/PWM 3 output.                              |

|                             |                       | 1               | 0                | I           | ST               | Capture 3 input.                                            |

|                             | T3CKI <sup>(2)</sup>  | 1               | 0                | I           | ST               | Timer3 clock input.                                         |

|                             | T1G                   | 1               | 0                | I           | ST               | Timer1 external clock gate input.                           |

|                             | AN13                  | 1               | 1                | I           | AN               | Analog input 13.                                            |

**Legend:** AN = Analog input or output; TTL = TTL compatible input;  $HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; <math>I^2C = Schmitt Trigger input with I^2C$ .

**Note 1:** Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

3: Function on PORTD and PORTE for PIC18(L)F4XK22 devices.

| FIGURE 12-7:           | TIMER1/3/5 GATE SING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LE-PULSE AND TOGGLE COMBINED MODE                   |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| TMRxGE                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGPOL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGSPM                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGTM                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGG <u>O/</u><br>DONE | <ul> <li>Set by software</li> <li>Counting enabled of the set of the</li></ul> | Cleared by hardware on falling edge of TxGVAL       |

| TxG_IN                 | rising edge of TxG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

| ТхСКІ                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGVAL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TIMER1/3/5             | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>N + 1</u> <u>N + 2</u> <u>N + 3</u> <u>N + 4</u> |

| TMRxGIF                | — Cleared by software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Set by hardware on<br>falling edge of TxGVAL        |

# 12.12 Peripheral Module Disable

When a peripheral module is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bits for Timer1 (TMR1MD), Timer3 (TMR3MD) and Timer5 (TMR5MD) are in the PMD0 Register. See Section 3.0 "Power-Managed Modes" for more information.

#### 14.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is selected (CCPxM<3:0> = 1011), and a match of the TMRxH:TMRxL and the CCPRxH:CCPRxL registers occurs, all CCPx and ECCPx modules will immediately:

- Set the CCP interrupt flag bit CCPxIF

- CCP5 will start an ADC conversion, if the ADC is enabled

On the next TimerX rising clock edge:

• A Reset of TimerX register pair occurs – TMRxH:TMRxL = 0x0000,

This Special Event Trigger mode does not:

- Assert control over the CCPx or ECCPx pins.

- Set the TMRxIF interrupt bit when the TMRxH:TMRxL register pair is reset. (TMRxIF gets set on a TimerX overflow.)

If the value of the CCPRxH:CCPRxL registers are modified when a match occurs, the user should be aware that the automatic reset of TimerX occurs on the next rising edge of the clock. Therefore, modifying the CCPRxH:CCPRxL registers before this reset occurs will allow the TimerX to continue without being reset, inadvertently resulting in the next event being advanced or delayed.

The Special Event Trigger mode allows the CCPRxH:CCPRxL register pair to effectively provide a 16-bit programmable period register for TimerX.

#### Register Bit 4 Name Bit 7 Bit 6 Bit 5 Bit 3 Bit 2 Bit 1 Bit 0 on Page CCP1CON P1M<1:0> DC1B<1.0>CCP1M<3:0> 198 P2M<1:0> CCP2CON DC2B<1.0> CCP2M<3:0> 198 CCP3CON P3M<1:0> DC3B<1:0> CCP3M<3:0> 198 CCP4CON DC4B<1:0> CCP4M<3:0> 198 CCP5CON CCP5M<3:0> DC5B<1:0> 198 CCPR1H Capture/Compare/PWM Register 1 High Byte (MSB) CCPR1L Capture/Compare/PWM Register 1 Low Byte (LSB) CCPR2H Capture/Compare/PWM Register 2 High Byte (MSB) \_\_\_\_ CCPR2L Capture/Compare/PWM Register 2 Low Byte (LSB) \_ CCPR3H Capture/Compare/PWM Register 3 High Byte (MSB) \_ CCPR3L Capture/Compare/PWM Register 3 Low Byte (LSB) CCPR4H Capture/Compare/PWM Register 4 High Byte (MSB) \_\_\_\_ CCPR4L Capture/Compare/PWM Register 4 Low Byte (LSB) CCPR5H Capture/Compare/PWM Register 5 High Byte (MSB) \_\_\_\_ CCPR5L Capture/Compare/PWM Register 5 Low Byte (LSB) CCPTMRS0 C3TSEL<1:0> C2TSEL<1:0> C1TSEL<1:0> \_\_\_\_\_ 201 CCPTMRS1 C5TSEL<1:0> C4TSEL<1:0> 201 INTCON RBIE TMR0IF **INTOIF GIE/GIEH** PEIE/GIEL TMR0IE **INTOIE** RBIF 109 IPR1 ADIP RC1IP TX1IP SSP1IP CCP1IP TMR2IP TMR1IP 121

### TABLE 14-5: REGISTERS ASSOCIATED WITH COMPARE

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Compare mode.

Note 1: These registers/bits are available on PIC18(L)F4XK22 devices.

#### 14.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

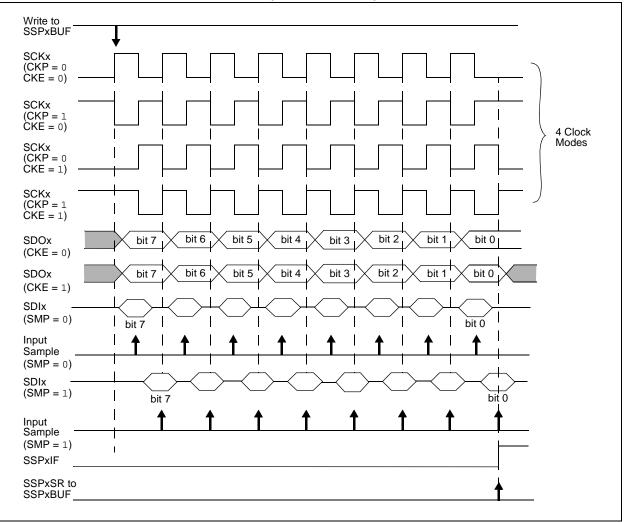

#### 15.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCKx line. The master determines when the slave (Processor 2, Figure 15-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPxBUF register is written to. If the SPI is only going to receive, the SDOx output could be disabled (programmed as an input). The SSPxSR register will continue to shift in the signal present on the SDIx pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPxBUF register as if a normal received byte (interrupts and Status bits appropriately set).

The clock polarity is selected by appropriately programming the CKP bit of the SSPxCON1 register and the CKE bit of the SSPxSTAT register.

This then, would give waveforms for SPI communication as shown in Figure 15-6, Figure 15-8, Figure 15-9 and Figure 15-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPxADD + 1))

Figure 15-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDOx data is valid before there is a clock edge on SCKx. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPxBUF is loaded with the received data is shown.

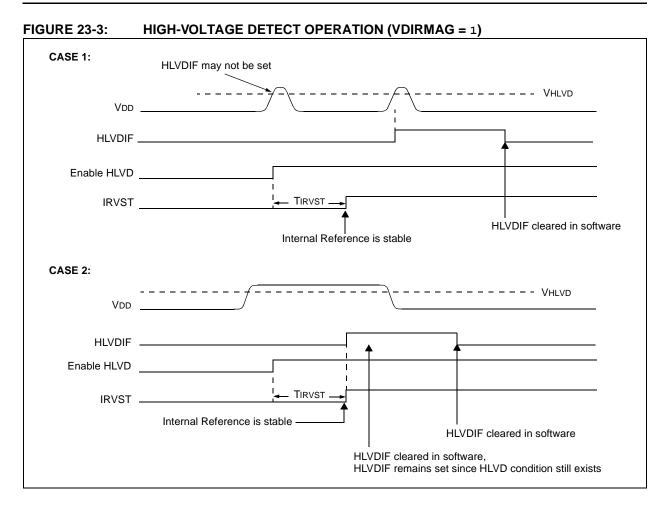

# 23.6 Applications

In many applications, it is desirable to detect a drop below, or rise above, a particular voltage threshold. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

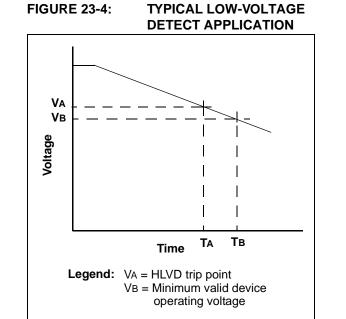

For general battery applications, Figure 23-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and a controlled shutdown before the device voltage exits the valid operating range at TB. This would give the application a time window, represented by the difference between TA and TB, to safely exit.

| ΒZ           |                                                                                     | Branch if                                                                 | Branch if Zero                                                                                                           |                                                          |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|

| Synta        | ax:                                                                                 | BZ n                                                                      | BZ n                                                                                                                     |                                                          |  |  |  |  |  |

| Oper         | ands:                                                                               | -128 ≤ n ≤ ′                                                              | 27                                                                                                                       |                                                          |  |  |  |  |  |

| Oper         | ation:                                                                              | if ZERO bit<br>(PC) + 2 + 2                                               |                                                                                                                          |                                                          |  |  |  |  |  |

| Statu        | is Affected:                                                                        | None                                                                      |                                                                                                                          |                                                          |  |  |  |  |  |

| Enco         | oding:                                                                              | 1110                                                                      | 0000 nnr                                                                                                                 | nn nnnn                                                  |  |  |  |  |  |

| Desc         | ription:                                                                            | will branch.<br>The 2's con<br>added to th<br>have incren<br>instruction, | ) bit is '1', ther<br>nplement num<br>e PC. Since th<br>nented to fetch<br>the new addre<br>n. This instruct<br>ruction. | ber '2n' is<br>he PC will<br>he the next<br>hess will be |  |  |  |  |  |

| Word         | ds:                                                                                 | 1                                                                         |                                                                                                                          |                                                          |  |  |  |  |  |

| Cycle        | es:                                                                                 | 1(2)                                                                      | 1(2)                                                                                                                     |                                                          |  |  |  |  |  |

| Q C<br>If Ju | ycle Activity:                                                                      |                                                                           |                                                                                                                          |                                                          |  |  |  |  |  |

|              | Q1                                                                                  | Q2                                                                        | Q3                                                                                                                       | Q4                                                       |  |  |  |  |  |

|              | Decode                                                                              | Read literal<br>'n'                                                       | Process<br>Data                                                                                                          | Write to PC                                              |  |  |  |  |  |

|              | No<br>operation                                                                     | No<br>operation                                                           | No<br>operation                                                                                                          | No<br>operation                                          |  |  |  |  |  |

| lf No        | o Jump:                                                                             |                                                                           |                                                                                                                          |                                                          |  |  |  |  |  |

|              | Q1                                                                                  | Q2                                                                        | Q3                                                                                                                       | Q4                                                       |  |  |  |  |  |

|              | Decode                                                                              | Read literal<br>'n'                                                       | Process<br>Data                                                                                                          | No<br>operation                                          |  |  |  |  |  |

| <u>Exan</u>  | nple:<br>Before Instruc<br>PC<br>After Instructic<br>If ZERO<br>PC<br>If ZERO<br>PC | = ad<br>= 1;<br>= ad<br>= 0;                                              | BZ Jump<br>dress (HERE<br>dress (Jump<br>dress (HERE                                                                     | )                                                        |  |  |  |  |  |

|                                                     | Subrouti                                                                                                                                                             |                                                                                                                                 |                                                                                               |                                                                                                                                     |                      |  |  |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| Syntax:                                             | -                                                                                                                                                                    | CALL k {,s}                                                                                                                     |                                                                                               |                                                                                                                                     |                      |  |  |

| Operands:                                           | 0 ≤ k ≤ 104<br>s ∈ [0,1]                                                                                                                                             | 8575                                                                                                                            |                                                                                               |                                                                                                                                     |                      |  |  |

| Operation:                                          | (PC) + 4 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<20:1>,<br>if s = 1<br>(W) $\rightarrow$ WS,<br>(Status) $\rightarrow$ STATUSS,<br>(BSR) $\rightarrow$ BSRS         |                                                                                                                                 |                                                                                               |                                                                                                                                     |                      |  |  |

| Status Affected:                                    | None                                                                                                                                                                 |                                                                                                                                 |                                                                                               |                                                                                                                                     |                      |  |  |

| Encoding:<br>1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110<br>1111                                                                                                                                                         | 110s<br>k <sub>19</sub> kkk                                                                                                     | k <sub>7</sub> kki<br>kkkk                                                                    |                                                                                                                                     |                      |  |  |

|                                                     | memory ra                                                                                                                                                            |                                                                                                                                 |                                                                                               |                                                                                                                                     | s                    |  |  |

|                                                     | (PC + 4) is<br>stack. If 's'<br>BSR registr<br>respective<br>STATUSS i<br>update occ<br>20-bit value<br>CALL is a                                                    | pushed of<br>= 1, the <sup>1</sup><br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                            | onto the<br>W, STA<br>so push<br>registers<br>S. If 's'<br>ult). Th<br>ded into               | e return<br>TUS and<br>hed into<br>'s, WS,<br>= 0, no<br>hen, the<br>o PC<20                                                        | d<br>th              |  |  |

| Words:                                              | (PC + 4) is<br>stack. If 's'<br>BSR registe<br>respective<br>STATUSS<br>update occ<br>20-bit value                                                                   | pushed of<br>= 1, the <sup>1</sup><br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                            | onto the<br>W, STA<br>so push<br>registers<br>S. If 's'<br>ult). Th<br>ded into               | e return<br>TUS and<br>hed into<br>'s, WS,<br>= 0, no<br>hen, the<br>o PC<20                                                        | d<br>th              |  |  |

| Words:<br>Cycles:                                   | (PC + 4) is<br>stack. If 's'<br>BSR register<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a                                                   | pushed of<br>= 1, the <sup>1</sup><br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                            | onto the<br>W, STA<br>so push<br>registers<br>S. If 's'<br>ult). Th<br>ded into               | e return<br>TUS and<br>hed into<br>'s, WS,<br>= 0, no<br>hen, the<br>o PC<20                                                        | d<br>th              |  |  |

|                                                     | (PC + 4) is<br>stack. If 's'<br>BSR registr<br>respective<br>STATUSS i<br>update occ<br>20-bit value<br>CALL is a                                                    | pushed of<br>= 1, the <sup>1</sup><br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                            | onto the<br>W, STA<br>so push<br>registers<br>S. If 's'<br>ult). Th<br>ded into               | e return<br>TUS and<br>hed into<br>'s, WS,<br>= 0, no<br>hen, the<br>o PC<20                                                        | d<br>th              |  |  |

| Cycles:                                             | (PC + 4) is<br>stack. If 's'<br>BSR registr<br>respective<br>STATUSS i<br>update occ<br>20-bit value<br>CALL is a                                                    | pushed of<br>= 1, the <sup>1</sup><br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                            | onto the<br>W, STA<br>register:<br>S. If 's'<br>ult). Th<br>ded into<br>astructio             | e return<br>TUS and<br>hed into<br>'s, WS,<br>= 0, no<br>hen, the<br>o PC<20                                                        | d<br>th              |  |  |

| Cycles:<br>Q Cycle Activity:                        | (PC + 4) is<br>stack. If 's'<br>BSR registr<br>respective<br>STATUSS i<br>update occ<br>20-bit value<br>CALL is a<br>2<br>2                                          | pushed (<br>= 1, the <sup>1</sup> )<br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>9 'k' is loa<br>2-cycle ir             | onto the<br>W, STA<br>so push<br>register:<br>S. If 's'<br>ult). Th<br>ded into<br>astruction | e return<br>TUS and<br>hed into<br>s, WS,<br>= 0, no<br>ien, the<br>o PC<20<br>on.                                                  | d<br>th<br>0:1       |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>No  | (PC + 4) is<br>stack. If 's'<br>BSR registr<br>respective<br>STATUSS i<br>update occ<br>20-bit value<br>CALL is a<br>2<br>2<br>Q2<br>Read literal<br>'k'<7:0>,<br>No | pushed (<br>= 1, the V<br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa<br>2-cycle ir<br>Q3<br>PUSH F<br>stac  | onto the<br>W, STA<br>so push<br>register:<br>S. If 's'<br>ult). Th<br>ded into<br>astruction | e return<br>TUS and<br>hed into<br>s, WS,<br>= 0, no<br>hen, the<br>o PC<20<br>on.<br>Q4<br>Read litt<br>'k'<19:8<br>Write to<br>No | d<br>D:1<br>er<br>8> |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode        | (PC + 4) is<br>stack. If 's'<br>BSR registr<br>respective<br>STATUSS<br>update occ<br>20-bit value<br>CALL is a<br>2<br>2<br>2<br>Read literal<br>'k'<7:0>,          | pushed of<br>= 1, the V<br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa<br>2-cycle ir<br>Q3<br>PUSH F<br>stac | onto the<br>W, STA<br>so push<br>register:<br>S. If 's'<br>ult). Th<br>ded into<br>astruction | e return<br>TUS and<br>hed into<br>s, WS,<br>= 0, no<br>hen, the<br>o PC<20<br>on.<br>Q4<br>Read litt<br>'k'<19:8<br>Write to       | d<br>D:1<br>er<br>8> |  |  |

After Instruction

PC = TOS = WS = BSRS = STATUSS = address (THERE) address (HERE + 4) W BSR Status

| Param.<br>No. | Symbol    |                            | Characteristi                    | c              | Min                                     | Max    | Units | Conditions                               |

|---------------|-----------|----------------------------|----------------------------------|----------------|-----------------------------------------|--------|-------|------------------------------------------|

| 40            | Tt0H      | T0CKI High P               | ulse Width                       | No prescaler   | 0.5 TCY + 20                            |        | ns    |                                          |