Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 30x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

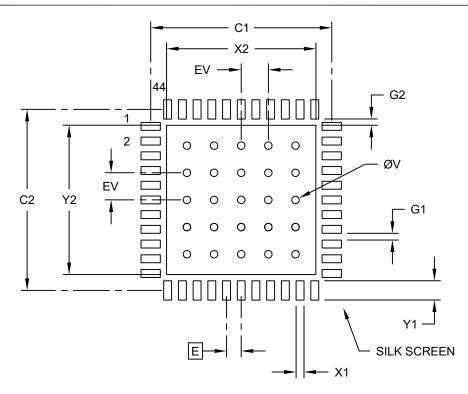

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f44k22-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 2: | PIC18(L)F2XK22 PIN SUMMARY |

|----------|----------------------------|

|----------|----------------------------|

| IAD                       | ABLE 2. FICTO(L)FZARZZ FIN SUMMART |     |        |            |       |          |                 |                                                  |         |              |                                               |            |         |              |

|---------------------------|------------------------------------|-----|--------|------------|-------|----------|-----------------|--------------------------------------------------|---------|--------------|-----------------------------------------------|------------|---------|--------------|

| 28-SSOP, SOIC<br>28-SPDIP | 28-QFN, UQFN                       | 0/1 | Analog | Comparator | СТМИ  | SR Latch | Reference       | (E)CCP                                           | EUSART  | MSSP         | Timers                                        | Interrupts | dn-lluq | Basic        |

| 2                         | 27                                 | RA0 | AN0    | C12IN0-    |       |          |                 |                                                  |         |              |                                               |            |         |              |

| 3                         | 28                                 | RA1 | AN1    | C12IN1-    |       |          |                 |                                                  |         |              |                                               |            |         |              |

| 4                         | 1                                  | RA2 | AN2    | C2IN+      |       |          | VREF-<br>DACOUT |                                                  |         |              |                                               |            |         |              |

| 5                         | 2                                  | RA3 | AN3    | C1IN+      |       |          | VREF+           |                                                  |         |              |                                               |            |         |              |

| 6                         | 3                                  | RA4 |        | C1OUT      |       | SRQ      |                 | CCP5                                             |         |              | TOCKI                                         |            |         |              |

| 7                         | 4                                  | RA5 | AN4    | C2OUT      |       | SRNQ     | HLVDIN          |                                                  |         | SS1          |                                               |            |         |              |

| 10                        | 7                                  | RA6 |        |            |       |          |                 |                                                  |         |              |                                               |            |         | OSC2<br>CLKO |

| 9                         | 6                                  | RA7 |        |            |       |          |                 |                                                  |         |              |                                               |            |         | OSC1<br>CLKI |

| 21                        | 18                                 | RB0 | AN12   |            |       | SRI      |                 | CCP4<br>FLT0                                     |         | SS2          |                                               | INT0       | Y       |              |

| 22                        | 19                                 | RB1 | AN10   | C12IN3-    |       |          |                 | P1C                                              |         | SCK2<br>SCL2 |                                               | INT1       | Y       |              |

| 23                        | 20                                 | RB2 | AN8    |            | CTED1 |          |                 | P1B                                              |         | SDI2<br>SDA2 |                                               | INT2       | Y       |              |

| 24                        | 21                                 | RB3 | AN9    | C12IN2-    | CTED2 |          |                 | CCP2<br>P2A <sup>(1)</sup>                       |         | SDO2         |                                               |            | Y       |              |

| 25                        | 22                                 | RB4 | AN11   |            |       |          |                 | P1D                                              |         |              | T5G                                           | IOC        | Υ       |              |

| 26                        | 23                                 | RB5 | AN13   |            |       |          |                 | CCP3<br>P3A <sup>(4)</sup><br>P2B <sup>(3)</sup> |         |              | T1G<br>T3CKI <sup>(2)</sup>                   | IOC        | Y       |              |

| 27                        | 24                                 | RB6 |        |            |       |          |                 |                                                  | TX2/CK2 |              |                                               | IOC        | Y       | PGC          |

| 28                        | 25                                 | RB7 |        |            |       |          |                 |                                                  | RX2/DT2 |              |                                               | IOC        | Y       | PGD          |

| 11                        | 8                                  | RC0 |        |            |       |          |                 | P2B <sup>(3)</sup>                               |         |              | SOSCO<br>T1CKI<br>T3CKI <sup>(2)</sup><br>T3G |            |         |              |

| 12                        | 9                                  | RC1 |        |            |       |          |                 | CCP2<br>P2A <sup>(1)</sup>                       |         |              | SOSCI                                         |            |         |              |

| 13                        | 10                                 | RC2 | AN14   |            | CTPLS |          |                 | CCP1<br>P1A                                      |         |              | T5CKI                                         |            |         |              |

| 14                        | 11                                 | RC3 | AN15   |            |       |          |                 |                                                  |         | SCK1<br>SCL1 |                                               |            |         |              |

| 15                        | 12                                 | RC4 | AN16   |            |       |          |                 |                                                  |         | SDI1<br>SDA1 |                                               |            |         |              |

| 16                        | 13                                 | RC5 | AN17   |            |       |          |                 |                                                  |         | SDO1         |                                               |            |         |              |

| 17                        | 14                                 | RC6 | AN18   |            |       |          |                 | CCP3<br>P3A <sup>(4)</sup>                       | TX1/CK1 |              |                                               |            |         |              |

| 18                        | 15                                 | RC7 | AN19   |            |       |          |                 | P3B                                              | RX1/DT1 |              |                                               |            |         |              |

| 1                         | 26                                 | RE3 |        |            |       |          |                 |                                                  |         |              |                                               |            |         | MCLR<br>VPP  |

| 8, 19<br>19               | 5, 16<br>16                        | Vss |        |            |       |          |                 |                                                  |         |              |                                               |            |         | Vss          |

| 20                        | 17                                 | Vdd |        |            |       |          |                 |                                                  |         |              |                                               |            |         | Vdd          |

|                           |                                    |     |        |            |       |          |                 |                                                  |         |              |                                               |            |         |              |

CCP2/P2A multiplexed in fuses.

T3CKI multiplexed in fuses.

P2B multiplexed in fuses.

CCP3/P3A multiplexed in fuses. Note 1:

#### 2.9 Effects of Power-Managed Modes on the Various Clock Sources

For more information about the modes discussed in this section see **Section 3.0** "**Power-Managed Modes**". A quick reference list is also available in Table 3-1.

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin, if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the secondary oscillator (SOSC) is operating and providing the device clock. The secondary oscillator may also run in all power-managed modes if required to clock Timer1, Timer3 or Timer5.

In internal oscillator modes (INTOSC\_RUN and INTOSC\_IDLE), the internal oscillator block provides the device clock source. The 31.25 kHz LFINTOSC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the power-managed mode (see Section 24.3 "Watchdog Timer (WDT)", Section 2.12 "Two-Speed Clock Start-up Mode" and Section 2.13 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up). The HFINTOSC and MFINTOSC outputs may be used directly to clock the device or may be divided down by the postscaler. The HFINTOSC and MFINTOSC outputs are disabled when the clock is provided directly from the LFINTOSC output.

When the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The LFINTOSC is required to support WDT operation. Other features may be operating that do not require a device clock source (i.e., SSP slave, PSP, INTn pins and others). Peripherals that may add significant current consumption are listed in Section 27.8 "DC Characteristics: Input/Output Characteristics, PIC18(L)F2X/4XK22".

#### 2.10 Power-up Delays

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 4.6** "**Device Reset Timers**".

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up. It is enabled by clearing (= 0) the PWRTEN Configuration bit.

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the PLL is enabled with external oscillator modes, the device is kept in Reset for an additional 2 ms, following the OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of interval TCSD, following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIOSC modes are used as the primary clock source.

When the HFINTOSC is selected as the primary clock, the main system clock can be delayed until the HFINTOSC is stable. This is user selectable by the HFOFST bit of the CONFIG3H Configuration register. When the HFOFST bit is cleared, the main system clock is delayed until the HFINTOSC is stable. When the HFOFST bit is set, the main system clock starts immediately.

In either case, the HFIOFS bit of the OSCCON register can be read to determine whether the HFINTOSC is operating and stable.

| Address | Name     | Bit 7     | Bit 6                                                                                                                                                                                                                                        | Bit 5           | Bit 4           | Bit 3                           | Bit 2           | Bit 1           | Bit 0            | <u>Value c</u><br>POR, BO |     |

|---------|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|---------------------------------|-----------------|-----------------|------------------|---------------------------|-----|

| FFFh    | TOSU     | —         | Top-of-Stack, Upper Byte (TOS<20:16>)                                                                                                                                                                                                        |                 |                 |                                 |                 |                 |                  |                           | 000 |

| FFEh    | TOSH     |           | Top-of-Stack, High Byte (TOS<15:8>)                                                                                                                                                                                                          |                 |                 |                                 |                 |                 |                  |                           |     |

| FFDh    | TOSL     |           | Top-of-Stack, Low Byte (TOS<7:0>)                                                                                                                                                                                                            |                 |                 |                                 |                 |                 |                  |                           |     |

| FFCh    | STKPTR   | STKFUL    | STKUNF                                                                                                                                                                                                                                       | _               |                 | ç                               | STKPTR<4:0>     |                 |                  | 00-00                     | 000 |

| FFBh    | PCLATU   | _         | _                                                                                                                                                                                                                                            | _               |                 | Holding F                       | Register for PC | <20:16>         |                  | 0 00                      | 000 |

| FFAh    | PCLATH   |           | •                                                                                                                                                                                                                                            | ŀ               | Holding Regist  | er for PC<15:8                  | >               |                 |                  | 0000 00                   | 000 |

| FF9h    | PCL      |           |                                                                                                                                                                                                                                              |                 | Holding Regis   | ter for PC<7:0>                 | •               |                 |                  | 0000 00                   | 000 |

| FF8h    | TBLPTRU  | _         | _                                                                                                                                                                                                                                            | Pi              | rogram Memor    | y Table Pointer                 | Upper Byte(T    | BLPTR<21:16     | 6>)              | 00 00                     | 000 |

| FF7h    | TBLPTRH  |           | F                                                                                                                                                                                                                                            | Program Memo    | ory Table Point | ter High Byte(T                 | BLPTR<15:8>     | )               |                  | 0000 00                   | 000 |

| FF6h    | TBLPTRL  |           | Р                                                                                                                                                                                                                                            | rogram Memo     | ory Table Point | er Low Byte(TE                  | 3LPTR<7:0>)     |                 |                  | 0000 00                   | 000 |

| FF5h    | TABLAT   |           |                                                                                                                                                                                                                                              |                 | Program Men     | ory Table Latc                  | h               |                 |                  | 0000 00                   | 000 |

| FF4h    | PRODH    |           |                                                                                                                                                                                                                                              |                 | Product Regis   | ter, High Byte                  |                 |                 |                  | XXXX XX                   | xxx |

| FF3h    | PRODL    |           |                                                                                                                                                                                                                                              |                 | Product Regis   | ster, Low Byte                  |                 |                 |                  | XXXX XX                   | xxx |

| FF2h    | INTCON   | GIE/GIEH  | PEIE/GIEL                                                                                                                                                                                                                                    | TMR0IE          | INTOIE          | RBIE                            | TMR0IF          | INT0IF          | RBIF             | 0000 00                   | 00x |

| FF1h    | INTCON2  | RBPU      | INTEDG0                                                                                                                                                                                                                                      | INTEDG1         | INTEDG2         | _                               | TMR0IP          | _               | RBIP             | 1111 -1                   | 1-1 |

| FF0h    | INTCON3  | INT2IP    | INT1IP                                                                                                                                                                                                                                       | _               | INT2IE          | INT1IE                          | _               | INT2IF          | INT1IF           | 11-0 0-                   | -00 |

| FEFh    | INDF0    | Uses cont | ents of FSR0                                                                                                                                                                                                                                 | to address da   | ta memorv – v   | alue of FSR0 r                  | ot changed (no  | ot a physical r | egister)         |                           |     |

| FEEh    | POSTINCO |           |                                                                                                                                                                                                                                              |                 |                 | alue of FSR0 p                  | <b>.</b> .      |                 | • ,              |                           |     |

| FEDh    | POSTDEC0 |           |                                                                                                                                                                                                                                              |                 | ,               | alue of FSR0 p                  |                 | · · · ·         | 0 /              |                           |     |

| FECh    | PREINC0  |           |                                                                                                                                                                                                                                              |                 | ,               |                                 |                 | · · · ·         | 0 /              |                           |     |

| FEBh    | PLUSW0   |           | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register)<br>Jses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register) – value of FSR0 offset by W |                 |                 |                                 |                 |                 |                  |                           |     |

| FEAh    | FSR0H    | _         | — — — Indirect Data Memory Address Pointer 0, High Byte                                                                                                                                                                                      |                 |                 |                                 |                 |                 |                  | 00                        | 000 |

| FE9h    | FSR0L    | In        | direct Data Me                                                                                                                                                                                                                               | emory Addres    | s Pointer 0, Lo | w Byte                          |                 |                 |                  | XXXX XX                   | xxx |

| FE8h    | WREG     |           |                                                                                                                                                                                                                                              | 1               | Working Regis   | ter                             |                 |                 |                  | XXXX XX                   | xxx |

| FE7h    | INDF1    | Uses cor  | ntents of FSR1                                                                                                                                                                                                                               | to address d    | ata memory -    | value of FSR1                   | not changed (i  | not a physical  | reaister)        |                           |     |

| FE6h    | POSTINC1 |           |                                                                                                                                                                                                                                              |                 |                 | value of FSR1                   | 0 (             |                 | • <i>i</i>       |                           |     |

| FE5h    | POSTDEC1 |           |                                                                                                                                                                                                                                              |                 |                 | value of FSR1                   |                 |                 |                  |                           |     |

| FE4h    | PREINC1  |           |                                                                                                                                                                                                                                              |                 |                 | value of FSR1                   |                 |                 |                  |                           |     |

| FE3h    | PLUSW1   |           |                                                                                                                                                                                                                                              |                 | memory – val    | ue of FSR1 pre                  |                 | · · · ·         |                  |                           |     |

| FE2h    | FSR1H    | _         | _                                                                                                                                                                                                                                            | _               | _               | Indirect Dat                    | a Memory Add    | ress Pointer 1  | , High Byte      | 00                        | 000 |

| FE1h    | FSR1L    |           | •                                                                                                                                                                                                                                            | Indirect Data I | Memory Addre    | ss Pointer 1, L                 | ow Byte         |                 |                  | XXXX XX                   | xxx |

| FE0h    | BSR      | —         | —                                                                                                                                                                                                                                            | —               | —               |                                 | Bank Selec      | t Register      |                  | 00                        | 000 |

| FDFh    | INDF2    | Uses co   | ntents of FSR                                                                                                                                                                                                                                | 2 to address of | ata memory -    | value of FSR2                   | not changed (   | not a physical  | l register)      |                           |     |

| FDEh    | POSTINC2 | Uses co   | ntents of FSR                                                                                                                                                                                                                                | 2 to address d  | lata memory –   | value of FSR2                   | post-incremer   | ited (not a phy | /sical register) |                           |     |

| FDDh    | POSTDEC2 | Uses co   | ntents of FSR2                                                                                                                                                                                                                               | 2 to address d  | ata memory –    | value of FSR2                   | post-decreme    | nted (not a ph  | vsical register  | )                         |     |

| FDCh    | PREINC2  |           |                                                                                                                                                                                                                                              |                 |                 | - value of FSR2                 |                 |                 |                  |                           |     |

| FDBh    | PLUSW2   |           |                                                                                                                                                                                                                                              |                 | memory – val    | ue of FSR2 pre<br>2 offset by W |                 |                 | , s              |                           |     |

| FDAh    | FSR2H    | _         | _                                                                                                                                                                                                                                            | _               | _               | Indirect Dat                    | a Memory Add    | ress Pointer 2  | , High Byte      | 00                        | 000 |

| FD9h    | FSR2L    |           |                                                                                                                                                                                                                                              | ndirect Data N  | lemory Addres   | s Pointer 2, Lo                 | w Byte          |                 |                  | XXXX XX                   | xxx |

| FD8h    | STATUS   | _         | _                                                                                                                                                                                                                                            | _               | N               | OV                              | Z               | DC              | С                | x xx                      |     |

| FD7h    | TMR0H    |           | 1                                                                                                                                                                                                                                            | 1               | Timer0 Regist   |                                 |                 | -               | -                | 0000 00                   |     |

| FD6h    | TMR0L    |           |                                                                                                                                                                                                                                              |                 | Timer0 Regist   |                                 |                 |                 |                  | xxxx xx                   |     |

| FD5h    | TOCON    | TMR0ON    | T08BIT                                                                                                                                                                                                                                       | TOCS            | TOSE            | PSA                             |                 | T0PS<2:0>       |                  | 1111 11                   |     |

| FD3h    | OSCCON   | IDLEN     | 100011                                                                                                                                                                                                                                       | IRCF<2:0>       | 1002            | OSTS                            | HFIOFS          |                 | <1:0>            | 0011 q                    |     |

| FD2h    | OSCCON2  | PLLRDY    | SOSCRUN                                                                                                                                                                                                                                      |                 | MFIOSEL         | SOSCGO                          | PRISD           | MFIOFS          | LFIOFS           | 00-0 01                   |     |

| Legend: |          |           |                                                                                                                                                                                                                                              |                 |                 | nds on conditio                 |                 |                 |                  | 00.000                    | -70 |

TABLE 5-2: REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES

Note 1: PIC18(L)F4XK22 devices only.

2: PIC18(L)F2XK22 devices only.

3: PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

| Address | Name                  | Bit 7   | Bit 6                                     | Bit 5                        | Bit 4            | Bit 3                   | Bit 2          | Bit 1                        | Bit 0   | <u>Value on</u><br>POR, BOR |

|---------|-----------------------|---------|-------------------------------------------|------------------------------|------------------|-------------------------|----------------|------------------------------|---------|-----------------------------|

| FD1h    | WDTCON                | _       | —                                         | —                            | _                | _                       |                | —                            | SWDTEN  | 0                           |

| FD0h    | RCON                  | IPEN    | SBOREN                                    | _                            | RI               | TO                      | PD             | POR                          | BOR     | 01-1 1100                   |

| FCFh    | TMR1H                 |         | Holding R                                 | egister for the              | Most Significa   | ant Byte of the         | 16-bit TMR1 R  | egister                      | •       | xxxx xxxx                   |

| FCEh    | TMR1L                 |         |                                           | Least Signif                 | icant Byte of th | ne 16-bit TMR1          | Register       |                              |         | xxxx xxxx                   |

| FCDh    | T1CON                 | TMR1C   | S<1:0>                                    | T1CKF                        | PS<1:0>          | T1SOSCEN                | T1SYNC         | T1RD16                       | TMR10N  | 0000 0000                   |

| FCCh    | T1GCON                | TMR1GE  | T1GPOL                                    | T1GTM                        | T1GSPM           | T <u>1GGO</u> /<br>DONE | T1GVAL         | T1GS                         | S<1:0>  | 0000 xx00                   |

| FCBh    | SSP1CON3              | ACKTIM  | PCIE                                      | SCIE                         | BOEN             | SDAHT                   | SBCDE          | AHEN                         | DHEN    | 0000 0000                   |

| FCAh    | SSP1MSK               |         |                                           |                              | SSP1 MASK F      | Register bits           |                |                              |         | 1111 1111                   |

| FC9h    | SSP1BUF               |         |                                           | SSP1                         | Receive Buffer   | r/Transmit Reg          | ister          |                              |         | xxxx xxxx                   |

| FC8h    | SSP1ADD               | SSP1    | Address Regis                             | ster in I <sup>2</sup> C Sla | ve Mode. SSP     | 1 Baud Rate R           | eload Register | r in I <sup>2</sup> C Master | Mode    | 0000 0000                   |

| FC7h    | SSP1STAT              | SMP     | CKE                                       | D/A                          | Р                | S                       | R/W            | UA                           | BF      | 0000 0000                   |

| FC6h    | SSP1CON1              | WCOL    | SSPOV                                     | SSPEN                        | CKP              |                         | SSPM           | <3:0>                        |         | 0000 0000                   |

| FC5h    | SSP1CON2              | GCEN    | ACKSTAT                                   | ACKDT                        | ACKEN            | RCEN                    | PEN            | RSEN                         | SEN     | 0000 0000                   |

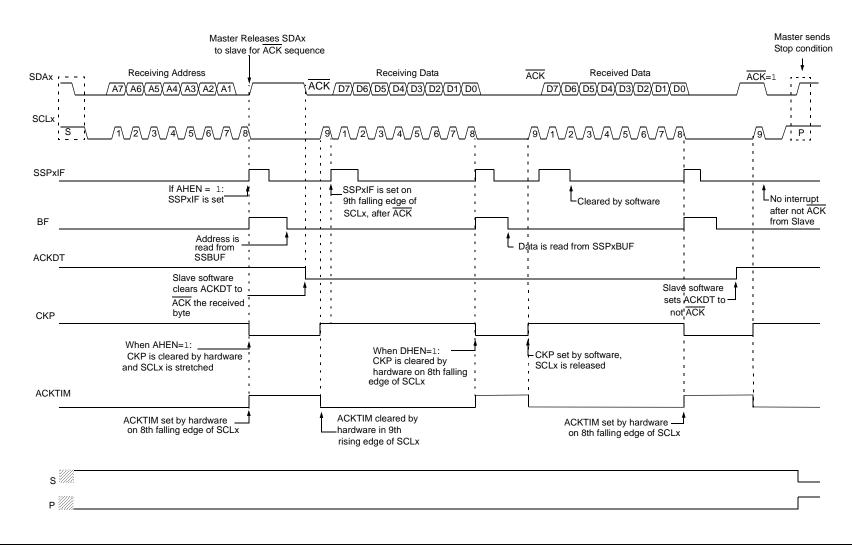

| FC4h    | ADRESH                |         |                                           |                              | A/D Result,      | High Byte               |                |                              |         | xxxx xxxx                   |

| FC3h    | ADRESL                |         |                                           |                              | A/D Result,      | Low Byte                |                |                              |         | xxxx xxxx                   |

| FC2h    | ADCON0                | _       |                                           |                              | CHS<4:0>         |                         |                | GO/DONE                      | ADON    | 00 0000                     |

| FC1h    | ADCON1                | TRIGSEL | _                                         | _                            | _                | PVCF                    | G<1:0>         | NVCF                         | G<1:0>  | 0 0000                      |

| FC0h    | ADCON2                | ADFM    | _                                         |                              | ACQT<2:0>        |                         |                | ADCS<2:0>                    |         | 0-00 0000                   |

| FBFh    | CCPR1H                |         | Capture/Compare/PWM Register 1, High Byte |                              |                  |                         |                |                              |         | xxxx xxxx                   |

| FBEh    | CCPR1L                |         |                                           | Captur                       | e/Compare/PV     | VM Register 1,          | Low Byte       |                              |         | xxxx xxxx                   |

| FBDh    | CCP1CON               | P1M<    | <1:0>                                     | DC1E                         | 3<1:0>           |                         | CCP1N          | 1<3:0>                       |         | 0000 0000                   |

| FBCh    | TMR2                  |         |                                           |                              | Timer2 F         | Register                |                |                              |         | 0000 0000                   |

| FBBh    | PR2                   |         |                                           |                              | Timer2 Peri      | od Register             |                |                              |         | 1111 1111                   |

| FBAh    | T2CON                 | _       |                                           | T2OUT                        | PS<3:0>          |                         | TMR2ON         | T2CKP                        | 'S<1:0> | -000 0000                   |

| FB9h    | PSTR1CON              | _       | _                                         | _                            | STR1SYNC         | STR1D                   | STR1C          | STR1B                        | STR1A   | 0 0001                      |

| FB8h    | BAUDCON1              | ABDOVF  | RCIDL                                     | DTRXP                        | CKTXP            | BRG16                   | _              | WUE                          | ABDEN   | 0100 0-00                   |

| FB7h    | PWM1CON               | P1RSEN  |                                           |                              |                  | P1DC<6:0>               |                |                              |         | 0000 0000                   |

| FB6h    | ECCP1AS               | CCP1ASE |                                           | CCP1AS<2:0                   | >                | PSS1A                   | .C<1:0>        | PSS1B                        | D<1:0>  | 0000 0000                   |

| FB4h    | T3GCON                | TMR3GE  | T3GPOL                                    | T3GTM                        | T3GSPM           | T <u>3GGO</u> /<br>DONE | T3GVAL         | T3GS                         | S<1:0>  | 00x0 0x00                   |

| FB3h    | TMR3H                 |         | Holding R                                 | egister for the              | Most Significa   | ant Byte of the         | 16-bit TMR3 R  | egister                      |         | xxxx xxxx                   |

| FB2h    | TMR3L                 |         |                                           | Least Signif                 | icant Byte of th | ne 16-bit TMR3          | Register       |                              |         | xxxx xxxx                   |

| FB1h    | T3CON                 | TMR3C   | S<1:0>                                    | T3CKF                        | PS<1:0>          | T3SOSCEN                | T3SYNC         | T3RD16                       | TMR3ON  | 0000 0000                   |

| FB0h    | SPBRGH1               |         |                                           | EUSAR                        | T1 Baud Rate     | Generator, Hig          | h Byte         |                              |         | 0000 0000                   |

| FAFh    | SPBRG1                |         |                                           | EUSAR                        | T1 Baud Rate     | Generator, Lov          | w Byte         |                              |         | 0000 0000                   |

| FAEh    | RCREG1                |         |                                           |                              | T1 Receive Re    |                         |                |                              |         | 0000 0000                   |

| FADh    | TXREG1                |         |                                           | EUSAR                        | T1 Transmit R    | egister                 |                |                              |         | 0000 0000                   |

| FACh    | TXSTA1                | CSRC    | TX9                                       | TXEN                         | SYNC             | SENDB                   | BRGH           | TRMT                         | TX9D    | 0000 0010                   |

| FABh    | RCSTA1                | SPEN    | RX9                                       | SREN                         | CREN             | ADDEN                   | FERR           | OERR                         | RX9D    | 0000 000x                   |

| FAAh    | EEADRH <sup>(5)</sup> | _       | _                                         | _                            | _                | _                       | _              |                              | R<9:8>  | 00                          |

| FA9h    | EEADR                 |         |                                           | 1                            | EEAD             | R<7:0>                  |                |                              |         | 0000 0000                   |

| FA8h    | EEDATA                |         |                                           |                              | EEPROM Da        |                         |                |                              |         | 0000 0000                   |

| FA7h    | EECON2                |         |                                           | EEPROM Co                    |                  | 2 (not a physic         | cal register)  |                              |         | 00                          |

| FA6h    | EECON1                | EEPGD   | CFGS                                      | _                            | FREE             | WRERR                   | WREN           | WR                           | RD      | xx-0 x000                   |

| FA5h    | IPR3                  | SSP2IP  | BCL2IP                                    | RC2IP                        | TX2IP            | CTMUIP                  | TMR5GIP        | TMR3GIP                      | TMR1GIP | 0000 0000                   |

| FA4h    | PIR3                  | SSP2IF  | BCL2IF                                    | RC2IF                        | TX2IF            | CTMUIF                  | TMR5GIF        | TMR3GIF                      | TMR1GIF | 0000 0000                   |

| FA3h    | PIE3                  | SSP2IE  | BCL2IE                                    | RC2IE                        | TX2IE            | CTMUIE                  | TMR5GIE        | TMR3GIE                      | TMR1GIE | 0000 0000                   |

#### **TABLE 5-2:** REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES (CONTINUED)

Legend:  $\mathbf{x}$  = unknown,  $\mathbf{u}$  = unchanged, — = unimplemented,  $\mathbf{q}$  = value depends on condition

PIC18(L)F4XK22 devices only. Note 1:

PIC18(L)F2XK22 devices only. 2:

PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only. PIC18(L)F26K22 and PIC18(L)F46K22 devices only. 3:

4:

DS40001412G-page 80

| U-0           | U-0                                                                  | U-0                                                 | U-0                           | U-0             | R/W-0                            | R/W-0           | R/W-0  |

|---------------|----------------------------------------------------------------------|-----------------------------------------------------|-------------------------------|-----------------|----------------------------------|-----------------|--------|

| —             | _                                                                    |                                                     | —                             | —               | CCP5IF                           | CCP4IF          | CCP3IF |

| bit 7         |                                                                      |                                                     |                               |                 |                                  |                 | bit (  |

|               |                                                                      |                                                     |                               |                 |                                  |                 |        |

| Legend:       |                                                                      |                                                     | L :4                          |                 |                                  | (O)             |        |

| R = Readabl   |                                                                      | W = Writable                                        |                               | -               | mented bit, read                 |                 |        |

| -n = Value at | PUR                                                                  | '1' = Bit is se                                     | [                             | '0' = Bit is cl | eared                            | x = Bit is unkı | lown   |

| bit 7-3       | Unimplemer                                                           | nted: Read as                                       | 0'                            |                 |                                  |                 |        |

| bit 2         | CCP5IF: CC                                                           | P5 Interrupt Fla                                    | ag bits                       |                 |                                  |                 |        |

|               |                                                                      | <u>le:</u><br>register capture<br>t register captur |                               | ist be cleared  | in software)                     |                 |        |

|               |                                                                      | register compar<br>R register compa                 |                               |                 | cleared in softw                 | are)            |        |

| bit 1         | CCP4IF: CC                                                           | P4 Interrupt Fla                                    | ag bits                       |                 |                                  |                 |        |

|               |                                                                      | <u>le:</u><br>register capture<br>t register captur |                               | ist be cleared  | in software)                     |                 |        |

|               | 0 = No TMR<br><u>PWM mode:</u>                                       | register compar<br>register compa                   |                               |                 | cleared in softw                 | are)            |        |

| hit 0         | Unused in P                                                          |                                                     | log hito                      |                 |                                  |                 |        |

| bit 0         | <u>Capture mod</u><br>1 = A TMR r<br>0 = No TMR<br><u>Compare mo</u> | register capture<br>register captur<br>ode:         | e occurred (mu<br>re occurred |                 | in software)<br>cleared in softw | are)            |        |

|               | 0 = No TMR<br><u>PWM mode:</u><br>Unused in P\                       |                                                     | are match occ                 | urred           |                                  |                 |        |

#### REGISTER 9-7: PIR4: PERIPHERAL INTERRUPT (FLAG) REGISTER 4

#### 10.4 PORTC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., disable the output driver). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 10-8). The pins have Schmitt Trigger input buffers.

Some of these pin functions can be relocated to alternate pins using the Control fuse bits in CONFIG3H. RC0 is the default pin for T3CKI. Clearing the T3CMX bit moves the pin function to RB5. RC1 is the default pin for the CCP2 peripheral pin. Clearing the CCP2MX bit moves the pin function to the RB3 pin.

Two other pin functions, P2B and CCP3, can be relocated from their default pins to PORTC pins by clearing the control fuses in CONFIG3H. Clearing P2BMX and CCP3MX moves the pin functions to RC0 and RC6<sup>(1)</sup>/RE0<sup>(2)</sup>, respectively.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. The EUSART and MSSP peripherals override the TRIS bit to make a pin an output or an input, depending on the peripheral configuration. Refer to the corresponding peripheral section for additional information.

Note: On a Power-on Reset, these pins are configured as analog inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

#### EXAMPLE 10-3: INITIALIZING PORTC

| MOVLB<br>CLRF | 0xF<br>PORTC | ; Set BSR for banked SFRs<br>; Initialize PORTC by |

|---------------|--------------|----------------------------------------------------|

| СШКГ          | IONIC        | ; clearing output                                  |

|               |              | ; data latches                                     |

| CLRF          | LATC         | ; Alternate method                                 |

|               |              | ; to clear output                                  |

|               |              | ; data latches                                     |

| MOVLW         | OCFh         | ; Value used to                                    |

|               |              | ; initialize data                                  |

|               |              | ; direction                                        |

| MOVWF         | TRISC        | ; Set RC<3:0> as inputs                            |

|               |              | ; RC<5:4> as outputs                               |

|               |              | ; RC<7:6> as inputs                                |

| MOVLW         | 30h          | ; Value used to                                    |

|               |              | ; enable digital inputs                            |

| MOVWF         | ANSELC       | ; RC<3:2> dig input enable                         |

|               |              | ; No ANSEL bits for RC<1:0>                        |

|               |              | ; RC<7:6> dig input enable                         |

|               |              |                                                    |

#### 10.4.1 PORTC OUTPUT PRIORITY

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the higher priority. Table 10-4 lists the PORTC pin functions from the highest to the lowest priority.

Analog input functions, such as ADC, comparator and SR latch inputs, are not shown in the priority lists.

These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below.

#### 10.5 PORTD Registers

| Note: | PORTD is only available on 40-pin and |

|-------|---------------------------------------|

|       | 44-pin devices.                       |

PORTD is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., disable the output driver). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

All of the PORTD pins are multiplexed with analog and digital peripheral modules. See Table 10-11.

**Note:** On a Power-on Reset, these pins are configured as analog inputs.

EXAMPLE 10-4: INITIALIZING PORTD

| MOVLB<br>CLRF | 0xF<br>PORTD | ; Set BSR for banked SFRs<br>; Initialize PORTD by<br>; clearing output |

|---------------|--------------|-------------------------------------------------------------------------|

|               |              | ; data latches                                                          |

| CLRF          | LATD         | ; Alternate method                                                      |

|               |              | ; to clear output                                                       |

|               |              | ; data latches                                                          |

| MOVLW         | OCFh         | ; Value used to                                                         |

|               |              | ; initialize data                                                       |

|               |              | ; direction                                                             |

| MOVWF         | TRISD        | ; Set RD<3:0> as inputs                                                 |

|               |              | ; RD<5:4> as outputs                                                    |

|               |              | ; RD<7:6> as inputs                                                     |

| MOVLW         | 30h          | ; Value used to                                                         |

|               |              | ; enable digital inputs                                                 |

| MOVWF         | ANSELD       | ; RD<3:0> dig input enable                                              |

|               |              | ; RC<7:6> dig input enable                                              |

|               |              |                                                                         |

#### 10.5.1 PORTD OUTPUT PRIORITY

Each PORTD pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the higher priority. Table 10-4 lists the PORTD pin functions from the highest to the lowest priority.

Analog input functions, such as ADC, comparator and SR latch inputs, are not shown in the priority lists.

These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below.

| REGISTER I       | U-Z. FURI   | C. FURIERI        | EGISTER     |                    |                         |                         |                         |

|------------------|-------------|-------------------|-------------|--------------------|-------------------------|-------------------------|-------------------------|

| U-0              | U-0         | U-0               | U-0         | R/W-u/x            | R/W-u/x                 | R/W-u/x                 | R/W-u/x                 |

| _                | —           | —                 | —           | RE3 <sup>(1)</sup> | RE2 <sup>(2), (3)</sup> | RE1 <sup>(2), (3)</sup> | RE0 <sup>(2), (3)</sup> |

| bit 7            |             |                   |             |                    |                         |                         | bit C                   |

|                  |             |                   |             |                    |                         |                         |                         |

| Legend:          |             |                   |             |                    |                         |                         |                         |

| R = Readable     | bit         | W = Writable      | bit         | U = Unimpler       | mented bit, read        | d as '0'                |                         |

| '1' = Bit is set |             | '0' = Bit is clea | ared        | x = Bit is unk     | nown                    |                         |                         |

| -n/n = Value at  | POR and BOR | R/Value at all o  | ther Resets |                    |                         |                         |                         |

|                  |             |                   |             |                    |                         |                         |                         |

|                  |             |                   |             |                    |                         |                         |                         |

#### REGISTER 10-2: PORTE: PORTE REGISTER

bit 3 **RE3:** PORTE Input bit value<sup>(1)</sup>

bit 2-0 **RE<2:0>:** PORTE I/O bit values<sup>(2), (3)</sup>

**Note 1:** Port is available as input only when MCLRE = 0.

- 2: Writes to PORTx are written to corresponding LATx register. Reads from PORTx register is return of I/O pin values.

- 3: Available on PIC18(L)F4XK22 devices.

#### REGISTER 10-3: ANSELA – PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| —     | —   | ANSA5 | —   | ANSA3 | ANSA2 | ANSA1 | ANSA0 |

| bit 7 |     |       |     |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                   |

|---------|----------------------------------------------------------------------------------------------|

| bit 5   | ANSA5: RA5 Analog Select bit                                                                 |

|         | <ul><li>1 = Digital input buffer disabled</li><li>0 = Digital input buffer enabled</li></ul> |

| bit 4   | Unimplemented: Read as '0'                                                                   |

| bit 3-0 | ANSA<3:0>: RA<3:0> Analog Select bit                                                         |

|         | 1 = Digital input buffer disabled                                                            |

0 = Digital input buffer enabled

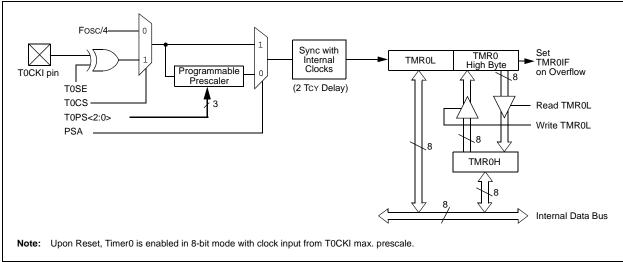

#### FIGURE 11-2: TIMER0 BLOCK DIAGRAM (16-BIT MODE)

#### 11.4 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS<2:0> bits of the T0CON register which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When the prescaler is assigned, prescale values from 1:2 through 1:256 in integer power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

#### 11.4.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

#### 11.5 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit of the INTCON register. Before re-enabling the interrupt, the TMR0IF bit must be cleared by software in the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name    | Bit 7                     | Bit 6     | Bit 5   | Bit 4        | Bit 3        | Bit 2  | Bit 1         | Bit 0  | Reset<br>Values<br>on page |

|---------|---------------------------|-----------|---------|--------------|--------------|--------|---------------|--------|----------------------------|

| INTCON  | GIE/GIEH                  | PEIE/GIEL | TMR0IE  | INT0IE       | RBIE         | TMR0IF | <b>INT0IF</b> | RBIF   | 109                        |

| INTCON2 | RBPU                      | INTEDG0   | INTEDG1 | INTEDG2      | —            | TMR0IP |               | RBIP   | 110                        |

| T0CON   | TMR0ON                    | T08BIT    | TOCS    | T0SE         | PSA          |        | T0PS<2:0>     |        | 154                        |

| TMR0H   |                           |           | Tin     | ner0 Registe | er, High Byt | е      |               |        | —                          |

| TMR0L   | Timer0 Register, Low Byte |           |         |              |              |        |               | —      |                            |

| TRISA   | TRISA7                    | TRISA6    | TRISA5  | TRISA4       | TRISA3       | TRISA2 | TRISA1        | TRISA0 | 151                        |

#### TABLE 11-1: REGISTERS ASSOCIATED WITH TIMER0

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by Timer0.

#### 15.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPxOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 15-5.

An MSSPx interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCLx will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 15.2.3 "SPI Master Mode"** for more detail.

#### 15.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSPx module configured as an  $I^2C$  slave in 7-bit Addressing mode. All decisions made by hardware or software and their effect on reception. Figure 15-14 and Figure 15-5 are used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $\mathsf{I}^2\mathsf{C}$  communication.

- 1. Start bit detected.

- S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCLx line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes Idle.

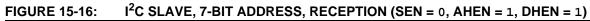

#### 15.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the 8th falling edge of SCLx. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 15-16 displays a module using both address and data holding. Figure 15-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- 1. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the 8th falling edge of SCLx.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPx-CON3 register to <u>determine</u> if the SSPxIF was after or before the ACK.

- 5. Slave reads the address value from SSPxBUF, clearing the BF flag.

- Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF

**Note:** SSPxIF is still set after the 9th falling edge of SCLx even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPxIF not set.

- 11. SSPxIF set and CKP cleared after 8th falling edge of SCLx for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

#### 16.5.1.6 Synchronous Master Reception

Data is received at the RXx/DTx pin. The RXx/DTx pin output driver must be disabled by setting the corresponding TRIS bits when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTAx register) or the Continuous Receive Enable bit (CREN of the RCSTAx register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RXx/DTx pin on the trailing edge of the TXx/CKx clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCxIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREGx. The RCxIF bit remains set as long as there are un-read characters in the receive FIFO.

#### 16.5.1.7 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TXx/CKx line. The TXx/CKx pin output driver must be disabled by setting the associated TRIS bit when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 16.5.1.8 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREGx is read to access the FIFO. When this happens the OERR bit of the RCSTAx register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREGx.

If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTAx register or by clearing the SPEN bit which resets the EUSART.

#### 16.5.1.9 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTAx register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTAx register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREGx.

### 16.5.1.10 Synchronous Master Reception Setup:

- 1. Initialize the SPBRGHx, SPBRGx register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC. Disable RXx/DTx and TXx/CKx output drivers by setting the corresponding TRIS bits.

- 4. Ensure bits CREN and SREN are clear.

- If using interrupts, set the GIE/GIEH and PEIE/ GIEL bits of the INTCON register and set RCxIE.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RCxIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCxIE was set.

- 9. Read the RCSTAx register to get the ninth bit (if enabled) and determine if any error occurred during reception.