Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 30x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

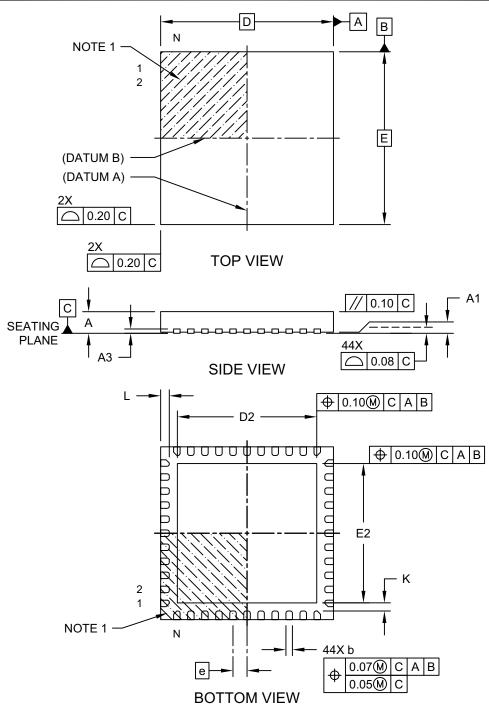

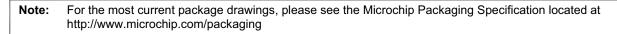

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f44k22-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 7.6 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to Section 24.0 "Special Features of the CPU" for additional information.

### 7.7 Protection Against Spurious Write

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT). The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

### 7.8 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM without exceeding the total number of write cycles to a single byte. Refer to the Data EEPROM Memory parameters in **Section 27.0** "**Electrical Specifications**" for write cycle limits. If this is the case, then an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 7-3.

Note: If data EEPROM is only used to store constants and/or data that changes rarely, an array refresh is likely not required. See specification.

| CLRF   | EEADR                                                                                                         | ; Start at address 0                                                                                                                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLRF   | EEADRH                                                                                                        | ; if > 256 bytes EEPROM                                                                                                                                                                                                   |

| BCF    | EECON1, CFGS                                                                                                  | ; Set for memory                                                                                                                                                                                                          |

| BCF    | EECON1, EEPGD                                                                                                 | ; Set for Data EEPROM                                                                                                                                                                                                     |

| BCF    | INTCON, GIE                                                                                                   | ; Disable interrupts                                                                                                                                                                                                      |

| BSF    | EECON1, WREN                                                                                                  | ; Enable writes                                                                                                                                                                                                           |

|        |                                                                                                               | ; Loop to refresh array                                                                                                                                                                                                   |

| BSF    | EECON1, RD                                                                                                    | ; Read current address                                                                                                                                                                                                    |

| MOVLW  | 55h                                                                                                           | ;                                                                                                                                                                                                                         |

| MOVWF  | EECON2                                                                                                        | ; Write 55h                                                                                                                                                                                                               |

| MOVLW  | 0AAh                                                                                                          | ;                                                                                                                                                                                                                         |

| MOVWF  | EECON2                                                                                                        | ; Write OAAh                                                                                                                                                                                                              |

| BSF    | EECON1, WR                                                                                                    | ; Set WR bit to begin write                                                                                                                                                                                               |

| BTFSC  | EECON1, WR                                                                                                    | ; Wait for write to complete                                                                                                                                                                                              |

| BRA    | \$-2                                                                                                          |                                                                                                                                                                                                                           |

| INCFSZ | EEADR, F                                                                                                      | ; Increment address                                                                                                                                                                                                       |

| BRA    | LOOP                                                                                                          | ; Not zero, do it again                                                                                                                                                                                                   |

| INCFSZ | EEADRH, F                                                                                                     | ; if > 256 bytes, Increment address                                                                                                                                                                                       |

| BRA    | LOOP                                                                                                          | ; if > 256 bytes, Not zero, do it again                                                                                                                                                                                   |

| DOF    | FECON1 MDEN                                                                                                   | ; Disable writes                                                                                                                                                                                                          |

|        | ,                                                                                                             |                                                                                                                                                                                                                           |

| BSF    | INTCON, GIE                                                                                                   | ; Enable interrupts                                                                                                                                                                                                       |

|        | CLRF<br>BCF<br>BCF<br>BSF<br>BSF<br>MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>BTFSC<br>BRA<br>INCFSZ<br>BRA<br>INCFSZ | CLRFEEADRHBCFEECON1, CFGSBCFEECON1, EEPGDBCFINTCON, GIEBSFEECON1, WRENBSFEECON1, RDMOVLW55hMOVWFEECON2MOVLW0AAhMOVWFEECON1, WRBSFEECON1, WRBSFEECON1, WRBRA\$-2INCFSZEEADR, FBRALOOPINCFSZEEADRH, FBRALOOPBCFEECON1, WREN |

### EXAMPLE 7-3: DATA EEPROM REFRESH ROUTINE

### 9.0 INTERRUPTS

The PIC18(L)F2X/4XK22 devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high or low priority level (INT0 does not have a priority bit, it is always a high priority). The high priority interrupt vector is at 0008h and the low priority interrupt vector is at 0018h. A high priority interrupt event will interrupt a low priority interrupt that may be in progress.

There are 19 registers used to control interrupt operation.

These registers are:

- INTCON, INTCON2, INTCON3

- PIR1, PIR2, PIR3, PIR4, PIR5

- PIE1, PIE2, PIE3, PIE4, PIE5

- IPR1, IPR2, IPR3, IPR4, IPR5

- RCON

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** to select high priority or low priority

### 9.1 Mid-Range Compatibility

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> microcontroller mid-range devices. In Compatibility mode, the interrupt priority bits of the IPRx registers have no effect. The PEIE/GIEL bit of the INTCON register is the global interrupt enable for the peripherals. The PEIE/GIEL bit disables only the peripheral interrupt sources and enables the peripheral interrupt sources when the GIE/GIEH bit is also set. The GIE/GIEH bit of the INTCON register is the global interrupt sources and enables all non-peripheral interrupt sources and disables all interrupt sources, including the peripherals. All interrupts branch to address 0008h in Compatibility mode.

### 9.2 Interrupt Priority

The interrupt priority feature is enabled by setting the IPEN bit of the RCON register. When interrupt priority is enabled the GIE/GIEH and PEIE/GIEL global interrupt enable bits of Compatibility mode are replaced by the GIEH high priority, and GIEL low priority, global interrupt enables. When set, the GIEH bit of the INTCON register enables all interrupts that have their associated IPRx register or INTCONx register priority bit set (high priority). When clear, the GIEH bit disables all interrupt sources including those selected as low priority. When clear, the GIEL bit of the INTCON register disables only the interrupts that have their associated priority bit cleared (low priority). When set, the GIEL bit enables the low priority sources when the GIEH bit is also set.

When the interrupt flag, enable bit and appropriate Global Interrupt Enable (GIE) bit are all set, the interrupt will vector immediately to address 0008h for high priority, or 0018h for low priority, depending on level of the interrupting source's priority bit. Individual interrupts can be disabled through their corresponding interrupt enable bits.

### 9.3 Interrupt Response

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. The GIE/GIEH bit is the Global Interrupt Enable when the IPEN bit is cleared. When the IPEN bit is set, enabling interrupt priority levels, the GIEH bit is the high priority global interrupt enable and the GIEL bit is the low priority Global Interrupt Enable. High priority interrupt sources can interrupt a low priority interrupt. Low priority interrupts are not processed while high priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits in the INTCONx and PIRx registers. The interrupt flag bits must be cleared by software before re-enabling interrupts to avoid repeating the same interrupt.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE/GIEH bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the PORTB interrupt-on-change, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one-cycle or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bits or the Global Interrupt Enable bit.

| R/W-1           | R/W-1         | R/W-1                                         | R/W-1            | U-0              | R/W-1             | U-0            | R/W-1          |  |  |

|-----------------|---------------|-----------------------------------------------|------------------|------------------|-------------------|----------------|----------------|--|--|

| RBPU            | INTEDG0       | INTEDG1                                       | INTEDG2          | —                | TMR0IP            | _              | RBIP           |  |  |

| bit 7           | •<br>•        |                                               |                  |                  |                   |                | bit            |  |  |

|                 |               |                                               |                  |                  |                   |                |                |  |  |

| Legend:         |               |                                               |                  |                  |                   |                |                |  |  |

| R = Readable    |               | W = Writable                                  |                  | -                | mented bit, read  |                |                |  |  |

| -n = Value at F | POR           | '1' = Bit is set                              |                  | '0' = Bit is cle | eared             | x = Bit is unk | nown           |  |  |

|                 |               |                                               |                  |                  |                   |                |                |  |  |

| bit 7           |               | TB Pull-up Ena                                |                  |                  |                   |                |                |  |  |

|                 |               | FB pull-ups are                               |                  | that the nin i   | s an input and th | e correspondi  | na WPLIB bit i |  |  |

|                 | set.          |                                               |                  |                  | s an input and t  | ie concoponali |                |  |  |

| bit 6           | INTEDG0: E>   | kternal Interrup                              | t 0 Edge Sele    | ct bit           |                   |                |                |  |  |

|                 |               | on rising edge                                |                  |                  |                   |                |                |  |  |

|                 | -             | on falling edge                               |                  |                  |                   |                |                |  |  |

| bit 5           |               | INTEDG1: External Interrupt 1 Edge Select bit |                  |                  |                   |                |                |  |  |

|                 |               | on rising edge<br>on falling edge             |                  |                  |                   |                |                |  |  |

| bit 4           | •             | kternal Interrup                              |                  | ot hit           |                   |                |                |  |  |

| DIL 4           |               | on rising edge                                | t z Euge Sele    |                  |                   |                |                |  |  |

|                 |               | on falling edge                               | )                |                  |                   |                |                |  |  |

| bit 3           | Unimplemen    | ted: Read as '                                | 0'               |                  |                   |                |                |  |  |

| bit 2           | TMROIP: TMI   | R0 Overflow In                                | terrupt Priority | / bit            |                   |                |                |  |  |

|                 | 1 = High prio | ority                                         |                  |                  |                   |                |                |  |  |

|                 | 0 = Low prior | rity                                          |                  |                  |                   |                |                |  |  |

| bit 1           | Unimplemen    | ted: Read as '                                | 0'               |                  |                   |                |                |  |  |

| bit 0           | RBIP: RB Po   | rt Change Inte                                | rrupt Priority b | it               |                   |                |                |  |  |

|                 | 1 = High prio | 2                                             |                  |                  |                   |                |                |  |  |

|                 | 0 = Low prior | P1+1/                                         |                  |                  |                   |                |                |  |  |

### REGISTER 9-2: INTCON2: INTERRUPT CONTROL 2 REGISTER

| Note: | Interrupt flag bits are set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs, regardless of the state of  |

|       | its corresponding enable bit or the global    |

|       | enable bit. User software should ensure       |

|       | the appropriate interrupt flag bits are clear |

|       | prior to enabling an interrupt. This feature  |

|       | allows for software polling.                  |

### 15.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDAx pin after the falling edge of SCLx is asserted. SCLx is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCLx is released high. When the SCLx pin is released high, it is held that way for TBRG. The data on the SDAx pin must remain stable for that duration and some hold time after the next falling edge of SCLx. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDAx. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of  $\overline{ACK}$  is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCLx low and SDAx unchanged (Figure 15-28).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCLx until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDAx pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDAx pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCLx low and allowing SDAx to float.

### 15.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all 8 bits are shifted out.

### 15.6.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

### 15.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

15.6.6.4 Typical Transmit Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSPx module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- 6. Address is shifted out the SDAx pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 7. The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDAx pin until all eight bits are transmitted.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPx-CON2 register. Interrupt is generated once the Stop/Restart condition is complete.

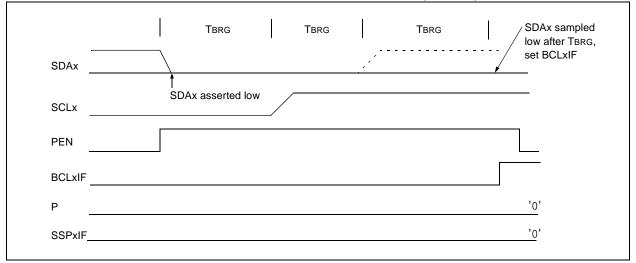

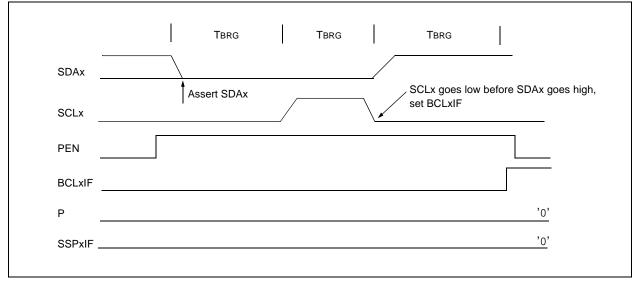

### 15.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out (Case 1).

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high (Case 2).

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to zero. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 15-38). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 15-39).

### FIGURE 15-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

### FIGURE 15-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

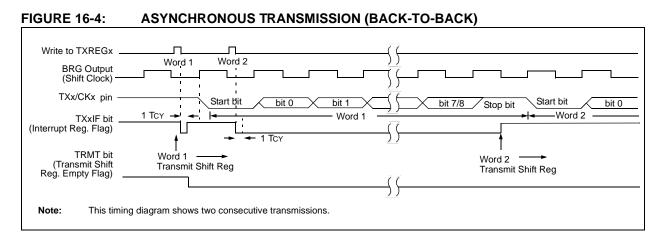

### TABLE 16-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name     | Bit 7                                  | Bit 6     | Bit 5  | Bit 4       | Bit 3        | Bit 2     | Bit 1   | Bit 0   | Reset<br>Values<br>on<br>Page |

|----------|----------------------------------------|-----------|--------|-------------|--------------|-----------|---------|---------|-------------------------------|

| BAUDCON1 | ABDOVF                                 | RCIDL     | DTRXP  | CKTXP       | BRG16        | —         | WUE     | ABDEN   | 271                           |

| BAUDCON2 | ABDOVF                                 | RCIDL     | DTRXP  | CKTXP       | BRG16        | —         | WUE     | ABDEN   | 271                           |

| INTCON   | GIE/GIEH                               | PEIE/GIEL | TMR0IE | INT0IE      | RBIE         | TMR0IF    | INT0IF  | RBIF    | 109                           |

| IPR1     | —                                      | ADIP      | RC1IP  | TX1IP       | SSP1IP       | CCP1IP    | TMR2IP  | TMR1IP  | 121                           |

| IPR3     | SSP2IP                                 | BCL2IP    | RC2IP  | TX2IP       | CTMUIP       | TMR5GIP   | TMR3GIP | TMR1GIP | 123                           |

| PIE1     | —                                      | ADIE      | RC1IE  | TX1IE       | SSP1IE       | CCP1IE    | TMR2IE  | TMR1IE  | 117                           |

| PIE3     | SSP2IE                                 | BCL2IE    | RC2IE  | TX2IE       | CTMUIE       | TMR5GIE   | TMR3GIE | TMR1GIE | 119                           |

| PIR1     | _                                      | ADIF      | RC1IF  | TX1IF       | SSP1IF       | CCP1IF    | TMR2IF  | TMR1IF  | 112                           |

| PIR3     | SSP2IF                                 | BCL2IF    | RC2IF  | TX2IF       | CTMUIF       | TMR5GIF   | TMR3GIF | TMR1GIF | 114                           |

| PMD0     | UART2MD                                | UART1MD   | TMR6MD | TMR5MD      | TMR4MD       | TMR3MD    | TMR2MD  | TMR1MD  | 52                            |

| RCSTA1   | SPEN                                   | RX9       | SREN   | CREN        | ADDEN        | FERR      | OERR    | RX9D    | 270                           |

| RCSTA2   | SPEN                                   | RX9       | SREN   | CREN        | ADDEN        | FERR      | OERR    | RX9D    | 270                           |

| SPBRG1   |                                        |           | EUSART | 1 Baud Rate | Generator,   | _ow Byte  |         |         | —                             |

| SPBRGH1  |                                        |           | EUSART | Baud Rate   | Generator, I | ligh Byte |         |         | —                             |

| SPBRG2   | EUSART2 Baud Rate Generator, Low Byte  |           |        |             |              |           |         | —       |                               |

| SPBRGH2  | EUSART2 Baud Rate Generator, High Byte |           |        |             |              |           |         | —       |                               |

| TXREG1   | EUSART1 Transmit Register              |           |        |             |              |           |         |         | —                             |

| TXSTA1   | CSRC                                   | TX9       | TXEN   | SYNC        | SENDB        | BRGH      | TRMT    | TX9D    | 269                           |

| TXREG2   |                                        |           | EL     | JSART2 Tra  | nsmit Regist | er        |         |         | —                             |

| TXSTA2   | CSRC                                   | TX9       | TXEN   | SYNC        | SENDB        | BRGH      | TRMT    | TX9D    | 269                           |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for asynchronous transmission.

### 16.4.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCONx register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGHx:SPBRGx register pair. After the ABDOVF has been set, the counter continues to count until the fifth rising edge is detected on the RXx/DTx pin. Upon detecting the fifth RXx/DTx edge, the hardware will set the RCxIF interrupt flag and clear the ABDEN bit of the BAUDCONx register. The RCxIF flag can be subsequently cleared by reading the RCREGx. The ABDOVF flag can be cleared by software directly.

To terminate the auto-baud process before the RCxIF flag is set, clear the ABDEN bit then clear the ABDOVF bit. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

### 16.4.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RXx/DTx line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCONx register. Once set, the normal receive sequence on RXx/DTx is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RXx/DTx line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCxIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 16-7), and asynchronously if the device is in Sleep mode (Figure 16-8). The interrupt condition is cleared by reading the RCREGx register.

The WUE bit is automatically cleared by the low-to-high transition on the RXx line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

### 16.4.3.1 Special Considerations

### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be 10 or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

### WUE Bit

The wake-up event causes a receive interrupt by setting the RCxIF bit. The WUE bit is cleared by hardware by a rising edge on RXx/DTx. The interrupt condition is then cleared by software by reading the RCREGx register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

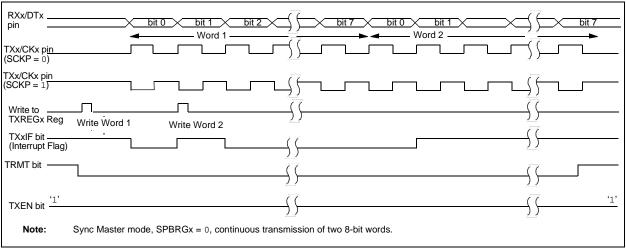

- 16.5.1.5 Synchronous Master Transmission Setup:

- 1. Initialize the SPBRGHx, SPBRGx register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 16.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- Enable the synchronous master serial port by 3. setting bits SYNC, SPEN and CSRC. Set the TRIS bits corresponding to the RXx/DTx and TXx/CKx I/O pins.

FIGURE 16-10:

- 4. Disable Receive mode by clearing bits SREN and CREN.

- Enable Transmit mode by setting the TXEN bit. 5.

- 6. If 9-bit transmission is desired, set the TX9 bit.

- 7. If interrupts are desired, set the TXxIE, GIE/ GIEH and PEIE/GIEL interrupt enable bits.

- If 9-bit transmission is selected, the ninth bit 8. should be loaded in the TX9D bit.

- Start transmission by loading data to the 9. TXREGx register.

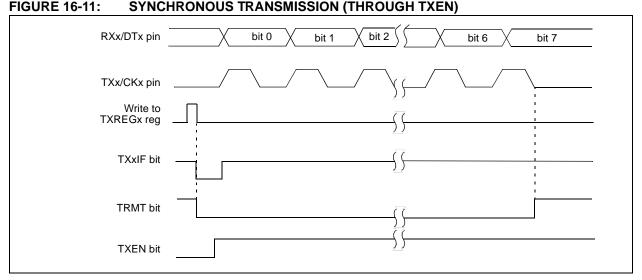

### **FIGURE 16-11:**

SYNCHRONOUS TRANSMISSION

### 16.5.1.6 Synchronous Master Reception

Data is received at the RXx/DTx pin. The RXx/DTx pin output driver must be disabled by setting the corresponding TRIS bits when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTAx register) or the Continuous Receive Enable bit (CREN of the RCSTAx register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RXx/DTx pin on the trailing edge of the TXx/CKx clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCxIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREGx. The RCxIF bit remains set as long as there are un-read characters in the receive FIFO.

### 16.5.1.7 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TXx/CKx line. The TXx/CKx pin output driver must be disabled by setting the associated TRIS bit when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

### 16.5.1.8 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREGx is read to access the FIFO. When this happens the OERR bit of the RCSTAx register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREGx.

If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTAx register or by clearing the SPEN bit which resets the EUSART.

### 16.5.1.9 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTAx register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTAx register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREGx.

## 16.5.1.10 Synchronous Master Reception Setup:

- 1. Initialize the SPBRGHx, SPBRGx register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC. Disable RXx/DTx and TXx/CKx output drivers by setting the corresponding TRIS bits.

- 4. Ensure bits CREN and SREN are clear.

- If using interrupts, set the GIE/GIEH and PEIE/ GIEL bits of the INTCON register and set RCxIE.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RCxIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCxIE was set.

- 9. Read the RCSTAx register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREGx register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTAx register or by clearing the SPEN bit which resets the EUSART.

| R/W-0        | R/W-0                                               | R/W-0                                                                                                     | R/W-0                                        | R/W-0                             | R/W-0           | R/W-0           | R/W-0  |

|--------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------|-----------------|-----------------|--------|

|              |                                                     | ITRIM                                                                                                     | <5:0>                                        |                                   |                 | IRNG            | i<1:0> |

| bit 7        |                                                     |                                                                                                           |                                              |                                   |                 |                 | bit (  |

| Legend:      |                                                     |                                                                                                           |                                              |                                   |                 |                 |        |

| R = Readal   | ble bit                                             | W = Writable I                                                                                            | bit                                          | U = Unimplen                      | nented bit, rea | d as '0'        |        |

| -n = Value a | at POR                                              | '1' = Bit is set                                                                                          |                                              | '0' = Bit is clea                 | ared            | x = Bit is unkr | nown   |

| bit 7-2      | 011111 = M<br>011110                                | Current Source Maximum positive Minimum positive Nominal current o Minimum negative                       | change from<br>change from<br>utput specifie | nominal current<br>d by IRNG<1:0> |                 |                 |        |

| bit 1-0      | IRNG<1:0><br>11 = 100 ×<br>10 = 10 × E<br>01 = Base | Maximum negative<br>Current Source<br>Base current<br>Base current<br>current level<br>nt source disabled | Range Selec                                  |                                   |                 |                 |        |

### REGISTER 19-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

| Name     | Bit 7      | Bit 6  | Bit 5    | Bit 4   | Bit 3  | Bit 2    | Bit 1    | Bit 0    | Reset<br>Values<br>on Page |

|----------|------------|--------|----------|---------|--------|----------|----------|----------|----------------------------|

| CTMUCONH | CTMUEN     | _      | CTMUSIDL | TGEN    | EDGEN  | EDGSEQEN | IDISSEN  | CTTRIG   | 323                        |

| CTMUCONL | EDG2POL    | EDG2SE | L<1:0>   | EDG1POL | EDG1S  | EL<1:0>  | EDG2STAT | EDG1STAT | 324                        |

| CTMUICON | ITRIM<5:0> |        |          |         |        |          | IRNG     | 6<1:0>   | 325                        |

| IPR3     | SSP2IP     | BCL2IP | RC2IP    | TX2IP   | CTMUIP | TMR5GIP  | TMR3GIP  | TMR1GIP  | 123                        |

| PIE3     | SSP2IE     | BCL2IE | RC2IE    | TX2IE   | CTMUIE | TMR5GIE  | TMR3GIE  | TMR1GIE  | 119                        |

| PIR3     | SSP2IF     | BCL2IF | RC2IF    | TX2IF   | CTMUIF | TMR5GIF  | TMR3GIF  | TMR1GIF  | 114                        |

| PMD2     | —          |        | —        | -       | CTMUMD | CMP2MD   | CMP1MD   | ADCMD    | 54                         |

**Legend:** — = unimplemented, read as '0'. Shaded bits are not used during CTMU operation.

### 20.5 Register Definitions: SR Latch Control

| R/W-0      | R/W-0                                                                                                       | R/W-0                                                                                                                                                                                                                               | R/W-0                                                                                                                             | R/W-0                                                                                        | R/W-0                                                                                                    | R/W-0                                                                                                                       | R/W-0                           |

|------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| SRLEN      | 1                                                                                                           | SRCLK<2:0>                                                                                                                                                                                                                          |                                                                                                                                   | SRQEN                                                                                        | SRNQEN                                                                                                   | SRPS                                                                                                                        | SRPR                            |

| bit 7      | •                                                                                                           |                                                                                                                                                                                                                                     |                                                                                                                                   |                                                                                              |                                                                                                          | ÷                                                                                                                           | bit (                           |

| Legend:    |                                                                                                             |                                                                                                                                                                                                                                     |                                                                                                                                   |                                                                                              |                                                                                                          |                                                                                                                             |                                 |

| R = Reada  | able bit                                                                                                    | W = Writable b                                                                                                                                                                                                                      | it                                                                                                                                | U = Unimplei                                                                                 | mented                                                                                                   | C = Clearable                                                                                                               | only bit                        |

| -n = Value | at POR                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                    |                                                                                                                                   | '0' = Bit is cle                                                                             | ared                                                                                                     | x = Bit is unknown                                                                                                          |                                 |

| bit 7      | SRLEN: SR                                                                                                   | Latch Enable bit                                                                                                                                                                                                                    | 1)                                                                                                                                |                                                                                              |                                                                                                          |                                                                                                                             |                                 |

|            | 1 = SR latch<br>0 = SR latch                                                                                | is enabled                                                                                                                                                                                                                          |                                                                                                                                   |                                                                                              |                                                                                                          |                                                                                                                             |                                 |

| bit 3      | 001 = Ger<br>010 = Gen<br>011 = Gen<br>100 = Gen<br>101 = Gen<br>110 = Gen<br>111 = Gen<br><b>SRQEN:</b> SR | erates a 2 Tosc y<br>erates a 2 Tosc y | wide pulse or<br>wide pulse or<br>wide pulse or<br>wide pulse or<br>wide pulse or<br>wide pulse or<br>wide pulse or<br>Enable bit | n DIVSRCLK e<br>n DIVSRCLK e<br>n DIVSRCLK e<br>n DIVSRCLK e<br>n DIVSRCLK e<br>n DIVSRCLK e | very 8 periphe<br>very 16 periph<br>very 32 periph<br>very 64 periph<br>very 128 perip<br>very 256 perip | ral clock cycles<br>eral clock cycles<br>eral clock cycles<br>eral clock cycles<br>heral clock cycles<br>heral clock cycles | S<br>S<br>S<br>S<br>S<br>S<br>S |

|            | $0 = \mathbf{Q}$ is inte                                                                                    | •                                                                                                                                                                                                                                   |                                                                                                                                   |                                                                                              |                                                                                                          |                                                                                                                             |                                 |

| bit 2      |                                                                                                             | R Latch $\overline{Q}$ Outpusent on the SRNe<br>ernal only                                                                                                                                                                          |                                                                                                                                   |                                                                                              |                                                                                                          |                                                                                                                             |                                 |

| bit 1      | 1 = Pulse se                                                                                                | e Set Input of the<br>et input for two To<br>ct on set input                                                                                                                                                                        |                                                                                                                                   |                                                                                              |                                                                                                          |                                                                                                                             |                                 |

| bit 0      | 1 = Pulse re                                                                                                | e Reset Input of t<br>eset input for two<br>ct on Reset input                                                                                                                                                                       |                                                                                                                                   |                                                                                              |                                                                                                          |                                                                                                                             |                                 |

| Note 1:    | Changing the SR inputs of the latch                                                                         |                                                                                                                                                                                                                                     | e SR latch is                                                                                                                     | enabled may o                                                                                | cause false trig                                                                                         | gers to the set                                                                                                             | and Reset                       |

|            | Set only, always                                                                                            |                                                                                                                                                                                                                                     |                                                                                                                                   |                                                                                              |                                                                                                          |                                                                                                                             |                                 |

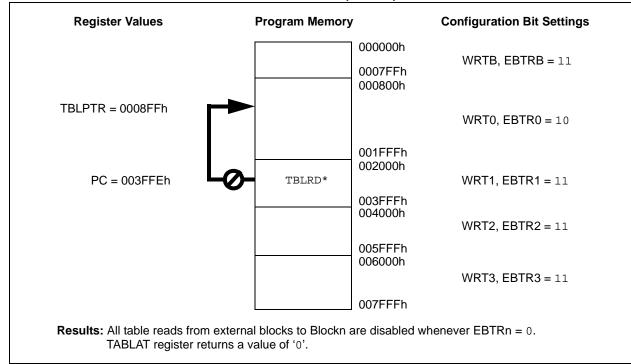

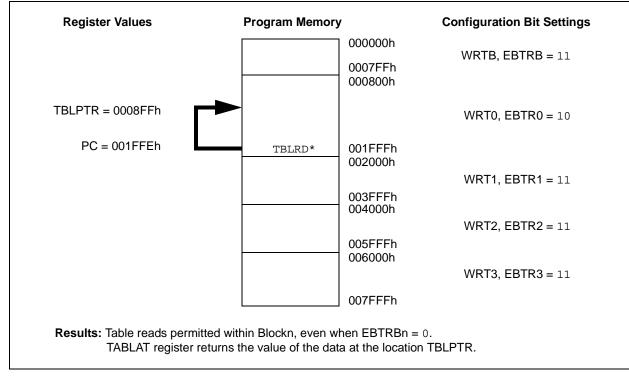

### FIGURE 24-4: EXTERNAL BLOCK TABLE READ (EBTRn) DISALLOWED

### FIGURE 24-5: EXTERNAL BLOCK TABLE READ (EBTRn) ALLOWED

| $\leq f \leq 255$<br>$\equiv [0,1]$<br>$\equiv [0,1]$<br>$\rightarrow dest$<br>Z<br>00001<br>e contempleme bred in V bred bacc $a' is '0', a' is '1', PR bank a' is '0' ist is enablindexed bode whe$                           | t<br>nts of reg<br>ented. If 'c<br>W. If 'd' is<br>k in regis<br>the Acce<br>the BSR                                                                                                                        | d' is '0',<br>'1', the<br>ster 'f' (dess Ban<br>is used<br>extended<br>instruct<br>Offset Ad<br>95 (5F<br>yte-Orie<br>uctions                      | are<br>the result is<br>result is<br>default).<br>k is sele<br>to select<br>d instruc-<br>tion oper<br>ddressin<br>h). See<br>ented ar<br>is in Inde | cted.<br>ct the<br>ction<br>rates<br>g<br>nd     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| $[0,1] = [0,1]$ $\rightarrow dest$ $[0,1] = [0,1]$ $\rightarrow dest$ $[0,001]$ e content<br>mpleme<br>bred in V<br>bred bacc<br>a' is '0',<br>a' is '1',<br>PR bank<br>a' is '0' is<br>t is enablighted<br>indexed<br>bode whe | t<br>11da<br>nts of reg<br>ented. If 'c<br>W. If 'd' is<br>ck in regis<br>the Acce<br>the BSR<br>the BSR<br>c.<br>and the e<br>bled, this<br>Literal C<br>enever $f \leq$<br><b>5.2.3 "By</b><br>ted Instru | gister 'f'<br>d' is '0',<br>. '1', the<br>ster 'f' (c<br>ss Ban<br>is used<br>extended<br>instruct<br>Offset Ac<br>: 95 (5F<br>yte-Orie<br>uctions | are<br>the result is<br>result is<br>default).<br>k is sele<br>to select<br>d instruc-<br>tion oper<br>ddressin<br>h). See<br>ented ar<br>is in Inde | ult is<br>cted.<br>ct the<br>ction<br>rates<br>g |

| Z<br>0001<br>e conter<br>mpleme<br>ored in V<br>ored bac<br>a' is '0',<br>a' is '1',<br>PR bank<br>a' is '0' a<br>t is enab<br>Indexed<br>ode whe                                                                               | 11da<br>nts of reg<br>ented. If 'c<br>W. If 'd' is<br>the Acce<br>the BSR<br>the BSR<br>and the e<br>bled, this<br>Literal C<br>enever $f \leq$<br>5.2.3 "By<br>ted Instru                                  | gister 'f'<br>d' is '0',<br>. '1', the<br>ster 'f' (c<br>ss Ban<br>is used<br>extended<br>instruct<br>Offset Ac<br>: 95 (5F<br>yte-Orie<br>uctions | are<br>the result is<br>result is<br>default).<br>k is sele<br>to select<br>d instruc-<br>tion oper<br>ddressin<br>h). See<br>ented ar<br>is in Inde | ult is<br>cted.<br>ct the<br>ction<br>rates<br>g |

| 0001<br>e conter<br>mpleme<br>ored in V<br>ored bac<br>a' is '0',<br>a' is '1',<br>PR bank<br>a' is '0' a<br>t is enat<br>indexed<br>ode whe                                                                                    | the Acce<br>the Acce<br>the BSR<br>and the e<br>bled, this<br>Literal C<br>enever $f \leq$<br><b>5.2.3 "By</b>                                                                                              | gister 'f'<br>d' is '0',<br>. '1', the<br>ster 'f' (c<br>ss Ban<br>is used<br>extended<br>instruct<br>Offset Ac<br>: 95 (5F<br>yte-Orie<br>uctions | are<br>the result is<br>result is<br>default).<br>k is sele<br>to select<br>d instruc-<br>tion oper<br>ddressin<br>h). See<br>ented ar<br>is in Inde | ult is<br>cted.<br>ct the<br>ction<br>rates<br>g |

| e conter<br>mpleme<br>ored in V<br>ored bac<br>a' is '0',<br>a' is '1',<br>PR bank<br>a' is '0' a<br>t is enab<br>Indexed<br>ode whe                                                                                            | the Acce<br>the Acce<br>the BSR<br>and the e<br>bled, this<br>Literal C<br>enever $f \leq$<br><b>5.2.3 "By</b>                                                                                              | gister 'f'<br>d' is '0',<br>. '1', the<br>ster 'f' (c<br>ss Ban<br>is used<br>extended<br>instruct<br>Offset Ac<br>: 95 (5F<br>yte-Orie<br>uctions | are<br>the result is<br>result is<br>default).<br>k is sele<br>to select<br>d instruc-<br>tion oper<br>ddressin<br>h). See<br>ented ar<br>is in Inde | ult is<br>cted.<br>ct the<br>ction<br>rates<br>g |

| mpleme<br>pred in V<br>pred bac<br>a' is '0',<br>a' is '1',<br>PR bank<br>a' is '0' a<br>t is enat<br>Indexed<br>pde whe                                                                                                        | ented. If $c$<br>W. If 'd' is<br>ck in regis<br>the Accee<br>the BSR<br>and the e<br>bled, this<br>Literal C<br>enever f $\leq$<br>5.2.3 "By<br>ted Instru                                                  | d' is '0',<br>'1', the<br>ster 'f' (dess Ban<br>is used<br>extended<br>instruct<br>Offset Ad<br>95 (5F<br>yte-Orie<br>uctions                      | the result is<br>result is<br>default).<br>k is seled<br>d instruc-<br>tion oper<br>ddressin<br>h). See<br>ented ar<br>is in Inde                    | cted.<br>ct the<br>ction<br>rates<br>g<br>nd     |

| -Orient                                                                                                                                                                                                                         |                                                                                                                                                                                                             | <b>e</b> 101 0                                                                                                                                     |                                                                                                                                                      |                                                  |

| eral Off                                                                                                                                                                                                                        |                                                                                                                                                                                                             |                                                                                                                                                    |                                                                                                                                                      |                                                  |

|                                                                                                                                                                                                                                 |                                                                                                                                                                                                             |                                                                                                                                                    |                                                                                                                                                      |                                                  |

|                                                                                                                                                                                                                                 |                                                                                                                                                                                                             |                                                                                                                                                    |                                                                                                                                                      |                                                  |

| _                                                                                                                                                                                                                               |                                                                                                                                                                                                             |                                                                                                                                                    | _                                                                                                                                                    |                                                  |

| Q2                                                                                                                                                                                                                              | Q                                                                                                                                                                                                           | -                                                                                                                                                  | Q4                                                                                                                                                   | 4.0                                              |

| Read<br>jister 'f'                                                                                                                                                                                                              | Proc<br>Da                                                                                                                                                                                                  |                                                                                                                                                    | Write<br>destina                                                                                                                                     |                                                  |

| <sup>MF</sup><br>13h<br>13h<br>ECh                                                                                                                                                                                              | REG,                                                                                                                                                                                                        | 0, 0                                                                                                                                               |                                                                                                                                                      |                                                  |

|                                                                                                                                                                                                                                 | -                                                                                                                                                                                                           | -                                                                                                                                                  | -                                                                                                                                                    |                                                  |

| 005050                           | 0                        | 6                                                               |                 |  |  |  |  |  |

|----------------------------------|--------------------------|-----------------------------------------------------------------|-----------------|--|--|--|--|--|

| CPFSEQ                           | -                        | f with W, sk                                                    | ID IT T = W     |  |  |  |  |  |

| Syntax:                          | CPFSEQ                   | f {,a}                                                          |                 |  |  |  |  |  |

| Operands:                        | 0 ≤ f ≤ 255<br>a ∈ [0,1] | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$ |                 |  |  |  |  |  |

| Operation:                       | (f) – (W),               |                                                                 |                 |  |  |  |  |  |

|                                  | skip if $(f) = ($        |                                                                 |                 |  |  |  |  |  |

| Statua Affaatad                  | None                     | comparison)                                                     |                 |  |  |  |  |  |

| Status Affected:                 |                          | 001a fff                                                        | f ffff          |  |  |  |  |  |

| Encoding:<br>Description:        | 0110                     | 001a fff                                                        |                 |  |  |  |  |  |

| Description.                     |                          | o the contents                                                  |                 |  |  |  |  |  |

|                                  | performing               | an unsigned s                                                   | ubtraction.     |  |  |  |  |  |

|                                  | ,                        | en the fetched<br>and a NOP is ex                               |                 |  |  |  |  |  |

|                                  |                          | king this a 2-c                                                 |                 |  |  |  |  |  |

|                                  | instruction.             | 5                                                               |                 |  |  |  |  |  |

|                                  |                          | he Access Bar                                                   |                 |  |  |  |  |  |

|                                  | GPR bank.                | he BSR is use                                                   | d to select the |  |  |  |  |  |

|                                  |                          | nd the extende                                                  | ed instruction  |  |  |  |  |  |

|                                  |                          | ed, this instruc                                                |                 |  |  |  |  |  |

|                                  |                          | Literal Offset A<br>iever f ≤ 95 (5F                            | 0               |  |  |  |  |  |

|                                  |                          | .2.3 "Byte-Ori                                                  | ,               |  |  |  |  |  |

|                                  |                          | d Instruction                                                   |                 |  |  |  |  |  |

|                                  |                          | set Mode" for                                                   | details.        |  |  |  |  |  |

| Words:                           | 1                        |                                                                 |                 |  |  |  |  |  |

| Cycles:                          | 1(2)<br>Note: 3 cv       | ycles if skip an                                                | d followed      |  |  |  |  |  |

|                                  |                          | a 2-word instru                                                 |                 |  |  |  |  |  |

| Q Cycle Activity:                |                          |                                                                 |                 |  |  |  |  |  |

| Q1                               | Q2                       | Q3                                                              | Q4              |  |  |  |  |  |

| Decode                           | Read                     | Process                                                         | No              |  |  |  |  |  |

| lf skip:                         | register 'f'             | Data                                                            | operation       |  |  |  |  |  |

| Q1                               | Q2                       | Q3                                                              | Q4              |  |  |  |  |  |

| No                               | No                       | No                                                              | No              |  |  |  |  |  |

| operation<br>If skip and followe | operation                | operation                                                       | operation       |  |  |  |  |  |

| Q1                               | Q2                       | Q3                                                              | Q4              |  |  |  |  |  |

| No                               | No                       | No                                                              | No              |  |  |  |  |  |

| operation                        | operation                | operation                                                       | operation       |  |  |  |  |  |