#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

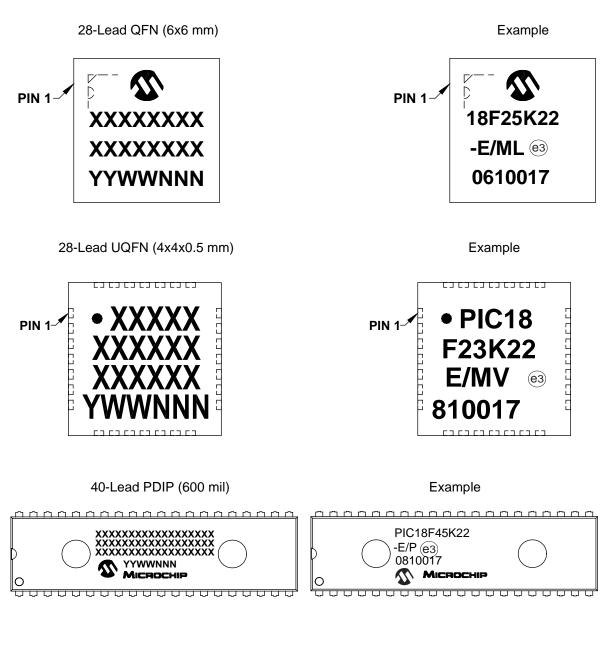

| Product Status             | Active                                                                    |  |  |  |  |

|----------------------------|---------------------------------------------------------------------------|--|--|--|--|

| Core Processor             | PIC                                                                       |  |  |  |  |

| Core Size                  | 8-Bit                                                                     |  |  |  |  |

| Speed                      | 64MHz                                                                     |  |  |  |  |

| Connectivity               | I²C, SPI, UART/USART                                                      |  |  |  |  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |  |  |  |  |

| Number of I/O              | 35                                                                        |  |  |  |  |

| Program Memory Size        | 16KB (8K x 16)                                                            |  |  |  |  |

| Program Memory Type        | FLASH                                                                     |  |  |  |  |

| EEPROM Size                | 256 x 8                                                                   |  |  |  |  |

| RAM Size                   | 768 × 8                                                                   |  |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |  |  |  |  |

| Data Converters            | A/D 30x10b                                                                |  |  |  |  |

| Oscillator Type            | Internal                                                                  |  |  |  |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |  |  |  |  |

| Mounting Type              | Through Hole                                                              |  |  |  |  |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |  |  |  |  |

| Supplier Device Package    | 40-PDIP                                                                   |  |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f44k22-i-p |  |  |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

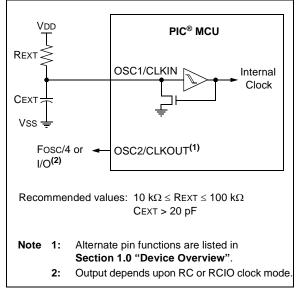

### 2.5.4 EXTERNAL RC MODES

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO.

#### 2.5.4.1 RC Mode

In RC mode, the RC circuit connects to OSC1. OSC2/ CLKOUT outputs the RC oscillator frequency divided by four. This signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements. Figure 2-8 shows the external RC mode connections.

#### FIGURE 2-8: EXTERNAL RC MODES

### 2.5.4.2 RCIO Mode

In RCIO mode, the RC circuit is connected to OSC1. OSC2 becomes a general purpose I/O pin.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- input threshold voltage variation

- component tolerances

- · packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

#### 2.6 Internal Clock Modes

The oscillator module has three independent, internal oscillators that can be configured or selected as the system clock source.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 2-3).

- The MFINTOSC (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 2-3).

- The LFINTOSC (Low-Frequency Internal Oscillator) is factory calibrated and operates at 31.25 kHz. The LFINTOSC cannot be useradjusted, but is designed to be stable over temperature and voltage.

The system clock speed can be selected via software using the Internal Oscillator Frequency select bits IRCF<2:0> of the OSCCON register.

The system clock can be selected between external or internal clock sources via the System Clock Selection (SCS<1:0>) bits of the OSCCON register. See **Section 2.11 "Clock Switching"** for more information.

#### 2.6.1 INTOSC WITH I/O OR CLOCKOUT

Two of the clock modes selectable with the FOSC<3:0> bits of the CONFIG1H Configuration register configure the internal oscillator block as the primary oscillator. Mode selection determines whether the OSC2/ CLKOUT pin will be configured as general purpose I/O or FOSC/4 (CLKOUT). In both modes, the OSC1/CLKIN pin is configured as general purpose I/O. See **Section 24.0 "Special Features of the CPU"** for more information.

The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

#### 5.3.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as either two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSb = 0). To maintain alignment with instruction boundaries, the PC increments in steps of two and the LSb will always read '0' (see Section 5.1.1 "Program Counter").

Figure 5-4 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 5-4 shows how the instruction GOTO 0006h is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. Section 25.0 "Instruction Set Summary" provides further details of the instruction set.

|                |            |                    | <b>LSB =</b> 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|------------|--------------------|----------------|---------|---------------------------|

|                | Program M  | lemory             |                |         | 000000h                   |

|                | Byte Locat | ions $\rightarrow$ |                |         | 000002h                   |

|                |            |                    |                |         | 000004h                   |

|                |            |                    |                |         | 000006h                   |

| Instruction 1: | MOVLW      | 055h               | 0Fh            | 55h     | 000008h                   |

| Instruction 2: | GOTO       | 0006h              | EFh            | 03h     | 00000Ah                   |

|                |            |                    | F0h            | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF      | 123h, 456h         | C1h            | 23h     | 00000Eh                   |

|                |            |                    | F4h            | 56h     | 000010h                   |

|                |            |                    |                |         | 000012h                   |

|                |            |                    |                |         | 000014h                   |

# FIGURE 5-4: INSTRUCTIONS IN PROGRAM MEMORY

# 5.3.4 TWO-WORD INSTRUCTIONS

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instruction always has '1111' as its four Most Significant bits; the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence – immediately after the first word – the data in the second word is accessed and used by the instruction sequence.

If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 5-4 shows how this works.

| Note: | See Section 5.8 "PIC18 Instruction<br>Execution and the Extended |

|-------|------------------------------------------------------------------|

|       | Instruction Set" for information on                              |

|       | two-word instructions in the extended instruction set.           |

| CASE 1:             |                  |                              |

|---------------------|------------------|------------------------------|

| Object Code         | Source Code      |                              |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; No, skip this word         |

| 1111 0100 0101 0110 |                  | ; Execute this word as a NOP |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |

| CASE 2:             |                  |                              |

| Object Code         | Source Code      |                              |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; Yes, execute this word     |

| 1111 0100 0101 0110 |                  | ; 2nd word of instruction    |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |

### EXAMPLE 5-4: TWO-WORD INSTRUCTIONS

# 6.5 Erasing Flash Program Memory

The minimum erase block is 32 words or 64 bytes. Only through the use of an external programmer, or through ICSP<sup>™</sup> control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. The TBLPTR<5:0> bits are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

The write initiate sequence for EECON2, shown as steps 4 through 6 in **Section 6.5.1** "**Flash Program Memory Erase Sequence**", is used to guard against accidental writes. This is sometimes referred to as a long write.

A long write is necessary for erasing the internal Flash. Instruction execution is halted during the long write cycle. The long write is terminated by the internal programming timer.

#### 6.5.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory is:

- 1. Load Table Pointer register with address of block being erased.

- 2. Set the EECON1 register for the erase operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN bit to enable writes;

- set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the block erase cycle.

- 7. The CPU will stall for duration of the erase (about 2 ms using internal timer).

- 8. Re-enable interrupts.

|          | MOVLW | CODE_ADDR_UPPER | ; load TBLPTR with the base     |

|----------|-------|-----------------|---------------------------------|

|          | MOVWF | TBLPTRU         | ; address of the memory block   |

|          | MOVLW | CODE_ADDR_HIGH  |                                 |

|          | MOVWF | TBLPTRH         |                                 |

|          | MOVLW | CODE_ADDR_LOW   |                                 |

|          | MOVWF | TBLPTRL         |                                 |

| ERASE_BL | ЭСК   |                 |                                 |

|          | BSF   | EECON1, EEPGD   | ; point to Flash program memory |

|          | BCF   | EECON1, CFGS    | ; access Flash program memory   |

|          | BSF   | EECON1, WREN    | ; enable write to memory        |

|          | BSF   | EECON1, FREE    | ; enable block Erase operation  |

|          | BCF   | INTCON, GIE     | ; disable interrupts            |

| Required | MOVLW | 55h             |                                 |

| Sequence | MOVWF | EECON2          | ; write 55h                     |

|          | MOVLW | 0AAh            |                                 |

|          | MOVWF | EECON2          | ; write OAAh                    |

|          | BSF   | EECON1, WR      | ; start erase (CPU stall)       |

|          | BSF   | INTCON, GIE     | ; re-enable interrupts          |

|          | BSF   | INTCON, GIE     | ; re-enable interrupts          |

#### EXAMPLE 6-2: ERASING A FLASH PROGRAM MEMORY BLOCK

| R/W-x        | R/W-x             | U-0                                                                                                                                              | R/W-0         | R/W-x                         | R/W-0            | R/S-0                                 | R/S-0         |  |  |  |

|--------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------|------------------|---------------------------------------|---------------|--|--|--|

| EEPGD        | CFGS              |                                                                                                                                                  | FREE          | WRERR                         | WREN             | WR                                    | RD            |  |  |  |

| bit 7        |                   |                                                                                                                                                  |               |                               |                  |                                       | bit (         |  |  |  |

|              |                   |                                                                                                                                                  |               |                               |                  |                                       |               |  |  |  |

| Legend:      |                   |                                                                                                                                                  |               |                               |                  |                                       |               |  |  |  |

| R = Readab   |                   | W = Writable                                                                                                                                     |               |                               |                  |                                       |               |  |  |  |

|              | be set by softwar |                                                                                                                                                  |               | •                             | mented bit, rea  |                                       |               |  |  |  |

| -n = Value a | t POR             | '1' = Bit is set                                                                                                                                 |               | '0' = Bit is cle              | eared            | x = Bit is unkı                       | nown          |  |  |  |

| bit 7        | EEPGD: Flas       | sh Program or I                                                                                                                                  | Data EEPRON   | / Memory Sele                 | ct bit           |                                       |               |  |  |  |

|              |                   | Flash program                                                                                                                                    |               |                               |                  |                                       |               |  |  |  |

|              | 0 = Access c      | data EEPROM                                                                                                                                      | memory        |                               |                  |                                       |               |  |  |  |

| bit 6        |                   | -                                                                                                                                                |               | Configuration S               | Select bit       |                                       |               |  |  |  |

|              |                   | Configuration re                                                                                                                                 | -             | 0.1                           |                  |                                       |               |  |  |  |

| bit 5        |                   | Flash program                                                                                                                                    |               | Ow memory                     |                  |                                       |               |  |  |  |

| bit 4        | -                 | Row (Block) E                                                                                                                                    |               | .i+                           |                  |                                       |               |  |  |  |

|              |                   | , ,                                                                                                                                              |               |                               | PTR on the ne    | ext WR commar                         | nd            |  |  |  |

|              | (cleared          | <ul> <li>1 = Erase the program memory block addressed by TBLPTR on the next WR command<br/>(cleared by completion of erase operation)</li> </ul> |               |                               |                  |                                       |               |  |  |  |

|              | 0 = Perform       | •                                                                                                                                                |               | (4)                           |                  |                                       |               |  |  |  |

| bit 3        |                   |                                                                                                                                                  |               | Error Flag bit <sup>(1)</sup> |                  |                                       |               |  |  |  |

|              |                   | peration is pre                                                                                                                                  | •             | • •                           | set during self- | timed programr                        | ning in norma |  |  |  |

|              |                   | e operation con                                                                                                                                  |               | P9                            |                  |                                       |               |  |  |  |

| bit 2        | WREN: Flash       | n Program/Data                                                                                                                                   | a EEPROM W    | rite Enable bit               |                  |                                       |               |  |  |  |

|              | 1 = Allows w      | rite cycles to F                                                                                                                                 | lash program/ | data EEPROM                   |                  |                                       |               |  |  |  |

|              | 0 = Inhibits v    | vrite cycles to F                                                                                                                                | -lash program | /data EEPROM                  | 1                |                                       |               |  |  |  |

| bit 1        | WR: Write Co      |                                                                                                                                                  |               | _                             |                  |                                       |               |  |  |  |

|              |                   |                                                                                                                                                  |               |                               |                  | ase cycle or writ<br>e write is compl |               |  |  |  |

|              |                   |                                                                                                                                                  |               | ed) by software               |                  |                                       | CIC.          |  |  |  |

|              |                   | cle to the EEPF                                                                                                                                  |               |                               | ,                |                                       |               |  |  |  |

| bit 0        | RD: Read Co       |                                                                                                                                                  |               |                               |                  |                                       |               |  |  |  |

|              |                   |                                                                                                                                                  |               |                               |                  | hardware. The F                       |               |  |  |  |

|              |                   | be set (not cleared) by software. RD bit cannot be set when EEPGD = 1 or CFGS = 1.)<br>0 = Does not initiate an EEPROM read                      |               |                               |                  |                                       |               |  |  |  |

|              |                   |                                                                                                                                                  |               |                               | · · · · · ·      |                                       |               |  |  |  |

| Note 1: W    | When a WRERR      | occurs, the EE                                                                                                                                   | PGD and CFG   | S bits are not                | cleared. This a  | llows tracing of                      | the           |  |  |  |

# REGISTER 7-1: EECON1: DATA EEPROM CONTROL 1 REGISTER

error condition.

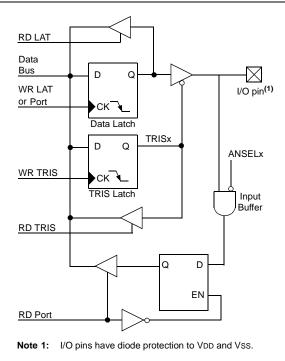

# 10.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. All pins of the I/O ports are multiplexed with one or more alternate functions from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has five registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

- ANSEL register (analog input control)

- SLRCON register (port slew rate control)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 10-1.

### FIGURE 10-1: GENERIC I/O PORT OPERATION

# 10.1 PORTA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the PORT latch.

The Data Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RA4/T0CKI/C1OUT pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 24.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs, and the comparator voltage reference output. The operation of pins RA<3:0> and RA5 as analog is selected by setting the ANSELA<5, 3:0> bits in the ANSELA register which is the default setting after a Power-on Reset.

Pins RA0 through RA5 may also be used as comparator inputs or outputs by setting the appropriate bits in the CM1CON0 and CM2CON0 registers.

Note: On a Power-on Reset, RA5 and RA<3:0> are configured as analog inputs and read as '0'. RA4 is configured as a digital input.

The RA4/T0CKI/C1OUT pin is a Schmitt Trigger input. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the drivers of the PORTA pins, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| MOVLB | 0xF    | ; | Set BSR for banked SFRs |

|-------|--------|---|-------------------------|

| CLRF  | PORTA  | ; | Initialize PORTA by     |

|       |        | ; | clearing output         |

|       |        | ; | data latches            |

| CLRF  | LATA   | ; | Alternate method        |

|       |        | ; | to clear output         |

|       |        | ; | data latches            |

| MOVLW | E0h    | ; | Configure I/O           |

| MOVWF | ANSELA | ; | for digital inputs      |

| MOVLW | OCFh   | ; | Value used to           |

|       |        | ; | initialize data         |

|       |        | ; | direction               |

| MOVWF | TRISA  | ; | Set RA<3:0> as inputs   |

|       |        | ; | RA<5:4> as outputs      |

|       |        |   | _                       |

### **10.7 Port Analog Control**

Most port pins are multiplexed with analog functions such as the Analog-to-Digital Converter and comparators. When these I/O pins are to be used as analog inputs it is necessary to disable the digital input buffer to avoid excessive current caused by improper biasing of the digital input. Individual control of the digital input buffers on pins which share analog functions is provided by the ANSELA, ANSELB, ANSELC, ANSELD and ANSELE registers. Setting an ANSx bit high will disable the associated digital input buffer and cause all reads of that pin to return '0' while allowing analog functions of that pin to operate correctly.

The state of the ANSx bits has no affect on digital output functions. A pin with the associated TRISx bit clear and ANSx bit set will still operate as a digital output but the input mode will be analog. This can cause unexpected behavior when performing readmodify-write operations on the affected port.

All ANSEL register bits default to '1' upon POR and BOR, disabling digital inputs for their associated port pins. All TRIS register bits default to '1' upon POR or BOR, disabling digital outputs for their associated port pins. As a result, all port pins that have an ANSEL register will default to analog inputs upon POR or BOR.

### 10.8 Port Slew Rate Control

The output slew rate of each port is programmable to select either the standard transition rate or a reduced transition rate of approximately 0.1 times the standard to minimize EMI. The reduced transition time is the default slew rate for all ports.

| 10.9 | Register | <b>Definitions</b> – | Port Control |

|------|----------|----------------------|--------------|

|------|----------|----------------------|--------------|

# REGISTER 10-1: PORTX<sup>(1)</sup>: PORTX REGISTER

| R/W-u/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

| Rx7     | Rx6     | Rx5     | Rx4     | Rx3     | Rx2     | Rx1     | Rx0     |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Logona.                    |                             |                                    |

|----------------------------|-----------------------------|------------------------------------|

| R = Readable bit           | W = Writable bit            | U = Unimplemented bit, read as '0' |

| '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown                 |

| -n/n = Value at POR and BO | R/Value at all other Resets |                                    |

bit 7-0 Rx<7:0>: PORTx I/O bit values<sup>(2)</sup>

**Note 1:** Register Description for PORTA, PORTB, PORTC and PORTD.

2: Writes to PORTx are written to corresponding LATx register. Reads from PORTx register is return of I/O pin values.

# 12.3 Timer1/3/5 Prescaler

Timer1/3/5 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The TxCKPS bits of the TxCON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMRxH or TMRxL.

# 12.4 Secondary Oscillator

A dedicated secondary low-power 32.768 kHz oscillator circuit is built-in between pins SOSCI (input) and SOSCO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the TxSOSCEN bit of the TxCON register, the SOSCGO bit of the OSCCON2 register or by selecting the secondary oscillator as the system clock by setting SCS<1:0> = 01 in the OSCCON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, TxSOSCEN should be set and a suitable delay observed prior to enabling Timer1/3/5.

# 12.5 Timer1/3/5 Operation in Asynchronous Counter Mode

If control bit TxSYNC of the TxCON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 12.5.1 "Reading and Writing Timer1/3/5 in Asynchronous Counter Mode").

Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 12.5.1 READING AND WRITING TIMER1/3/5 IN ASYNCHRONOUS COUNTER MODE

Reading TMRxH or TMRxL while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads. For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMRxH:TMRxL register pair.

# 12.6 Timer1/3/5 16-Bit Read/Write Mode

Timer1/3/5 can be configured to read and write all 16 bits of data, to and from, the 8-bit TMRxL and TMRxH registers, simultaneously. The 16-bit read and write operations are enabled by setting the RD16 bit of the TxCON register.

To accomplish this function, the TMRxH register value is mapped to a buffer register called the TMRxH buffer register. While in 16-Bit mode, the TMRxH register is not directly readable or writable and all read and write operations take place through the use of this TMRxH buffer register.

When a read from the TMRxL register is requested, the value of the TMRxH register is simultaneously loaded into the TMRxH buffer register. When a read from the TMRxH register is requested, the value is provided from the TMRxH buffer register instead. This provides the user with the ability to accurately read all 16 bits of the Timer1/3/5 value from a single instance in time.

In contrast, when not in 16-Bit mode, the user must read each register separately and determine if the values have become invalid due to a rollover that may have occurred between the read operations.

When a write request of the TMRxL register is requested, the TMRxH buffer register is simultaneously updated with the contents of the TMRxH register. The value of TMRxH must be preloaded into the TMRxH buffer register prior to the write request for the TMRxL register. This provides the user with the ability to write all 16 bits to the TMRxL:TMRxH register pair at the same time.

Any requests to write to the TMRxH directly does not clear the Timer1/3/5 prescaler value. The prescaler value is only cleared through write requests to the TMRxL register.

| Name     | Bit 7           | Bit 6                             | Bit 5         | Bit 4       | Bit 3       | Bit 2       | Bit 1  | Bit 0   | Register<br>on Page |

|----------|-----------------|-----------------------------------|---------------|-------------|-------------|-------------|--------|---------|---------------------|

| CCPTMRS0 | C3TSE           | L<1:0>                            | — C2TSEL<1:0> |             | —           | C1TSEL<1:0> |        | 201     |                     |

| CCPTMRS1 | _               | —                                 | —             | _           | C5TSE       | L<1:0>      | C4TS   | EL<1:0> | 201                 |

| INTCON   | GIE/GIEH        | PEIE/GIEL                         | TMR0IE        | INT0IE      | RBIE        | TMR0IF      | INT0IF | RBIF    | 109                 |

| IPR1     | _               | ADIP                              | RC1IP         | TX1IP       | SSP1IP      | CCP1IP      | TMR2IP | TMR1IP  | 121                 |

| IPR5     | _               | _                                 | _             | _           | _           | TMR6IP      | TMR5IP | TMR4IP  | 124                 |

| PIE1     | _               | ADIE                              | RC1IE         | TX1IE       | SSP1IE      | CCP1IE      | TMR2IE | TMR1IE  | 117                 |

| PIE5     | _               | _                                 |               | _           | _           | TMR6IE      | TMR5IE | TMR4IE  | 120                 |

| PIR1     | _               | ADIF                              | RC1IF         | TX1IF       | SSP1IF      | CCP1IF      | TMR2IF | TMR1IF  | 112                 |

| PIR5     | _               | _                                 |               | _           | _           | TMR6IF      | TMR5IF | TMR4IF  | 116                 |

| PMD0     | UART2MD         | UART1MD                           | TMR6MD        | TMR5MD      | TMR4MD      | TMR3MD      | TMR2MD | TMR1MD  | 52                  |

| PR2      |                 |                                   | -             | Timer2 Peri | od Register |             |        |         | —                   |

| PR4      |                 |                                   | -             | Timer4 Peri | od Register |             |        |         | —                   |

| PR6      |                 |                                   | -             | Timer6 Peri | od Register |             |        |         | _                   |

| T2CON    | _               |                                   | T2OUTPS       | S<3:0>      |             | TMR2ON      | T2CK   | PS<1:0> | 166                 |

| T4CON    |                 |                                   | T4OUTPS       | S<3:0>      |             | TMR4ON      | T4CK   | PS<1:0> | 166                 |

| T6CON    |                 | - T6OUTPS<3:0> TMR6ON T6CKPS<1:0> |               |             |             |             |        | 166     |                     |

| TMR2     | Timer2 Register |                                   |               |             |             |             |        | _       |                     |

| TMR4     |                 |                                   |               | Timer4 I    | Register    |             |        |         | —                   |

| TMR6     |                 |                                   |               | Timer6 I    | Register    |             |        |         | —                   |

### TABLE 13-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2/4/6

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by Timer2/4/6.

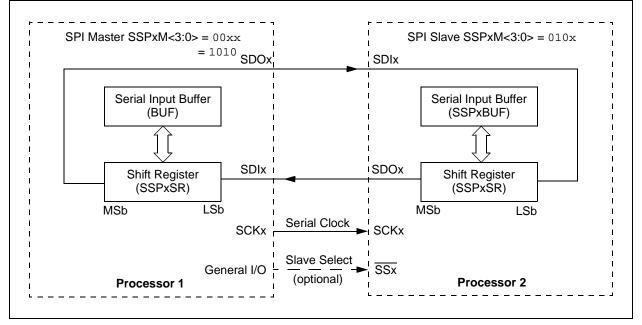

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

The MSSPx consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF of the SSPxSTAT register, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL of the SSPxCON1 register, will be

set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSPx interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

| R/W-0            | R-0                                                                                           | R/W-0                              | R/S/HC-0                        | R/S/HC-0                      | R/S/HC-0            | R/S/HC-0            | R/W/HC-0           |  |  |

|------------------|-----------------------------------------------------------------------------------------------|------------------------------------|---------------------------------|-------------------------------|---------------------|---------------------|--------------------|--|--|

| GCEN             | ACKSTAT                                                                                       | ACKDT                              | ACKEN <sup>(1)</sup>            | RCEN <sup>(1)</sup>           | PEN <sup>(1)</sup>  | RSEN <sup>(1)</sup> | SEN <sup>(1)</sup> |  |  |

| bit 7            |                                                                                               |                                    |                                 |                               |                     |                     | bit C              |  |  |

|                  |                                                                                               |                                    |                                 |                               |                     |                     |                    |  |  |

| Legend:          |                                                                                               |                                    |                                 |                               |                     |                     |                    |  |  |

| R = Readable     | bit                                                                                           | W = Writable                       | e bit                           | U = Unimple                   | mented bit, read    | l as '0'            |                    |  |  |

| u = Bit is unch  | anged                                                                                         | x = Bit is unk                     | nown                            | -n/n = Value                  | at POR and BO       | R/Value at all c    | other Resets       |  |  |

| '1' = Bit is set |                                                                                               | '0' = Bit is cle                   | eared                           | HC = Cleare                   | d by hardware       | S = User set        |                    |  |  |

|                  |                                                                                               |                                    | 0                               |                               |                     |                     |                    |  |  |

| bit 7            |                                                                                               |                                    | e bit (in I <sup>2</sup> C Sla  | •                             | ,                   |                     |                    |  |  |

|                  |                                                                                               | terrupt when a call address di     |                                 | ddress (0x00                  | or 00h) is receiv   | red in the SSP      | SR                 |  |  |

| bit 6            |                                                                                               |                                    | tatus bit (in I <sup>2</sup> C  | mode only)                    |                     |                     |                    |  |  |

|                  |                                                                                               | edge was not r                     |                                 | mode emy,                     |                     |                     |                    |  |  |

|                  |                                                                                               | edge was rece                      |                                 |                               |                     |                     |                    |  |  |

| bit 5            |                                                                                               |                                    | a bit (in I <sup>2</sup> C moo  | de only)                      |                     |                     |                    |  |  |

|                  | In Receive m                                                                                  |                                    |                                 |                               |                     |                     |                    |  |  |

|                  | 1 = Not Ackn                                                                                  |                                    | user initiates a                | in Acknowled                  | ge sequence at      | the end of a re-    | ceive              |  |  |

|                  | 0 = Acknowle                                                                                  |                                    |                                 |                               |                     |                     |                    |  |  |

| bit 4            | ACKEN <sup>(1)</sup> : Acknowledge Sequence Enable bit (in I <sup>2</sup> C Master mode only) |                                    |                                 |                               |                     |                     |                    |  |  |

|                  | In Master Receive mode:                                                                       |                                    |                                 |                               |                     |                     |                    |  |  |

|                  |                                                                                               |                                    |                                 | SDAx and S                    | SCLx pins, and      | I transmit ACI      | KDT data bit       |  |  |

|                  |                                                                                               | tically cleared b<br>ledge sequenc |                                 |                               |                     |                     |                    |  |  |

| bit 3            | RCEN <sup>(1)</sup> : Re                                                                      | ceive Enable b                     | oit (in I <sup>2</sup> C Maste  | er mode only)                 |                     |                     |                    |  |  |

|                  |                                                                                               | Receive mode                       | for I <sup>2</sup> C            |                               |                     |                     |                    |  |  |

|                  | 0 = Receive                                                                                   |                                    |                                 |                               |                     |                     |                    |  |  |

| bit 2            | SCKx Release                                                                                  |                                    | able bit (in I <sup>2</sup> C N | laster mode o                 | only)               |                     |                    |  |  |

|                  |                                                                                               |                                    | n SDAx and S(                   | Clyning Auto                  | omatically cleare   | d by hardware       |                    |  |  |

|                  | 0 = Stop con                                                                                  |                                    |                                 |                               |                     |                     | •                  |  |  |

| bit 1            | RSEN <sup>(1)</sup> : Re                                                                      | peated Start C                     | ondition Enable                 | ed bit (in I <sup>2</sup> C N | Aaster mode onl     | y)                  |                    |  |  |

|                  |                                                                                               |                                    |                                 | DAx and SCL                   | x pins. Automati    | cally cleared b     | y hardware.        |  |  |

|                  |                                                                                               | ed Start condition                 |                                 |                               |                     |                     |                    |  |  |

| bit 0            |                                                                                               |                                    | abled bit (in I <sup>2</sup> C  | Master mode                   | only)               |                     |                    |  |  |

|                  | In Master mo                                                                                  |                                    | n SDAy and S(                   | 71 x nine Auto                | omatically cleare   | ad by bardware      |                    |  |  |

|                  | 1 = 1111111111111111111111111111111111                                                        |                                    |                                 |                               |                     |                     | •                  |  |  |

|                  | In Slave mod                                                                                  | <u>le:</u>                         |                                 |                               |                     |                     |                    |  |  |

|                  |                                                                                               | etching is enal<br>etching is disa |                                 | ave transmit a                | nd slave receive    | e (stretch enabl    | ed)                |  |  |

| Note 1: For      |                                                                                               |                                    |                                 |                               | e is not in the Idl |                     |                    |  |  |

### REGISTER 15-4: SSPxCON2: SSPx CONTROL REGISTER 2

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

| Name                  | Bit 7    | Bit 6     | Bit 5    | Bit 4     | Bit 3          | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|-----------------------|----------|-----------|----------|-----------|----------------|-----------------------|-----------------------|-----------------------|---------------------|

| ADCON0                | _        |           |          | CHS<4:0>  |                |                       | GO/DONE               | ADON                  | 295                 |

| ADCON1                | TRIGSEL  | _         | _        | _         | PVCF           |                       | NVCFG                 | <1:0>                 | 296                 |

| ADCON2                | ADFM     | _         | ŀ        | \CQT<2:0> |                |                       | ADCS<2:0>             |                       | 297                 |

| ADRESH                |          |           |          | A/D Res   | ult, High Byte |                       |                       |                       | 298                 |

| ADRESL                |          |           |          | A/D Res   | ult, Low Byte  |                       |                       |                       | 298                 |

| ANSELA                | _        | _         | ANSA5    |           | ANSA3          | ANSA2                 | ANSA1                 | ANSA0                 | 149                 |

| ANSELB                | _        | _         | ANSB5    | ANSB4     | ANSB3          | ANSB2                 | ANSB1                 | ANSB0                 | 150                 |

| ANSELC                | ANSC7    | ANSC6     | ANSC5    | ANSC4     | ANSC3          | ANSC2                 | —                     | —                     | 150                 |

| ANSELD <sup>(1)</sup> | ANSD7    | ANSD6     | ANSD5    | ANSD4     | ANSD3          | ANSD2                 | ANSD1                 | ANSD0                 | 150                 |

| ANSELE <sup>(1)</sup> | _        | _         | _        | —         | _              | ANSE2                 | ANSE1                 | ANSE0                 | 151                 |

| CCP5CON               | —        | _         | DC5B<    | 1:0>      |                | CCP5M<3:0>            |                       |                       |                     |

| CTMUCONH              | CTMUEN   | _         | CTMUSIDL | TGEN      | EDGEN          | EDGSEQEN              | IDISSEN               | CTTRIG                | 323                 |

| INTCON                | GIE/GIEH | PEIE/GIEL | TMR0IE   | INTOIE    | RBIE           | TMR0IF                | INT0IF                | RBIF                  | 109                 |

| IPR1                  | —        | ADIP      | RC1IP    | TX1IP     | SSP1IP         | CCP1IP                | TMR2IP                | TMR1IP                | 121                 |

| IPR3                  | SSP2IP   | BCL2IP    | RC2IP    | TX2IP     | CTMUIP         | TMR5GIP               | TMR3GIP               | TMR1GIP               | 123                 |

| IPR4                  | —        | —         | —        | —         | _              | CCP5IP                | CCP4IP                | CCP3IP                | 124                 |

| PIE1                  | _        | ADIE      | RC1IE    | TX1IE     | SSP1IE         | CCP1IE                | TMR2IE                | TMR1IE                | 117                 |

| PIE3                  | SSP2IE   | BCL2IE    | RC2IE    | TX2IE     | CTMUIE         | TMR5GIE               | TMR3GIE               | TMR1GIE               | 119                 |

| PIE4                  | —        | _         | _        | —         | _              | CCP5IE                | CCP4IE                | CCP3IE                | 120                 |

| PIR1                  | —        | ADIF      | RC1IF    | TX1IF     | SSP1IF         | CCP1IF                | TMR2IF                | TMR1IF                | 112                 |

| PIR3                  | SSP2IF   | BCL2IF    | RC2IF    | TX2IF     | CTMUIF         | TMR5GIF               | TMR3GIF               | TMR1GIF               | 114                 |

| PIR4                  | —        | —         | —        | —         | _              | CCP5IF                | CCP4IF                | CCP3IF                | 115                 |

| PMD1                  | MSSP2MD  | MSSP1MD   | —        | CCP5MD    | CCP4MD         | CCP3MD                | CCP2MD                | CCP1MD                | 53                  |

| PMD2                  | _        | _         | _        | _         | CTMUMD         | CMP2MD                | CMP1MD                | ADCMD                 | 54                  |

| TRISA                 | TRISA7   | TRISA6    | TRISA5   | TRISA4    | TRISA3         | TRISA2                | TRISA1                | TRISA0                | 151                 |

| TRISB                 | TRISB7   | TRISB6    | TRISB5   | TRISB4    | TRISB3         | TRISB2                | TRISB1                | TRISB0                | 151                 |

| TRISC                 | TRISC7   | TRISC6    | TRISC5   | TRISC4    | TRISC3         | TRISC2                | TRISC1                | TRISC0                | 151                 |

| TRISD <sup>(1)</sup>  | TRISD7   | TRISD6    | TRISD5   | TRISD4    | TRISD3         | TRISD2                | TRISD1                | TRISD0                | 151                 |

| TRISE                 | WPUE3    | _         | _        | _         | _              | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 151                 |

| <b>TABLE 17-2</b> : | <b>REGISTERS ASSOCIATED WITH A/D OPERATION</b> |

|---------------------|------------------------------------------------|

|                     |                                                |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by this module.

Note 1: Available on PIC18(L)F4XK22 devices.

### TABLE 17-3: CONFIGURATION REGISTERS ASSOCIATED WITH THE ADC MODULE

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| CONFIG3H | MCLRE | _     | P2BMX | T3CMX | HFOFST | CCP3MX | PBADEN | CCP2MX | 348                 |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by the ADC module.

# 20.0 SR LATCH

The module consists of a single SR latch with multiple Set and Reset inputs as well as separate latch outputs. The SR latch module includes the following features:

- Programmable input selection

- SR latch output is available internally/externally

- Selectable Q and  $\overline{Q}$  output

- Firmware Set and Reset

The SR latch can be used in a variety of analog applications, including oscillator circuits, one-shot circuit, hysteretic controllers, and analog timing applications.

# 20.1 Latch Operation

The latch is a Set-Reset latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be set or reset by:

- Software control (SRPS and SRPR bits)

- Comparator C1 output (sync\_C1OUT)

- Comparator C2 output (sync\_C2OUT)

- SRI Pin

- Programmable clock (DIVSRCLK)

The SRPS and the SRPR bits of the SRCON0 register may be used to set or reset the SR latch, respectively. The latch is Reset-dominant. Therefore, if both Set and Reset inputs are high, the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

The output from Comparator C1 or C2 can be used as the Set or Reset inputs of the SR latch. The output of either Comparator can be synchronized to the Timer1 clock source. See Section 18.0 "Comparator Module" and Section 12.0 "Timer1/3/5 Module with Gate Control" for more information.

An external source on the SRI pin can be used as the Set or Reset inputs of the SR latch.

An internal clock source, DIVSRCLK, is available and it can periodically set or reset the SR latch. The SRCLK<2:0> bits in the SRCON0 register are used to select the clock source period. The SRSCKE and SRRCKE bits of the SRCON1 register enable the clock source to set or reset the SR latch, respectively.

# 20.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR latch outputs may be directly output to I/O pins at the same time. Control is determined by the state of bits SRQEN and SRNQEN in the SRCON0 register.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

# 20.3 DIVSRCLK Clock Generation

The DIVSRCLK clock signal is generated from the peripheral clock which is pre-scaled by a value determined by the SRCLK<2:0> bits. See Figure 20-2 and Table 20-1 for additional detail.

# 20.4 Effects of a Reset

Upon any device Reset, the SR latch is not initialized, and the SRQ and SRNQ outputs are unknown. The user's firmware is responsible to initialize the latch output before enabling it to the output pins.

# 22.7 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the VREFCON1 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

#### 22.8 Effects of a Reset

A device Reset affects the following:

- DAC is disabled

- DAC output voltage is removed from the DACOUT pin

- The DACR<4:0> range select bits are cleared

# 22.9 Register Definitions: DAC Control

#### REGISTER 22-1: VREFCON1: VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0 | R/W-0  | R/W-0 | U-0 | R/W-0       | R/W-0 | U-0 | R/W-0  |

|-------|--------|-------|-----|-------------|-------|-----|--------|

| DACEN | DACLPS | DACOE | —   | DACPSS<1:0> |       | —   | DACNSS |

| bit 7 |        |       |     |             |       |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | DACEN: DAC Enable bit<br>1 = DAC is enabled<br>0 = DAC is disabled                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | DACLPS: DAC Low-Power Voltage Source Select bit                                                                                                                                                |

|         | <ul><li>1 = DAC Positive reference source selected</li><li>0 = DAC Negative reference source selected</li></ul>                                                                                |

| bit 5   | <ul> <li>DACOE: DAC Voltage Output Enable bit</li> <li>1 = DAC voltage level is also an output on the DACOUT pin</li> <li>0 = DAC voltage level is disconnected from the DACOUT pin</li> </ul> |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 3-2 | DACPSS<1:0>: DAC Positive Source Select bits<br>00 = VDD<br>01 = VREF+<br>10 = FVR BUF1 output<br>11 = Reserved, do not use                                                                    |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 0   | DACNSS: DAC Negative Source Select bits<br>1 = VREF-                                                                                                                                           |

# PIC18(L)F2X/4XK22

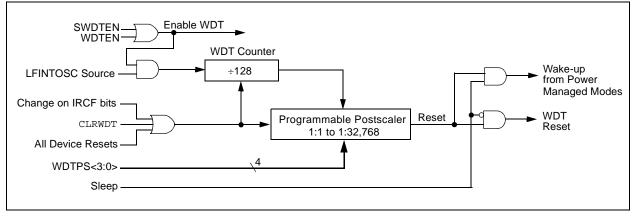

# 24.3 Watchdog Timer (WDT)

For PIC18(L)F2X/4XK22 devices, the WDT is driven by the LFINTOSC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the LFINTOSC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration Register 2H. Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: a SLEEP or CLRWDT instruction is executed, the IRCF bits of the OSCCON register are changed or a clock failure has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: Changing the setting of the IRCF bits of the OSCCON register clears the WDT and postscaler counts.

- **3:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

#### FIGURE 24-1: WDT BLOCK DIAGRAM

# 27.7 DC Characteristics: Secondary Oscillator Supply Current, PIC18(L)F2X/4XK22

| PIC18LF2X/4XK22<br>PIC18F2X/4XK22 |                             | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |    |    |        |            |                                |  |  |

|-----------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|--------|------------|--------------------------------|--|--|

|                                   |                             |                                                                                                                                                                                                                                           |    |    |        |            |                                |  |  |

| D130                              | Supply Current (IDD)(1),(2) | 3.5                                                                                                                                                                                                                                       | 23 | μΑ | -40°C  | VDD = 1.8V | Fosc = 32 kHz                  |  |  |

|                                   |                             | 3.7                                                                                                                                                                                                                                       | 25 | μΑ | +25°C  |            | (SEC_RUN mode,<br>SOSC source) |  |  |

|                                   |                             | 3.8                                                                                                                                                                                                                                       | —  | μΑ | +60°C  |            |                                |  |  |

|                                   |                             | 4.0                                                                                                                                                                                                                                       | 28 | μΑ | +85°C  |            |                                |  |  |

|                                   |                             | 5.1                                                                                                                                                                                                                                       | 30 | μΑ | +125°C |            |                                |  |  |

| D131                              |                             | 6.2                                                                                                                                                                                                                                       | 26 | μΑ | -40°C  | VDD = 3.0V |                                |  |  |

|                                   |                             | 6.4                                                                                                                                                                                                                                       | 30 | μΑ | +25°C  |            |                                |  |  |

|                                   |                             | 6.5                                                                                                                                                                                                                                       | —  | μΑ | +60°C  |            |                                |  |  |

|                                   |                             | 6.8                                                                                                                                                                                                                                       | 35 | μΑ | +85°C  |            |                                |  |  |

|                                   |                             | 7.8                                                                                                                                                                                                                                       | 40 | μΑ | +125°C |            |                                |  |  |

| D132                              |                             | 15                                                                                                                                                                                                                                        | 35 | μΑ | -40°C  | VDD = 2.3V | Fosc = 32 kHz                  |  |  |

|                                   |                             | 16                                                                                                                                                                                                                                        | 35 | μΑ | +25°C  |            | (SEC_RUN mode, SOSC source)    |  |  |

|                                   |                             | 17                                                                                                                                                                                                                                        | 35 | μΑ | +85°C  |            |                                |  |  |

|                                   |                             | 19                                                                                                                                                                                                                                        | 50 | μΑ | +125°C |            |                                |  |  |

| D133                              |                             | 18                                                                                                                                                                                                                                        | 50 | μΑ | -40°C  | VDD = 3.0V |                                |  |  |

|                                   |                             | 19                                                                                                                                                                                                                                        | 50 | μΑ | +25°C  |            |                                |  |  |

|                                   |                             | 21                                                                                                                                                                                                                                        | 50 | μΑ | +85°C  |            |                                |  |  |

|                                   |                             | 22                                                                                                                                                                                                                                        | 60 | μΑ | +125°C |            |                                |  |  |

| D134                              |                             | 19                                                                                                                                                                                                                                        | 55 | μΑ | -40°C  | VDD = 5.0V |                                |  |  |

|                                   |                             | 20                                                                                                                                                                                                                                        | 55 | μΑ | +25°C  |            |                                |  |  |

|                                   |                             | 22                                                                                                                                                                                                                                        | 55 | μΑ | +85°C  |            |                                |  |  |

|                                   |                             | 23                                                                                                                                                                                                                                        | 70 | μΑ | +125°C |            |                                |  |  |

**Note 1:** The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

Test condition: All Peripheral Module Control bits in PMD0, PMD1 and PMD2 set to '1'.

2: The test conditions for all IDD measurements in active operation mode are: All I/O pins set as outputs driven to Vss;

$\frac{AIII}{MCLR} = VDD;$

SOSCI / SOSCO = complementary external square wave, from rail-to-rail.

| Param.<br>No. | Symbol                | Characteristic                                                         | Min          | Max      | Units    | Conditions                        |

|---------------|-----------------------|------------------------------------------------------------------------|--------------|----------|----------|-----------------------------------|

| 70            | TssL2scH,<br>TssL2scL | $\overline{SS} \downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ Input | Тсү          | _        | ns       |                                   |

| 71            | TscH                  | SCK Input High Time Continuous                                         | 25           | _        | ns       |                                   |

| 72            | TscL                  | SCK Input Low Time Continuous                                          | 30           | _        | ns       |                                   |

| 73            | TdiV2scH,<br>TdiV2scL | Setup Time of SDI Data Input to SCK Edge                               | 25           | —        | ns       |                                   |

| 74            | TscH2diL,<br>TscL2diL | Hold Time of SDI Data Input to SCK Edge                                | 25           | —        | ns       |                                   |