Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 30x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

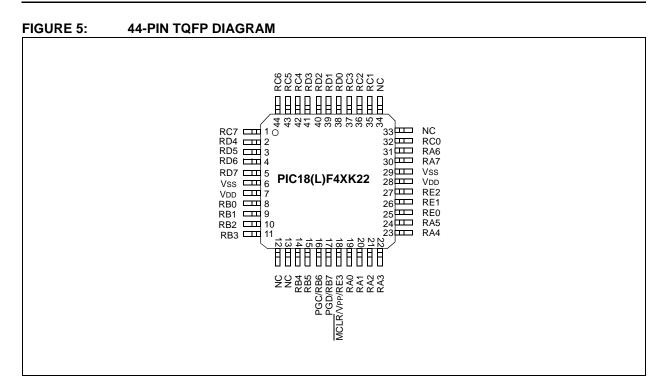

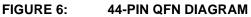

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f44k22-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18(L)F2X/4XK22

| Pin Nu        | umber        |                                | <b>D</b> '  | Duffer         |                                                     |

|---------------|--------------|--------------------------------|-------------|----------------|-----------------------------------------------------|

| PDIP,<br>SOIC | QFN,<br>UQFN | Pin Name                       | Pin<br>Type | Buffer<br>Type | Description                                         |

| 25            | 22           | RB4/IOC0/P1D/T5G/AN11          |             |                |                                                     |

|               |              | RB4                            | I/O         | TTL            | Digital I/O.                                        |

|               |              | IOC0                           | I           | TTL            | Interrupt-on-change pin.                            |

|               |              | P1D                            | 0           | CMOS           | Enhanced CCP1 PWM output.                           |

|               |              | T5G                            | I           | ST             | Timer5 external clock gate input.                   |

|               |              | AN11                           | I           | Analog         | Analog input 11.                                    |

| 26            | 23           | RB5/IOC1/P2B/P3A/CCP3/T3CKI/T1 | G/AN13      | 3              |                                                     |

|               |              | RB5                            | I/O         | TTL            | Digital I/O.                                        |

|               |              | IOC1                           | I           | TTL            | Interrupt-on-change pin.                            |

|               |              | P2B <sup>(1)</sup>             | 0           | CMOS           | Enhanced CCP2 PWM output.                           |

|               |              | P3A <sup>(1)</sup>             | 0           | CMOS           | Enhanced CCP3 PWM output.                           |

|               |              | CCP3 <sup>(1)</sup>            | I/O         | ST             | Capture 3 input/Compare 3 output/PWM 3 output.      |

|               |              | ТЗСКІ <sup>(2)</sup>           | I           | ST             | Timer3 clock input.                                 |

|               |              | T1G                            | I           | ST             | Timer1 external clock gate input.                   |

|               |              | AN13                           | I           | Analog         | Analog input 13.                                    |

| 27            | 24           | RB6/IOC2/TX2/CK2/PGC           |             |                |                                                     |

|               |              | RB6                            | I/O         | TTL            | Digital I/O.                                        |

|               |              | IOC2                           | I           | TTL            | Interrupt-on-change pin.                            |

|               |              | TX2                            | 0           | _              | EUSART asynchronous transmit.                       |

|               |              | CK2                            | I/O         | ST             | EUSART synchronous clock (see related RXx/DTx).     |

|               |              | PGC                            | I/O         | ST             | In-Circuit Debugger and ICSP™ programming clock pir |

| 28            | 25           | RB7/IOC3/RX2/DT2/PGD           |             |                |                                                     |

|               |              | RB7                            | I/O         | TTL            | Digital I/O.                                        |

|               |              | IOC3                           | I           | TTL            | Interrupt-on-change pin.                            |

|               |              | RX2                            | I           | ST             | EUSART asynchronous receive.                        |

|               |              | DT2                            | I/O         | ST             | EUSART synchronous data (see related TXx/CKx).      |

|               |              | PGD                            | I/O         | ST             | In-Circuit Debugger and ICSP™ programming data pin  |

| 11            | 8            | RC0/P2B/T3CKI/T3G/T1CKI/SOSCC  | )           |                |                                                     |

|               |              | RC0                            | I/O         | ST             | Digital I/O.                                        |

|               |              | P2B <sup>(2)</sup>             | 0           | CMOS           | Enhanced CCP1 PWM output.                           |

|               |              | ТЗСКІ <sup>(1)</sup>           | I           | ST             | Timer3 clock input.                                 |

|               |              | T3G                            | I           | ST             | Timer3 external clock gate input.                   |

|               |              | T1CKI                          | I           | ST             | Timer1 clock input.                                 |

|               |              | SOSCO                          | 0           | _              | Secondary oscillator output.                        |

| 12            | 9            | RC1/P2A/CCP2/SOSCI             | 1           | 1              |                                                     |

|               |              | RC1                            | I/O         | ST             | Digital I/O.                                        |

|               |              | P2A                            | 0           | CMOS           | Enhanced CCP2 PWM output.                           |

|               |              | CCP2 <sup>(1)</sup>            | I/O         | ST             | Capture 2 input/Compare 2 output/PWM 2 output.      |

|               |              | SOSCI                          | 1           | Analog         | Secondary oscillator input.                         |

### TABLE 1-2: PIC18(L)F2XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

# 2.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

# 2.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 2-1 illustrates a block diagram of the oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be configured from one of three internal oscillators, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, EC or RC modes) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The primary clock module can be configured to provide one of six clock sources as the primary clock.

- 1. RC External Resistor/Capacitor

- 2. LP Low-Power Crystal

- 3. XT Crystal/Resonator

- 4. INTOSC Internal Oscillator

- 5. HS High-Speed Crystal/Resonator

- 6. EC External Clock

The HS and EC oscillator circuits can be optimized for power consumption and oscillator speed using settings in FOSC<3:0>. Additional FOSC<3:0> selections enable RA6 to be used as I/O or CLKO (FOSC/4) for RC, EC and INTOSC Oscillator modes.

Primary Clock modes are selectable by the FOSC<3:0> bits of the CONFIG1H Configuration register. The primary clock operation is further defined by these Configuration and register bits:

- 1. PRICLKEN (CONFIG1H<5>)

- 2. PRISD (OSCCON2<2>)

- 3. PLLCFG (CONFIG1H<4>)

- 4. PLLEN (OSCTUNE<6>)

- 5. HFOFST (CONFIG3H<3>)

- 6. IRCF<2:0> (OSCCON<6:4>)

- 7. MFIOSEL (OSCCON2<4>)

- 8. INTSRC (OSCTUNE<7>)

The HFINTOSC, MFINTOSC and LFINTOSC are factory calibrated high, medium and low-frequency oscillators, respectively, which are used as the internal clock sources.

# 3.6 Selective Peripheral Module Control

Idle mode allows users to substantially reduce power consumption by stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what IDLE mode does not provide: the allocation of power resources to the CPU processing with minimal power consumption from the peripherals. PIC18(L)F2X/4XK22 family devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with control bits in the Peripheral Module Disable (PMD) registers. These bits generically named XXXMD are located in control registers PMD0, PMD1 or PMD2.

Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, power to the control and status registers associated with the peripheral is removed. Writes to these registers have no effect and read values are invalid. Clearing a set PMD bit restores power to the associated control and status registers, thereby setting those registers to their default values.

# 3.7 Register Definitions: Peripheral Module Disable

# REGISTER 3-1: PMD0: PERIPHERAL MODULE DISABLE REGISTER 0

| R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|---------|--------|--------|--------|--------|--------|--------|

| UART2MD | UART1MD | TMR6MD | TMR5MD | TMR4MD | TMR3MD | TMR2MD | TMR1MD |

| bit 7   | ·       |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                                     |                    |  |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |  |

| bit 7 | UART2MD: UART2 Peripheral Module Disable Control bit                                                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 6 | UART1MD: UART1 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 5 | TMR6MD: Timer6 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 4 | TMR5MD: Timer5 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 3 | TMR4MD: Timer4 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 2 | TMR3MD: Timer3 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 1 | TMR2MD: Timer2 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 0 | TMR1MD: Timer1 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

|       |                                                                                                                                                                                                    |

# PIC18(L)F2X/4XK22

| dress<br>F5Fh<br>F5Eh<br>F5Dh<br>F5Ch<br>F5Bh<br>F58h<br>F57h<br>F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F54h | Name<br>CCPR3H<br>CCPR3L<br>CCP3CON<br>PWM3CON<br>ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCPR4L<br>CCPR5H<br>CCPR5H<br>CCPR5L<br>CCP5CON |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| F5Eh<br>F5Dh<br>F5Ch<br>F5Bh<br>F58h<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F55h<br>F54h<br>F53h          | CCPR3L<br>CCP3CON<br>PWM3CON<br>ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                       |

| F5Dh<br>F5Ch<br>F5Bh<br>F5Ah<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F53h                          | CCP3CON<br>PWM3CON<br>ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                 |

| F5Ch<br>F5Bh<br>F5Ah<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F53h                                  | PWM3CON<br>ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                            |

| F5Bh<br>F5Ah<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F55h<br>F54h                                          | ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                                       |

| F5Ah<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F55h<br>F53h                                                  | PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                                                  |

| F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F53h                                                          | CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                                                              |

| F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F53h                                                                  | CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                                                                        |

| F57h<br>F56h<br>F55h<br>F54h<br>F53h                                                                          | CCP4CON<br>CCPR5H<br>CCPR5L                                                                                                                  |

| F56h<br>F55h<br>F54h<br>F53h                                                                                  | CCPR5H<br>CCPR5L                                                                                                                             |

| F55h<br>F54h<br>F53h                                                                                          | CCPR5L                                                                                                                                       |

| F54h<br>F53h                                                                                                  |                                                                                                                                              |

| F53h                                                                                                          | CCF5CON                                                                                                                                      |

|                                                                                                               | TMR4                                                                                                                                         |

| EEDh                                                                                                          | PR4                                                                                                                                          |

| F52h<br>F51h                                                                                                  | T4CON                                                                                                                                        |

|                                                                                                               | T4CON<br>TMR5H                                                                                                                               |

|                                                                                                               | TMR5L                                                                                                                                        |

|                                                                                                               | T5CON                                                                                                                                        |

|                                                                                                               | T5GCON                                                                                                                                       |

|                                                                                                               | TMR6                                                                                                                                         |

|                                                                                                               | PR6                                                                                                                                          |

|                                                                                                               | T6CON                                                                                                                                        |

|                                                                                                               | CCPTMRS0                                                                                                                                     |

|                                                                                                               | CCPTMRS1                                                                                                                                     |

|                                                                                                               | SRCON0                                                                                                                                       |

|                                                                                                               | SRCON1                                                                                                                                       |

|                                                                                                               | CTMUCONH                                                                                                                                     |

|                                                                                                               | CTMUCONL                                                                                                                                     |

|                                                                                                               | CTMUICON                                                                                                                                     |

|                                                                                                               | VREFCON0                                                                                                                                     |

|                                                                                                               | VREFCON1                                                                                                                                     |

| F40h                                                                                                          | VREFCON2                                                                                                                                     |

| F3Fh                                                                                                          | PMD0                                                                                                                                         |

| F3Eh                                                                                                          | PMD1                                                                                                                                         |

| F3Dh                                                                                                          | PMD2                                                                                                                                         |

| F3Ch                                                                                                          | ANSELE                                                                                                                                       |

| F3Bh                                                                                                          | ANSELD                                                                                                                                       |

| F3Ah                                                                                                          | ANSELC                                                                                                                                       |

| F39h                                                                                                          | ANSELB                                                                                                                                       |

| F38h                                                                                                          | ANSELA                                                                                                                                       |

|                                                                                                               | F3Fh<br>F3Eh<br>F3Dh<br>F3Ch<br>F3Bh<br>F3Ah<br>F39h                                                                                         |

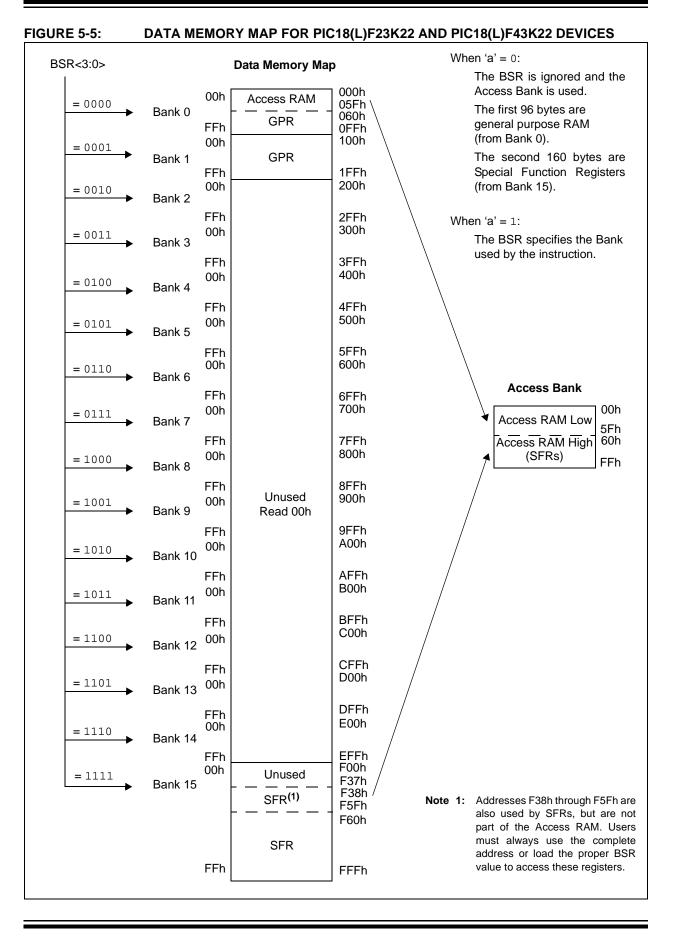

# TABLE 5-1: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F2X/4XK22 DEVICES

**Note 1:** This is not a physical register.

2: Unimplemented registers are read as '0'.

3: PIC18(L)F4XK22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

A mismatch condition will continue to set the RBIF flag bit. Reading or writing PORTB will end the mismatch condition and allow the RBIF bit to be cleared. The latch holding the last read value is not affected by a MCLR nor Brown-out Reset. After either one of these Resets, the RBIF flag will continue to be set if a mismatch is present.

Note: If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set. Furthermore, since a read or write on a port affects all bits of that port, care must be taken when using multiple pins in Interrupt-on-change mode. Changes on one pin may not be seen while servicing changes on another pin.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

# 10.3.3 ALTERNATE FUNCTIONS

PORTB is multiplexed with several peripheral functions (Table 10-5). The pins have TTL input buffers. Some of these pin functions can be relocated to alternate pins using the Control fuse bits in CONFIG3H. RB5 is the default pin for P2B (28-pin devices). Clearing the P2BMX bit moves the pin function to RC0. RB5 is also the default pin for the CCP3/P3A peripheral pin. Clearing the CCP3MX bit moves the pin function to the RC6 pin (28-pin devices) or RE0 (40/44-pin devices).

Two other pin functions, T3CKI and CCP2/P2A, can be relocated from their default pins to PORTB pins by clearing the control fuses in CONFIG3H. Clearing T3CMX and CCP2MX moves the pin functions to RB5 and RB3, respectively.

| Pin                        | Function            | TRIS<br>Setting | ANSEL<br>Setting | Pin<br>Type | Buffer<br>Type   | Description                                              |

|----------------------------|---------------------|-----------------|------------------|-------------|------------------|----------------------------------------------------------|

| RB0/INT0/CCP4/             | RB0                 | 0               | 0                | 0           | DIG              | LATB<0> data output; not affected by analog input.       |

| FLT0/SRI/SS2/<br>AN12      |                     | 1               | 0                | Ι           | TTL              | PORTB<0> data input; disabled when analog input enabled. |

|                            | INT0                | 1               | 0                | I           | ST               | External interrupt 0.                                    |

|                            | CCP4 <sup>(3)</sup> | 0               | 0                | 0           | DIG              | Compare 4 output/PWM 4 output.                           |

|                            |                     | 1               | 0                | I           | ST               | Capture 4 input.                                         |

|                            | FLT0                | 1               | 0                | I           | ST               | PWM Fault input for ECCP auto-shutdown.                  |

|                            | SRI                 | 1               | 0                | I           | ST               | SR latch input.                                          |

|                            | SS2 <sup>(3)</sup>  | 1               | 0                | I           | TTL              | SPI slave select input (MSSP2).                          |

|                            | AN12                | 1               | 1                | I           | AN               | Analog input 12.                                         |

| RB1/INT1/P1C/              | RB1                 | 0               | 0                | 0           | DIG              | LATB<1> data output; not affected by analog input.       |

| SCK2/SCL2/<br>C12IN3-/AN10 |                     | 1               | 0                | I           | TTL              | PORTB<1> data input; disabled when analog input enabled. |

|                            | INT1                | 1               | 0                | I           | ST               | External Interrupt 1.                                    |

|                            | P1C <sup>(3)</sup>  | 0               | 0                | 0           | DIG              | Enhanced CCP1 PWM output 3.                              |

|                            | SCK2 <sup>(3)</sup> | 0               | 0                | 0           | DIG              | MSSP2 SPI Clock output.                                  |

|                            |                     | 1               | 0                | I           | ST               | MSSP2 SPI Clock input.                                   |

|                            | SCL2 <sup>(3)</sup> | 0               | 0                | 0           | DIG              | MSSP2 I <sup>2</sup> C Clock output.                     |

|                            |                     | 1               | 0                | I           | l <sup>2</sup> C | MSSP2 I <sup>2</sup> C Clock input.                      |

|                            | C12IN3-             | 1               | 1                | I           | AN               | Comparators C1 and C2 inverting input.                   |

|                            | AN10                | 1               | 1                | I           | AN               | Analog input 10.                                         |

| TABLE 10-5: | PORTB I/O SUMMARY |

|-------------|-------------------|

| IADLE IV-J. |                   |

**Legend:** AN = Analog input or output; TTL = TTL compatible input;  $HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; <math>I^2C = Schmitt Trigger input with I^2C$ .

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

3: Function on PORTD and PORTE for PIC18(L)F4XK22 devices.

| R/W-0/u                                                                                  | R/W-0/u                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0/u                                                                   | R/W-0/u          | R/W/HC-0/u                                 | R-x/x           | R/W-0/u     | R/W-0/u    |  |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------|--------------------------------------------|-----------------|-------------|------------|--|

| TMRxGE                                                                                   | TxGPOL                                                                                                                                                                                                                                                                                                                                                                                            | TxGTM                                                                     | TxGSPM           | TxGGO/DONE                                 | TxGVAL          | TxGSS       | S<1:0>     |  |

| bit 7                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |                  |                                            |                 |             | bit 0      |  |

|                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |                  |                                            |                 |             |            |  |

| Legend:                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |                  |                                            |                 |             |            |  |

| R = Readable bit $W$ = Writable bit $U$ = Unimplemented bit, read as '0'                 |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |                  |                                            |                 |             |            |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other R |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |                  |                                            |                 |             | her Resets |  |

| '1' = Bit is set                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                   | '0' = Bit is clea                                                         | ared             | HC = Bit is clear                          | ed by hardwa    | re          |            |  |

| bit 7                                                                                    | If TMRxON =<br>This bit is ign<br>If TMRxON =<br>1 = Timer1/3                                                                                                                                                                                                                                                                                                                                     | <br>ored<br><u>1</u> :<br>/5 counting is c                                | controlled by th | ne Timer1/3/5 gate<br>r1/3/5 gate function |                 |             |            |  |

| bit 6                                                                                    | <b>TxGPOL:</b> Timer1/3/5 Gate Polarity bit<br>1 = Timer1/3/5 gate is active-high (Timer1/3/5 counts when gate is high)<br>0 = Timer1/3/5 gate is active-low (Timer1/3/5 counts when gate is low)                                                                                                                                                                                                 |                                                                           |                  |                                            |                 |             |            |  |

| bit 5                                                                                    | 1 = Timer1/3<br>0 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                      | er1/3/5 Gate To<br>/5 Gate Toggle<br>/5 Gate Toggle<br>ate flip-flop togg | mode is enab     | led<br>bled and toggle flip                | -flop is cleare | d           |            |  |

| bit 4                                                                                    | 1 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           | Pulse mode is    | enabled and is co                          | ontrolling Time | r1/3/5 gate |            |  |

| bit 3                                                                                    | <ul> <li>0 = Timer1/3/5 gate Single-Pulse mode is disabled</li> <li>TxGGO/DONE: Timer1/3/5 Gate Single-Pulse Acquisition Status bit</li> <li>1 = Timer1/3/5 gate single-pulse acquisition is ready, waiting for an edge</li> <li>0 = Timer1/3/5 gate single-pulse acquisition has completed or has not been started</li> <li>This bit is automatically cleared when TxGSPM is cleared.</li> </ul> |                                                                           |                  |                                            |                 |             |            |  |

| bit 2                                                                                    | <b>TxGVAL:</b> Timer1/3/5 Gate Current State bit<br>Indicates the current state of the Timer1/3/5 gate that could be provided to TMRxH:TMRxL.                                                                                                                                                                                                                                                     |                                                                           |                  |                                            |                 |             |            |  |

| bit 1-0                                                                                  | Unaffected by Timer1/3/5 Gate Enable (TMRxGE).<br><b>TxGSS&lt;1:0&gt;:</b> Timer1/3/5 Gate Source Select bits<br>00 = Timer1/3/5 Gate pin<br>01 = Timer2/4/6 Match PR2/4/6 output (See Table 12-5 for proper timer match selection)<br>10 = Comparator 1 optionally synchronized output (sync_C10UT)<br>11 = Comparator 2 optionally synchronized output (sync_C20UT)                             |                                                                           |                  |                                            |                 |             |            |  |

# REGISTER 12-2: TXGCON: TIMER1/3/5 GATE CONTROL REGISTER

| Name     | Bit 7    | Bit 6                                                    | Bit 5                       | Bit 4       | Bit 3       | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|----------------------------------------------------------|-----------------------------|-------------|-------------|--------|---------|---------|---------------------|

| CCPTMRS0 | C3TSE    | C3TSEL<1:0> — C2TSEL<1:0> — C1TSEL<1:0>                  |                             |             |             |        | EL<1:0> | 201     |                     |

| CCPTMRS1 | _        | —                                                        | — — C5TSEL<1:0> C4TSEL<1:0> |             |             |        |         |         | 201                 |

| INTCON   | GIE/GIEH | PEIE/GIEL                                                | TMR0IE                      | INT0IE      | RBIE        | TMR0IF | INT0IF  | RBIF    | 109                 |

| IPR1     | _        | ADIP                                                     | RC1IP                       | TX1IP       | SSP1IP      | CCP1IP | TMR2IP  | TMR1IP  | 121                 |

| IPR5     | _        | _                                                        | _                           | _           | _           | TMR6IP | TMR5IP  | TMR4IP  | 124                 |

| PIE1     | _        | ADIE                                                     | RC1IE                       | TX1IE       | SSP1IE      | CCP1IE | TMR2IE  | TMR1IE  | 117                 |

| PIE5     | _        | _                                                        |                             | _           | _           | TMR6IE | TMR5IE  | TMR4IE  | 120                 |

| PIR1     | _        | ADIF                                                     | RC1IF                       | TX1IF       | SSP1IF      | CCP1IF | TMR2IF  | TMR1IF  | 112                 |

| PIR5     | _        | _                                                        |                             | _           | _           | TMR6IF | TMR5IF  | TMR4IF  | 116                 |

| PMD0     | UART2MD  | ART2MD UART1MD TMR6MD TMR5MD TMR4MD TMR3MD TMR2MD TMR1MD |                             |             |             |        |         | 52      |                     |

| PR2      |          |                                                          | -                           | Timer2 Peri | od Register |        |         |         | —                   |

| PR4      |          |                                                          | -                           | Timer4 Peri | od Register |        |         |         | —                   |

| PR6      |          |                                                          | -                           | Timer6 Peri | od Register |        |         |         | _                   |

| T2CON    | _        |                                                          | T2OUTPS                     | S<3:0>      |             | TMR2ON | T2CK    | PS<1:0> | 166                 |

| T4CON    |          |                                                          | T4OUTPS                     | S<3:0>      |             | TMR4ON | T4CK    | PS<1:0> | 166                 |

| T6CON    |          | T6OUTPS<3:0> TMR6ON T6CKPS<1:0>                          |                             |             |             |        | PS<1:0> | 166     |                     |

| TMR2     |          |                                                          |                             | Timer2      | Register    |        |         |         | _                   |

| TMR4     |          |                                                          |                             | Timer4 I    | Register    |        |         |         | —                   |

| TMR6     |          |                                                          |                             | Timer6 I    | Register    |        |         |         | —                   |

# TABLE 13-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2/4/6

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by Timer2/4/6.

# 14.1 Capture Mode

The Capture mode function described in this section is identical for all CCP and ECCP modules available on this device family.

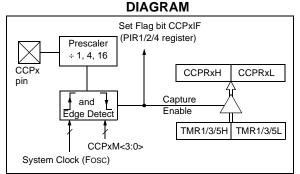

Capture mode makes use of the 16-bit Timer resources, Timer1, Timer3 and Timer5. The timer resources for each CCP capture function are independent and are selected using the CCPTMRS0 and CCPTMRS1 registers. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMRxH:TMRxL register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the corresponding Interrupt Request Flag bit CCPxIF of the PIR1, PIR2 or PIR4 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH:CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

# TABLE 14-2: CCP PIN MULTIPLEXING

Figure 14-1 shows a simplified diagram of the Capture operation.

FIGURE 14-1:

# CAPTURE MODE OPERATION BLOCK

# 14.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Some CCPx outputs are multiplexed on a couple of pins. Table 14-2 shows the CCP output pin multiplexing. Selection of the output pin is determined by the CCPxMX bits in Configuration register 3H (CONFIG3H). Refer to Register 24-4 for more details.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

| CCP OUTPUT | CONFIG 3H Control Bit | Bit Value | PIC18(L)F2XK22 I/O pin | PIC18(L)F4XK22 I/O pin |

|------------|-----------------------|-----------|------------------------|------------------------|

| CCP2       | CCP2MX                | 0         | RB3                    | RB3                    |

| CCP2       | CCPZIVIX              | 1(*)      | RC1                    | RC1                    |

| CCD2       | ССРЗМХ                | 0(*)      | RC6                    | RE0                    |

| CCP3       | CCP3IVIA              | 1         | RB5                    | RB5                    |

Legend: \* = Default

#### 14.1.2 TIMER1 MODE RESOURCE

The 16-bit Timer resource must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 12.0 "Timer1/3/5 Module with Gate Control" for more information on configuring the 16-bit Timers.

#### 14.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIE1, PIE2 or PIE4 register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIR1, PIR2 or PIR4 register following any change in Operating mode.

Note: Clocking the 16-bit Timer resource from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, the Timer resource must be clocked from the instruction clock (Fosc/4) or from an external clock source.

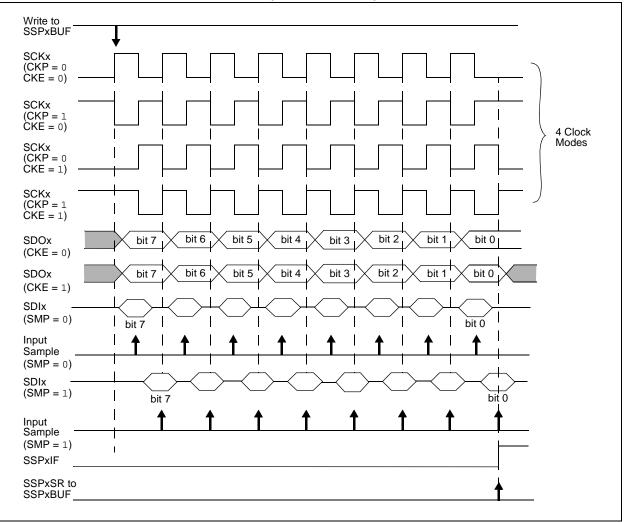

### 15.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCKx line. The master determines when the slave (Processor 2, Figure 15-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPxBUF register is written to. If the SPI is only going to receive, the SDOx output could be disabled (programmed as an input). The SSPxSR register will continue to shift in the signal present on the SDIx pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPxBUF register as if a normal received byte (interrupts and Status bits appropriately set).

The clock polarity is selected by appropriately programming the CKP bit of the SSPxCON1 register and the CKE bit of the SSPxSTAT register.

This then, would give waveforms for SPI communication as shown in Figure 15-6, Figure 15-8, Figure 15-9 and Figure 15-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPxADD + 1))

Figure 15-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDOx data is valid before there is a clock edge on SCKx. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPxBUF is loaded with the received data is shown.

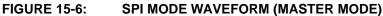

#### 15.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN, of the SSPxCON2 register. When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSPx module then goes into Idle mode (Figure 15-30).

# 15.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write does not occur).

# 15.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN, of the SSPxCON2 register. At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 15-31).

# 15.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

# FIGURE 15-30: ACKNOWLEDGE SEQUENCE WAVEFORM

# 19.3.2 CAPACITANCE CALIBRATION

There is a small amount of capacitance from the internal A/D Converter sample capacitor as well as stray capacitance from the circuit board traces and pads that affect the precision of capacitance measurements. A measurement of the stray capacitance can be taken by making sure the desired capacitance to be measured has been removed. The measurement is then performed using the following steps:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT (= 1).

- 3. Wait for a fixed delay of time *t*.

- 4. Clear EDG1STAT.

- 5. Perform an A/D conversion.

- 6. Calculate the stray and A/D sample capacitances:

$$C_{\text{OFFSET}} = C_{\text{STRAY}} + C_{\text{AD}} = (I \cdot t) / V$$

where *I* is known from the current source measurement step, *t* is a fixed delay and *V* is measured by performing an A/D conversion.

This measured value is then stored and used for calculations of time measurement or subtracted for capacitance measurement. For calibration, it is expected that the capacitance of CSTRAY + CAD is approximately known. CAD is approximately 4 pF.

An iterative process may need to be used to adjust the time, t, that the circuit is charged to obtain a reasonable voltage reading from the A/D Converter. The value of t may be determined by setting COFFSET to a theoretical value, then solving for t. For example, if CSTRAY is theoretically calculated to be 11 pF, and V is expected to be 70% of VDD, or 2.31V, then t would be:

or 63 µs.

See Example 19-3 for a typical routine for CTMU capacitance calibration.

# PIC18(L)F2X/4XK22

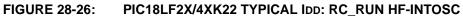

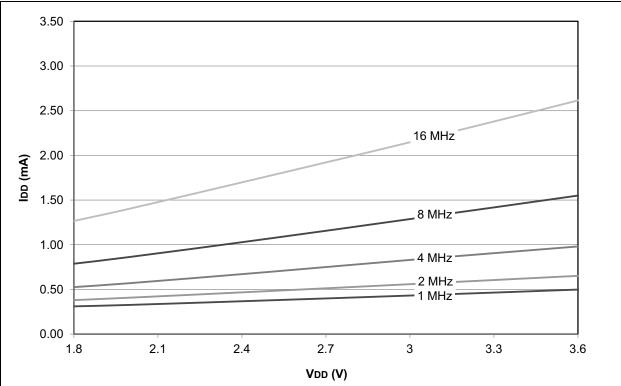

FIGURE 28-27: PIC18LF2X/4XK22 MAXIMUM IDD: RC\_RUN HF-INTOSC

© 2010-2016 Microchip Technology Inc.

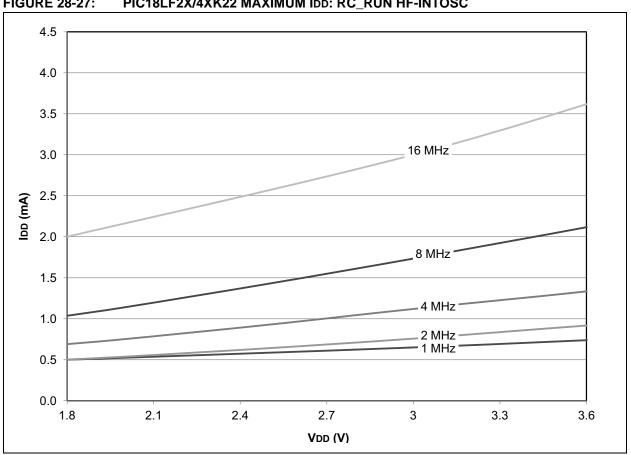

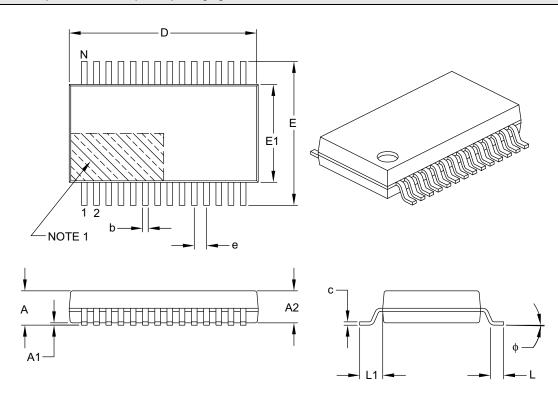

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     | MILLIMETERS |          |      |  |

|--------------------------|-----------|-------------|----------|------|--|

| Dimension                | Limits    | MIN         | NOM      | MAX  |  |

| Number of Pins           | N         |             | 28       |      |  |

| Pitch                    | е         |             | 1.27 BSC |      |  |

| Overall Height           | A         | I           | -        | 2.65 |  |

| Molded Package Thickness | A2        | 2.05        | -        | -    |  |

| Standoff §               | A1        | 0.10        | -        | 0.30 |  |

| Overall Width            | E         | 10.30 BSC   |          |      |  |

| Molded Package Width     | E1        | 7.50 BSC    |          |      |  |

| Overall Length           | D         | 17.90 BSC   |          |      |  |

| Chamfer (Optional)       | h         | 0.25        | -        | 0.75 |  |

| Foot Length              | L         | 0.40        | -        | 1.27 |  |

| Footprint                | L1        |             | 1.40 REF |      |  |

| Lead Angle               | Θ         | 0°          | -        | -    |  |

| Foot Angle               | $\varphi$ | 0°          | -        | 8°   |  |

| Lead Thickness           | С         | 0.18        | -        | 0.33 |  |

| Lead Width               | b         | 0.31        | -        | 0.51 |  |

| Mold Draft Angle Top     | α         | 5°          | -        | 15°  |  |

| Mold Draft Angle Bottom  | β         | 5°          | -        | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS |       |  |

|--------------------------|------------------|----------|-------------|-------|--|

| Dimension                | Dimension Limits |          | NOM         | MAX   |  |

| Number of Pins           | Ν                | 28       |             |       |  |

| Pitch                    | е                | 0.65 BSC |             |       |  |

| Overall Height           | Α                | —        | -           | 2.00  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75        | 1.85  |  |

| Standoff                 | A1               | 0.05     | -           | -     |  |

| Overall Width            | Е                | 7.40     | 7.80        | 8.20  |  |

| Molded Package Width     | E1               | 5.00     | 5.30        | 5.60  |  |

| Overall Length           | D                | 9.90     | 10.20       | 10.50 |  |

| Foot Length              | L                | 0.55     | 0.75        | 0.95  |  |

| Footprint                | L1               | 1.25 REF |             |       |  |

| Lead Thickness           | с                | 0.09     | -           | 0.25  |  |

| Foot Angle               | ¢                | 0°       | 4°          | 8°    |  |

| Lead Width               | b                | 0.22     | -           | 0.38  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | MILLIMETERS |      |      |

|-------------------------|--------|-------------|------|------|

| Dimension               | Limits | MIN         | NOM  | MAX  |

| Number of Pins          | Z      | 28          |      |      |

| Pitch                   | е      | 0.65 BSC    |      |      |

| Overall Height          | A      | 0.80        | 0.90 | 1.00 |

| Standoff                | A1     | 0.00        | 0.02 | 0.05 |

| Terminal Thickness      | A3     | 0.20 REF    |      |      |

| Overall Width           | Ш      | 6.00 BSC    |      |      |

| Exposed Pad Width       | E2     | 3.65        | 3.70 | 4.20 |

| Overall Length          | D      | 6.00 BSC    |      |      |

| Exposed Pad Length      | D2     | 3.65        | 3.70 | 4.20 |

| Terminal Width          | b      | 0.23        | 0.30 | 0.35 |

| Terminal Length         | L      | 0.50        | 0.55 | 0.70 |

| Terminal-to-Exposed Pad | K      | 0.20        | -    | -    |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2

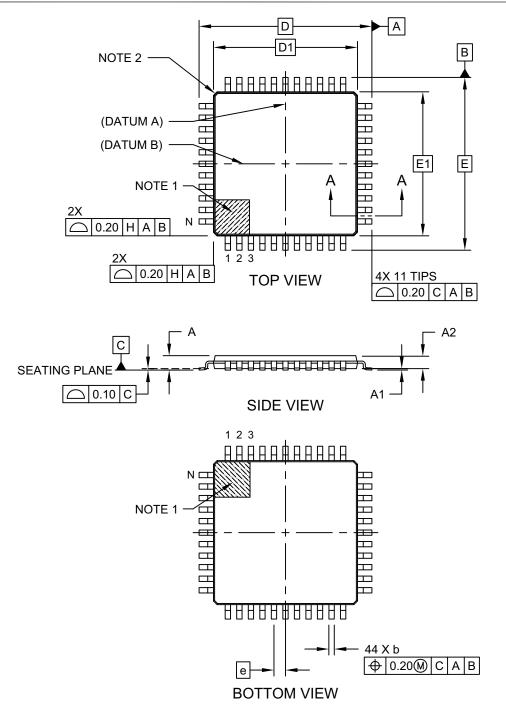

# 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

Microchip Technology Drawing C04-076C Sheet 1 of 2

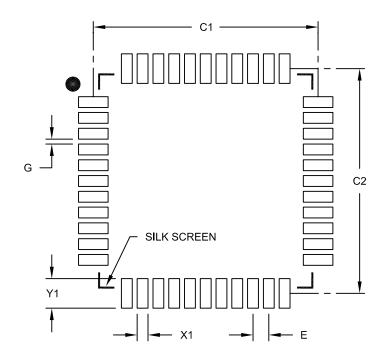

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units | Units MILLIMETERS |          | S    |  |

|--------------------------|-------|-------------------|----------|------|--|

| Dimension Limits         |       | MIN               | NOM      | MAX  |  |

| Contact Pitch            | E     |                   | 0.80 BSC |      |  |

| Contact Pad Spacing      | C1    |                   | 11.40    |      |  |

| Contact Pad Spacing      | C2    |                   | 11.40    |      |  |

| Contact Pad Width (X44)  | X1    |                   |          | 0.55 |  |

| Contact Pad Length (X44) | Y1    |                   |          | 1.50 |  |

| Distance Between Pads    | G     | 0.25              |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL00® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

$\textcircled{\mbox{\sc op}}$  2010-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0907-6