Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

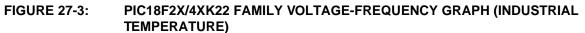

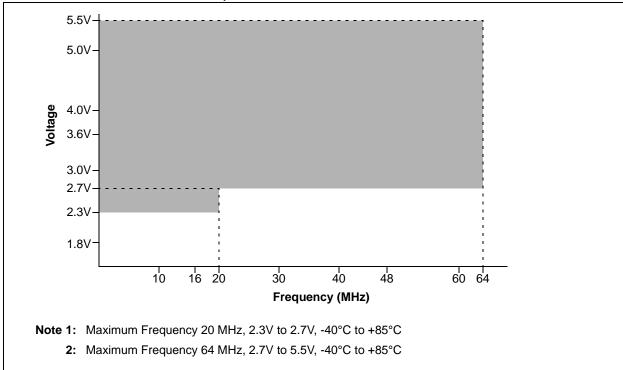

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 30x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f44k22t-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Nu        | ımber        |                                 |             |                |                                                                                                               |

|---------------|--------------|---------------------------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------|

| PDIP,<br>SOIC | QFN,<br>UQFN | Pin Name                        | Pin<br>Type | Buffer<br>Type | Description                                                                                                   |

| 9             | 6            | RA7/CLKI/OSC1                   |             |                |                                                                                                               |

|               |              | RA7                             | I/O         | TTL            | Digital I/O.                                                                                                  |

|               |              | CLKI                            | Ι           | CMOS           | External clock source input. Always associated with pin function OSC1.                                        |

|               |              | OSC1                            | Ι           | ST             | Oscillator crystal input or external clock source input ST buffer when configured in RC mode; CMOS otherwise. |

| 21            | 18           | RB0/INT0/CCP4/FLT0/SRI/SS2/AN12 | 2           |                |                                                                                                               |

|               |              | RB0                             | I/O         | TTL            | Digital I/O.                                                                                                  |

|               |              | ΙΝΤΟ                            | I           | ST             | External interrupt 0.                                                                                         |

|               |              | CCP4                            | I/O         | ST             | Capture 4 input/Compare 4 output/PWM 4 output.                                                                |

|               |              | FLTO                            | I           | ST             | PWM Fault input for ECCP Auto-Shutdown.                                                                       |

|               |              | SRI                             | I           | ST             | SR latch input.                                                                                               |

|               |              | SS2                             | 1           | TTL            | SPI slave select input (MSSP).                                                                                |

|               |              | AN12                            | I           | Analog         | Analog input 12.                                                                                              |

| 22            | 19           | RB1/INT1/P1C/SCK2/SCL2/C12IN3-/ | 'AN10       |                |                                                                                                               |

|               |              | RB1                             | I/O         | TTL            | Digital I/O.                                                                                                  |

|               |              | INT1                            | Ι           | ST             | External interrupt 1.                                                                                         |

|               |              | P1C                             | 0           | CMOS           | Enhanced CCP1 PWM output.                                                                                     |

|               |              | SCK2                            | I/O         | ST             | Synchronous serial clock input/output for SPI mode (MSSP).                                                    |

|               |              | SCL2                            | I/O         | ST             | Synchronous serial clock input/output for I <sup>2</sup> C mode (MSSP).                                       |

|               |              | C12IN3-                         | Ι           | Analog         | Comparators C1 and C2 inverting input.                                                                        |

|               |              | AN10                            | Ι           | Analog         | Analog input 10.                                                                                              |

| 23            | 20           | RB2/INT2/CTED1/P1B/SDI2/SDA2/A  | N8          |                |                                                                                                               |

|               |              | RB2                             | I/O         | TTL            | Digital I/O.                                                                                                  |

|               |              | INT2                            | Ι           | ST             | External interrupt 2.                                                                                         |

|               |              | CTED1                           | Ι           | ST             | CTMU Edge 1 input.                                                                                            |

|               |              | P1B                             | 0           | CMOS           | Enhanced CCP1 PWM output.                                                                                     |

|               |              | SDI2                            | Ι           | ST             | SPI data in (MSSP).                                                                                           |

|               |              | SDA2                            | I/O         | ST             | I <sup>2</sup> C data I/O (MSSP).                                                                             |

|               |              | AN8                             | I           | Analog         | Analog input 8.                                                                                               |

| 24            | 21           | RB3/CTED2/P2A/CCP2/SDO2/C12IN   | 2-/AN9      | )              |                                                                                                               |

|               |              | RB3                             | I/O         | TTL            | Digital I/O.                                                                                                  |

|               |              | CTED2                           | Т           | ST             | CTMU Edge 2 input.                                                                                            |

|               |              | P2A                             | 0           | CMOS           | Enhanced CCP2 PWM output.                                                                                     |

|               |              | CCP2 <sup>(2)</sup>             | I/O         | ST             | Capture 2 input/Compare 2 output/PWM 2 output.                                                                |

|               |              | SDO2                            | 0           | —              | SPI data out (MSSP).                                                                                          |

|               |              | C12IN2-                         | I           | Analog         | Comparators C1 and C2 inverting input.                                                                        |

|               |              | AN9                             | I           | Analog         | Analog input 9.                                                                                               |

| l edend.      |              |                                 |             |                | t or output: ST - Schmitt Trigger input with CMOS levels:                                                     |

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

#### 2.4 Clock Source Modes

Clock Source modes can be classified as external or internal.

- External Clock modes rely on external circuitry for the clock source. Examples are: Clock modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC mode) circuits.

- Internal clock sources are contained internally within the Oscillator block. The Oscillator block has three internal oscillators: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz Medium-Frequency Internal Oscillator (MFINTOSC) and the 31.25 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS<1:0>) bits of the OSCCON register. See **Section 2.11 "Clock Switching"** for additional information.

#### 2.5 External Clock Modes

#### 2.5.1 OSCILLATOR START-UP TIMER (OST)

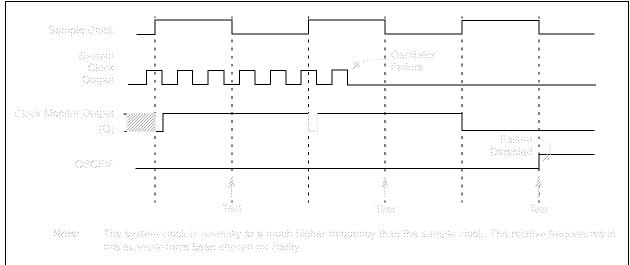

When the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module. When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 2-2.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see **Section 2.12 "Two-Speed Clock Start-up Mode"**).

| TABLE 2-2. USCILLA   | TOR DELAT LAA                    |                                                          |                                      |

|----------------------|----------------------------------|----------------------------------------------------------|--------------------------------------|

| Switch From          | Switch To                        | Frequency                                                | Oscillator Delay                     |

| Sleep/POR/BOR        | LFINTOSC<br>MFINTOSC<br>HFINTOSC | 31.25 kHz<br>31.25 kHz to 500 kHz<br>31.25 kHz to 16 MHz | Oscillator Start-up Delay (Tiosc_st) |

| Sleep/POR/BOR        | EC, RC                           | DC – 64 MHz                                              | 2 instruction cycles                 |

| LFINTOSC (31.25 kHz) | EC, RC                           | DC – 64 MHz                                              | 1 cycle of each                      |

| Sleep/POR/BOR        | LP, XT, HS                       | 32 kHz to 40 MHz                                         | 1024 Clock Cycles (OST)              |

| Sleep/POR/BOR        | 4xPLL                            | 32 MHz to 64 MHz                                         | 1024 Clock Cycles (OST) + 2 ms       |

| LFINTOSC (31.25 kHz) | LFINTOSC<br>HFINTOSC             | 31.25 kHz to 16 MHz                                      | 1 μs (approx.)                       |

#### TABLE 2-2: OSCILLATOR DELAY EXAMPLES

#### 2.5.2 EC MODE

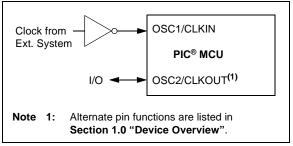

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 2-5 shows the pin connections for EC mode.

The External Clock (EC) offers different power modes, Low Power (ECLP), Medium Power (ECMP) and High Power (ECHP), selectable by the FOSC<3:0> bits. Each mode is best suited for a certain range of frequencies. The ranges are:

- ECLP below 500 kHz

- ECMP between 500 kHz and 16 MHz

- ECHP above 16 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep.

Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

#### 2.7.1 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a 31.25 kHz internal clock source. The LFINTOSC is not tunable, but is designed to be stable across temperature and voltage. See **Section 27.0 "Electrical Specifications"** for the LFINTOSC accuracy specifications.

The output of the LFINTOSC can be a clock source to the primary clock or the INTOSC clock (see Figure 2-1). The LFINTOSC is also the clock source for the Powerup Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

#### 2.7.2 FREQUENCY SELECT BITS (IRCF)

The HFINTOSC (16 MHz) and MFINTOSC (500 MHz) outputs connect to a divide circuit that provides frequencies of 16 MHz to 31.25 kHz. These divide circuit frequencies, along with the 31.25 kHz LFINTOSC output, are multiplexed to provide a single INTOSC clock output (see Figure 2-1). The IRCF<2:0> bits of the OSCCON register, the MFIOSEL bit of the OSCCON2 register and the INTSRC bit of the OSCTUNE register, select the output frequency of the internal oscillators. One of eight frequencies can be selected via software:

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz (default after Reset)

- 500 kHz (MFINTOSC or HFINTOSC)

- 250 kHz (MFINTOSC or HFINTOSC)

- 31 kHz (LFINTOSC, MFINTOSC or HFINTOSC)

#### 2.7.3 INTOSC FREQUENCY DRIFT

The factory calibrates the internal oscillator block outputs (HFINTOSC/MFINTOSC) for 16 MHz/500 kHz. However, this frequency may drift as VDD or temperature changes. It is possible to adjust the HFINTOSC/MFINTOSC frequency by modifying the value of the TUN<5:0> bits in the OSCTUNE register. This has no effect on the LFINTOSC clock source frequency.

Tuning the HFINTOSC/MFINTOSC source requires knowing when to make the adjustment, in which direction it should be made and, in some cases, how large a change is needed. Three possible compensation techniques are discussed in the following sections. However, other techniques may be used.

#### 2.7.3.1 Compensating with the EUSART

An adjustment may be required when the EUSART begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high; to adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low; to compensate, increment OSCTUNE to increase the clock frequency.

#### 2.7.3.2 Compensating with the Timers

This technique compares device clock speed to some reference clock. Two timers may be used; one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator.

Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

### 2.7.3.3 Compensating with the CCP Module in Capture Mode

A CCP module can use free running Timer1, Timer3 or Timer5 clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast; to compensate, decrement the OSCTUNE register. If the measured time is much less than the calculated time, the internal oscillator block is running too slow; to compensate, increment the OSCTUNE register.

TABLE 2-4: REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7    | Bit 6     | Bit 5     | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|----------|-----------|-----------|---------|---------|--------|--------|--------|---------------------|

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE    | INT0IE  | RBIE    | TMR0IF | INTOIF | RBIF   | 109                 |

| IPR2    | OSCFIP   | C1IP      | C2IP      | EEIP    | BCL1IP  | HLVDIP | TMR3IP | CCP2IP | 122                 |

| OSCCON  | IDLEN    |           | IRCF<2:0> |         | OSTS    | HFIOFS | SCS    | 30     |                     |

| OSCCON2 | PLLRDY   | SOSCRUN   | —         | MFIOSEL | SOSCGO  | PRISD  | MFIOFS | LFIOFS | 31                  |

| OSCTUNE | INTSRC   | PLLEN     |           |         | TUN<5:( | )>     |        |        | 35                  |

| PIE2    | OSCFIE   | C1IE      | C2IE      | EEIE    | BCL1IE  | HLVDIE | TMR3IE | CCP2IE | 118                 |

| PIR2    | OSCFIF   | C1IF      | C2IF      | EEIF    | BCL1IF  | HLVDIF | TMR3IF | CCP2IF | 113                 |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by clock sources.

TABLE 2-5: CONFIGURATION REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name     | Bit 7 | Bit 6 | Bit 5    | Bit 4  | Bit 4 Bit 3 |        | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------|-------|----------|--------|-------------|--------|--------|--------|---------------------|

| CONFIG1H | IESO  | FCMEN | PRICLKEN | PLLCFG |             | FOSC   | 345    |        |                     |

| CONFIG2L | —     | —     | _        | BOR∖   | /<1:0>      | BOREI  | N<1:0> | PWRTEN | 346                 |

| CONFIG3H | MCLRE | _     | P2BMX    | T3CMX  | HFOFST      | CCP3MX | PBADEN | CCP2MX | 348                 |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for clock sources.

|          | 00111 |       |       |       |        |            |        |        |                     |

|----------|-------|-------|-------|-------|--------|------------|--------|--------|---------------------|

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |

| CONFIG2L |       |       |       | BORV  | <1:0>  | BOREN<1:0> |        | PWRTEN | 346                 |

| CONFIG2H | _     | _     |       | WDPS  | 6<3:0> |            | WDTE   | 347    |                     |

| CONFIG3H | MCLRE | —     | P2BMX | T3CMX | HFOFST | CCP3MX     | PBADEN | CCP2MX | 348                 |

| CONFIG4L | DEBUG | XINST |       |       |        | LVP        |        | STRVEN | 349                 |

TABLE 4-5: CONFIGURATION REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for Resets.

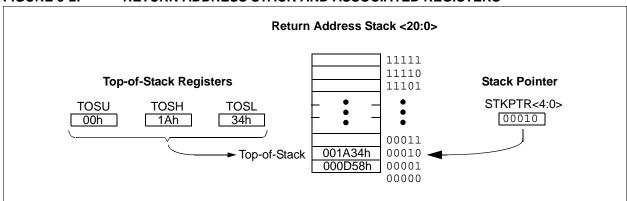

The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack (TOS) Special File Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full or has overflowed or has underflowed.

#### 5.1.2.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 5-2). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the Global Interrupt Enable (GIE) bits while accessing the stack to prevent inadvertent stack corruption.

#### FIGURE 5-2: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

#### 5.1.2.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 5-1) contains the Stack Pointer value, the STKFUL (stack full) Status bit and the STKUNF (Stack Underflow) Status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 24.1 "Configuration Bits"** for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31<sup>st</sup> push and STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

**Note:** Returning a value of zero to the PC on an underflow has the effect of vectoring the program to the Reset vector, where the stack conditions can be verified and appropriate actions can be taken. This is not the same as a Reset, as the contents of the SFRs are not affected.

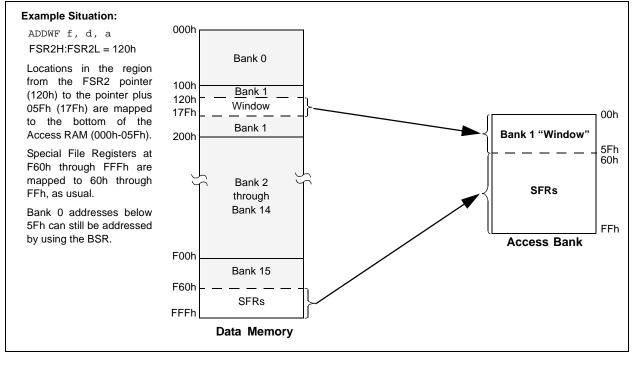

### 5.7.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the first 96 locations of Access RAM (00h to 5Fh) are mapped. Rather than containing just the contents of the bottom section of Bank 0, this mode maps the contents from a user defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see Section 5.4.2 "Access Bank"). An example of Access Bank remapping in this addressing mode is shown in Figure 5-12.

Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use direct addressing as before.

### 5.8 PIC18 Instruction Execution and the Extended Instruction Set

Enabling the extended instruction set adds eight additional commands to the existing PIC18 instruction set. These instructions are executed as described in **Section 25.2 "Extended Instruction Set"**.

#### FIGURE 5-12: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

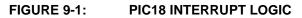

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

| Name     | Bit 7   | Bit 6  | Bit 5       | Bit 4               | Bit 3               | Bit 2     | Bit 1   | Bit 0  | Register<br>on Page |

|----------|---------|--------|-------------|---------------------|---------------------|-----------|---------|--------|---------------------|

| ANSELC   | ANSC7   | ANSC6  | ANSC5       | ANSC4               | ANSC3               | ANSC2     | —       |        | 150                 |

| ECCP1AS  | CCP1ASE |        | CCP1AS<2:0> |                     | PSS1A0              | C<1:0>    | PSS1B   | D<1:0> | 202                 |

| CCP1CON  | P1M<    | 1:0>   | DC1B<       | 1:0>                |                     | CCP1M<3:0 | )>      |        | 198                 |

| ECCP2AS  | CCP2ASE |        | CCP2AS<2:0> |                     | PSS2A0              | C<1:0>    | PSS2B   | D<1:0> | 202                 |

| CCP2CON  | P2M<    | 1:0>   | DC2B<       | 1:0>                |                     | CCP2M<3:0 | )>      |        | 198                 |

| CTMUCONH | CTMUEN  |        | CTMUSIDL    | TGEN                | EDGEN               | EDGSEQEN  | IDISSEN | CTTRIG | 323                 |

| LATC     | LATC7   | LATC6  | LATC5       | LATC4               | LATC3               | LATC2     | LATC1   | LATC0  | 152                 |

| PORTC    | RC7     | RC6    | RC5         | RC4                 | RC3                 | RC2       | RC1     | RC0    | 148                 |

| RCSTA1   | SPEN    | RX9    | SREN        | CREN                | ADDEN               | FERR      | OERR    | RX9D   | 270                 |

| SLRCON   | _       |        | _           | SLRE <sup>(1)</sup> | SLRD <sup>(1)</sup> | SLRC      | SLRB    | SLRA   | 153                 |

| SSP1CON1 | WCOL    | SSPOV  | SSPEN       | CKP                 |                     | SSPM<3:0  | 253     |        |                     |

| T1CON    | TMR1CS  | 5<1:0> | T1CKPS      | <1:0>               | T1SOSCEN            | T1SYNC    | T1RD16  | TMR10N | 166                 |

| T3CON    | TMR3CS  | 5<1:0> | T3CKPS-     | <1:0>               | T3SOSCEN            | T3SYNC    | T3RD16  | TMR3ON | 166                 |

| T3GCON   | TMR3GE  | T3GPOL | T3GTM       | T3GSPM              | T3GGO/DONE          | T3GVAL    | T3GS    | S<1:0> | 167                 |

| T5CON    | TMR5CS  | 5<1:0> | T5CKPS      | T5CKPS<1:0>         |                     | T5SYNC    | T5RD16  | TMR5ON | 166                 |

| TRISC    | TRISC7  | TRISC6 | TRISC5      | TRISC4              | TRISC3              | TRISC2    | TRISC1  | TRISC0 | 151                 |

| TXSTA1   | CSRC    | TX9    | TXEN        | SYNC                | SENDB               | BRGH      | TRMT    | TX9D   | 269                 |

#### TABLE 10-9: REGISTERS ASSOCIATED WITH PORTC

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for PORTC.

**Note 1:** Available on PIC18(L)F4XK22 devices.

#### TABLE 10-10: CONFIGURATION REGISTERS ASSOCIATED WITH PORTC

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| CONFIG3H | MCLRE | —     | P2BMX | T3CMX | HFOFST | CCP3MX | PBADEN | CCP2MX | 348                 |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTC.

#### TABLE 10-11: PORTD I/O SUMMARY

| Pin Name            | Function           | TRIS<br>Setting | ANSEL setting | Pin<br>Type | Buffer<br>Type   | Description                                              |

|---------------------|--------------------|-----------------|---------------|-------------|------------------|----------------------------------------------------------|

| RD0/SCK2/SCL2/AN20  | RD0                | 0               | 0             | 0           | DIG              | LATD<0> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<0> data input; disabled when analog input enabled. |

|                     | SCK2               | 0               | 0             | 0           | DIG              | MSSP2 SPI Clock output.                                  |

|                     |                    | 1               | 0             | I           | ST               | MSSP2 SPI Clock input.                                   |

|                     | SCL2               | 0               | 0             | 0           | DIG              | MSSP2 I <sup>2</sup> C Clock output.                     |

|                     |                    | 1               | 0             | I           | l <sup>2</sup> C | MSSP2 I <sup>2</sup> C Clock input.                      |

|                     | AN20               | 1               | 1             | I           | AN               | Analog input 20.                                         |

| RD1/CCP4/SDI2/SDA2/ | RD1                | 0               | 0             | 0           | DIG              | LATD<1> data output; not affected by analog input.       |

| AN21                |                    | 1               | 0             | I           | ST               | PORTD<1> data input; disabled when analog input enabled. |

|                     | CCP4               | 0               | 0             | 0           | DIG              | Compare 4 output/PWM 4 output.                           |

|                     |                    | 1               | 0             | I           | ST               | Capture 4 input.                                         |

|                     | SDI2               | 1               | 0             | I           | ST               | MSSP2 SPI data input.                                    |

|                     | SDA2               | 0               | 0             | 0           | DIG              | MSSP2 I <sup>2</sup> C data output.                      |

|                     |                    | 1               | 0             | I           | l <sup>2</sup> C | MSSP2 I <sup>2</sup> C data input.                       |

|                     | AN21               | 1               | 1             | I           | AN               | Analog input 21.                                         |

| RD2/P2B/AN22        | RD2                | 0               | 0             | 0           | DIG              | LATD<2> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<2> data input; disabled when analog input enabled. |

|                     | P2B <sup>(1)</sup> | 0               | 0             | 0           | DIG              | Enhanced CCP2 PWM output 2.                              |

|                     | AN22               | 1               | 1             | I           | AN               | Analog input 22.                                         |

| RD3/P2C/SS2/AN23    | RD3                | 0               | 0             | 0           | DIG              | LATD<3> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<3> data input; disabled when analog input enabled. |

|                     | P2C                | 0               | 0             | 0           | DIG              | Enhanced CCP2 PWM output 4.                              |

|                     | SS2                | 1               | 0             | I           | TTL              | MSSP2 SPI slave select input.                            |

|                     | AN23               | 1               | 1             | I           | AN               | Analog input 23.                                         |

| RD4/P2D/SDO2/AN24   | RD4                | 0               | 0             | 0           | DIG              | LATD<4> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<4> data input; disabled when analog input enabled. |

|                     | P2D                | 0               | 0             | 0           | DIG              | Enhanced CCP2 PWM output 3.                              |

|                     | SDO2               | 0               | 0             | 0           | DIG              | MSSP2 SPI data output.                                   |

|                     | AN24               | 1               | 1             | I           | AN               | Analog input 24.                                         |

| RD5/P1B/AN25        | RD5                | 0               | 0             | 0           | DIG              | LATD<5> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<5> data input; disabled when analog input enabled. |

|                     | P1B                | 0               | 0             | 0           | DIG              | Enhanced CCP1 PWM output 2.                              |

|                     | AN25               | 1               | 1             | I           | AN               | Analog input 25.                                         |

**Legend:** AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;  $I^2C$  = Schmitt Trigger input with  $I^2C$ .

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

| FIGURE 15-9:                               | SPI N            | IODE W                                                 | /AVEFO                | RM (SL                | AVE MC                                                 | DE WIT                                           | HCKE                            | = 0)                                             |                        |            |                                       |

|--------------------------------------------|------------------|--------------------------------------------------------|-----------------------|-----------------------|--------------------------------------------------------|--------------------------------------------------|---------------------------------|--------------------------------------------------|------------------------|------------|---------------------------------------|

|                                            | \<br>\           |                                                        |                       |                       |                                                        |                                                  |                                 |                                                  |                        |            | <br><br>                              |

|                                            | 2<br>2<br>2<br>2 |                                                        |                       |                       |                                                        |                                                  | -<br>                           |                                                  |                        |            | ·<br>·<br>·<br>·                      |

| - 50%x<br>- (CKF = 0,<br>- CKF = 0)        | ·                |                                                        |                       |                       |                                                        |                                                  |                                 |                                                  |                        |            | 3<br>                                 |

| 980908-00<br>SURPARATE<br>VIREA            | •                |                                                        | 2<br>2<br>2<br>2<br>4 | 2<br>5<br>5<br>5<br>7 | 4<br>6<br>5<br>6<br>                                   | ·<br>·<br>·<br>· · · · · · · · · · · · · · · · · | 2<br>2<br>2<br>2<br>2<br>2<br>2 | ·<br>·<br>·<br>· · · · · · · · · · · · · · · · · | <pre>&lt;</pre>        |            | •<br>•<br>•<br>•<br>•                 |

| - \$5X0x<br>- \$50%                        |                  | 1. 232. 7<br>                                          |                       |                       | 1933 4.<br>                                            | × 88.3                                           | 7. 394. 2.                      | /                                                |                        | 68 0<br>Ma | · · · · · · · · · · · · · · · · · · · |

| incuá<br>Secoles                           |                  | - 1997<br>- 1995 - 7<br>- 1996 - 1997<br>- 1996 - 1997 |                       |                       |                                                        | , "//////<br>. 4, .                              |                                 |                                                  |                        | ////<br>-3 | ·<br>·                                |

| - SSPXH                                    |                  |                                                        | 2                     |                       | (                                                      | ·                                                | 2                               |                                                  | 5                      |            |                                       |

| inierrup:<br>Pieg<br>SSPXSR to<br>SSPXSR)F | •                | ·<br>·<br>·                                            | 2<br>2<br>2<br>2      | <br>2<br>2<br>2       | \$<br>5<br>5<br>5<br>• • • • • • • • • • • • • • • • • | ·<br>·<br>·<br>·                                 | 2                               |                                                  | 6<br>6 5<br>6 5<br>5 5 | :<br>//p.  |                                       |

| Varias Codiscon<br>detection activa        |                  |                                                        |                       |                       |                                                        |                                                  |                                 |                                                  | . ,                    |            | ~~                                    |

#### FIGURE 15-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

|                                     |                       |                       |                  |                       |                  |                       |                       | /                |       |                       |  |

|-------------------------------------|-----------------------|-----------------------|------------------|-----------------------|------------------|-----------------------|-----------------------|------------------|-------|-----------------------|--|

| SSx<br>Nex Optional                 |                       |                       |                  |                       |                  |                       |                       |                  |       | /                     |  |

| SCKx<br>(CKP = <u>0</u><br>CKE = 1) | ,<br>,<br>,<br>,<br>, |                       |                  |                       |                  |                       |                       |                  |       |                       |  |

| SCKx<br>(CKP = 1<br>CKE = 1)        | ;<br>;<br>;<br>;      |                       |                  |                       |                  |                       |                       |                  |       |                       |  |

| Write to<br>SSPxBUF                 | <br> <br> <br>        | 1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 | <br> <br> <br> <br>   | <br> <br> <br>   | <br> <br> <br> <br>   | 1<br>1<br>1<br>1      | <br> <br> <br>   |       |                       |  |

| SDOx                                | <u> </u>              | bit 7                 | bit 6            | bit 5                 | bit 4            | bit 3                 | bit 2                 | bit 1            | bit 0 |                       |  |

| SDIx ———                            |                       | bit 7                 | $\bigcirc$       |                       | $\sim$           |                       | $\rightarrow$         | $\sim$           | bit 0 | ,<br>,<br>,<br>,<br>, |  |

| Input<br>Sample                     | 1<br>1<br>1<br>1      | 1                     | 1                | 1                     | 1                | 1                     | 1                     | 1                | 1     |                       |  |

| SSPxIF<br>Interrupt<br>Flag         | 1<br>1<br>1<br>1<br>1 |                       |                  | ,<br>,<br>,<br>,<br>, | <br> <br> <br>   | ,<br>,<br>,<br>,<br>, | 1<br>1<br>1<br>1<br>1 | <br> <br> <br>   |       |                       |  |

| SSPxSR to<br>SSPxBUF                | 1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1 |                  | <br> <br> <br>        | 1<br>1<br>1<br>1 | <br> <br> <br>        | ,<br>,<br>,<br>,      | 1<br>1<br>1<br>1 |       | ×                     |  |

| Wille Collesion<br>detection police | 1                     | •                     |                  |                       | •                |                       | •                     |                  |       |                       |  |

|                                     |                       |                       |                  |                       |                  |                       |                       |                  |       |                       |  |

### 20.0 SR LATCH

The module consists of a single SR latch with multiple Set and Reset inputs as well as separate latch outputs. The SR latch module includes the following features:

- Programmable input selection

- SR latch output is available internally/externally

- Selectable Q and  $\overline{Q}$  output

- Firmware Set and Reset

The SR latch can be used in a variety of analog applications, including oscillator circuits, one-shot circuit, hysteretic controllers, and analog timing applications.

#### 20.1 Latch Operation

The latch is a Set-Reset latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be set or reset by:

- Software control (SRPS and SRPR bits)

- Comparator C1 output (sync\_C1OUT)

- Comparator C2 output (sync\_C2OUT)

- SRI Pin

- Programmable clock (DIVSRCLK)

The SRPS and the SRPR bits of the SRCON0 register may be used to set or reset the SR latch, respectively. The latch is Reset-dominant. Therefore, if both Set and Reset inputs are high, the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

The output from Comparator C1 or C2 can be used as the Set or Reset inputs of the SR latch. The output of either Comparator can be synchronized to the Timer1 clock source. See Section 18.0 "Comparator Module" and Section 12.0 "Timer1/3/5 Module with Gate Control" for more information.

An external source on the SRI pin can be used as the Set or Reset inputs of the SR latch.

An internal clock source, DIVSRCLK, is available and it can periodically set or reset the SR latch. The SRCLK<2:0> bits in the SRCON0 register are used to select the clock source period. The SRSCKE and SRRCKE bits of the SRCON1 register enable the clock source to set or reset the SR latch, respectively.

#### 20.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR latch outputs may be directly output to I/O pins at the same time. Control is determined by the state of bits SRQEN and SRNQEN in the SRCON0 register.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

#### 20.3 DIVSRCLK Clock Generation

The DIVSRCLK clock signal is generated from the peripheral clock which is pre-scaled by a value determined by the SRCLK<2:0> bits. See Figure 20-2 and Table 20-1 for additional detail.

#### 20.4 Effects of a Reset

Upon any device Reset, the SR latch is not initialized, and the SRQ and SRNQ outputs are unknown. The user's firmware is responsible to initialize the latch output before enabling it to the output pins.

### 23.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

The PIC18(L)F2X/4XK22 devices have a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that sets both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution branches to the interrupt vector address and the software responds to the interrupt. The High/Low-Voltage Detect Control register (Register 23-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The module's block diagram is shown in Figure 23-1.

### 23.1 Register - HLVD Control

#### REGISTER 23-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

| R/W-0   | R-0   | R-0   | R/W-0  | R/W-0 | R/W-1 | R/W-0  | R/W-1 |

|---------|-------|-------|--------|-------|-------|--------|-------|

| VDIRMAG | BGVST | IRVST | HLVDEN |       | HLVDI | _<3:0> |       |

| bit 7   |       |       |        |       |       |        | bit 0 |

| Legend:                                                           |                 |                                                              |                                                                     |                                                                           |

|-------------------------------------------------------------------|-----------------|--------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------|

| R = Readable bitW = Writable bit-n = Value at POR'1' = Bit is set |                 | U = Unimplemented bit,                                       | read as '0'                                                         |                                                                           |

|                                                                   |                 | '1' = Bit is set                                             | '0' = Bit is cleared                                                | x = Bit is unknown                                                        |

|                                                                   |                 |                                                              |                                                                     |                                                                           |

| bit 7                                                             | VDIRMA          | G: Voltage Direction Magnit                                  | ude Select bit                                                      |                                                                           |

|                                                                   |                 | <b>U</b>                                                     | ls or exceeds trip point (HLVD<br>Is or falls below trip point (HLV |                                                                           |

| bit 6                                                             | BGVST:          | Band Gap Reference Voltag                                    | es Stable Status Flag bit                                           |                                                                           |

|                                                                   |                 | nal band gap voltage referer<br>nal band gap voltage referer |                                                                     |                                                                           |

| bit 5                                                             | IRVST:          | nternal Reference Voltage S                                  | table Flag bit                                                      |                                                                           |

|                                                                   | 0 = Indi        | •                                                            | logic will not generate the inte                                    | flag at the specified voltage rang<br>errupt flag at the specified voltag |

| bit 4                                                             | HLVDEN          | I: High/Low-Voltage Detect F                                 | Power Enable bit                                                    |                                                                           |

|                                                                   | 1 = HLV         | ′D enabled<br>′D disabled                                    |                                                                     |                                                                           |

| bit 3-0                                                           | HLVDL<          | 3:0>: Voltage Detection Lev                                  | el bits <sup>(1)</sup>                                              |                                                                           |

|                                                                   | 1111 <b>=  </b> | -                                                            | l (input comes from the HLVDI                                       | N pin)                                                                    |

|                                                                   |                 |                                                              |                                                                     |                                                                           |

|                                                                   |                 |                                                              |                                                                     |                                                                           |

|                                                                   | 0000 =          | Vinimum setting                                              |                                                                     |                                                                           |

| Note 1.                                                           |                 | -5 for specifications                                        |                                                                     |                                                                           |

**Note 1:** See Table 27-5 for specifications.

| R/P-1      | U-0                                                              | R/P-1                                                                | R/P-1          | R/P-1                              | R/P-1            | R/P-1        | R/P-1  |

|------------|------------------------------------------------------------------|----------------------------------------------------------------------|----------------|------------------------------------|------------------|--------------|--------|

| MCLRE      |                                                                  | P2BMX                                                                | T3CMX          | HFOFST                             | CCP3MX           | PBADEN       | CCP2MX |

| bit 7      |                                                                  |                                                                      |                | ·                                  |                  |              | bit (  |

| Legend:    |                                                                  |                                                                      |                |                                    |                  |              |        |

| R = Reada  | able bit                                                         | P = Program                                                          | nable bit      | U = Unimpler                       | nented bit, read | d as '0'     |        |

| -n = Value | when device is un                                                | programmed                                                           |                | x = Bit is unki                    | nown             |              |        |

| bit 7      |                                                                  | R Pin Enable                                                         |                |                                    |                  |              |        |

|            |                                                                  | enabled; RE3                                                         |                |                                    |                  |              |        |

| bit 6      | Unimplemen                                                       | ted: Read as '                                                       | 0'             |                                    |                  |              |        |

| bit 5      | <b>P2BMX:</b> P2B<br>1 = P2B is on<br>P2B is on<br>0 = P2B is on | RD2 <sup>(2)</sup>                                                   |                |                                    |                  |              |        |

| bit 4      | <b>T3CMX:</b> Time<br>1 = T3CKI is 0<br>0 = T3CKI is 0           |                                                                      | MUX bit        |                                    |                  |              |        |

| bit 3      | 1 = HFINTOS                                                      |                                                                      | ng the CPU wi  | thout waiting fo                   |                  | to stabilize |        |

| bit 2      | 0 = CCP3 inp                                                     | CP3 MUX bit<br>ut/output is mu<br>ut/output is mu<br>ut/output is mu | ltiplexed with | RC6 <sup>(1)</sup>                 |                  |              |        |

| bit 1      | 1 = ANSELB<                                                      |                                                                      | 1, PORTB<5:    | 0> pins are cor<br>0> pins are cor |                  |              |        |

| bit 0      |                                                                  | P2 MUX bit<br>ut/output is mu<br>ut/output is mu                     |                |                                    |                  |              |        |

| Note 1:    | PIC18(L)F2XK22                                                   | devices only.                                                        |                |                                    |                  |              |        |

| 2:         | PIC18(L)F4XK22                                                   | devices only.                                                        |                |                                    |                  |              |        |

#### REGISTER 24-4: CONFIG3H: CONFIGURATION REGISTER 3 HIGH

| POP                                  | Pop Top of Return Stack                                                                                                                                                                                                                                                                    | PUSH                                      | Push Top of Return Stack                                                                                                                                                                                                                    |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                              | POP                                                                                                                                                                                                                                                                                        | Syntax:                                   | PUSH                                                                                                                                                                                                                                        |

| Operands:                            | None                                                                                                                                                                                                                                                                                       | Operands:                                 | None                                                                                                                                                                                                                                        |

| Operation:                           | $(TOS) \rightarrow bit bucket$                                                                                                                                                                                                                                                             | Operation:                                | $(PC + 2) \rightarrow TOS$                                                                                                                                                                                                                  |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                       | Status Affected:                          | None                                                                                                                                                                                                                                        |

| Encoding:                            | 0000 0000 0000 0110                                                                                                                                                                                                                                                                        | Encoding:                                 | 0000 0000 0000 0101                                                                                                                                                                                                                         |

| Description:                         | The TOS value is pulled off the return<br>stack and is discarded. The TOS value<br>then becomes the previous value that<br>was pushed onto the return stack.<br>This instruction is provided to enable<br>the user to properly manage the return<br>stack to incorporate a software stack. | Description:<br>Words:                    | The PC + 2 is pushed onto the top of<br>the return stack. The previous TOS<br>value is pushed down on the stack.<br>This instruction allows implementing a<br>software stack by modifying TOS and<br>then pushing it onto the return stack. |

| Words:                               | 1                                                                                                                                                                                                                                                                                          | Cycles:                                   | 1                                                                                                                                                                                                                                           |

| Cycles:                              | 1                                                                                                                                                                                                                                                                                          | Q Cycle Activity:                         |                                                                                                                                                                                                                                             |

| Q Cycle Activity:                    |                                                                                                                                                                                                                                                                                            | Q1                                        | Q2 Q3 Q4                                                                                                                                                                                                                                    |

| Q1<br>Decode                         | Q2Q3Q4NoPOP TOSNooperationvalueoperation                                                                                                                                                                                                                                                   | Decode                                    | PUSH No No   PC + 2 onto operation operation   return stack                                                                                                                                                                                 |

| Example:                             | POP<br>Goto new                                                                                                                                                                                                                                                                            | Example:<br>Before Instruc                | PUSH                                                                                                                                                                                                                                        |

| Before Instruct<br>TOS<br>Stack (1 I | ion<br>= 0031A2h<br>evel down) = 014332h                                                                                                                                                                                                                                                   | TOS<br>PC                                 | = 345Ah<br>= 0124h                                                                                                                                                                                                                          |

| After Instructio<br>TOS<br>PC        | n<br>= 014332h<br>= NEW                                                                                                                                                                                                                                                                    | After Instructio<br>PC<br>TOS<br>Stack (1 | on<br>= 0126h<br>= 0126h<br>level down) = 345Ah                                                                                                                                                                                             |

| RET   | RETURN Return from Subroutine                                                                                                                                           |                                                                                                                           |                                                                          |                                                            |                                                  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------|--|--|

| Synta | ax:                                                                                                                                                                     | RETURN                                                                                                                    | {S}                                                                      |                                                            |                                                  |  |  |

| Oper  | ands:                                                                                                                                                                   | s ∈ [0,1]                                                                                                                 |                                                                          |                                                            |                                                  |  |  |

| Oper  | theration: $(TOS) \rightarrow PC,$<br>if s = 1<br>$(WS) \rightarrow W,$<br>$(STATUSS) \rightarrow Status,$<br>$(BSRS) \rightarrow BSR,$<br>PCLATU, PCLATH are unchanged |                                                                                                                           |                                                                          |                                                            |                                                  |  |  |

| Statu | is Affected:                                                                                                                                                            | None                                                                                                                      |                                                                          |                                                            |                                                  |  |  |

| Enco  | oding:                                                                                                                                                                  | 0000                                                                                                                      | 0000                                                                     | 0001                                                       | 001s                                             |  |  |

|       |                                                                                                                                                                         | popped and<br>is loaded in<br>'s'= 1, the c<br>registers, W<br>are loaded<br>registers, W<br>'s' = 0, no c<br>occurs (def | to the pr<br>contents<br>/S, STAT<br>into their<br>/, STATL<br>ipdate of | ogram co<br>of the sha<br>USS and<br>correspo<br>IS and BS | unter. If<br>adow<br>I BSRS,<br>onding<br>SR. If |  |  |

| Word  | ls:                                                                                                                                                                     | 1                                                                                                                         | 1                                                                        |                                                            |                                                  |  |  |

| Cycle | es:                                                                                                                                                                     | 2                                                                                                                         |                                                                          |                                                            |                                                  |  |  |

| QC    | ycle Activity:                                                                                                                                                          |                                                                                                                           |                                                                          |                                                            |                                                  |  |  |

|       | Q1                                                                                                                                                                      | Q2                                                                                                                        | Q                                                                        | 3                                                          | Q4                                               |  |  |

|       | Decode                                                                                                                                                                  | No<br>operation                                                                                                           | Proce<br>Dat                                                             |                                                            | POP PC<br>om stack                               |  |  |

|       | No                                                                                                                                                                      | No                                                                                                                        | No                                                                       | )                                                          | No                                               |  |  |

|       | operation                                                                                                                                                               | operation                                                                                                                 | opera                                                                    | tion c                                                     | peration                                         |  |  |

|       |                                                                                                                                                                         |                                                                                                                           |                                                                          |                                                            |                                                  |  |  |

| Example: | RETURN |

|----------|--------|

After Instruction: PC = TOS