Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 30x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k22-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F23K22 PIC18LF23K22

- PIC18F24K22 PIC18LF24K22

- PIC18F25K22

PIC18LF25K22

- PIC18F26K22 PIC18LF26K22

- PIC18F43K22 PIC18LF43K22

- PIC18F44K22 PIC18LF44K22

- PIC18F45K22 PIC18LF45K22

- PIC18F46K22 PIC18LF46K22

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Flash program memory. On top of these features, the PIC18(L)F2X/4XK22 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

#### 1.1 New Core Features

#### 1.1.1 XLP TECHNOLOGY

All of the devices in the PIC18(L)F2X/4XK22 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- **On-the-fly Mode Switching:** The powermanaged modes are invoked by user code during operation, allowing the user to incorporate powersaving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 27.0 "Electrical Specifications" for values.

#### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18(L)F2X/4XK22 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O)

- Two External RC Oscillator modes with the same pin options as the External Clock modes

- An internal oscillator block which contains a 16 MHz HFINTOSC oscillator and a 31 kHz LFINTOSC oscillator, which together provide eight user selectable clock frequencies, from 31 kHz to 16 MHz. This option frees the two oscillator pins for use as additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both external and internal oscillator modes, which allows clock speeds of up to 64 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 64 MHz – all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the LFINTOSC. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or Wake-up from Sleep mode, until the primary clock source is available.

# 2.2 Oscillator Control

The OSCCON, OSCCON2 and OSCTUNE registers (Register 2-1 to Register 2-3) control several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

- Main System Clock Selection (SCS)

- Primary Oscillator Circuit Shutdown (PRISD)

- Secondary Oscillator Enable (SOSCGO)

- Primary Clock Frequency 4x multiplier (PLLEN)

- Internal Frequency selection bits (IRCF, INTSRC)

- Clock Status bits (OSTS, HFIOFS, MFIOFS, LFIOFS. SOSCRUN, PLLRDY)

- Power management selection (IDLEN)

#### 2.2.1 MAIN SYSTEM CLOCK SELECTION

The System Clock Select bits, SCS<1:0>, select the main clock source. The available clock sources are

- Primary clock defined by the FOSC<3:0> bits of CONFIG1H. The primary clock can be the primary oscillator, an external clock, or the internal oscillator block.

- Secondary clock (secondary oscillator)

- Internal oscillator block (HFINTOSC, MFINTOSC and LFINTOSC).

The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared to select the primary clock on all forms of Reset.

#### 2.2.2 INTERNAL FREQUENCY SELECTION

The Internal Oscillator Frequency Select bits (IRCF<2:0>) select the frequency output of the internal oscillator block. The choices are the LFINTOSC source (31.25 kHz), the MFINTOSC source (31.25 kHz, 250 kHz or 500 kHz) and the HFINTOSC source (16 MHz) or one of the frequencies derived from the HFINTOSC postscaler (31.25 kHz to 8 MHz). If the internal oscillator block is supplying the main clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the output frequency of the internal oscillator is set to the default frequency of 1 MHz.

## 2.2.3 LOW FREQUENCY SELECTION

When a nominal output frequency of 31.25 kHz is selected (IRCF<2:0> = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit of the OSCTUNE register and MFIOSEL bit of the OSCCON2 register. See Figure 2-2 and Register 2-1 for specific 31.25 kHz selection. This option allows users to select a 31.25 kHz clock (MFINTOSC or HFINTOSC) that can be tuned using the TUN<5:0> bits in OSCTUNE register, while maintaining power savings with a very low clock speed. LFINTOSC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor, regardless of the setting of INTSRC and MFIOSEL bits

This option allows users to select the tunable and more precise HFINTOSC as a clock source, while maintaining power savings with a very low clock speed.

### 2.2.4 POWER MANAGEMENT

The IDLEN bit of the OSCCON register determines whether the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

### 5.3 PIC18 Instruction Cycle

#### 5.3.1 CLOCKING SCHEME

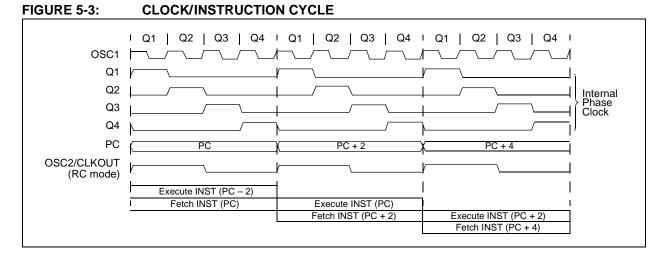

The microcontroller clock input, whether from an internal or external source, is internally divided by four to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the program counter is incremented on every Q1; the instruction is fetched from the program memory and latched into the instruction register during Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 5-3.

#### 5.3.2 INSTRUCTION FLOW/PIPELINING

An "Instruction Cycle" consists of four Q cycles: Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 5-3).

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### EXAMPLE 5-3: INSTRUCTION PIPELINE FLOW

|                                                                                                                  | Тсү0      | TCY1      | Tcy2      | Tcy3      | TCY4        | TCY5 |

|------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-------------|------|

| 1. MOVLW 55h                                                                                                     | Fetch 1   | Execute 1 |           |           | •           |      |

| 2. MOVWF PORTB                                                                                                   |           | Fetch 2   | Execute 2 |           |             |      |

| 3. BRA SUB_1                                                                                                     |           |           | Fetch 3   | Execute 3 |             |      |

| 4. BSF PORTA, BIT3                                                                                               | (Forced N | OP)       |           | Fetch 4   | Flush (NOP) |      |

| 5. Instruction @ address SUB_1 Fetch SUB_1 Execute SUB_1                                                         |           |           |           |           |             |      |

| <b>Note:</b> All instructions are single cycle, except for any program branches. These take two cycles since the |           |           |           |           |             |      |

**Note:** All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

# 7.0 DATA EEPROM MEMORY

The data EEPROM is a nonvolatile memory array, separate from the data RAM and program memory, which is used for long-term storage of program data. It is not directly mapped in either the register file or program memory space but is indirectly addressed through the Special Function Registers (SFRs). The EEPROM is readable and writable during normal operation over the entire VDD range.

Four SFRs are used to read and write to the data EEPROM as well as the program memory. They are:

- EECON1

- EECON2

- EEDATA

- EEADR

- EEADRH

The data EEPROM allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and the EEADR:EEADRH register pair hold the address of the EEPROM location being accessed.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer; it will vary with voltage and temperature as well as from chip-to-chip. Please refer to the Data EEPROM Memory parameters in Section 27.0 "Electrical Specifica-tions" for limits.

# 7.1 EEADR and EEADRH Registers

The EEADR register is used to address the data EEPROM for read and write operations. The 8-bit range of the register can address a memory range of 256 bytes (00h to FFh). The EEADRH register expands the range to 1024 bytes by adding an additional two address bits.

## 7.2 EECON1 and EECON2 Registers

Access to the data EEPROM is controlled by two registers: EECON1 and EECON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The EECON1 register (Register 7-1) is the control register for data and program memory access. Control bit EEPGD determines if the access will be to program or data EEPROM memory. When the EEPGD bit is clear, operations will access the data EEPROM memory. When the EEPGD bit is set, program memory is accessed.

Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When the CFGS bit is set, subsequent operations access Configuration registers. When the CFGS bit is clear, the EEPGD bit selects either program Flash or data EEPROM memory.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear.

The WRERR bit is set by hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR         |

|-------|--------------------------------------------|

|       | may read as '1'. This can indicate that a  |

|       | write operation was prematurely termi-     |

|       | nated by a Reset, or a write operation was |

|       | attempted improperly.                      |

The WR control bit initiates write operations. The bit can be set but not cleared by software. It is cleared only by hardware at the completion of the write operation.

Note: The EEIF interrupt flag bit of the PIR2 register is set when the write is complete. It must be cleared by software.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 6.1 "Table Reads and Table Writes"** regarding table reads.

The EECON2 register is not a physical register. It is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

| R/W-1      |                                       | U-0                              | R/W-0           | R/W-0            | U-0             | R/W-0           | R/W-0  |

|------------|---------------------------------------|----------------------------------|-----------------|------------------|-----------------|-----------------|--------|

| INT2I      | P INT1IP                              | —                                | INT2IE          | INT1IE           | —               | INT2IF          | INT1IF |

| bit 7      |                                       |                                  |                 |                  |                 |                 | bit C  |

| Legend:    |                                       |                                  |                 |                  |                 |                 |        |

| R = Read   | able bit                              | W = Writable                     | bit             | U = Unimpler     | mented bit, rea | d as '0'        |        |

| -n = Value |                                       | '1' = Bit is set                 |                 | '0' = Bit is cle |                 | x = Bit is unkr | nown   |

|            |                                       |                                  |                 |                  |                 |                 |        |

| bit 7      | INT2IP: INT2                          | External Interr                  | upt Priority bi | t                |                 |                 |        |

|            | 1 = High pric                         | •                                |                 |                  |                 |                 |        |

|            | 0 = Low prio                          | •                                |                 |                  |                 |                 |        |

| bit 6      |                                       | External Interr                  | upt Priority bi | t                |                 |                 |        |

|            | 1 = High pric                         |                                  |                 |                  |                 |                 |        |

| hit E      | 0 = Low prio                          | ited: Read as '                  | 0'              |                  |                 |                 |        |

| bit 5      | -                                     |                                  |                 |                  |                 |                 |        |

| bit 4      |                                       | External Interr                  | -               | t                |                 |                 |        |

|            |                                       | the INT2 exter<br>the INT2 exter |                 |                  |                 |                 |        |

| bit 3      |                                       | External Intern                  | •               | t                |                 |                 |        |

|            |                                       | the INT1 exter                   | -               | •                |                 |                 |        |

|            |                                       | the INT1 exter                   | •               |                  |                 |                 |        |

| bit 2      | Unimplemer                            | ted: Read as '                   | 0'              |                  |                 |                 |        |

| bit 1      | INT2IF: INT2                          | External Interr                  | upt Flag bit    |                  |                 |                 |        |

|            |                                       |                                  | •               | (must be clear   | ed by software  | )               |        |

|            |                                       | 2 external inter                 | •               | ccur             |                 |                 |        |

| bit 0      |                                       | External Interr                  |                 |                  |                 |                 |        |

|            |                                       |                                  |                 | (must be clear   | ed by software  | )               |        |

|            | 0 = 1 he in 1                         | 1 external inter                 | rupt did not o  | ccur             |                 |                 |        |

| Note:      | Interrupt flag bits a                 | ire set when an                  | interrupt       |                  |                 |                 |        |

|            | condition occurs, r                   |                                  |                 |                  |                 |                 |        |

|            | its corresponding                     |                                  |                 |                  |                 |                 |        |

|            | enable bit. User sthe appropriate int |                                  |                 |                  |                 |                 |        |

|            | prior to enabling a                   |                                  |                 |                  |                 |                 |        |

|            | allows for software                   |                                  | 0.0000          |                  |                 |                 |        |

#### REGISTER 9-3: INTCON3: INTERRUPT CONTROL 3 REGISTER

| FIGURE 12-7:           | TIMER1/3/5 GATE SING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LE-PULSE AND TOGGLE COMBINED MODE                   |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| TMRxGE                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGPOL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGSPM                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGTM                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGG <u>O/</u><br>DONE | <ul> <li>Set by software</li> <li>Counting enabled of the set of the</li></ul> | Cleared by hardware on falling edge of TxGVAL       |

| TxG_IN                 | rising edge of TxG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

| ТхСКІ                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGVAL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TIMER1/3/5             | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>N + 1</u> <u>N + 2</u> <u>N + 3</u> <u>N + 4</u> |

| TMRxGIF                | Cleared by software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Set by hardware on<br>falling edge of TxGVAL        |

# 12.12 Peripheral Module Disable

When a peripheral module is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bits for Timer1 (TMR1MD), Timer3 (TMR3MD) and Timer5 (TMR5MD) are in the PMD0 Register. See Section 3.0 "Power-Managed Modes" for more information.

#### 14.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is selected (CCPxM<3:0> = 1011), and a match of the TMRxH:TMRxL and the CCPRxH:CCPRxL registers occurs, all CCPx and ECCPx modules will immediately:

- Set the CCP interrupt flag bit CCPxIF

- CCP5 will start an ADC conversion, if the ADC is enabled

On the next TimerX rising clock edge:

• A Reset of TimerX register pair occurs – TMRxH:TMRxL = 0x0000,

This Special Event Trigger mode does not:

- Assert control over the CCPx or ECCPx pins.

- Set the TMRxIF interrupt bit when the TMRxH:TMRxL register pair is reset. (TMRxIF gets set on a TimerX overflow.)

If the value of the CCPRxH:CCPRxL registers are modified when a match occurs, the user should be aware that the automatic reset of TimerX occurs on the next rising edge of the clock. Therefore, modifying the CCPRxH:CCPRxL registers before this reset occurs will allow the TimerX to continue without being reset, inadvertently resulting in the next event being advanced or delayed.

The Special Event Trigger mode allows the CCPRxH:CCPRxL register pair to effectively provide a 16-bit programmable period register for TimerX.

#### Register Bit 4 Name Bit 7 Bit 6 Bit 5 Bit 3 Bit 2 Bit 1 Bit 0 on Page CCP1CON P1M<1:0> DC1B<1.0>CCP1M<3:0> 198 P2M<1:0> CCP2CON DC2B<1.0> CCP2M<3:0> 198 CCP3CON P3M<1:0> DC3B<1:0> CCP3M<3:0> 198 CCP4CON DC4B<1:0> CCP4M<3:0> 198 CCP5CON CCP5M<3:0> DC5B<1:0> 198 CCPR1H Capture/Compare/PWM Register 1 High Byte (MSB) CCPR1L Capture/Compare/PWM Register 1 Low Byte (LSB) CCPR2H Capture/Compare/PWM Register 2 High Byte (MSB) \_\_\_\_ CCPR2L Capture/Compare/PWM Register 2 Low Byte (LSB) \_ CCPR3H Capture/Compare/PWM Register 3 High Byte (MSB) \_ CCPR3L Capture/Compare/PWM Register 3 Low Byte (LSB) CCPR4H Capture/Compare/PWM Register 4 High Byte (MSB) \_\_\_\_ CCPR4L Capture/Compare/PWM Register 4 Low Byte (LSB) CCPR5H Capture/Compare/PWM Register 5 High Byte (MSB) \_\_\_\_ CCPR5L Capture/Compare/PWM Register 5 Low Byte (LSB) CCPTMRS0 C3TSEL<1:0> C2TSEL<1:0> C1TSEL<1:0> \_\_\_\_\_ 201 CCPTMRS1 C5TSEL<1:0> C4TSEL<1:0> 201 INTCON RBIE TMR0IF **INTOIF GIE/GIEH** PEIE/GIEL TMR0IE **INTOIE** RBIF 109 IPR1 ADIP RC1IP TX1IP SSP1IP CCP1IP TMR2IP TMR1IP 121

### TABLE 14-5: REGISTERS ASSOCIATED WITH COMPARE

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Compare mode.

Note 1: These registers/bits are available on PIC18(L)F4XK22 devices.

#### 14.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

| R/W-0           | R/W-0                                                                                                | R/W-0                                                                                                                                                                              | R/W-0                                                                                               | R/W-0                                                                                                       | R/W-0                                                                                  | R/W-0                                                  | R/W-0        |

|-----------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------|--------------|

| CCPxASE         |                                                                                                      | CCPxAS<2:0>                                                                                                                                                                        |                                                                                                     | PSSxA                                                                                                       | AC<1:0>                                                                                | PSSxB                                                  | D<1:0>       |

| bit 7           |                                                                                                      |                                                                                                                                                                                    |                                                                                                     |                                                                                                             |                                                                                        |                                                        | bit (        |

|                 |                                                                                                      |                                                                                                                                                                                    |                                                                                                     |                                                                                                             |                                                                                        |                                                        |              |

| Legend:         |                                                                                                      |                                                                                                                                                                                    |                                                                                                     |                                                                                                             |                                                                                        |                                                        |              |

| R = Readab      | le bit                                                                                               | W = Writable                                                                                                                                                                       | bit                                                                                                 | •                                                                                                           | nented bit, read                                                                       |                                                        |              |

| u = Bit is un   | changed                                                                                              | x = Bit is unkr                                                                                                                                                                    | nown                                                                                                | -n/n = Value a                                                                                              | at POR and BO                                                                          | R/Value at all                                         | other Resets |

| '1' = Bit is se | et                                                                                                   | '0' = Bit is clea                                                                                                                                                                  | ared                                                                                                |                                                                                                             |                                                                                        |                                                        |              |

| bit 7           | if <b>PxRSEN</b><br>1 = An Auto<br>CCPx o<br>0 = CCPx o<br>if <b>PxRSEN</b><br>1 = An Auto<br>CCPx o | o-shutdown even<br>outputs in shutdow<br>utputs are opera                                                                                                                          | t occurred; C<br>wn state<br>ting<br>t occurred; bi<br>wn state                                     | CPxASE bit will                                                                                             | ·                                                                                      |                                                        |              |

| bit 6-4         | 000 = Auto<br>001 = Com<br>010 = Com<br>011 = Eithe<br>100 = FLT0<br>101 = FLT0<br>110 = FLT0        | :0>: CCPx Auto-<br>shutdown is disa<br>parator C1 (asyn<br>parator C2 (asyn<br>r Comparator C1<br>pin – low level w<br>pin – low level o<br>pin – low level o<br>pin – low level o | ibled<br>c_C1OUT) –<br>c_C2OUT) –<br>or C2 – outp<br>vill cause shu<br>r Comparator<br>r Comparator | output high will<br>output high will<br>out high will caus<br>tdown event<br>C1 (async_C10<br>C2 (async_C20 | cause shutdow<br>cause shutdow<br>se shutdown ev<br>DUT) – high lev<br>DUT) – high lev | n event<br>ent<br>el will cause sł<br>el will cause sł | nutdown even |

| bit 3-2         | 00 = Drive p<br>01 = Drive p                                                                         | :0>: Pins PxA ar<br>pins PxA and PxO<br>pins PxA and PxO<br>pxA and PxC tri-s                                                                                                      | C to '0'<br>C to '1'                                                                                | own State Conti                                                                                             | rol bits                                                                               |                                                        |              |

| bit 1-0         | 00 = Drive p<br>01 = Drive p                                                                         | :0>: Pins PxB an<br>bins PxB and PxI<br>bins PxB and PxI<br>pxB and PxD tri-s                                                                                                      | D to '0'<br>D to '1'                                                                                | own State Contr                                                                                             | ol bits                                                                                |                                                        |              |

|                 | C1SYNC or C                                                                                          | 2SYNC bits in the                                                                                                                                                                  | e CM2CON1                                                                                           | register are ena                                                                                            | bled, the shutd                                                                        | own will be de                                         | layed by Tim |

#### REGISTER 14-5: ECCPxAS: CCPX AUTO-SHUTDOWN CONTROL REGISTER

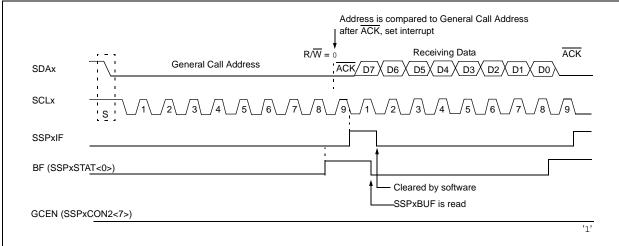

#### 15.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^2C$  protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically  $\overline{ACK}$  the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 15-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the 8th falling edge of SCLx. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

#### FIGURE 15-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

#### 15.5.9 SSPx MASK REGISTER

An SSPx Mask (SSPxMSK) register (Register 15-6) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPxSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSPx operation until written with a mask value.

The SSPx Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSPx mask has no effect during the reception of the first (high) byte of the address.

#### 16.4.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RXx signal, the RXx signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCONx register starts the auto-baud calibration sequence (Section 16.4.2 "Auto-baud Overflow"). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRGx begins counting up using the BRG counter clock as shown in Table 16-6. The fifth rising edge will occur on the RXx/ DTx pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGHx:SPBRGx register pair, the ABDEN bit is automatically cleared, and the RCxIF interrupt flag is set. A read operation on the RCREGx needs to be performed to clear the RCxIF interrupt. RCREGx content should be discarded. When calibrating for modes that do not use the SPBRGHx register the user can verify that the SPBRGx register did not overflow by checking for 00h in the SPBRGHx register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 16-6. During ABD, both the SPBRGHx and SPBRGx registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGHx and SPBRGx registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte <u>following</u> the Break character (see Section 16.4.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the autobaud counter starts counting at one. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract one from the SPBRGHx:SPBRGx register pair.

| TABLE 16-6: | BRG COUNTER CLOCK |

|-------------|-------------------|

|             | RATES             |

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

Note: During the ABD sequence, SPBRGx and SPBRGHx registers are both used as a 16-bit counter, independent of BRG16 setting.

| BRG Value   | XXXXh           | 0000h                   |                                                         | 001Ch         |

|-------------|-----------------|-------------------------|---------------------------------------------------------|---------------|

| RXx/DTx pin |                 | Start                   | Edge #1 Edge #2 Edge #3 Edge #4                         | it 7 Stop bit |

| BRG Clock   |                 | huuuuuu                 |                                                         |               |

|             | Set by User —   | I<br>I                  |                                                         | Auto Cleared  |

| ABDEN bit   | ·               |                         |                                                         |               |

| RCIDL       |                 | '<br>'<br>'             |                                                         |               |

| RCxIF bit   |                 | 1 <b>—</b> ——<br>1<br>1 |                                                         |               |

| (Interrupt) |                 | 1                       | 1                                                       |               |

| Read        |                 | 1<br> <br>              |                                                         |               |

| RCREGx      |                 | 1                       | 1                                                       |               |

| SPBRGx      |                 | I<br>I                  | XXh                                                     | ( 1Ch         |

| SPBRGHx     |                 | 1                       | XXh                                                     | ) 00h         |

| Note        | I: The ABD sequ | ence requires the EUSA  | <b>RT</b> module to be configured in Asynchronous mode. |               |

# FIGURE 16-6: AUTOMATIC BAUD RATE CALIBRATION

#### 18.2 Comparator Control

Each comparator has a separate control and Configuration register: CM1CON0 for Comparator C1 and CM2CON0 for Comparator C2. In addition, Comparator C2 has a second control register, CM2CON1, for controlling the interaction with Timer1 and simultaneous reading of both comparator outputs.

The CM1CON0 and CM2CON0 registers (see Register 18-1) contain the control and status bits for the following:

- Enable

- Input selection

- Reference selection

- Output selection

- Output polarity

- Speed selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 18.2.2 COMPARATOR INPUT SELECTION

The CxCH<1:0> bits of the CMxCON0 register direct one of four analog input pins to the comparator inverting input.

| Note: | To us                                       | e CxIN+ an  | d C12INx- p   | ins as a  | nalog  |  |

|-------|---------------------------------------------|-------------|---------------|-----------|--------|--|

|       | inputs, the appropriate bits must be set in |             |               |           |        |  |

|       | the                                         | ANSEL       | register      | and       | the    |  |

|       | corres                                      | sponding Tl | RIS bits mu   | st also b | oe set |  |

|       | to dis                                      | able the ou | tput drivers. |           |        |  |

#### 18.2.3 COMPARATOR REFERENCE SELECTION

Setting the CxR bit of the CMxCON0 register directs an internal voltage reference or an analog input pin to the non-inverting input of the comparator. See **Section 21.0 "Fixed Voltage Reference (FVR)"** for more information on the Internal Voltage Reference module.

#### 18.2.4 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CM2CON1 register. In order to make the output available for an external connection, the following conditions must be true:

- CxOE bit of the CMxCON0 register must be set

- · Corresponding TRIS bit must be cleared

- CxON bit of the CMxCON0 register must be set

- Note 1: The CxOE bit overrides the PORT data latch. Setting the CxON has no impact on the port override.

- 2: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 18.2.5 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 18-1 shows the output state versus input conditions, including polarity control.

#### TABLE 18-1: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition   | CxPOL | CxOUT |

|-------------------|-------|-------|

| CxVIN - > CxVIN + | 0     | 0     |

| CxVIN- < CxVIN+   | 0     | 1     |

| CxVIN - > CxVIN + | 1     | 1     |

| CxVIN- < CxVIN+   | 1     | 0     |

## 18.2.6 COMPARATOR SPEED SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the normal speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

# 18.3 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section 27.0 "Electrical Specifications"** for more details.

### 19.1 CTMU Operation

The CTMU works by using a fixed current source to charge a circuit. The type of circuit depends on the type of measurement being made. In the case of charge measurement, the current is fixed, and the amount of time the current is applied to the circuit is fixed. The amount of voltage read by the A/D is then a measurement of the capacitance of the circuit. In the case of time measurement, the current, as well as the capacitance of the circuit, is fixed. In this case, the voltage read by the A/D is then representative of the amount of time elapsed from the time the current source starts and stops charging the circuit.

If the CTMU is being used as a time delay, both capacitance and current source are fixed, as well as the voltage supplied to the comparator circuit. The delay of a signal is determined by the amount of time it takes the voltage to charge to the comparator threshold voltage.

#### 19.1.1 THEORY OF OPERATION

The operation of the CTMU is based on the equation for charge:

$$I = C \cdot \frac{dV}{dT}$$

More simply, the amount of charge measured in coulombs in a circuit is defined as current in amperes (*I*) multiplied by the amount of time in seconds that the current flows (t). Charge is also defined as the capacitance in farads (C) multiplied by the voltage of the circuit (V). It follows that:

$$I \cdot t = C \cdot V.$$

The CTMU module provides a constant, known current source. The A/D Converter is used to measure (V) in the equation, leaving two unknowns: capacitance (C) and time (t). The above equation can be used to calculate capacitance or time, by either the relationship using the known fixed capacitance of the circuit:

$$t = (C \cdot V) / I$$

or by:

$$C = (I \cdot t) / V$$

using a fixed time that the current source is applied to the circuit.

#### 19.1.2 CURRENT SOURCE

At the heart of the CTMU is a precision current source, designed to provide a constant reference for measurements. The level of current is user-selectable across three ranges, with the ability to trim the output. The current range is selected by the IRNG<1:0> bits (CTMUICON<1:0>), with a value of '00' representing the lowest range.

Current trim is provided by the ITRIM<5:0> bits (CTMUICON<7:2>). Note that half of the range adjusts the current source positively and the other half reduces the current source. A value of '000000' is the neutral position (no change). A value of '100000' is the maximum negative adjustment, and '011111' is the maximum positive adjustment.

### 19.1.3 EDGE SELECTION AND CONTROL

CTMU measurements are controlled by edge events occurring on the module's two input channels. Each channel, referred to as Edge 1 and Edge 2, can be configured to receive input pulses from one of the edge input pins (CTED1 and CTED2) or ECCPx Special Event Triggers. The input channels are level-sensitive, responding to the instantaneous level on the channel rather than a transition between levels. The inputs are selected using the EDG1SEL and EDG2SEL bit pairs (CTMUCONL<3:2 and 6:5>).

In addition to source, each channel can be configured for event polarity using the EDGE2POL and EDGE1POL bits (CTMUCONL<7,4>). The input channels can also be filtered for an edge event sequence (Edge 1 occurring before Edge 2) by setting the EDGSEQEN bit (CTMUCONH<2>).

#### 19.1.4 EDGE STATUS

The CTMUCONL register also contains two Status bits: EDG2STAT and EDG1STAT (CTMUCONL<1:0>). Their primary function is to show if an edge response has occurred on the corresponding channel. The CTMU automatically sets a particular bit when an edge response is detected on its channel. The level-sensitive nature of the input channels also means that the Status bits become set immediately if the channel's configuration is changed and is the same as the channel's current state.

| RCALL                        | Relative                                                                                                                                                                                                                                                                                                                       | Call   |      |      |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|--|

| Syntax:                      | RCALL n                                                                                                                                                                                                                                                                                                                        |        |      |      |  |

| Operands:                    | -1024 ≤ n :                                                                                                                                                                                                                                                                                                                    | ≤ 1023 |      |      |  |

| Operation:                   | $(PC) + 2 \rightarrow TOS,$<br>$(PC) + 2 + 2n \rightarrow PC$                                                                                                                                                                                                                                                                  |        |      |      |  |

| Status Affected:             | None                                                                                                                                                                                                                                                                                                                           |        |      |      |  |

| Encoding:                    | 1101                                                                                                                                                                                                                                                                                                                           | 1nnn   | nnnn | nnnn |  |

| Description:                 | Subroutine call with a jump up to 1K from the current location. First, return address (PC + 2) is pushed onto the stack. Then, add the 2's complement number '2n' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is a 2-cycle instruction. |        |      |      |  |

| Words:                       | 1                                                                                                                                                                                                                                                                                                                              |        |      |      |  |

| Cycles:<br>Q Cycle Activity: | 2                                                                                                                                                                                                                                                                                                                              |        |      |      |  |

| Q1              | Q2                                         | Q3              | Q4              |

|-----------------|--------------------------------------------|-----------------|-----------------|

| Decode          | Read literal<br>'n'<br>PUSH PC to<br>stack | Process<br>Data | Write to PC     |

| No<br>operation | No<br>operation                            | No<br>operation | No<br>operation |

#### Example: HERE RCALL Jump

Before Instruction

PC = Address (HERE)

After Instruction

PC = Address (Jump) TOS = Address (HERE + 2)

#### RESET Reset Syntax: RESET Operands: None Operation: Reset all registers and flags that are affected by a MCLR Reset. Status Affected: All Encoding: 0000 0000 1111 1111 Description: This instruction provides a way to execute a MCLR Reset by software. Words: 1 Cycles: 1 Q Cycle Activity: Q1 Q2 Q3 Q4 Decode Start No No Reset operation operation

| Example: |

|----------|

|----------|

After Instruction

| Registers = | Reset Value |

|-------------|-------------|

| Flags* =    | Reset Value |

RESET

#### TABLE 27-22: A/D CONVERSION REQUIREMENTS PIC18(L)F2X/4XK22