#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 64MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 30x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k22-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F23K22 PIC18LF23K22

- PIC18F24K22 PIC18LF24K22

- PIC18F25K22

PIC18LF25K22

- PIC18F26K22 PIC18LF26K22

- PIC18F43K22 PIC18LF43K22

- PIC18F44K22 PIC18LF44K22

- PIC18F45K22 PIC18LF45K22

- PIC18F46K22 PIC18LF46K22

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Flash program memory. On top of these features, the PIC18(L)F2X/4XK22 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

#### 1.1 New Core Features

#### 1.1.1 XLP TECHNOLOGY

All of the devices in the PIC18(L)F2X/4XK22 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- **On-the-fly Mode Switching:** The powermanaged modes are invoked by user code during operation, allowing the user to incorporate powersaving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 27.0 "Electrical Specifications" for values.

#### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18(L)F2X/4XK22 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O)

- Two External RC Oscillator modes with the same pin options as the External Clock modes

- An internal oscillator block which contains a 16 MHz HFINTOSC oscillator and a 31 kHz LFINTOSC oscillator, which together provide eight user selectable clock frequencies, from 31 kHz to 16 MHz. This option frees the two oscillator pins for use as additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both external and internal oscillator modes, which allows clock speeds of up to 64 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 64 MHz – all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

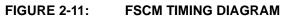

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the LFINTOSC. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or Wake-up from Sleep mode, until the primary clock source is available.

TABLE 2-4: REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7    | Bit 6     | Bit 5     | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|----------|-----------|-----------|---------|---------|--------|--------|--------|---------------------|

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE    | INT0IE  | RBIE    | TMR0IF | INTOIF | RBIF   | 109                 |

| IPR2    | OSCFIP   | C1IP      | C2IP      | EEIP    | BCL1IP  | HLVDIP | TMR3IP | CCP2IP | 122                 |

| OSCCON  | IDLEN    |           | IRCF<2:0> |         |         | HFIOFS | SCS    | 30     |                     |

| OSCCON2 | PLLRDY   | SOSCRUN   | —         | MFIOSEL | SOSCGO  | PRISD  | MFIOFS | LFIOFS | 31                  |

| OSCTUNE | INTSRC   | PLLEN     |           |         | TUN<5:( | )>     |        |        | 35                  |

| PIE2    | OSCFIE   | C1IE      | C2IE      | EEIE    | BCL1IE  | HLVDIE | TMR3IE | CCP2IE | 118                 |

| PIR2    | OSCFIF   | C1IF      | C2IF      | EEIF    | BCL1IF  | HLVDIF | TMR3IF | CCP2IF | 113                 |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by clock sources.

TABLE 2-5: CONFIGURATION REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name     | Bit 7 | Bit 6 | Bit 5    | Bit 4  | Bit 3  | Bit 2           | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------|-------|----------|--------|--------|-----------------|--------|--------|---------------------|

| CONFIG1H | IESO  | FCMEN | PRICLKEN | PLLCFG |        | FOSC            | 2<3:0> |        | 345                 |

| CONFIG2L | —     | —     | _        | BORV   | /<1:0> | 1:0> BOREN<1:0> |        | PWRTEN | 346                 |

| CONFIG3H | MCLRE | _     | P2BMX    | T3CMX  | HFOFST | CCP3MX          | PBADEN | CCP2MX | 348                 |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for clock sources.

## 4.3 Master Clear (MCLR)

The  $\overline{\text{MCLR}}$  pin provides a method for triggering an external Reset of the device. A Reset is generated by holding the pin low. These devices have a noise filter in the  $\overline{\text{MCLR}}$  Reset path which detects and ignores small pulses. An internal weak <u>pull-up</u> is enabled when the pin is configured as the  $\overline{\text{MCLR}}$  input.

The  $\overline{\text{MCLR}}$  pin is not driven low by any internal Resets, including the WDT.

In PIC18(L)F2X/4XK22 devices, the MCLR input can be disabled with the MCLRE Configuration bit. When MCLR is disabled, the pin becomes a digital input. See **Section 10.6 "PORTE Registers"** for more information.

## 4.4 **Power-on Reset (POR)**

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

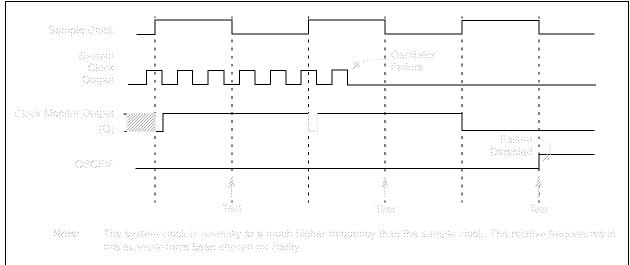

To take advantage of the POR circuitry either leave the pin floating, or tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified. For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure proper operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

POR events are captured by the POR bit of the RCON register. The state of the bit is set to '0' whenever a POR occurs; it does not change for any other Reset event. POR is not reset to '1' by any hardware event. To capture multiple events, the user must manually set the bit to '1' by software following any POR.

#### FIGURE 4-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $15 \text{ k}\Omega < R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

## 5.3 PIC18 Instruction Cycle

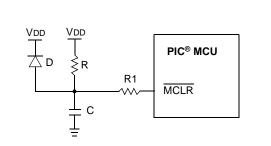

#### 5.3.1 CLOCKING SCHEME

The microcontroller clock input, whether from an internal or external source, is internally divided by four to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the program counter is incremented on every Q1; the instruction is fetched from the program memory and latched into the instruction register during Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 5-3.

#### 5.3.2 INSTRUCTION FLOW/PIPELINING

An "Instruction Cycle" consists of four Q cycles: Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 5-3).

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### EXAMPLE 5-3: INSTRUCTION PIPELINE FLOW

|                        | Тсү0       | TCY1      | Tcy2      | Tcy3        | TCY4          | TCY5                |

|------------------------|------------|-----------|-----------|-------------|---------------|---------------------|

| 1. MOVLW 55h           | Fetch 1    | Execute 1 |           |             | •             |                     |

| 2. MOVWF PORTB         |            | Fetch 2   | Execute 2 |             |               |                     |

| 3. BRA SUB_1           |            |           | Fetch 3   | Execute 3   |               |                     |

| 4. BSF PORTA, BIT3     | (Forced N  | OP)       |           | Fetch 4     | Flush (NOP)   |                     |

| 5. Instruction @ addr  | ress SUB_1 |           |           | Fetch SUB_1 | Execute SUB_1 |                     |

| Note: All instructions |            |           |           |             |               | vo cycles since the |

**Note:** All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### TABLE 10-1: PORTA I/O SUMMARY

| Pin Name                       | Function | TRIS<br>Setting | ANSEL<br>Setting | Pin<br>Type | Buffer<br>Type | Description                                                                                                          |

|--------------------------------|----------|-----------------|------------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------|

| RA0/C12IN0-/AN0                | RA0      | 0               | 0                | 0           | DIG            | LATA<0> data output; not affected by analog input.                                                                   |

|                                |          | 1               | 0                | Ι           | TTL            | PORTA<0> data input; disabled when analog input enabled.                                                             |

|                                | C12IN0-  | 1               | 1                | Ι           | AN             | Comparators C1 and C2 inverting input.                                                                               |

|                                | AN0      | 1               | 1                | I           | AN             | Analog input 0.                                                                                                      |

| RA1/C12IN1-/AN1                | RA1      | 0               | 0                | 0           | DIG            | LATA<1> data output; not affected by analog input.                                                                   |

|                                |          | 1               | 0                | I           | TTL            | PORTA<1> data input; disabled when analog input enabled.                                                             |

|                                | C12IN1-  | 1               | 1                | I           | AN             | Comparators C1 and C2 inverting input.                                                                               |

|                                | AN1      | 1               | 1                | I           | AN             | Analog input 1.                                                                                                      |

| RA2/C2IN+/AN2/<br>DACOUT/VREF- | RA2      | 0               | 0                | 0           | DIG            | LATA<2> data output; not affected by analog input; disabled when DACOUT enabled.                                     |

|                                |          | 1 0             |                  | Ι           | TTL            | PORTA<2> data input; disabled when analog input enabled;<br>disabled when DACOUT enabled.                            |

|                                | C2IN+    | 1               | 1                | Ι           | AN             | Comparator C2 non-inverting input.                                                                                   |

|                                | AN2      | 1               | 1                | Ι           | AN             | Analog output 2.                                                                                                     |

|                                | DACOUT   | x               | 1                | 0           | AN             | DAC Reference output.                                                                                                |

|                                | VREF-    | 1               | 1                | Ι           | AN             | A/D reference voltage (low) input.                                                                                   |

| RA3/C1IN+/AN3/                 | RA3      | 0               |                  | 0           | DIG            | LATA<3> data output; not affected by analog input.                                                                   |

| VREF+                          |          | 1               | 0                | I           | TTL            | PORTA<3> data input; disabled when analog input enabled.                                                             |

|                                | C1IN+    | 1               | 1                | I           | AN             | Comparator C1 non-inverting input.                                                                                   |

|                                | AN3      | 1               | 1                | I           | AN             | Analog input 3.                                                                                                      |

|                                | VREF+    | 1               | 1                | I           | AN             | A/D reference voltage (high) input.                                                                                  |

| RA4/CCP5/C1OUT/                | RA4      | 0               | —                | 0           | DIG            | LATA<4> data output.                                                                                                 |

| SRQ/T0CKI<br>-                 |          | 1               | _                | I           | ST             | PORTA<4> data input; default configuration on POR.                                                                   |

|                                | CCP5     | 0               | _                | 0           | DIG            | CCP5 Compare output/PWM output, takes priority over RA4 output                                                       |

|                                |          | 1               | —                | I           | ST             | Capture 5 input/Compare 5 output/ PWM 5 output.                                                                      |

|                                | C1OUT    | 0               | _                | 0           | DIG            | Comparator C1 output.                                                                                                |

|                                | SRQ      | 0               | _                | 0           | DIG            | SR latch Q output; take priority over CCP 5 output.                                                                  |

|                                | TOCKI    | 1               | _                | I           | ST             | Timer0 external clock input.                                                                                         |

| RA5/C2OUT/SRNQ/                | RA5      | 0               | 0                | 0           | DIG            | LATA<5> data output; not affected by analog input.                                                                   |

| SS1/<br>HLVDIN/AN4             |          | 1               | 0                | I           | TTL            | PORTA<5> data input; disabled when analog input enabled.                                                             |

| HLVDIN/AN4                     | C2OUT    | 0               | 0                | 0           | DIG            | Comparator C2 output.                                                                                                |

|                                | SRNQ     | 0               | 0                | 0           | DIG            | SR latch $\overline{Q}$ output.                                                                                      |

|                                | SS1      | 1               | 0                | I           | TTL            | SPI slave select input (MSSP1).                                                                                      |

|                                | HLVDIN   | 1               | 1                | I           | AN             | High/Low-Voltage Detect input.                                                                                       |

|                                | AN4      | 1               | 1                | 1           | AN             | A/D input 4.                                                                                                         |

| RA6/CLKO/OSC2                  | RA6      | 0               | _                | 0           | DIG            | LATA<6> data output; enabled in INTOSC modes when CLKO is no<br>enabled.                                             |

|                                |          | 1               | —                | Ι           | TTL            | PORTA<6> data input; enabled in INTOSC modes when CLKO is not enabled.                                               |

|                                | CLKO     | x               | —                | 0           | DIG            | In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the fre-<br>quency of OSC1 and denotes the instruction cycle rate. |

|                                | OSC2     | x               | _                | 0           | XTAL           | Oscillator crystal output; connects to crystal or resonator in Crystal Oscillator mode.                              |

| RA7/CLKI/OSC1                  | RA7      | 0               | _                | 0           | DIG            | LATA<7> data output; disabled in external oscillator modes.                                                          |

|                                |          | 1               | —                | Ι           | TTL            | PORTA<7> data input; disabled in external oscillator modes.                                                          |

|                                | CLKI     | x               | —                | I           | AN             | External clock source input; always associated with pin function OSC1.                                               |

|                                | OSC1     | x               |                  | Ι           | XTAL           | Oscillator crystal input or external clock source input ST buffer wher<br>configured in RC mode; CMOS otherwise.     |

Legend: AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C.

#### TABLE 10-15: REGISTERS ASSOCIATED WITH PORTE

| Name                  | Bit 7 | Bit 6   | Bit 5   | Bit 4               | Bit 3               | Bit 2                 | Bit 1                 | Bit 0                 | Reset<br>Values<br>on page |

|-----------------------|-------|---------|---------|---------------------|---------------------|-----------------------|-----------------------|-----------------------|----------------------------|

| ANSELE <sup>(1)</sup> |       | —       |         | —                   |                     | ANSE2                 | ANSE1                 | ANSE0                 | 151                        |

| INTCON2               | RBPU  | INTEDG0 | INTEDG1 | INTEDG2             |                     | TMR0IP                |                       | RBIP                  | 110                        |

| LATE <sup>(1)</sup>   | _     | —       | _       | —                   | _                   | LATE2                 | LATE1                 | LATE0                 | 152                        |

| PORTE                 | _     | —       | _       | —                   | RE3                 | RE2 <sup>(1)</sup>    | RE1 <sup>(1)</sup>    | RE0 <sup>(1)</sup>    | 149                        |

| SLRCON                | —     | —       | —       | SLRE <sup>(1)</sup> | SLRD <sup>(1)</sup> | SLRC                  | SLRB                  | SLRA                  | 153                        |

| TRISE                 | WPUE3 | _       | _       | _                   | _                   | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 151                        |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTE.

**Note 1:** Available on PIC18(L)F4XK22 devices.

#### TABLE 10-16: CONFIGURATION REGISTERS ASSOCIATED WITH PORTE

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2              | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------|-------|-------|-------|-------|--------|--------------------|--------|--------|----------------------------|

| CONFIG3H | MCLRE |       | P2BMX | T3CMX | HFOFST | CCP3MX             | PBADEN | CCP2MX | 348                        |

| CONFIG4L | DEBUG | XINST | _     | _     | _      | LVP <sup>(1)</sup> | _      | STRVEN | 349                        |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for Interrupts.

Note 1: Can only be changed when in high voltage programming mode.

| .egend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reservers         it 7-6       PxM       '0' = Bit is cleared         it 7-6       PxM       CPxM<3:2> = 00, 01, 10: (Capture/Compare modes)         xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins         Half-Bridge ECCP Modules <sup>(1)</sup> :       If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA, modulated; PxB assigned as port pin       1x = Half-Bridge output; PxA, PxB modulated with dead-band control         Full-Bridge ECCP Modules <sup>(1)</sup> :       If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA, nodulated; PxB assigned as port pin         1x = Half-Bridge output; PxA, PxB modulated with dead-band control         Full-Bridge ECCP Modules <sup>(1)</sup> :         If CCPxM<3:2> = 11: (PWM modes)         00 = Single output; PxA, modulated; PxB, PxC, PxD assigned as port pins         01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive         10 = Half-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as port pins         11 = Full-Bridge output; reverse; PxB modulated; PxC active; PxA, PxD inactive                                                                                                                                                                                                                                    | R/x-0                | R/W-0                                                | R/W-0                                                                       | R/W-0                                                          | R/W-0                                                 | R/W-0                             | R/W-0                   | R/W-0         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------|-----------------------------------|-------------------------|---------------|

| Aregend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         I = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Rese         I' = Bit is set       '0' = Bit is cleared         it 7-6 <b>PxM&lt;1:0</b> >: Enhanced PWM Output Configuration bits         If CCPxM<3:2> = 00, 01, 10: (Capture/Compare modes)         xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins         Half-Bridge ECCP Modules <sup>(1)</sup> :         If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA modulated; PxB assigned as port pin         1x = Half-Bridge output; PxA, modulated; PxB, PxC, PxD assigned as port pin         1x = Half-Bridge output; PxA, modulated; PxB, PxC, PxD assigned as port pin         1x = Half-Bridge output; PxA, modulated; PxB, PxC, PxD assigned as port pins         01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive         10 = Half-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as port pins         11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive         10 = Half-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive         11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive         11 = Full-Bridge output coverse; PxB modulated; PxC active; PxA, PxD inactive         11 = Full-Bridge output; PxA, PxB modulat                                                                                           | PxM                  | /<1:0>                                               | DCx                                                                         | 3<1:0>                                                         |                                                       | CCPx                              | V<3:0>                  |               |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         i = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reserverse         i' = Bit is set       '0' = Bit is cleared         wit 7-6       PxM<1:0>: Enhanced PWM Output Configuration bits         If CCPxM<3:2> = 00, 01, 10: (Capture/Compare modes)         xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins         Half-Bridge ECCP Modules <sup>(1)</sup> :         If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA modulated; PxB assigned as port pin         1x = Half-Bridge output; PxA, PxB modulated with dead-band control         Full-Bridge ECCP Modules <sup>(1)</sup> :         If CCPxM<3:2> = 11: (PWM modes)         00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pin         1x = Half-Bridge output; PxA, PxB modulated; PxA active; PxB, PxC inactive         10 = Single output; PxA, modulated; PxB pxC, PxD assigned as port pins         01 = Full-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as port pins         11 = Full-Bridge output; PxA, PxB modulated; with dead-band control; PxC, PxD assigned as port pins         11 = Full-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive         10 = Half-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive         11 = Full-Bridge output cycle Least Significant bits                                                                                                   | bit 7                |                                                      |                                                                             |                                                                |                                                       |                                   |                         | bit (         |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         i = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reserverse         i' = Bit is set       '0' = Bit is cleared         wit 7-6       PxM<1:0>: Enhanced PWM Output Configuration bits         If CCPxM<3:2> = 00, 01, 10: (Capture/Compare modes)         xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins         Half-Bridge ECCP Modules <sup>(1)</sup> :         If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA modulated; PxB assigned as port pin         1x = Half-Bridge output; PxA, PxB modulated with dead-band control         Full-Bridge ECCP Modules <sup>(1)</sup> :         If CCPxM<3:2> = 11: (PWM modes)         00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pin         1x = Half-Bridge output; PxA, PxB modulated; PxA active; PxB, PxC inactive         10 = Single output; PxA, modulated; PxB pxC, PxD assigned as port pins         01 = Full-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as port pins         11 = Full-Bridge output; PxA, PxB modulated; with dead-band control; PxC, PxD assigned as port pins         11 = Full-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive         10 = Half-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive         11 = Full-Bridge output cycle Least Significant bits                                                                                                   |                      |                                                      |                                                                             |                                                                |                                                       |                                   |                         |               |

| a = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reservers         it 7-6       PxM<1:0>: Enhanced PWM Output Configuration bits       If CCPxM<3:2> = 00, 01, 10: (Capture/Compare modes)         xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins       Half-Bridge ECCP Modules <sup>(1)</sup> :       If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA modulated; PxB assigned as port pin       1x = Half-Bridge cutput; PxA, PxB modulated with dead-band control         Full-Bridge ECCP Modules <sup>(1)</sup> :       If CCPxM<3:2> = 11: (PWM modes)       00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins         00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins       If CCPxM<3:2> = 11: (PWM modes)       00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins         01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive       10 = Half-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD assigned as port pins         11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive       11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive         11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive       Capture mode:         Unused       Compare mode:       Unused         Compare mode:       Unused       Compare mode:         Unused       PWM mode:       These bits are the two LSbs of the PWM duty cycle. The eight MSb | Legend:              |                                                      |                                                                             |                                                                |                                                       |                                   |                         |               |

| <ul> <li>i' = Bit is set</li> <li>'0' = Bit is cleared</li> <li>it 7-6</li> <li>PxM&lt;1:0&gt;: Enhanced PWM Output Configuration bits<br/>If CCPxM&lt;3:2&gt; = 00, 01, 10: (Capture/Compare modes)<br/>xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins</li> <li>Half-Bridge ECCP Modules<sup>(1)</sup>:<br/>If CCPxM&lt;3:2&gt; = 11: (PWM modes)</li> <li>0x = Single output; PxA modulated; PxB assigned as port pin<br/>1x = Half-Bridge output; PxA, PxB modulated with dead-band control</li> <li>Full-Bridge ECCP Modules<sup>(1)</sup>:<br/>If CCPxM&lt;3:2&gt; = 11: (PWM modes)</li> <li>00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins<br/>01 = Full-Bridge output; PxA modulated; PxB, PxC, PxD assigned as port pins<br/>01 = Full-Bridge output; PxA modulated; PxB modulated; PxA active; PxB, PxC inactive<br/>10 = Half-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD assigned as port<br/>pins<br/>11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive</li> <li>it 5-4</li> <li>DCxB&lt;1:0&gt;: PWM Duty Cycle Least Significant bits<br/>Capture mode:<br/>Unused<br/>Compare mode:<br/>Unused</li> <li>PWM mode:<br/>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.</li> </ul>                                                                                                                                                                                                                                                                                            | R = Readable         | e bit                                                | W = Writable b                                                              | bit                                                            | U = Unimple                                           | mented bit, rea                   | ad as '0'               |               |

| <ul> <li>PxM&lt;1:0&gt;: Enhanced PWM Output Configuration bits<br/>If CCPxM&lt;3:2&gt; = 00, 01, 10: (Capture/Compare modes)<br/>xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins<br/>Half-Bridge ECCP Modules<sup>(1)</sup>:<br/>If CCPxM&lt;3:2&gt; = 11: (PWM modes)<br/>0x = Single output; PxA modulated; PxB assigned as port pin<br/>1x = Half-Bridge output; PxA, PxB modulated with dead-band control<br/>Full-Bridge ECCP Modules<sup>(1)</sup>:<br/>If CCPxM&lt;3:2&gt; = 11: (PWM modes)<br/>00 = Single output; PxA, modulated; PxB, PxC, PxD assigned as port pins<br/>01 = Full-Bridge output; PxA modulated; PxB, PxC, PxD assigned as port pins<br/>01 = Full-Bridge output; PxA, PxB modulated; PxA active; PxB, PxC inactive<br/>10 = Half-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive<br/>11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive<br/>12 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive<br/>13 = Full-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive<br/>14 = Full-Bridge output; PxB modulated; PxC active; PxA, PxD inactive<br/>15 = Unused<br/>Compare mode:<br/>Unused<br/><u>PWM mode:</u><br/>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.</li> </ul>                                                                                                                                                                                                                                                                 | u = Bit is unchanged |                                                      | x = Bit is unkn                                                             | own                                                            | -n/n = Value                                          | at POR and B                      | OR/Value at al          | I other Reset |

| If CCPxM<3:2> = 00, 01, 10: (Capture/Compare modes)<br>xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins<br>Half-Bridge ECCP Modules <sup>(1)</sup> :<br>If CCPxM<3:2> = 11: (PWM modes)<br>0x = Single output; PxA modulated; PxB assigned as port pin<br>1x = Half-Bridge output; PxA, PxB modulated with dead-band control<br>Full-Bridge ECCP Modules <sup>(1)</sup> :<br>If CCPxM<3:2> = 11: (PWM modes)<br>00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins<br>01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive<br>10 = Half-Bridge output forward; PxD modulated with dead-band control; PxC, PxD assigned as port<br>pins<br>11 = Full-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive<br>11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive<br>11 = Full-Bridge output cycle Least Significant bits<br>Capture mode:<br>Unused<br>Compare mode:<br>Unused<br>PWM mode:<br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | '1' = Bit is set     | t                                                    | '0' = Bit is clea                                                           | red                                                            |                                                       |                                   |                         |               |

| If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA modulated; PxB assigned as port pin         1x = Half-Bridge output; PxA, PxB modulated with dead-band control         Full-Bridge ECCP Modules <sup>(1)</sup> :<br>If CCPxM<3:2> = 11: (PWM modes)         00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins         01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive         10 = Half-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as por<br>pins         11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive         it 5-4       DCxB<1:0>: PWM Duty Cycle Least Significant bits         Capture mode:<br>Unused       Unused         PWM mode:<br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 7-6              | ľ                                                    | f CCPxM<3:2> =                                                              | 00, 01, 10:                                                    | (Capture/Comp                                         | ,                                 | l as port pins          |               |

| <ul> <li>If CCPxM&lt;3:2&gt; = 11: (PWM modes)</li> <li>00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins</li> <li>01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive</li> <li>10 = Half-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as por pins</li> <li>11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive</li> <li>bit 5-4</li> <li>bit 5-4</li> <li>bit 5-4</li> <li>bit 5-4</li> <li>capture mode:<br/>Unused</li> <li>Unused</li> <li>compare mode:<br/>Unused</li> <li>PWM mode:<br/>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      | ار<br>0x = Singl                                     | CCPxM<3:2> =<br>e output; PxA mo                                            | 11: (PWM mo<br>dulated; PxB a                                  | assigned as port                                      |                                   |                         |               |

| Capture mode:<br>Unused<br>Compare mode:<br>Unused<br><u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | ا<br>00 = Singl<br>01 = Full-E<br>10 = Half-<br>pins | CCPxM<3:2> =<br>e output; PxA mo<br>Bridge output forw<br>Bridge output; Px | 11: (PWM mod<br>dulated; PxB,<br>vard; PxD mod<br>A, PxB modul | PxC, PxD assig<br>ulated; PxA acti<br>ated with dead- | ve; PxB, PxC i<br>band control; I | nactive<br>PxC, PxD ass | igned as por  |

| Unused<br><u>Compare mode:</u><br>Unused<br><u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 5-4              | DCxB<1:0:                                            | -: PWM Duty Cyc                                                             | le Least Signi                                                 | ficant bits                                           |                                   |                         |               |

| Unused<br><u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                                                      | ode:                                                                        |                                                                |                                                       |                                   |                         |               |

| These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      | •                                                    | node:                                                                       |                                                                |                                                       |                                   |                         |               |

| lote 1: See Table 14-1 to determine full-bridge and half-bridge ECCPs for the device being used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |                                                      |                                                                             | of the PWM d                                                   | uty cycle. The e                                      | ight MSbs are t                   | found in CCPF           | RxL.          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Note 1: Se           | ee Table 14-1 t                                      | o determine full-b                                                          | oridge and half                                                | -bridge ECCPs                                         | for the device b                  | being used.             |               |

#### REGISTER 14-2: CCPxCON: ENHANCED CCPx CONTROL REGISTER

| R/W-0                                                                                                                            | R/W-0            | R/W-0                                                                                   | R/W-0      | R/W-0                                                 | R/W-0                         | R/W-0        | R/W-0          |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------|------------|-------------------------------------------------------|-------------------------------|--------------|----------------|--|--|--|--|

| PxRSEN                                                                                                                           |                  |                                                                                         |            | PxDC<6:0>                                             |                               |              |                |  |  |  |  |

| bit 7                                                                                                                            |                  |                                                                                         |            |                                                       |                               |              | bit 0          |  |  |  |  |

|                                                                                                                                  |                  |                                                                                         |            |                                                       |                               |              |                |  |  |  |  |

| Legend:                                                                                                                          |                  |                                                                                         |            |                                                       |                               |              |                |  |  |  |  |

| R = Readable bit                                                                                                                 |                  | W = Writable                                                                            | bit        | U = Unimpler                                          | nimplemented bit, read as '0' |              |                |  |  |  |  |

| u = Bit is unchanged                                                                                                             |                  | x = Bit is unknown                                                                      |            | -n/n = Value at POR and BOR/Value at all other Resets |                               |              |                |  |  |  |  |

| '1' = Bit is set                                                                                                                 | '1' = Bit is set |                                                                                         | ared       |                                                       |                               |              |                |  |  |  |  |

|                                                                                                                                  |                  |                                                                                         |            |                                                       |                               |              |                |  |  |  |  |

| bit 7                                                                                                                            | PxRSEN: P        | WM Restart Ena                                                                          | able bit   |                                                       |                               |              |                |  |  |  |  |

| 1 = Upon auto-shutdown, the CCPxASE bit clears automatically once the shutdown event goes away<br>the PWM restarts automatically |                  |                                                                                         |            |                                                       |                               |              | ent goes away; |  |  |  |  |

|                                                                                                                                  | 0 = Upon a       | uto-shutdown, C                                                                         | CPxASE mus | st be cleared in s                                    | software to rest              | tart the PWM |                |  |  |  |  |

| bit 6-0                                                                                                                          | PxDC<6:0>        | : PWM Delay Co                                                                          | ount bits  |                                                       |                               |              |                |  |  |  |  |

|                                                                                                                                  | PxDCx = N        | PxDCx = Number of Fosc/4 (4 * Tosc) cycles between the scheduled time when a PWM signal |            |                                                       |                               |              |                |  |  |  |  |

#### REGISTER 14-6: PWMxCON: ENHANCED PWM CONTROL REGISTER

#### REGISTER 14-7: PSTRxCON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-1 |

|-------|-----|-----|----------|-------|-------|-------|-------|

| —     | —   | —   | STRxSYNC | STRxD | STRxC | STRxB | STRxA |

| bit 7 |     |     |          |       |       |       | bit 0 |

should transition active and the actual time it transitions active

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                         |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <b>STRxSYNC:</b> Steering Sync bit<br>1 = Output steering update occurs on next PWM period<br>0 = Output steering update occurs at the beginning of the instruction cycle boundary |

| bit 3   | <b>STRxD:</b> Steering Enable bit D<br>1 = PxD pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxD pin is assigned to port pin                               |

| bit 2   | <b>STRxC:</b> Steering Enable bit C<br>1 = PxC pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxC pin is assigned to port pin                               |

| bit 1   | <b>STRxB:</b> Steering Enable bit B<br>1 = PxB pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxB pin is assigned to port pin                               |

| bit 0   | <b>STRxA:</b> Steering Enable bit A<br>1 = PxA pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxA pin is assigned to port pin                               |

| Note 1. | The DWM Steering mode is evoluble only when the CCDyCON register hits CCDyM (20) 11.0                                                                                              |

**Note 1:** The PWM Steering mode is available only when the CCPxCON register bits CCPxM<3:2> = 11 and PxM<1:0> = 00.

#### 15.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

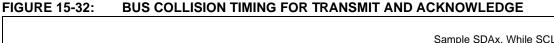

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF, and reset the I<sup>2</sup>C port to its Idle state (Figure 15-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $l^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

| R/W-0         | R/W-0                     | R/W-0                                                     | R/W-0             | R/W-0           | R-0               | R-0                                | R-0     |

|---------------|---------------------------|-----------------------------------------------------------|-------------------|-----------------|-------------------|------------------------------------|---------|

| SPEN          | RX9                       | SREN                                                      | CREN              | ADDEN           | FERR              | OERR                               | RX9D    |

| bit 7         |                           |                                                           |                   |                 |                   |                                    | bit     |

| Legend:       |                           |                                                           |                   |                 |                   |                                    |         |

| R = Readable  | e bit                     | W = Writable                                              | e bit             | U = Unimple     | emented bit, rea  | d as '0'                           |         |

| -n = Value at | POR                       | '1' = Bit is se                                           | t                 | ʻ0' = Bit is cl | eared             | x = Bit is unkr                    | nown    |

| bit 7         |                           | al Port Enable b                                          |                   |                 |                   |                                    |         |

|               |                           | port enabled (co<br>port disabled (he                     |                   | DTx and TXx/    | CKx pins as ser   | ial port pins)                     |         |

| bit 6         | <b>RX9:</b> 9-bit F       | Receive Enable                                            | bit               |                 |                   |                                    |         |

|               |                           | <ul><li>9-bit reception</li><li>8-bit reception</li></ul> |                   |                 |                   |                                    |         |

| bit 5         | SREN: Sing                | gle Receive Ena                                           | ble bit           |                 |                   |                                    |         |

|               | Asynchrono                | ous mode:                                                 |                   |                 |                   |                                    |         |

|               | Don't care                |                                                           |                   |                 |                   |                                    |         |

|               |                           | <u>is mode – Maste</u>                                    |                   |                 |                   |                                    |         |

|               |                           | s single receive<br>es single receive                     |                   |                 |                   |                                    |         |

|               |                           | leared after rece                                         |                   | ete.            |                   |                                    |         |

|               | <u>Synchronou</u>         | <u>ıs mode – Slave</u>                                    | <u>.</u>          |                 |                   |                                    |         |

|               | Don't care                |                                                           |                   |                 |                   |                                    |         |

| bit 4         | CREN: Con                 | tinuous Receive                                           | e Enable bit      |                 |                   |                                    |         |

|               | <u>Asynchronc</u>         |                                                           |                   |                 |                   |                                    |         |

|               | 1 = Enable                |                                                           |                   |                 |                   |                                    |         |

|               | 0 = Disable<br>Synchronou |                                                           |                   |                 |                   |                                    |         |

|               |                           |                                                           | ceive until enal  | hle hit CREN    | is cleared (CRF   | N overrides SR                     | EN)     |

|               |                           | es continuous re                                          |                   |                 |                   |                                    |         |

| bit 3         | ADDEN: Ad                 | dress Detect E                                            | nable bit         |                 |                   |                                    |         |

|               | Asynchronc                | ous mode 9-bit (                                          | <u>RX9 = 1)</u> : |                 |                   |                                    |         |

|               | 0 = Disable               |                                                           | ction, all bytes  |                 |                   | ouffer when RSF<br>n be used as pa |         |

|               | Don't care                |                                                           |                   |                 |                   |                                    |         |

| bit 2         | FERR: Frar                | ning Error bit                                            |                   |                 |                   |                                    |         |

|               | 1 = Framin<br>0 = No fran |                                                           | updated by rea    | ading RCREG     | x register and re | eceive next valio                  | d byte) |

| bit 1         | OERR: Ove                 | errun Error bit                                           |                   |                 |                   |                                    |         |

|               | 1 = Overru<br>0 = No ove  | n error (can be o<br>rrun error                           | cleared by clea   | aring bit CREN  | 1)                |                                    |         |

| bit 0         | RX9D: Nint                | h bit of Receive                                          | d Data            |                 |                   |                                    |         |

|               |                           |                                                           | abata             |                 |                   |                                    |         |

# REGISTER 16-2: RCSTAX: RECEIVE STATUS AND CONTROL REGISTER

#### 17.1.7 RESULT FORMATTING

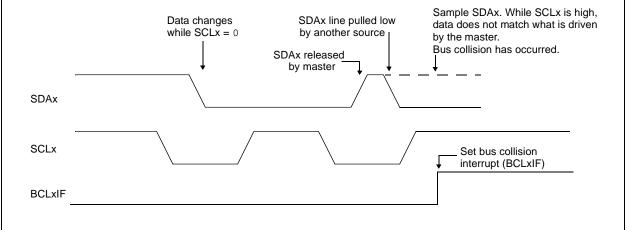

The 10-bit A/D conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON2 register controls the output format.

Figure 17-2 shows the two output formats.

## FIGURE 17-2: 10-BIT A/D CONVERSION RESULT FORMAT

|                 |                                                                                                                                               |                                          | -               |                  |                 |                 |        |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------|------------------|-----------------|-----------------|--------|--|--|--|

| R-0             | R-0                                                                                                                                           | R/W-0                                    | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0  |  |  |  |

| MC1OUT          | MC2OUT                                                                                                                                        | C1RSEL                                   | C2RSEL          | C1HYS            | C2HYS           | C1SYNC          | C2SYNC |  |  |  |