Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 30x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k22-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 2: | PIC18(L)F2XK22 PIN SUMMARY |

|----------|----------------------------|

|----------|----------------------------|

| IAD                       |              |     |        | FZANZZ     | 1 114 50 |          |                 |                                                  |         |              |                                               |            |         |              |

|---------------------------|--------------|-----|--------|------------|----------|----------|-----------------|--------------------------------------------------|---------|--------------|-----------------------------------------------|------------|---------|--------------|

| 28-SSOP, SOIC<br>28-SPDIP | 28-QFN, UQFN | 0/1 | Analog | Comparator | СТМИ     | SR Latch | Reference       | (E)CCP                                           | EUSART  | MSSP         | Timers                                        | Interrupts | dn-lluq | Basic        |

| 2                         | 27           | RA0 | AN0    | C12IN0-    |          |          |                 |                                                  |         |              |                                               |            |         |              |

| 3                         | 28           | RA1 | AN1    | C12IN1-    |          |          |                 |                                                  |         |              |                                               |            |         |              |

| 4                         | 1            | RA2 | AN2    | C2IN+      |          |          | VREF-<br>DACOUT |                                                  |         |              |                                               |            |         |              |

| 5                         | 2            | RA3 | AN3    | C1IN+      |          |          | VREF+           |                                                  |         |              |                                               |            |         |              |

| 6                         | 3            | RA4 |        | C1OUT      |          | SRQ      |                 | CCP5                                             |         |              | TOCKI                                         |            |         |              |

| 7                         | 4            | RA5 | AN4    | C2OUT      |          | SRNQ     | HLVDIN          |                                                  |         | SS1          |                                               |            |         |              |

| 10                        | 7            | RA6 |        |            |          |          |                 |                                                  |         |              |                                               |            |         | OSC2<br>CLKO |

| 9                         | 6            | RA7 |        |            |          |          |                 |                                                  |         |              |                                               |            |         | OSC1<br>CLKI |

| 21                        | 18           | RB0 | AN12   |            |          | SRI      |                 | CCP4<br>FLT0                                     |         | SS2          |                                               | INT0       | Y       |              |

| 22                        | 19           | RB1 | AN10   | C12IN3-    |          |          |                 | P1C                                              |         | SCK2<br>SCL2 |                                               | INT1       | Y       |              |

| 23                        | 20           | RB2 | AN8    |            | CTED1    |          |                 | P1B                                              |         | SDI2<br>SDA2 |                                               | INT2       | Y       |              |

| 24                        | 21           | RB3 | AN9    | C12IN2-    | CTED2    |          |                 | CCP2<br>P2A <sup>(1)</sup>                       |         | SDO2         |                                               |            | Y       |              |

| 25                        | 22           | RB4 | AN11   |            |          |          |                 | P1D                                              |         |              | T5G                                           | IOC        | Υ       |              |

| 26                        | 23           | RB5 | AN13   |            |          |          |                 | CCP3<br>P3A <sup>(4)</sup><br>P2B <sup>(3)</sup> |         |              | T1G<br>T3CKI <sup>(2)</sup>                   | IOC        | Y       |              |

| 27                        | 24           | RB6 |        |            |          |          |                 |                                                  | TX2/CK2 |              |                                               | IOC        | Y       | PGC          |

| 28                        | 25           | RB7 |        |            |          |          |                 |                                                  | RX2/DT2 |              |                                               | IOC        | Y       | PGD          |

| 11                        | 8            | RC0 |        |            |          |          |                 | P2B <sup>(3)</sup>                               |         |              | SOSCO<br>T1CKI<br>T3CKI <sup>(2)</sup><br>T3G |            |         |              |

| 12                        | 9            | RC1 |        |            |          |          |                 | CCP2<br>P2A <sup>(1)</sup>                       |         |              | SOSCI                                         |            |         |              |

| 13                        | 10           | RC2 | AN14   |            | CTPLS    |          |                 | CCP1<br>P1A                                      |         |              | T5CKI                                         |            |         |              |

| 14                        | 11           | RC3 | AN15   |            |          |          |                 |                                                  |         | SCK1<br>SCL1 |                                               |            |         |              |

| 15                        | 12           | RC4 | AN16   |            |          |          |                 |                                                  |         | SDI1<br>SDA1 |                                               |            |         |              |

| 16                        | 13           | RC5 | AN17   |            |          |          |                 |                                                  |         | SDO1         |                                               |            |         |              |

| 17                        | 14           | RC6 | AN18   |            |          |          |                 | CCP3<br>P3A <sup>(4)</sup>                       | TX1/CK1 |              |                                               |            |         |              |

| 18                        | 15           | RC7 | AN19   |            |          |          |                 | P3B                                              | RX1/DT1 |              |                                               |            |         |              |

| 1                         | 26           | RE3 |        |            |          |          |                 |                                                  |         |              |                                               |            |         | MCLR<br>VPP  |

| 8, 19<br>19               | 5, 16<br>16  | Vss |        |            |          |          |                 |                                                  |         |              |                                               |            |         | Vss          |

| 20                        | 17           | Vdd |        |            |          |          |                 |                                                  |         |              |                                               |            |         | Vdd          |

|                           |              |     |        |            |          |          |                 |                                                  |         |              |                                               |            |         |              |

CCP2/P2A multiplexed in fuses.

T3CKI multiplexed in fuses.

P2B multiplexed in fuses.

CCP3/P3A multiplexed in fuses. Note 1:

#### TABLE 3: PIC18(L)F4XK22 PIN SUMMARY (CONTINUED)

|           | •.      | -                |               | -,  |        |            |      | (        |           | ,      |        |             |        |            |         |             |

|-----------|---------|------------------|---------------|-----|--------|------------|------|----------|-----------|--------|--------|-------------|--------|------------|---------|-------------|

| 40-PDIP   | 40-UQFN | 44-TQFP          | 44-QFN        | 0/1 | Analog | Comparator | стми | SR Latch | Reference | (E)CCP | EUSART | <b>JSSM</b> | Timers | Interrupts | Pull-up | Basic       |

| 9         | 24      | 26               | 26            | RE1 | AN6    |            |      |          |           | P3B    |        |             |        |            |         |             |

| 10        | 25      | 27               | 27            | RE2 | AN7    |            |      |          |           | CCP5   |        |             |        |            |         |             |

| 1         | 16      | 18               | 18            | RE3 |        |            |      |          |           |        |        |             |        |            | Y       | MCLR<br>VPP |

| 11,<br>32 | 7, 26   | 7,<br>28         | 7,8<br>28, 29 | Vdd |        |            |      |          |           |        |        |             |        |            |         | Vdd         |

| 12,<br>31 | 6, 27   | 6,<br>29         | 6,<br>30, 31  | Vss |        |            |      |          |           |        |        |             |        |            |         | Vss         |

| —         | —       | 12, 13<br>33, 34 | 13            | NC  |        |            |      |          |           |        |        |             |        |            |         |             |

CCP2 multiplexed in fuses. T3CKI multiplexed in fuses. Note 1:

2:

3: CCP3/P3A multiplexed in fuses.

4: P2B multiplexed in fuses.

## 3.6 Selective Peripheral Module Control

Idle mode allows users to substantially reduce power consumption by stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what IDLE mode does not provide: the allocation of power resources to the CPU processing with minimal power consumption from the peripherals. PIC18(L)F2X/4XK22 family devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with control bits in the Peripheral Module Disable (PMD) registers. These bits generically named XXXMD are located in control registers PMD0, PMD1 or PMD2.

Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, power to the control and status registers associated with the peripheral is removed. Writes to these registers have no effect and read values are invalid. Clearing a set PMD bit restores power to the associated control and status registers, thereby setting those registers to their default values.

## 3.7 Register Definitions: Peripheral Module Disable

### REGISTER 3-1: PMD0: PERIPHERAL MODULE DISABLE REGISTER 0

| R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|---------|--------|--------|--------|--------|--------|--------|

| UART2MD | UART1MD | TMR6MD | TMR5MD | TMR4MD | TMR3MD | TMR2MD | TMR1MD |

| bit 7   | ·       |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7 | UART2MD: UART2 Peripheral Module Disable Control bit                                                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 6 | UART1MD: UART1 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 5 | TMR6MD: Timer6 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 4 | TMR5MD: Timer5 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 3 | TMR4MD: Timer4 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 2 | TMR3MD: Timer3 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 1 | TMR2MD: Timer2 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 0 | TMR1MD: Timer1 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

|       |                                                                                                                                                                                                    |

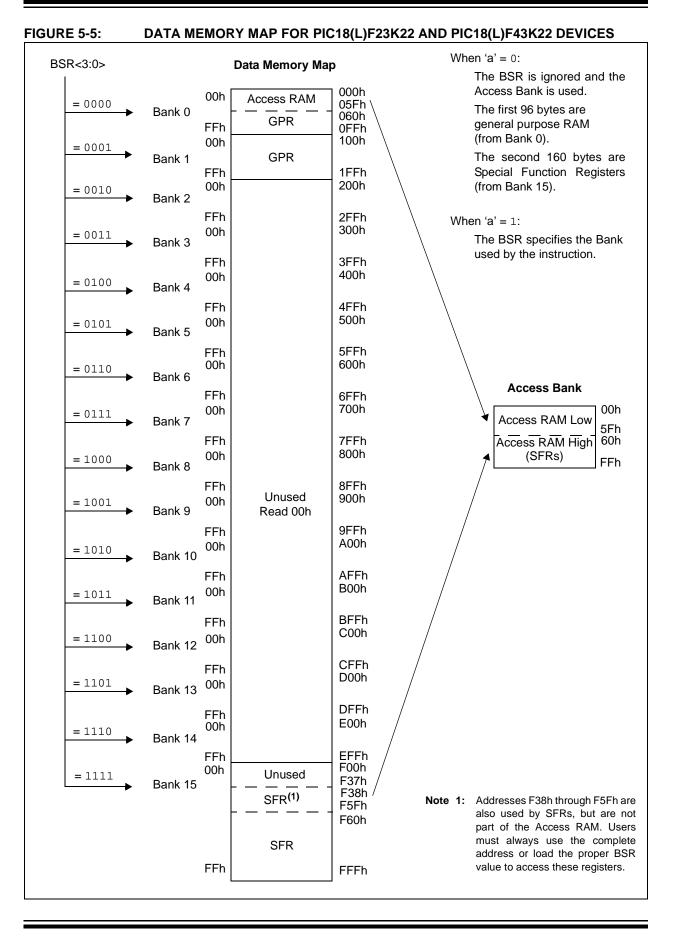

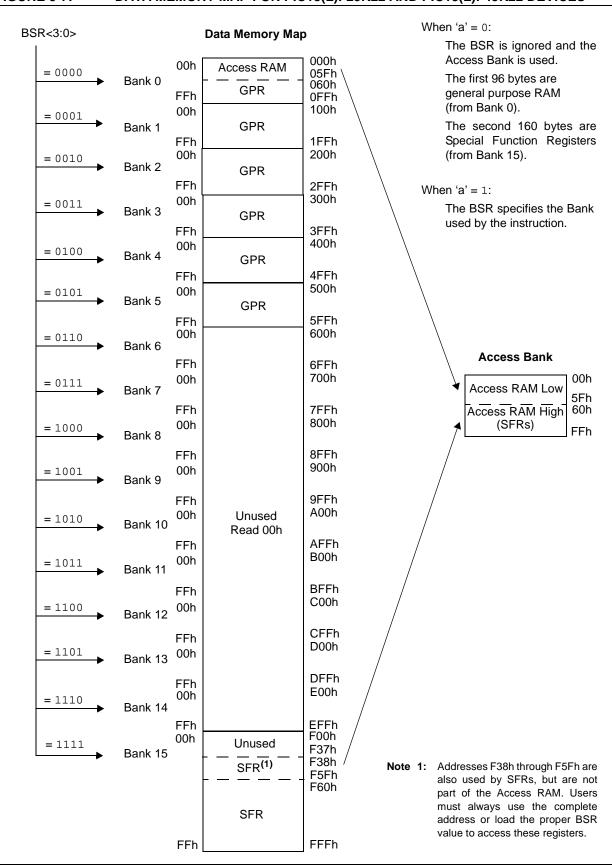

## 5.6 Data Addressing Modes

Note: The execution of some instructions in the core PIC18 instruction set are changed when the PIC18 extended instruction set is enabled. See Section 5.7 "Data Memory and the Extended Instruction Set" for more information.

While the program memory can be addressed in only one way – through the program counter – information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 5.7.1** "**Indexed Addressing with Literal Offset**".

## 5.6.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

### 5.6.2 DIRECT ADDRESSING

Direct addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byteoriented instructions use some version of direct addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (**Section 5.4.3 "General**  **Purpose Register File**") or a location in the Access Bank (Section 5.4.2 "Access Bank") as the data source for the instruction.

The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 5.4.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

## 5.6.3 INDIRECT ADDRESSING

Indirect addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations which are to be read or written. Since the FSRs are themselves located in RAM as Special File Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for indirect addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 5-5.

## EXAMPLE 5-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0, 100h | ; |                |

|---------|-------|------------|---|----------------|

| NEXT    | CLRF  | POSTINC0   | ; | Clear INDF     |

|         |       |            | ; | register then  |

|         |       |            | ; | inc pointer    |

|         | BTFSS | FSROH, 1   | ; | All done with  |

|         |       |            | ; | Bank1?         |

|         | BRA   | NEXT       | ; | NO, clear next |

| CONTINU | JE    |            | ; | YES, continue  |

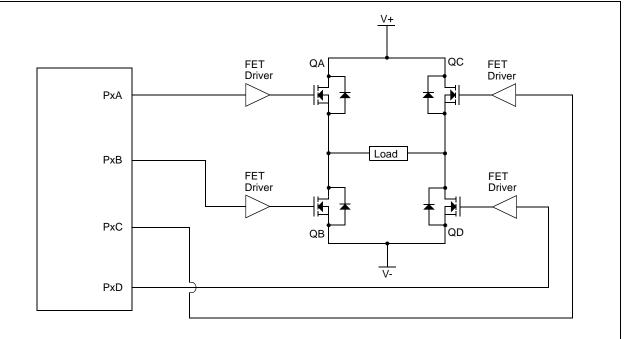

### 14.4.2 FULL-BRIDGE MODE

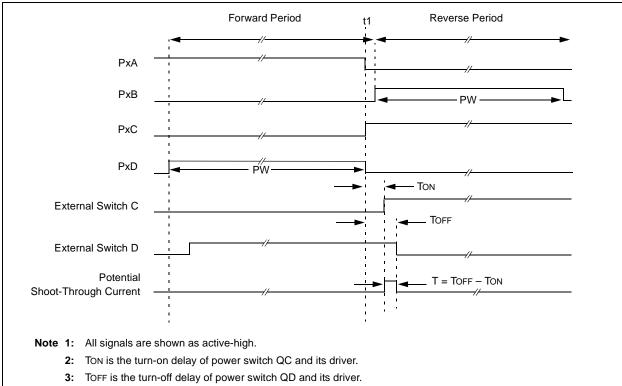

In Full-Bridge mode, all four pins are used as outputs. An example of full-bridge application is shown in Figure 14-10.

In the Forward mode, pin CCPx/PxA is driven to its active state, pin PxD is modulated, while PxB and PxC will be driven to their inactive state as shown in Figure 14-11.

In the Reverse mode, PxC is driven to its active state, pin PxB is modulated, while PxA and PxD will be driven to their inactive state as shown Figure 14-11.

PxA, PxB, PxC and PxD outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the PxA, PxB, PxC and PxD pins as outputs.

### FIGURE 14-10: EXAMPLE OF FULL-BRIDGE APPLICATION

### 14.4.3 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the CCPxAS<2:0> bits of the ECCPxAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- Comparator Cx (async\_CxOUT)

- Setting the CCPxASE bit in firmware

A shutdown condition is indicated by the CCPxASE (Auto-Shutdown Event Status) bit of the ECCPxAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The CCPxASE bit is set to '1'. The CCPxASE will remain set until cleared in firmware or an auto-restart occurs (see Section 14.4.4 "Auto-Restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [PxA/PxC] and [PxB/PxD].

The state of each pin pair is determined by the PSSxAC<1:0> and PSSxBD<1:0> bits of the ECCPxAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

Note 1: The auto-shutdown condition is a levelbased signal, not an edge-based signal. As long as the level is present, the autoshutdown will persist.

- 2: Writing to the CCPxASE bit is disabled while an auto-shutdown condition persists.

- 3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

### 15.6.2 CLOCK ARBITRATION

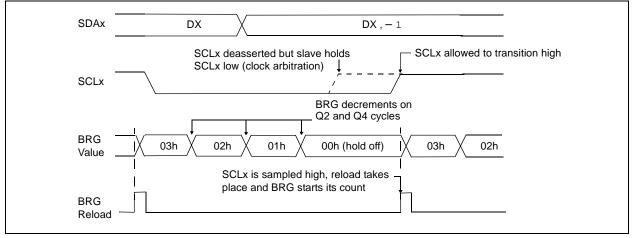

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCLx pin (SCLx allowed to float high). When the SCLx pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCLx pin is actually sampled high. When the SCLx pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and begins counting. This ensures that the SCLx high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 15-25).

### FIGURE 15-25: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

## 15.6.3 WCOL STATUS FLAG

If the user writes the SSPxBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPxBUF was attempted while the module was not Idle.

| Note: | Because queueing of events is not         |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|

|       | allowed, writing to the lower 5 bits of   |  |  |  |  |  |

|       | SSPxCON2 is disabled until the Start con- |  |  |  |  |  |

|       | dition is complete.                       |  |  |  |  |  |

## 15.8 Register Definitions: MSSP Control

#### REGISTER 15-2: SSPxSTAT: SSPx STATUS REGISTER

| R/W-0            | R/W-0                                           | R-0                                                                                                 | R-0                                        | R-0                                       | R-0                  | R-0                 | R-0           |  |  |  |  |

|------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------|----------------------|---------------------|---------------|--|--|--|--|

| SMP              | CKE                                             | D/A                                                                                                 | Р                                          | S                                         | R/W                  | UA                  | BF            |  |  |  |  |

| bit 7            | •                                               |                                                                                                     | 1                                          | 1                                         |                      |                     | bit (         |  |  |  |  |

|                  |                                                 |                                                                                                     |                                            |                                           |                      |                     |               |  |  |  |  |

| Legend:          |                                                 |                                                                                                     |                                            |                                           |                      |                     |               |  |  |  |  |

| R = Readable b   | bit                                             | W = Writable b                                                                                      | bit                                        | U = Unimplem                              | ented bit, read as   | '0'                 |               |  |  |  |  |

| u = Bit is uncha | nged                                            | x = Bit is unkn                                                                                     | own                                        | -n/n = Value a                            | t POR and BOR/V      | alue at all other F | Resets        |  |  |  |  |

| '1' = Bit is set |                                                 | '0' = Bit is clea                                                                                   | ired                                       |                                           |                      |                     |               |  |  |  |  |

| L '1 <b>7</b>    |                                                 |                                                                                                     | •,                                         |                                           |                      |                     |               |  |  |  |  |

| bit 7            |                                                 | a Input Sample b                                                                                    | DIT                                        |                                           |                      |                     |               |  |  |  |  |

|                  | <u>SPI Master mo</u><br>1 = Input data          | sampled at end                                                                                      | of data output                             | time                                      |                      |                     |               |  |  |  |  |

|                  | •                                               | sampled at mide                                                                                     | •                                          |                                           |                      |                     |               |  |  |  |  |

|                  | <u>SPI Slave moo</u><br>SMP must be             | <u>de:</u><br>cleared when SF                                                                       | PI is used in Sla                          | ave mode                                  |                      |                     |               |  |  |  |  |

|                  | In I <sup>2</sup> C Master                      | or Slave mode:                                                                                      |                                            |                                           |                      |                     |               |  |  |  |  |

|                  |                                                 |                                                                                                     |                                            | peed mode (100 k<br>mode (400 kHz)        | (Hz and 1 MHz)       |                     |               |  |  |  |  |

| bit 6            | CKE: SPI Cloo                                   | ck Edge Select b                                                                                    | it (SPI mode o                             | nly)                                      |                      |                     |               |  |  |  |  |

|                  |                                                 | or Slave mode:                                                                                      | ,                                          |                                           |                      |                     |               |  |  |  |  |

|                  |                                                 |                                                                                                     |                                            | to Idle clock state<br>active clock state |                      |                     |               |  |  |  |  |

|                  |                                                 | 0 = Transmit occurs on transition from Idle to active clock state<br>In I <sup>2</sup> C mode only: |                                            |                                           |                      |                     |               |  |  |  |  |

|                  |                                                 | out logic so that t<br>Mbus specific inp                                                            |                                            | compliant with SN                         | lbus specification   |                     |               |  |  |  |  |

| bit 5            | D/A: Data/Add                                   | Iress bit (I <sup>2</sup> C mo                                                                      | de only)                                   |                                           |                      |                     |               |  |  |  |  |

|                  |                                                 |                                                                                                     |                                            | nsmitted was data                         |                      |                     |               |  |  |  |  |

|                  |                                                 | nat the last byte                                                                                   | received or tra                            | nsmitted was add                          | ress                 |                     |               |  |  |  |  |

| bit 4            | P: Stop bit                                     | . This hit is sleep                                                                                 |                                            |                                           |                      |                     |               |  |  |  |  |

|                  |                                                 |                                                                                                     |                                            | d last (this bit is '                     | disabled, SSPxEN     | N IS cleared.)      |               |  |  |  |  |

|                  |                                                 | as not detected la                                                                                  |                                            |                                           | ,                    |                     |               |  |  |  |  |

| bit 3            | S: Start bit                                    |                                                                                                     |                                            |                                           |                      |                     |               |  |  |  |  |

|                  |                                                 |                                                                                                     |                                            |                                           | disabled, SSPxEN     | l is cleared.)      |               |  |  |  |  |

|                  |                                                 | hat a Start bit ha<br>as not detected l                                                             |                                            | d last (this bit is '                     | o' on Reset)         |                     |               |  |  |  |  |

| bit 2            |                                                 | rite bit informatio                                                                                 |                                            |                                           |                      |                     |               |  |  |  |  |

|                  | This bit holds t                                | he R/W bit inforn<br>Int bit, Stop bit, or                                                          | natio <u>n foll</u> owing<br>: not ACK bit | the last address                          | match. This bit is o | only valid from the | address match |  |  |  |  |

|                  | In I <sup>2</sup> C Slave m                     |                                                                                                     | not not of bit.                            |                                           |                      |                     |               |  |  |  |  |

|                  | 1 = Read                                        |                                                                                                     |                                            |                                           |                      |                     |               |  |  |  |  |

|                  | 0 = Write                                       |                                                                                                     |                                            |                                           |                      |                     |               |  |  |  |  |

|                  | <u>In I<sup>2</sup>C Master</u><br>1 = Transmit |                                                                                                     |                                            |                                           |                      |                     |               |  |  |  |  |

|                  |                                                 | is not in progres                                                                                   | s                                          |                                           |                      |                     |               |  |  |  |  |

|                  | -                                               |                                                                                                     |                                            |                                           | will indicate if the | MSSPx is in Idle    | mode.         |  |  |  |  |

| bit 1            |                                                 | ddress bit (10-bit                                                                                  |                                            |                                           |                      |                     |               |  |  |  |  |

|                  |                                                 | hat the user nee<br>oes not need to l                                                               |                                            | e address in the s                        | SSPxADD registe      | r                   |               |  |  |  |  |

| bit 0            | BF: Buffer Ful                                  |                                                                                                     |                                            |                                           |                      |                     |               |  |  |  |  |

| Dit U            |                                                 | and I <sup>2</sup> C modes):                                                                        |                                            |                                           |                      |                     |               |  |  |  |  |

|                  |                                                 | omplete, SSPxB                                                                                      | UF is full                                 |                                           |                      |                     |               |  |  |  |  |

|                  |                                                 | ot complete, SSF                                                                                    | PxBUF is empty                             | /                                         |                      |                     |               |  |  |  |  |

|                  | <u>Transmit (I<sup>2</sup>C)</u>                | mode only):                                                                                         | doos not inclui                            | lo the ACK and C                          | top bits), SSPxBU    | E is full           |               |  |  |  |  |

|                  | $\perp = Data trans$                            | mit in progress (                                                                                   |                                            | the ACK and Stop                          | iop diis), sspxBU    |                     |               |  |  |  |  |

## 18.5 Operation During Sleep

The comparator, if enabled before entering Sleep mode, remains active during Sleep. The additional current consumed by the comparator is shown separately in **Section 27.0** "**Electrical Specifications**". If the comparator is not used to wake the device, power consumption can be minimized while in Sleep mode by turning off the comparator. Each comparator is turned off by clearing the CxON bit of the CMxCON0 register.

A change to the comparator output can wake-up the device from Sleep. To enable the comparator to wake the device from Sleep, the CxIE bit of the PIE2 register and the PEIE/GIEL bit of the INTCON register must be set. The instruction following the SLEEP instruction always executes following a wake from Sleep. If the GIE/GIEH bit of the INTCON register is also set, the device will then execute the Interrupt Service Routine.

## 18.6 Effects of a Reset

A device Reset forces the CMxCON0 and CM2CON1 registers to their Reset states. This forces both comparators and the voltage references to their Off states.Comparator Control Registers.

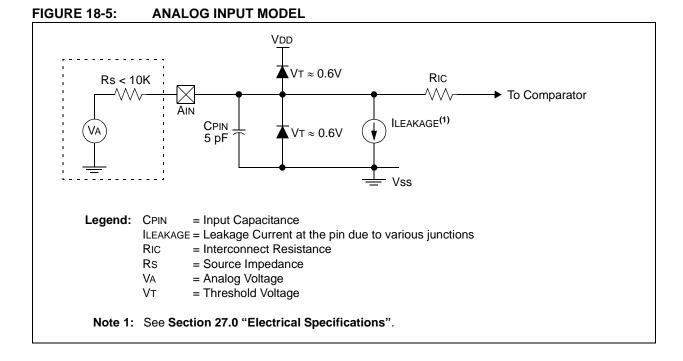

## 18.7 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 18-5. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

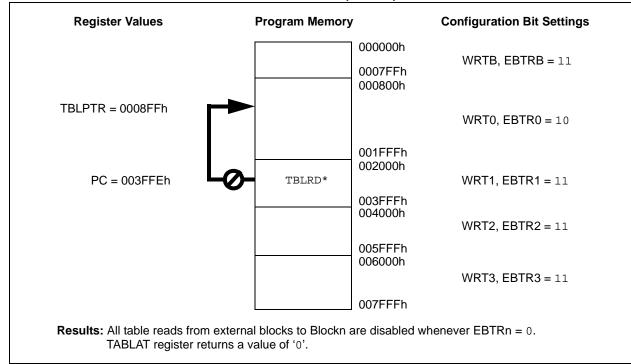

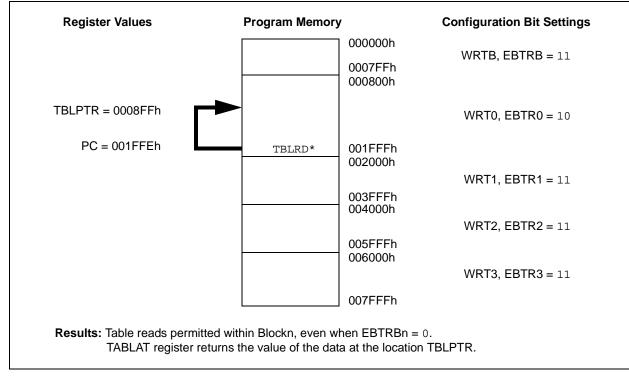

### 24.5.1 PROGRAM MEMORY CODE PROTECTION

The program memory may be read to or written from any location using the table read and table write instructions. The device ID may be read with table reads. The Configuration registers may be read and written with the table read and table write instructions.

In Normal execution mode, the CPn bits have no direct effect. CPn bits inhibit external reads and writes. A block of user memory may be protected from table writes if the WRTn Configuration bit is '0'. The EBTRn bits control table reads. For a block of user memory with the EBTRn bit cleared to '0', a table READ instruction that executes from within that block is allowed to read. A table read instruction that executes from a location outside of that block is not allowed to read and will result in reading '0's. Figures 24-3 through 24-5 illustrate table write and table read protection.

| Note: | Code protection bits may only be written         |  |  |  |  |  |

|-------|--------------------------------------------------|--|--|--|--|--|

|       | to a '0' from a '1' state. It is not possible to |  |  |  |  |  |

|       | write a '1' to a bit in the '0' state. Code pro- |  |  |  |  |  |

|       | tection bits are only set to '1' by a full chip  |  |  |  |  |  |

|       | erase or block erase function. The full chip     |  |  |  |  |  |

|       | erase and block erase functions can only         |  |  |  |  |  |

|       | be initiated via ICSP™ or an external            |  |  |  |  |  |

|       | programmer.                                      |  |  |  |  |  |

## FIGURE 24-3: TABLE WRITE (WRTn) DISALLOWED

| <b>Register Values</b>       | Program Memory                     | Configuration Bit Settings |

|------------------------------|------------------------------------|----------------------------|

|                              | 0000001<br>0007FF<br>0008001       | WRTB, EBTRB = 11<br>h      |

| TBLPTR = 0008FFh             | ▶┍╼▶                               | WRT0, EBTR0 = 01           |

| PC = 001FFEh                 | Твыwт* 001FFF<br>002000            |                            |

|                              | 003FFF<br>0040001                  |                            |

| PC = 005FFEh                 | TBLWT* 005FFF 006000               |                            |

|                              |                                    | WRT3, EBTR3 = 11           |

| Results: All table writes di | abled to Blockn whenever WRTn = 0. | n                          |

### FIGURE 24-4: EXTERNAL BLOCK TABLE READ (EBTRn) DISALLOWED

## FIGURE 24-5: EXTERNAL BLOCK TABLE READ (EBTRn) ALLOWED

| MOVFF                                                                | Move f to f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | MOVLB                           | Move lite                          | Move literal to low nibble in BSR                                                           |                         |                        |                            |  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------|------------------------------------|---------------------------------------------------------------------------------------------|-------------------------|------------------------|----------------------------|--|

| Syntax:                                                              | MOVFF f <sub>s</sub> ,f <sub>d</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |                                 | Syntax:                            | MOVLW                                                                                       | MOVLW k                 |                        |                            |  |

| Operands: $0 \le f_s \le 4095$                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         | Operands:                       | $Operands: \qquad 0 \le k \le 255$ |                                                                                             |                         |                        |                            |  |

|                                                                      | $0 \le f_d \le 4095$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |                                 | Operation:                         | $k \rightarrow BSR$                                                                         |                         |                        |                            |  |

| Operation:                                                           | $(f_s) \rightarrow f_d$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         |                                 | Status Affected:                   | None                                                                                        | None                    |                        |                            |  |

| Status Affected:                                                     | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |                                 | Encoding:                          | 0000                                                                                        | 0001                    | kkkk                   | kkkk                       |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.)<br>Description: | 1100<br>1111<br>The content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ffff ffi<br>ffff ffi<br>ts of source re | ff ffff <sub>d</sub>            | Description:                       | The 8-bit li<br>Bank Sele<br>of BSR<7:<br>regardless                                        | ct Registe<br>4> always | er (BSR).<br>s remains | The value<br>s '0',        |  |

|                                                                      | moved to destination register 'f <sub>d</sub> '.<br>Location of source 'f <sub>s</sub> ' can be anywhere<br>in the 4096-byte data space (000h to<br>FFFh) and location of destination 'f <sub>d</sub> '<br>can also be anywhere from 000h to<br>FFFh.<br>Either source or destination can be W<br>(a useful special situation).<br>MOVFF is particularly useful for<br>transferring a data memory location to a<br>peripheral register (such as the transmit<br>buffer or an I/O port).<br>The MOVFF instruction cannot use the<br>PCL, TOSU, TOSH or TOSL as the<br>destination register. |                                         |                                 | Words:                             | •                                                                                           |                         |                        |                            |  |

|                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         |                                 | Cycles:                            | 1                                                                                           |                         |                        |                            |  |

|                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         |                                 | Q Cycle Activity:                  |                                                                                             |                         |                        |                            |  |

|                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         |                                 | Q1                                 | Q2                                                                                          | Q                       | 3                      | Q4                         |  |

|                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         |                                 | Decode                             | Read<br>literal 'k'                                                                         | Proce<br>Dat            | ess V                  | Vrite literal<br>k' to BSR |  |

|                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         |                                 | BSR R<br>After Instruc             | Example:MOVLB5Before Instruction<br>BSR Register =02hAfter Instruction<br>BSR Register =05h |                         |                        |                            |  |

| Words:                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         |                                 |                                    |                                                                                             |                         |                        |                            |  |

| Cycles:                                                              | 2 (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |                                 |                                    |                                                                                             |                         |                        |                            |  |

| Q Cycle Activity:                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         |                                 |                                    |                                                                                             |                         |                        |                            |  |

| Q1                                                                   | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Q3                                      | Q4                              |                                    |                                                                                             |                         |                        |                            |  |

| Decode                                                               | Read<br>register 'f'<br>(src)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Process<br>Data                         | No<br>operation                 |                                    |                                                                                             |                         |                        |                            |  |

| Decode                                                               | No<br>operation<br>No dummy<br>read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No<br>operation                         | Write<br>register 'f'<br>(dest) |                                    |                                                                                             |                         |                        |                            |  |

| Example:                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REG1, REG2                              |                                 |                                    |                                                                                             |                         |                        |                            |  |

| Before Instruc<br>REG1<br>REG2<br>After Instructio                   | = 33<br>= 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |                                 |                                    |                                                                                             |                         |                        |                            |  |

REG1 REG2 = = 33h 33h

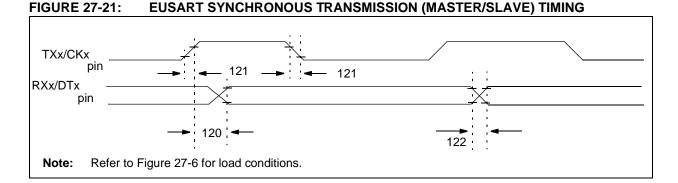

## TABLE 27-19: EUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param.<br>No. | Symbol   | Characteristic                                                        | Min | Max | Units | Conditions |

|---------------|----------|-----------------------------------------------------------------------|-----|-----|-------|------------|

| 120           | TckH2dtV | <u>SYNC XMIT (MASTER &amp; SLAVE)</u><br>Clock High to Data Out Valid | _   | 40  | ns    |            |

| 121           | Tckrf    | Clock Out Rise Time and Fall Time<br>(Master mode)                    | _   | 20  | ns    |            |

| 122           | Tdtrf    | Data Out Rise Time and Fall Time                                      | _   | 20  | ns    |            |

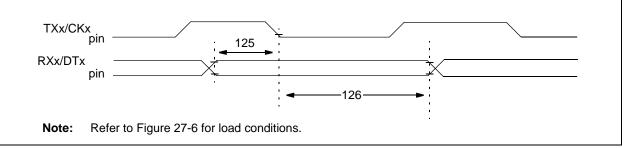

## FIGURE 27-22: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## TABLE 27-20: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param.<br>No. | Symbol   | Characteristic                                                                 | Min | Max | Units | Conditions |

|---------------|----------|--------------------------------------------------------------------------------|-----|-----|-------|------------|

| 125           | TdtV2ckl | SYNC RCV (MASTER & SLAVE)<br>Data Setup before CK $\downarrow$ (DT setup time) | 10  |     | ns    |            |

| 126           | TckL2dtl | Data Hold after CK $\downarrow$ (DT hold time)                                 | 15  | _   | ns    |            |

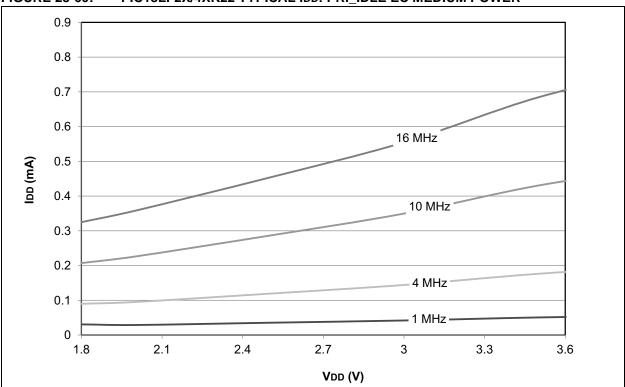

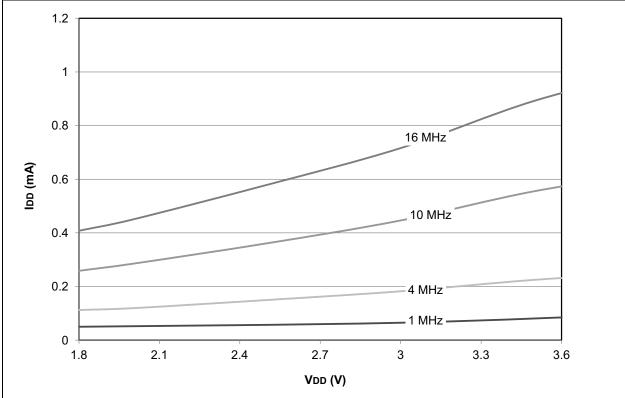

FIGURE 28-60: PIC18LF2X/4XK22 TYPICAL IDD: PRI\_IDLE EC MEDIUM POWER

© 2010-2016 Microchip Technology Inc.

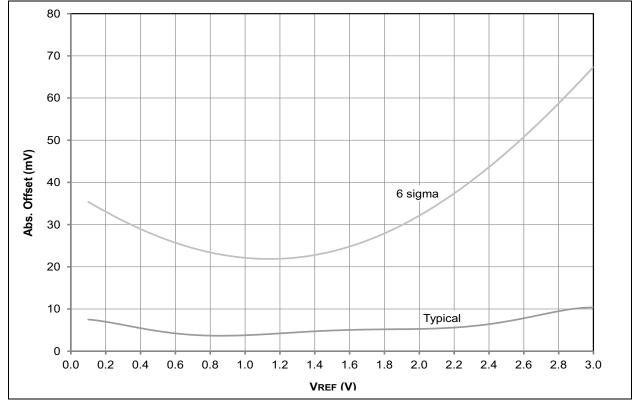

FIGURE 28-91: PIC18(L)F2X/4XK22 COMPARATOR OFFSET VOLTAGE, LOW-POWER MODE; VDD=3.0V

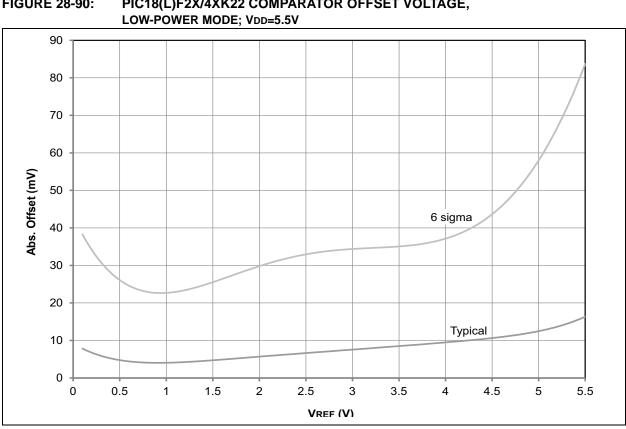

FIGURE 28-90: PIC18(L)F2X/4XK22 COMPARATOR OFFSET VOLTAGE,

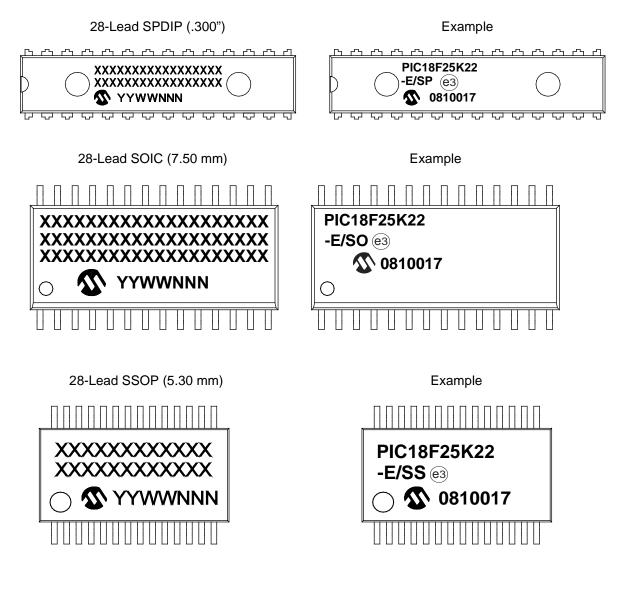

## 29.0 PACKAGING INFORMATION

## 29.1 Package Marking Information

| Legend | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                     | Customer-specific information or Microchip part number<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                                                    |  |