#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I²C, SPI, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 30x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k22t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE I Z. |               |              |          |           |        |                                          |  |

|------------|---------------|--------------|----------|-----------|--------|------------------------------------------|--|

|            | Pin Nu        | ımber        |          | Pin       | Buffer |                                          |  |

|            | PDIP,<br>SOIC | QFN,<br>UQFN | Pin Name | Туре Туре |        | Description                              |  |

|            | 20            | 17           | Vdd      | Р         | _      | Positive supply for logic and I/O pins.  |  |

|            | 8, 19         | 5, 16        | Vss      | Р         | _      | Ground reference for logic and I/O pins. |  |

#### TABLE 1-2: PIC18(L)F2XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

| TABLE 1-3: | PIC18(L)F4XK22 PINOUT I/O DESCRIPTIONS |

|------------|----------------------------------------|

|------------|----------------------------------------|

|      | Pin Number |     | Din Nama | Pin                  | Buffer          | Description |                                        |

|------|------------|-----|----------|----------------------|-----------------|-------------|----------------------------------------|

| PDIP | TQFP       | QFN | UQFN     | Pin Name             | Туре            | Туре        | Description                            |

| 2    | 19         | 19  | 17       | RA0/C12IN0-/AN0      |                 |             |                                        |

|      |            |     |          | RA0                  | I/O             | TTL         | Digital I/O.                           |

|      |            |     |          | C12IN0-              | I               | Analog      | Comparators C1 and C2 inverting input. |

|      |            |     |          | AN0                  | Ι               | Analog      | Analog input 0.                        |

| 3    | 20         | 20  | 18       | RA1/C12IN1-/AN1      |                 |             |                                        |

|      |            |     |          | RA1                  | I/O             | TTL         | Digital I/O.                           |

|      |            |     |          | C12IN1-              | I               | Analog      | Comparators C1 and C2 inverting input. |

|      |            |     |          | AN1                  | I               | Analog      | Analog input 1.                        |

| 4    | 21         | 21  | 19       | RA2/C2IN+/AN2/DACOUT | Wref-           |             |                                        |

|      |            |     |          | RA2                  | I/O             | TTL         | Digital I/O.                           |

|      |            |     |          | C2IN+                | I               | Analog      | Comparator C2 non-inverting input.     |

|      |            |     |          | AN2                  | I               | Analog      | Analog input 2.                        |

|      |            |     |          | DACOUT               | 0               | Analog      | DAC Reference output.                  |

|      |            |     |          | VREF-                | I               | Analog      | A/D reference voltage (low) input.     |

| 5    | 22         | 22  | 20       | RA3/C1IN+/AN3/VREF+  |                 |             |                                        |

|      |            |     |          | RA3                  | I/O             | TTL         | Digital I/O.                           |

|      |            |     |          | C1IN+                | Ι               | Analog      | Comparator C1 non-inverting input.     |

|      |            |     |          | AN3                  | I               | Analog      | Analog input 3.                        |

|      |            |     |          | VREF+                | Ι               | Analog      | A/D reference voltage (high) input.    |

| 6    | 23         | 23  | 21       | RA4/C1OUT/SRQ/T0CKI  |                 |             |                                        |

|      |            |     |          | RA4                  | I/O             | ST          | Digital I/O.                           |

|      |            |     |          | C1OUT                | 0               | CMOS        | Comparator C1 output.                  |

|      |            |     |          | SRQ                  | 0               | TTL         | SR latch Q output.                     |

|      |            |     |          | TOCKI                | l<br>atible inc | ST          | Timer0 external clock input.           |

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

#### 3.6 Selective Peripheral Module Control

Idle mode allows users to substantially reduce power consumption by stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what IDLE mode does not provide: the allocation of power resources to the CPU processing with minimal power consumption from the peripherals. PIC18(L)F2X/4XK22 family devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with control bits in the Peripheral Module Disable (PMD) registers. These bits generically named XXXMD are located in control registers PMD0, PMD1 or PMD2.

Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, power to the control and status registers associated with the peripheral is removed. Writes to these registers have no effect and read values are invalid. Clearing a set PMD bit restores power to the associated control and status registers, thereby setting those registers to their default values.

### 3.7 Register Definitions: Peripheral Module Disable

#### REGISTER 3-1: PMD0: PERIPHERAL MODULE DISABLE REGISTER 0

| R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|---------|--------|--------|--------|--------|--------|--------|

| UART2MD | UART1MD | TMR6MD | TMR5MD | TMR4MD | TMR3MD | TMR2MD | TMR1MD |

| bit 7   | ·       |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7 | UART2MD: UART2 Peripheral Module Disable Control bit                                                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 6 | UART1MD: UART1 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 5 | TMR6MD: Timer6 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 4 | TMR5MD: Timer5 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 3 | TMR4MD: Timer4 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 2 | TMR3MD: Timer3 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 1 | TMR2MD: Timer2 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 0 | TMR1MD: Timer1 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

|       |                                                                                                                                                                                                    |

| U-0           | U-0             | U-0              | U-0            | R/W-0            | R/W-0             | R/W-0             | R/W-0 |

|---------------|-----------------|------------------|----------------|------------------|-------------------|-------------------|-------|

| —             | _               | _                | —              | CTMUMD           | CMP2MD            | CMP1MD            | ADCMD |

| bit 7         |                 |                  |                |                  |                   |                   | bit 0 |

|               |                 |                  |                |                  |                   |                   |       |

| Legend:       |                 |                  |                |                  |                   |                   |       |

| R = Readable  | e bit           | W = Writable     | bit            | U = Unimpler     | mented bit, read  | l as '0'          |       |

| -n = Value at | POR             | '1' = Bit is set |                | '0' = Bit is cle | ared              | x = Bit is unkr   | nown  |

|               |                 |                  |                |                  |                   |                   |       |

| bit 7-4       | Unimplemen      | ted: Read as '   | )'             |                  |                   |                   |       |

| bit 3         | CTMUMD: CT      | MU Periphera     | I Module Disa  | able Control bit |                   |                   |       |

|               | 1 = Module is   | disabled, Clo    | ck Source is o | disconnected, n  | nodule does no    | t draw digital po | ower  |

|               | 0 = Module is   | enabled, Cloo    | k Source is c  | connected, mod   | lule draws digita | al power          |       |

| bit 2         | CMP2MD: Co      | mparator C2 F    | eripheral Mo   | dule Disable Co  | ontrol bit        |                   |       |

|               |                 |                  |                |                  | nodule does no    |                   | ower  |

|               |                 |                  |                |                  | lule draws digita | al power          |       |

| bit 1         | CMP1MD: Co      | mparator C1 F    | eripheral Mo   | dule Disable Co  | ontrol bit        |                   |       |

|               |                 |                  |                |                  | nodule does no    | • .               | ower  |

|               |                 |                  |                |                  | lule draws digita | al power          |       |

| bit 0         |                 | C Peripheral M   |                |                  |                   |                   |       |

|               |                 |                  |                |                  | nodule does no    | • .               | ower  |

|               | 0 = iviodule is |                  | K Source IS C  | connected, mod   | lule draws digita | a power           |       |

#### REGISTER 3-3: PMD2: PERIPHERAL MODULE DISABLE REGISTER 2

| Address | Name                  | Bit 7   | Bit 6         | Bit 5                        | Bit 4            | Bit 3                   | Bit 2                   | Bit 1                        | Bit 0     | <u>Value on</u><br>POR, BOR |

|---------|-----------------------|---------|---------------|------------------------------|------------------|-------------------------|-------------------------|------------------------------|-----------|-----------------------------|

| FD1h    | WDTCON                | _       | —             | —                            | _                | _                       |                         | —                            | SWDTEN    | 0                           |

| FD0h    | RCON                  | IPEN    | SBOREN        | _                            | RI               | TO                      | PD                      | POR                          | BOR       | 01-1 1100                   |

| FCFh    | TMR1H                 |         | Holding R     | egister for the              | Most Significa   | ant Byte of the         | 16-bit TMR1 R           | egister                      | •         | xxxx xxxx                   |

| FCEh    | TMR1L                 |         |               | Least Signif                 | icant Byte of th | ne 16-bit TMR1          | Register                |                              |           | xxxx xxxx                   |

| FCDh    | T1CON                 | TMR1C   | S<1:0>        | T1CKF                        | PS<1:0>          | T1SOSCEN                | T1SYNC                  | T1RD16                       | TMR10N    | 0000 0000                   |

| FCCh    | T1GCON                | TMR1GE  | T1GPOL        | T1GTM                        | T1GSPM           | T <u>1GGO</u> /<br>DONE | T1GVAL                  | T1GS                         | S<1:0>    | 0000 xx00                   |

| FCBh    | SSP1CON3              | ACKTIM  | PCIE          | SCIE                         | BOEN             | SDAHT                   | SBCDE                   | AHEN                         | DHEN      | 0000 0000                   |

| FCAh    | SSP1MSK               |         |               |                              | SSP1 MASK F      | Register bits           |                         |                              |           | 1111 1111                   |

| FC9h    | SSP1BUF               |         |               | SSP1                         | Receive Buffer   | r/Transmit Reg          | ister                   |                              |           | xxxx xxxx                   |

| FC8h    | SSP1ADD               | SSP1    | Address Regis | ster in I <sup>2</sup> C Sla | ve Mode. SSP     | 1 Baud Rate R           | eload Register          | r in I <sup>2</sup> C Master | Mode      | 0000 0000                   |

| FC7h    | SSP1STAT              | SMP     | CKE           | D/A                          | Р                | S                       | R/W                     | UA                           | BF        | 0000 0000                   |

| FC6h    | SSP1CON1              | WCOL    | SSPOV         | SSPEN                        | CKP              |                         | SSPM                    | <3:0>                        |           | 0000 0000                   |

| FC5h    | SSP1CON2              | GCEN    | ACKSTAT       | ACKDT                        | ACKEN            | RCEN                    | PEN                     | RSEN                         | SEN       | 0000 0000                   |

| FC4h    | ADRESH                |         |               |                              | A/D Result,      | High Byte               |                         |                              |           | xxxx xxxx                   |

| FC3h    | ADRESL                |         |               |                              | A/D Result,      | Low Byte                |                         |                              |           | xxxx xxxx                   |

| FC2h    | ADCON0                | _       |               |                              | CHS<4:0>         |                         |                         | GO/DONE                      | ADON      | 00 0000                     |

| FC1h    | ADCON1                | TRIGSEL | _             | _                            | _                | PVCF                    | G<1:0>                  | NVCF                         | G<1:0>    | 0 0000                      |

| FC0h    | ADCON2                | ADFM    | _             |                              | ACQT<2:0>        |                         |                         | ADCS<2:0>                    |           | 0-00 0000                   |

| FBFh    | CCPR1H                |         |               | Captu                        | re/Compare/P\    | VM Register 1,          | High Byte               |                              |           | xxxx xxxx                   |

| FBEh    | CCPR1L                |         |               | Captur                       | e/Compare/PV     | VM Register 1,          | Low Byte                |                              |           | xxxx xxxx                   |

| FBDh    | CCP1CON               | P1M<    | <1:0>         | DC1E                         | 3<1:0>           |                         | CCP1N                   | 1<3:0>                       |           | 0000 0000                   |

| FBCh    | TMR2                  |         |               |                              | Timer2 F         | Register                |                         |                              |           | 0000 0000                   |

| FBBh    | PR2                   |         |               |                              | Timer2 Peri      | od Register             |                         |                              |           | 1111 1111                   |

| FBAh    | T2CON                 | _       |               | T2OUT                        | PS<3:0>          |                         | TMR2ON                  | 'S<1:0>                      | -000 0000 |                             |

| FB9h    | PSTR1CON              | _       | _             | _                            | STR1SYNC         | STR1D                   | STR1C                   | STR1B                        | STR1A     | 0 0001                      |

| FB8h    | BAUDCON1              | ABDOVF  | RCIDL         | DTRXP                        | CKTXP            | BRG16                   | _                       | WUE                          | ABDEN     | 0100 0-00                   |

| FB7h    | PWM1CON               | P1RSEN  |               |                              |                  | P1DC<6:0>               |                         |                              |           | 0000 0000                   |

| FB6h    | ECCP1AS               | CCP1ASE |               | CCP1AS<2:0                   | >                | PSS1A                   | PSS1AC<1:0> PSS1BD<1:0> |                              |           | 0000 0000                   |

| FB4h    | T3GCON                | TMR3GE  | T3GPOL        | T3GTM                        | T3GSPM           | T <u>3GGO</u> /<br>DONE | T3GVAL T3GSS<1:0>       |                              |           | 00x0 0x00                   |

| FB3h    | TMR3H                 |         | Holding R     | egister for the              | Most Significa   | ant Byte of the         | 16-bit TMR3 R           | egister                      |           | xxxx xxxx                   |

| FB2h    | TMR3L                 |         |               | Least Signif                 | icant Byte of th | ne 16-bit TMR3          | Register                |                              |           | xxxx xxxx                   |

| FB1h    | T3CON                 | TMR3C   | S<1:0>        | T3CKF                        | PS<1:0>          | T3SOSCEN                | T3SYNC                  | T3RD16                       | TMR3ON    | 0000 0000                   |

| FB0h    | SPBRGH1               |         |               | EUSAR                        | T1 Baud Rate     | Generator, Hig          | h Byte                  |                              |           | 0000 0000                   |

| FAFh    | SPBRG1                |         |               | EUSAR                        | T1 Baud Rate     | Generator, Lov          | w Byte                  |                              |           | 0000 0000                   |

| FAEh    | RCREG1                |         |               |                              | T1 Receive Re    |                         |                         |                              |           | 0000 0000                   |

| FADh    | TXREG1                |         |               | EUSAR                        | T1 Transmit R    | egister                 |                         |                              |           | 0000 0000                   |

| FACh    | TXSTA1                | CSRC    | TX9           | TXEN                         | SYNC             | SENDB                   | BRGH                    | TRMT                         | TX9D      | 0000 0010                   |

| FABh    | RCSTA1                | SPEN    | RX9           | SREN                         | CREN             | ADDEN                   | FERR                    | OERR                         | RX9D      | 0000 000x                   |

| FAAh    | EEADRH <sup>(5)</sup> | _       | _             | _                            | _                | _                       | _                       |                              | R<9:8>    | 00                          |

| FA9h    | EEADR                 |         |               | 1                            | EEAD             | R<7:0>                  |                         |                              |           | 0000 0000                   |

| FA8h    | EEDATA                |         |               |                              | EEPROM Da        |                         |                         |                              |           | 0000 0000                   |

| FA7h    | EECON2                |         |               | EEPROM Co                    |                  | 2 (not a physic         | cal register)           |                              |           | 00                          |

| FA6h    | EECON1                | EEPGD   | CFGS          | _                            | FREE             | WRERR                   | WREN                    | WR                           | RD        | xx-0 x000                   |

| FA5h    | IPR3                  | SSP2IP  | BCL2IP        | RC2IP                        | TX2IP            | CTMUIP                  | TMR5GIP                 | TMR3GIP                      | TMR1GIP   | 0000 0000                   |

| FA4h    | PIR3                  | SSP2IF  | BCL2IF        | RC2IF                        | TX2IF            | CTMUIF                  | TMR5GIF                 | TMR3GIF                      | TMR1GIF   | 0000 0000                   |

| FA3h    | PIE3                  | SSP2IE  | BCL2IE        | RC2IE                        | TX2IE            | CTMUIE                  | TMR5GIE                 | TMR3GIE                      | TMR1GIE   | 0000 0000                   |

#### **TABLE 5-2:** REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES (CONTINUED)

Legend:  $\mathbf{x}$  = unknown,  $\mathbf{u}$  = unchanged, — = unimplemented,  $\mathbf{q}$  = value depends on condition

PIC18(L)F4XK22 devices only. Note 1:

PIC18(L)F2XK22 devices only. 2:

PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only. PIC18(L)F26K22 and PIC18(L)F46K22 devices only. 3:

4:

DS40001412G-page 80

#### **10.7 Port Analog Control**

Most port pins are multiplexed with analog functions such as the Analog-to-Digital Converter and comparators. When these I/O pins are to be used as analog inputs it is necessary to disable the digital input buffer to avoid excessive current caused by improper biasing of the digital input. Individual control of the digital input buffers on pins which share analog functions is provided by the ANSELA, ANSELB, ANSELC, ANSELD and ANSELE registers. Setting an ANSx bit high will disable the associated digital input buffer and cause all reads of that pin to return '0' while allowing analog functions of that pin to operate correctly.

The state of the ANSx bits has no affect on digital output functions. A pin with the associated TRISx bit clear and ANSx bit set will still operate as a digital output but the input mode will be analog. This can cause unexpected behavior when performing readmodify-write operations on the affected port.

All ANSEL register bits default to '1' upon POR and BOR, disabling digital inputs for their associated port pins. All TRIS register bits default to '1' upon POR or BOR, disabling digital outputs for their associated port pins. As a result, all port pins that have an ANSEL register will default to analog inputs upon POR or BOR.

#### 10.8 Port Slew Rate Control

The output slew rate of each port is programmable to select either the standard transition rate or a reduced transition rate of approximately 0.1 times the standard to minimize EMI. The reduced transition time is the default slew rate for all ports.

| 10.9 | Register | <b>Definitions</b> – | Port Control |

|------|----------|----------------------|--------------|

|------|----------|----------------------|--------------|

### REGISTER 10-1: PORTX<sup>(1)</sup>: PORTX REGISTER

| R/W-u/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

| Rx7     | Rx6     | Rx5     | Rx4     | Rx3     | Rx2     | Rx1     | Rx0     |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Logona.                    |                             |                                    |

|----------------------------|-----------------------------|------------------------------------|

| R = Readable bit           | W = Writable bit            | U = Unimplemented bit, read as '0' |

| '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown                 |

| -n/n = Value at POR and BO | R/Value at all other Resets |                                    |

bit 7-0 Rx<7:0>: PORTx I/O bit values<sup>(2)</sup>

**Note 1:** Register Description for PORTA, PORTB, PORTC and PORTD.

2: Writes to PORTx are written to corresponding LATx register. Reads from PORTx register is return of I/O pin values.

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCLx line, is called clock stretching. Clock stretching give slave devices a mechanism to control the flow of data. When this detection is used on the SDAx line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

#### 15.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCLx clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCLx line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCLx connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

### 15.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDAx data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels don't match, loses arbitration, and must stop transmitting on the SDAx line.

For example, if one transmitter holds the SDAx line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDAx line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDAx line. If this transmitter is also a master device, it also must stop driving the SCLx line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDAx line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

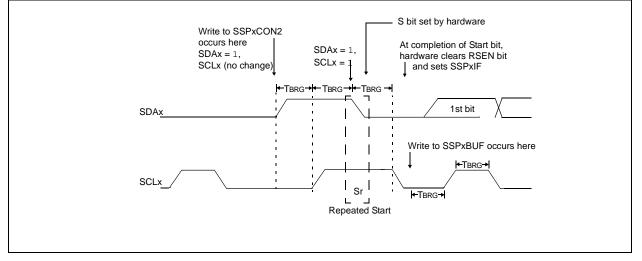

#### 15.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

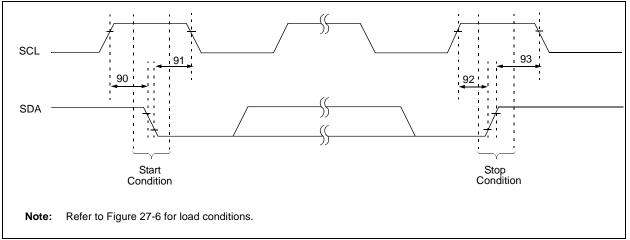

A Repeated Start condition (Figure 15-27) occurs when the RSEN bit of the SSPxCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. SCLx is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

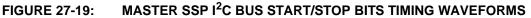

## FIGURE 15-27: REPEAT START CONDITION WAVEFORM

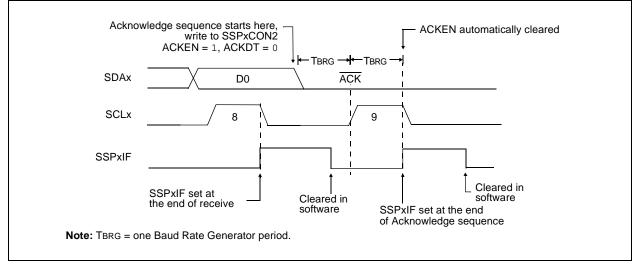

#### 15.6.8 ACKNOWLEDGE SEQUENCE TIMING

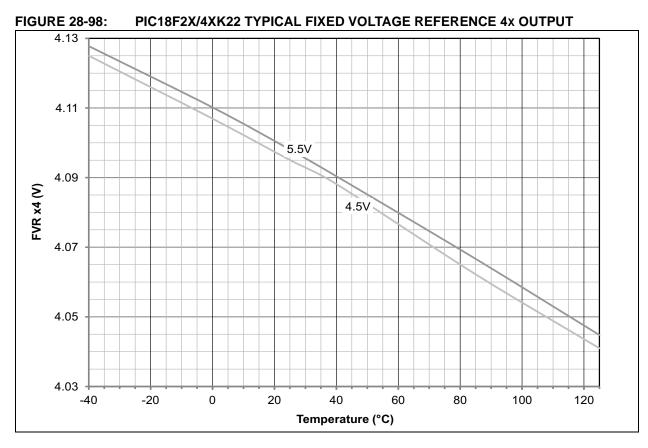

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN, of the SSPxCON2 register. When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSPx module then goes into Idle mode (Figure 15-30).

#### 15.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write does not occur).

#### 15.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN, of the SSPxCON2 register. At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 15-31).

#### 15.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### FIGURE 15-30: ACKNOWLEDGE SEQUENCE WAVEFORM

| Name                  | Bit 7                     | Bit 6     | Bit 5   | Bit 4     | Bit 3        | Bit 2     | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------------|---------------------------|-----------|---------|-----------|--------------|-----------|---------|---------|---------------------|

| BAUDCON1              | ABDOVF                    | RCIDL     | DTRXP   | CKTXP     | BRG16        | —         | WUE     | ABDEN   | 271                 |

| BAUDCON2              | ABDOVF                    | RCIDL     | DTRXP   | CKTXP     | BRG16        | _         | WUE     | ABDEN   | 271                 |

| INTCON                | GIE/GIEH                  | PEIE/GIEL | TMR0IE  | INT0IE    | RBIE         | TMR0IF    | INT0IF  | RBIF    | 109                 |

| IPR1                  | _                         | ADIP      | RC1IP   | TX1IP     | SSP1IP       | CCP1IP    | TMR2IP  | TMR1IP  | 121                 |

| IPR3                  | SSP2IP                    | BCL2IP    | RC2IP   | TX2IP     | CTMUIP       | TMR5GIP   | TMR3GIP | TMR1GIP | 123                 |

| PIE1                  | _                         | ADIE      | RC1IE   | TX1IE     | SSP1IE       | CCP1IE    | TMR2IE  | TMR1IE  | 117                 |

| PIE3                  | SSP2IE                    | BCL2IE    | RC2IE   | TX2IE     | CTMUIE       | TMR5GIE   | TMR3GIE | TMR1GIE | 119                 |

| PIR1                  | _                         | ADIF      | RC1IF   | TX1IF     | SSP1IF       | CCP1IF    | TMR2IF  | TMR1IF  | 112                 |

| PIR3                  | SSP2IF                    | BCL2IF    | RC2IF   | TX2IF     | CTMUIF       | TMR5GIF   | TMR3GIF | TMR1GIF | 114                 |

| PMD0                  | UART2MD                   | UART1MD   | TMR6MD  | TMR5MD    | TMR4MD       | TMR3MD    | TMR2MD  | TMR1MD  | 52                  |

| RCSTA1                | SPEN                      | RX9       | SREN    | CREN      | ADDEN        | FERR      | OERR    | RX9D    | 270                 |

| RCSTA2                | SPEN                      | RX9       | SREN    | CREN      | ADDEN        | FERR      | OERR    | RX9D    | 270                 |

| SPBRG1                |                           |           | EUSART1 | Baud Rate | Generator, L | ow Byte   |         |         | _                   |

| SPBRGH1               |                           |           | EUSART1 | Baud Rate | Generator, H | ligh Byte |         |         | _                   |

| SPBRG2                |                           |           | EUSART2 | Baud Rate | Generator, L | ow Byte   |         |         | _                   |

| SPBRGH2               |                           |           | EUSART2 | Baud Rate | Generator, H | ligh Byte |         |         | _                   |

| TRISB <sup>(2)</sup>  | TRISB7                    | TRISB6    | TRISB5  | TRISB4    | TRISB3       | TRISB2    | TRISB1  | TRISB0  | 151                 |

| TRISC                 | TRISC7                    | TRISC6    | TRISC5  | TRISC4    | TRISC3       | TRISC2    | TRISC1  | TRISC0  | 151                 |

| TRISD <sup>(1)</sup>  | TRISD7                    | TRISD6    | TRISD5  | TRISD4    | TRISD3       | TRISD2    | TRISD1  | TRISD0  | 151                 |

| ANSELC                | ANSC7                     | ANSC6     | ANSC5   | ANSC4     | ANSC3        | ANSC2     | _       | —       | 150                 |

| ANSELD <sup>(1)</sup> | ANSD7                     | ANSD6     | ANSD5   | ANSD4     | ANSD3        | ANSD2     | ANSD1   | ANSD0   | 150                 |

| TXREG1                | EUSART1 Transmit Register |           |         |           |              |           |         |         |                     |

| TXSTA1                | CSRC                      | TX9       | TXEN    | SYNC      | SENDB        | BRGH      | TRMT    | TX9D    | 269                 |

| TXREG2                | EUSART2 Transmit Register |           |         |           |              |           |         |         | —                   |

| TXSTA2                | CSRC                      | TX9       | TXEN    | SYNC      | SENDB        | BRGH      | TRMT    | TX9D    | 269                 |

### TABLE 16-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for synchronous master transmission.

Note 1: PIC18(L)F4XK22 devices.

2: PIC18(L)F2XK22 devices.

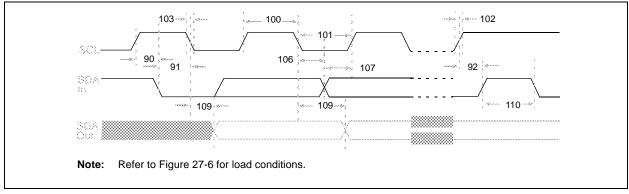

### 21.3 Register Definitions: FVR Control

| REGISTER       | <u> 21-1: VREF</u>                                                     | CON0: FIXED                                                                                 |                                                                 | REFERENC                                                               | E CONTROL F      | REGISTER         |              |

|----------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------|------------------|------------------|--------------|

| R/W-0          | R/W-0                                                                  | R/W-0                                                                                       | R/W-1                                                           | U-0                                                                    | U-0              | U-0              | U-0          |

| FVREN          | FVRST                                                                  | FVRS                                                                                        | 6<1:0>                                                          | —                                                                      | —                | —                | —            |

| bit 7          |                                                                        | ·                                                                                           |                                                                 | -                                                                      |                  |                  | bit          |

| Legend:        |                                                                        |                                                                                             |                                                                 |                                                                        |                  |                  |              |

| R = Readat     | ole bit                                                                | W = Writable                                                                                | bit                                                             | U = Unimplei                                                           | mented bit, read | as '0'           |              |

| u = Bit is ur  | nchanged                                                               | x = Bit is unk                                                                              | nown                                                            | -n/n = Value                                                           | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is s | et                                                                     | '0' = Bit is cle                                                                            | ared                                                            |                                                                        |                  |                  |              |

| bit 6          | 0 = Fixed V                                                            | ed Voltage Refe<br>oltage Referenc<br>oltage Referenc                                       | e output is no                                                  | ot ready or not e                                                      | enabled          |                  |              |

| bit 5-4        | <b>FVRS&lt;1:0&gt;</b><br>00 = Fixed \<br>01 = Fixed \<br>10 = Fixed \ | : Fixed Voltage<br>/oltage Referen<br>/oltage Referen<br>/oltage Referen<br>/oltage Referen | Reference Se<br>ce Peripheral<br>ce Peripheral<br>ce Peripheral | election bits<br>output is off<br>output is 1x (1,<br>output is 2x (2, | .048V)(1)        |                  |              |

| bit 3-2        |                                                                        | Read as '0'. Mai                                                                            | •                                                               | •                                                                      |                  |                  |              |

| bit 1-0        | Unimpleme                                                              | nted: Read as '                                                                             | 0'.                                                             |                                                                        |                  |                  |              |

| Note 1.        | Fixed Voltage B                                                        |                                                                                             |                                                                 |                                                                        |                  |                  |              |

#### REGISTER 21-1: VREFCON0: FIXED VOLTAGE REFERENCE CONTROL REGISTER

Note 1: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name     | Bit 7 | Bit 6 | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|----------|-------|-------|-----------|-------|-------|-------|-------|-------|---------------------|

| VREFCON0 | FVREN | FVRST | FVRS<1:0> |       | _     |       |       |       | 332                 |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by the FVR module.

#### 23.7 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

#### 23.8 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| HLVDCON | VDIRMAG  | BGVST     | IRVST  | HLVDEN |        | HLVDI  | _<3:0> |        | 337                        |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 109                        |

| IPR2    | OSCFIP   | C1IP      | C2IP   | EEIP   | BCL1IP | HLVDIP | TMR3IP | CCP2IP | 122                        |

| PIE2    | OSCFIE   | C1IE      | C2IE   | EEIE   | BCL1IE | HLVDIE | TMR3IE | CCP2IE | 118                        |

| PIR2    | OSCFIF   | C1IF      | C2IF   | EEIF   | BCL1IF | HLVDIF | TMR3IF | CCP2IF | 113                        |

| TRISA   | TRISA7   | TRISA6    | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 151                        |

#### TABLE 23-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are unused by the HLVD module.

CNT Z C DC

After Instruction

CNT Z C DC

FFh 0 ? ?

00h

= = = =

= = = 1 1 1

| GOTO                                   | Uncondit                                                                                                                                                                            | ional Bran      | ch          |                                                                                                    | INCF                                       | Incremen                                                              | t f                                                                                   |                                                             |                                                                                                                         |                                                              |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|----------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Syntax:                                | GOTO k                                                                                                                                                                              |                 |             |                                                                                                    | Syntax:                                    | INCF f{,c                                                             | INCF f {,d {,a}}                                                                      |                                                             |                                                                                                                         |                                                              |

| Operands:                              | $0 \le k \le 104$                                                                                                                                                                   | 8575            |             |                                                                                                    | Operands:                                  | $0 \leq f \leq 255$                                                   |                                                                                       |                                                             |                                                                                                                         |                                                              |

| Operation:                             | $k \rightarrow PC < 20$                                                                                                                                                             | ):1>            |             |                                                                                                    |                                            | d ∈ [0,1]<br>a ∈ [0,1]                                                |                                                                                       |                                                             |                                                                                                                         |                                                              |

| Status Affected:                       | None                                                                                                                                                                                | None            |             | Operation:                                                                                         | $a \in [0, 1]$<br>(f) + 1 $\rightarrow$ de | act                                                                   |                                                                                       |                                                             |                                                                                                                         |                                                              |

| Encoding:                              |                                                                                                                                                                                     |                 |             |                                                                                                    | Status Affected:                           | $(1) \neq 1 \rightarrow 0$<br>C, DC, N,                               |                                                                                       |                                                             |                                                                                                                         |                                                              |

| 1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110<br>1111                                                                                                                                                                        |                 | 7kkk<br>kkk | kkkk <sub>0</sub><br>kkkk <sub>8</sub>                                                             | Encoding:                                  | 0010                                                                  | 10da ff                                                                               | ff ffff                                                     |                                                                                                                         |                                                              |

| Description:                           | GOTO allows an unconditional branch<br>anywhere within entire<br>2-Mbyte memory range. The 20-bit<br>value 'k' is loaded into PC<20:1>.<br>GOTO is always a 2-cycle<br>instruction. |                 |             | 2-Mbyte memory range. The 20-bit<br>value 'k' is loaded into PC<20:1>.<br>GOTO is always a 2-cycle |                                            |                                                                       | Description:                                                                          | incremente<br>placed in W<br>placed bac<br>If 'a' is '0', t | ts of register 'f<br>d. If 'd' is '0', t<br>V. If 'd' is '1', th<br>k in register 'f'<br>the Access Ba<br>he BSR is use | he result is<br>ne result is<br>(default).<br>nk is selected |

| Words:                                 | 2                                                                                                                                                                                   |                 |             |                                                                                                    |                                            | GPR bank.                                                             |                                                                                       |                                                             |                                                                                                                         |                                                              |

| Cycles:                                | 2                                                                                                                                                                                   |                 |             |                                                                                                    |                                            |                                                                       | If 'a' is '0' and the extended instructio<br>set is enabled, this instruction operate |                                                             |                                                                                                                         |                                                              |

| Q Cycle Activity:                      |                                                                                                                                                                                     |                 |             |                                                                                                    |                                            | in Indexed Literal Offset Addressing                                  |                                                                                       |                                                             |                                                                                                                         |                                                              |

| Q1                                     | Q2                                                                                                                                                                                  | Q3              |             | Q4                                                                                                 |                                            | mode whenever $f \le 95$ (5Fh). See Section 25.2.3 "Byte-Oriented and |                                                                                       |                                                             |                                                                                                                         |                                                              |

| Decode                                 | Read literal<br>'k'<7:0>,                                                                                                                                                           | No<br>operation | 'k'         | ad literal<br>2<19:8>,<br>rite to PC                                                               |                                            | Bit-Oriente                                                           | ed Instruction<br>set Mode" for                                                       | s in Indexed                                                |                                                                                                                         |                                                              |

| No                                     | No                                                                                                                                                                                  | No              |             | No                                                                                                 | Words:                                     | 1                                                                     |                                                                                       |                                                             |                                                                                                                         |                                                              |

| operation                              | operation                                                                                                                                                                           | operation       | op          | peration                                                                                           | Cycles:                                    | 1                                                                     |                                                                                       |                                                             |                                                                                                                         |                                                              |

|                                        |                                                                                                                                                                                     |                 |             |                                                                                                    | Q Cycle Activity:                          |                                                                       |                                                                                       |                                                             |                                                                                                                         |                                                              |

| Example:                               | GOTO THE                                                                                                                                                                            | RE              |             |                                                                                                    | Q1                                         | Q2                                                                    | Q3                                                                                    | Q4                                                          |                                                                                                                         |                                                              |

| After Instruction<br>PC =              | on<br>Address (T                                                                                                                                                                    | HERE)           |             |                                                                                                    | Decode                                     | Read<br>register 'f'                                                  | Process<br>Data                                                                       | Write to destination                                        |                                                                                                                         |                                                              |

|                                        |                                                                                                                                                                                     |                 |             |                                                                                                    | Example:                                   | INCF                                                                  | CNT, 1, 0                                                                             |                                                             |                                                                                                                         |                                                              |

|                                        |                                                                                                                                                                                     |                 |             | Before Instruc                                                                                     | ction                                      |                                                                       |                                                                                       |                                                             |                                                                                                                         |                                                              |

| SUBWFB                                 | Su                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | btract                                        | W from f wit           | h Borrow    |  |  |  |  |  |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------|-------------|--|--|--|--|--|

| Syntax:                                | SU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IBWFB                                         | f {,d {,a}}            |             |  |  |  |  |  |

| Operands:                              | 0 ≤                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f ≤ 255                                       |                        |             |  |  |  |  |  |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | d ∈ [0,1]                                     |                        |             |  |  |  |  |  |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | a ∈ [0,1]                                     |                        |             |  |  |  |  |  |

| Operation:                             | (f) ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $(f) - (W) - (\overline{C}) \rightarrow dest$ |                        |             |  |  |  |  |  |

| Status Affected:                       | N,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | N, OV, C, DC, Z                               |                        |             |  |  |  |  |  |

| Encoding:                              | (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0101                                          | 10da fff               | f fff       |  |  |  |  |  |

| Description:<br>Words:                 | Subtract W and the CARRY flag<br>(borrow) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f' (default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                               |                        |             |  |  |  |  |  |

|                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |                        |             |  |  |  |  |  |

| Cycles:                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |                        |             |  |  |  |  |  |

| Q Cycle Activity:<br>Q1                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Q2                                            | Q3                     | Q4          |  |  |  |  |  |