Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 30x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46k22-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.9 Effects of Power-Managed Modes on the Various Clock Sources

For more information about the modes discussed in this section see **Section 3.0** "**Power-Managed Modes**". A quick reference list is also available in Table 3-1.

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin, if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the secondary oscillator (SOSC) is operating and providing the device clock. The secondary oscillator may also run in all power-managed modes if required to clock Timer1, Timer3 or Timer5.

In internal oscillator modes (INTOSC\_RUN and INTOSC\_IDLE), the internal oscillator block provides the device clock source. The 31.25 kHz LFINTOSC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the power-managed mode (see Section 24.3 "Watchdog Timer (WDT)", Section 2.12 "Two-Speed Clock Start-up Mode" and Section 2.13 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up). The HFINTOSC and MFINTOSC outputs may be used directly to clock the device or may be divided down by the postscaler. The HFINTOSC and MFINTOSC outputs are disabled when the clock is provided directly from the LFINTOSC output.

When the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The LFINTOSC is required to support WDT operation. Other features may be operating that do not require a device clock source (i.e., SSP slave, PSP, INTn pins and others). Peripherals that may add significant current consumption are listed in Section 27.8 "DC Characteristics: Input/Output Characteristics, PIC18(L)F2X/4XK22".

# 2.10 Power-up Delays

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 4.6** "**Device Reset Timers**".

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up. It is enabled by clearing (= 0) the PWRTEN Configuration bit.

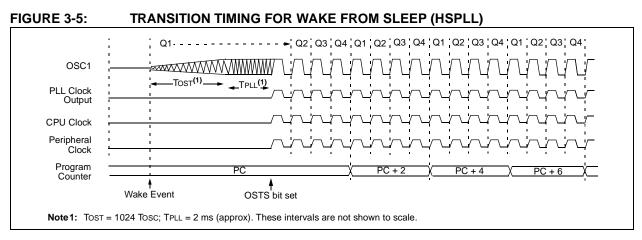

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the PLL is enabled with external oscillator modes, the device is kept in Reset for an additional 2 ms, following the OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of interval TCSD, following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIOSC modes are used as the primary clock source.

When the HFINTOSC is selected as the primary clock, the main system clock can be delayed until the HFINTOSC is stable. This is user selectable by the HFOFST bit of the CONFIG3H Configuration register. When the HFOFST bit is cleared, the main system clock is delayed until the HFINTOSC is stable. When the HFOFST bit is set, the main system clock starts immediately.

In either case, the HFIOFS bit of the OSCCON register can be read to determine whether the HFINTOSC is operating and stable.

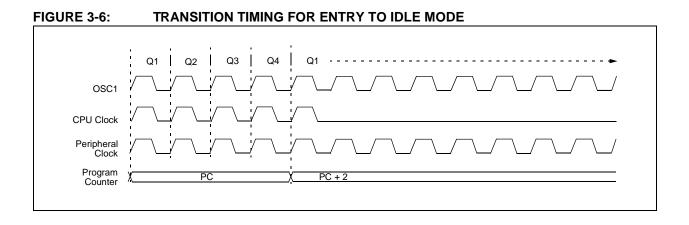

### 3.4.1 PRI\_IDLE MODE

This mode is unique among the three low-power Idle modes, in that it does not disable the primary device clock. For timing sensitive applications, this allows for the fastest resumption of device operation with its more accurate primary clock source, since the clock source does not have to "warm-up" or transition from another oscillator.

PRI\_IDLE mode is entered from PRI\_RUN mode by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set IDLEN first, then clear the SCS bits and execute SLEEP. Although the CPU is disabled, the peripherals continue to be clocked from the primary clock source specified by the FOSC<3:0> Configuration bits. The OSTS bit remains set (see Figure 3-6).

When a wake event occurs, the CPU is clocked from the primary clock source. A delay of interval TCSD is required between the wake event and when code execution starts. This is required to allow the CPU to become ready to execute instructions. After the wake-up, the OSTS bit remains set. The IDLEN and SCS bits are not affected by the wake-up (see Figure 3-7).

# 3.4.2 SEC\_IDLE MODE

In SEC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the SOSC oscillator. This mode is entered from SEC\_RUN by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set the IDLEN bit first, then set the SCS<1:0> bits to '01' and execute SLEEP. When the clock source is switched to the SOSC oscillator, the primary oscillator is shut down, the OSTS bit is cleared and the SOSCRUN bit is set.

When a wake event occurs, the peripherals continue to be clocked from the SOSC oscillator. After an interval of TCSD following the wake event, the CPU begins executing code being clocked by the SOSC oscillator. The IDLEN and SCS bits are not affected by the wake-up; the SOSC oscillator continues to run (see Figure 3-7).

Note: The SOSC oscillator should already be running prior to entering SEC\_IDLE mode. At least one of the secondary oscillator enable bits (SOSCGO, T1SOSCEN, T3SOSCEN or T5SOSCEN) must be set when the SLEEP instruction is executed. Otherwise, the main system clock will continue to operate in the previously selected mode and the corresponding IDLE mode will be entered (i.e., PRI\_IDLE or RC\_IDLE).

|                                         |              |                  |          |                  | · ·              |                 |        |  |  |  |

|-----------------------------------------|--------------|------------------|----------|------------------|------------------|-----------------|--------|--|--|--|

| U-0                                     | U-0          | U-0              | U-0      | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |

|                                         | —            | —                | —        | —                | CCP5IE           | CCP4IE          | CCP3IE |  |  |  |

| bit 7 bit 0                             |              |                  |          |                  |                  |                 |        |  |  |  |

|                                         |              |                  |          |                  |                  |                 |        |  |  |  |

| Legend:                                 |              |                  |          |                  |                  |                 |        |  |  |  |

| R = Readable                            | bit          | W = Writable     | bit      | U = Unimpler     | mented bit, read | as '0'          |        |  |  |  |

| -n = Value at I                         | POR          | '1' = Bit is set |          | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |  |  |

|                                         |              |                  |          |                  |                  |                 |        |  |  |  |

| bit 7-3                                 | Unimplemen   | ted: Read as '   | 0'       |                  |                  |                 |        |  |  |  |

| bit 2                                   | CCP5IE: CCF  | P5 Interrupt En  | able bit |                  |                  |                 |        |  |  |  |

|                                         | 1 = Enabled  |                  |          |                  |                  |                 |        |  |  |  |

|                                         | 0 = Disabled |                  |          |                  |                  |                 |        |  |  |  |

| bit 1                                   | CCP4IE: CCF  | P4 Interrupt En  | able bit |                  |                  |                 |        |  |  |  |

|                                         | 1 = Enabled  |                  |          |                  |                  |                 |        |  |  |  |

|                                         | 0 = Disabled |                  |          |                  |                  |                 |        |  |  |  |

| bit 0 CCP3IE: CCP3 Interrupt Enable bit |              |                  |          |                  |                  |                 |        |  |  |  |

|                                         | 1 = Enabled  |                  |          |                  |                  |                 |        |  |  |  |

|                                         | 0 = Disabled |                  |          |                  |                  |                 |        |  |  |  |

|                                         |              |                  |          |                  |                  |                 |        |  |  |  |

|                                         |              |                  |          |                  |                  |                 |        |  |  |  |

### REGISTER 9-12: PIE4: PERIPHERAL INTERRUPT ENABLE (FLAG) REGISTER 4

# REGISTER 9-13: PIE5: PERIPHERAL INTERRUPT ENABLE (FLAG) REGISTER 5

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| —     | —   | —   | —   | —   | TMR6IE | TMR5IE | TMR4IE |

| bit 7 |     |     |     |     |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-3 | Unimplemented: Read as '0'                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| bit 2   | TMR6IE: TMR6 to PR6 Match Interrupt Enable bit                                                                        |

|         | <ul> <li>1 = Enables the TMR6 to PR6 match interrupt</li> <li>0 = Disables the TMR6 to PR6 match interrupt</li> </ul> |

| bit 1   | TMR5IE: TMR5 Overflow Interrupt Enable bit                                                                            |

|         | <ul><li>1 = Enables the TMR5 overflow interrupt</li><li>0 = Disables the TMR5 overflow interrupt</li></ul>            |

| bit 0   | TMR4IE: TMR4 to PR4 Match Interrupt Enable bit                                                                        |

|         | <ul> <li>1 = Enables the TMR4 to PR4 match interrupt</li> <li>0 = Disables the TMR4 to PR4 match interrupt</li> </ul> |

### 10.1.1 PORTA OUTPUT PRIORITY

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the higher priority. Table 10-4 lists the PORTA pin functions from the highest to the lowest priority.

Analog input functions, such as ADC and comparator, are not shown in the priority lists.

These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below.

| D I. M   |                     | Port Fun            | ction Priority by P | ort Pin              |                      |  |

|----------|---------------------|---------------------|---------------------|----------------------|----------------------|--|

| Port bit | PORTA               | PORTB               | PORTC               | PORTD <sup>(2)</sup> | PORTE <sup>(2)</sup> |  |

| 0        | RA0                 | CCP4 <sup>(1)</sup> | SOSCO               | SCL2                 | CCP3 <sup>(8)</sup>  |  |

|          |                     | RB0                 | P2B <sup>(6)</sup>  | SCK2                 | P3A <sup>(8)</sup>   |  |

|          |                     |                     | RC0                 | RD0                  | RE0                  |  |

| 1        | RA1                 | SCL2 <sup>(1)</sup> | SOSCI               | SDA2                 | P3B                  |  |

|          |                     | SCK2 <sup>(1)</sup> | CCP2 <sup>(3)</sup> | CCP4                 | RE1                  |  |

|          |                     | P1C <sup>(1)</sup>  | P2A <sup>(3)</sup>  | RD1                  |                      |  |

|          |                     | RB1                 | RC1                 |                      |                      |  |

| 2        | RA2                 | SDA2 <sup>(1)</sup> | CCP1                | P2B                  | CCP5                 |  |

|          |                     | P1B <sup>(1)</sup>  | P1A                 | RD2 <sup>(4)</sup>   | RE2                  |  |

|          |                     | RB2                 | CTPLS               |                      |                      |  |

|          |                     |                     | RC2                 |                      |                      |  |

| 3        | RA3                 | SDO2 <sup>(1)</sup> | SCL1                | P2C                  | MCLR                 |  |

|          |                     | CCP2 <sup>(6)</sup> | SCK1                | RD3                  | Vpp                  |  |

|          |                     | P2A <sup>(6)</sup>  | RC3                 |                      | RE3                  |  |

|          |                     | RB3                 |                     |                      |                      |  |

| 4        | SRQ                 | P1D <sup>(1)</sup>  | SDA1                | SDO2                 |                      |  |

|          | C1OUT               | RB4                 | RC4                 | P2D                  |                      |  |

|          | CCP5 <sup>(1)</sup> |                     |                     | RD4                  |                      |  |

|          | RA4                 |                     |                     |                      |                      |  |

### TABLE 10-4: PORT PIN FUNCTION PRIORITY

Note 1: PIC18(L)F2XK22 devices.

2: PIC18(L)F4XK22 devices.

- **3:** Function default pin.

- **4:** Function default pin (28-pin devices).

- **5:** Function default pin (40/44-pin devices).

- **6:** Function alternate pin.

- 7: Function alternate pin (28-pin devices).

- 8: Function alternate pin (40/44-pin devices)

| <b>D</b> . (1)( |       | Port Fun               | ction Priority by P    | ort Pin              |                      |

|-----------------|-------|------------------------|------------------------|----------------------|----------------------|

| Port bit        | PORTA | PORTB                  | PORTC                  | PORTD <sup>(2)</sup> | PORTE <sup>(2)</sup> |

| 5               | SRNQ  | CCP3 <sup>(3)</sup>    | SDO1                   | P1B                  |                      |

|                 | C2OUT | P3A <sup>(3)</sup>     | RC5                    | RD5                  |                      |

|                 | RA5   | P2B <sup>(1)(4)</sup>  |                        |                      |                      |

|                 |       | RB5                    |                        |                      |                      |

| 6               | OSC2  | PGC                    | TX1/CK1                | TX2/CK2              |                      |

|                 | CLKO  | TX2/CK2 <sup>(1)</sup> | CCP3 <sup>(1)(7)</sup> | P1C                  |                      |

|                 | RA6   | RB6                    | P3A <sup>(1)(7)</sup>  | RD6                  |                      |

|                 |       | ICDCK                  | RC6                    |                      |                      |

| 7               | RA7   |                        |                        |                      |                      |

|                 | OSC1  | PGD                    | RX1/DT1                | RX2/DT2              |                      |

|                 | RA7   | RX2/DT2 <sup>(1)</sup> | P3B <sup>(1)</sup>     | P1D                  |                      |

|                 |       | RB7                    | RC7                    | RD7                  |                      |

|                 |       | ICDDT                  |                        |                      |                      |

### TABLE 10-4: PORT PIN FUNCTION PRIORITY (CONTINUED)

Note 1: PIC18(L)F2XK22 devices.

2: PIC18(L)F4XK22 devices.

3: Function default pin.

4: Function default pin (28-pin devices).

5: Function default pin (40/44-pin devices).

6: Function alternate pin.

7: Function alternate pin (28-pin devices).

8: Function alternate pin (40/44-pin devices)

| R/W-0/u                                                            | R/W-0/u                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0/u                                                                   | R/W-0/u                          | R/W/HC-0/u                                                                         | R-x/x           | R/W-0/u          | R/W-0/u    |  |  |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------|-----------------|------------------|------------|--|--|

| TMRxGE                                                             | TxGPOL                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TxGTM                                                                     | TxGSPM                           | TxGGO/DONE                                                                         | TxGVAL          | TxGSS            | S<1:0>     |  |  |

| bit 7                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |                                  |                                                                                    |                 |                  | bit 0      |  |  |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |                                  |                                                                                    |                 |                  |            |  |  |

| Legend:                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |                                  |                                                                                    |                 |                  |            |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |                                  |                                                                                    |                 |                  |            |  |  |

| u = Bit is unch                                                    | nanged                                                                                                                                                                                                                                                                                                                                                                                                                                                             | x = Bit is unkr                                                           | nown                             | -n/n = Value at P                                                                  | OR and BOR      | /Value at all ot | her Resets |  |  |

| '1' = Bit is set                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '0' = Bit is clea                                                         | ared                             | HC = Bit is clear                                                                  | ed by hardwa    | re               |            |  |  |

| bit 7                                                              | If TMRxON =<br>This bit is ign<br>If TMRxON =<br>1 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                                                      | <br>ored<br><u>1</u> :<br>/5 counting is c                                | controlled by th                 | ne Timer1/3/5 gate<br>r1/3/5 gate function                                         |                 |                  |            |  |  |

| bit 6                                                              | 1 = Timer1/3<br>0 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                                                                                       | /5 gate is activ                                                          | e-high (Timer1<br>e-low (Timer1/ | /3/5 counts when<br>3/5 counts when g                                              |                 |                  |            |  |  |

| bit 5                                                              | 1 = Timer1/3<br>0 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                                                                                       | er1/3/5 Gate To<br>/5 Gate Toggle<br>/5 Gate Toggle<br>ate flip-flop togg | mode is enab                     | led<br>bled and toggle flip                                                        | -flop is cleare | d                |            |  |  |

| bit 4                                                              | 1 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ner1/3/5 Gate \$<br>/5 gate Single-<br>/5 gate Single-                    | Pulse mode is                    | enabled and is co                                                                  | ontrolling Time | r1/3/5 gate      |            |  |  |

| bit 3                                                              | 1 = Timer1/3<br>0 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                                                                                       | /5 gate single- <sub> </sub><br>/5 gate single- <sub> </sub>              | oulse acquisition                | ulse Acquisition St<br>on is ready, waiting<br>on has completed<br>SPM is cleared. | g for an edge   | en started       |            |  |  |

| bit 2                                                              | This bit is automatically cleared when TxGSPM is cleared.<br><b>TxGVAL:</b> Timer1/3/5 Gate Current State bit<br>Indicates the current state of the Timer1/3/5 gate that could be provided to TMRxH:TMRxL.<br>Unaffected by Timer1/3/5 Gate Enable (TMRxGE)                                                                                                                                                                                                        |                                                                           |                                  |                                                                                    |                 |                  |            |  |  |

| bit 1-0                                                            | Indicates the current state of the Timer1/3/5 gate that could be provided to TMRxH:TMRxL.<br>Unaffected by Timer1/3/5 Gate Enable (TMRxGE).<br><b>TxGSS&lt;1:0&gt;:</b> Timer1/3/5 Gate Source Select bits<br>00 = Timer1/3/5 Gate pin<br>01 = Timer2/4/6 Match PR2/4/6 output (See Table 12-5 for proper timer match selection)<br>10 = Comparator 1 optionally synchronized output (sync_C1OUT)<br>11 = Comparator 2 optionally synchronized output (sync_C2OUT) |                                                                           |                                  |                                                                                    |                 |                  |            |  |  |

### REGISTER 12-2: TXGCON: TIMER1/3/5 GATE CONTROL REGISTER

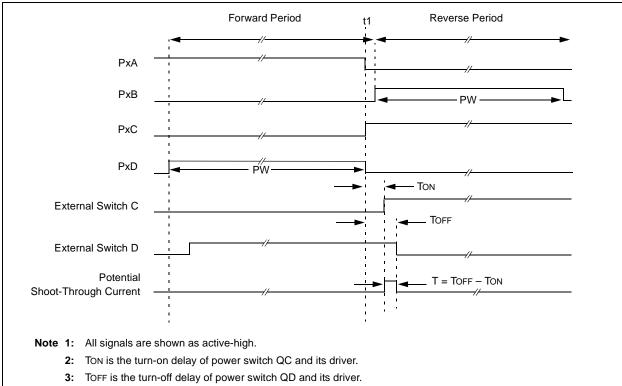

### 14.4.3 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the CCPxAS<2:0> bits of the ECCPxAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- Comparator Cx (async\_CxOUT)

- Setting the CCPxASE bit in firmware

A shutdown condition is indicated by the CCPxASE (Auto-Shutdown Event Status) bit of the ECCPxAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The CCPxASE bit is set to '1'. The CCPxASE will remain set until cleared in firmware or an auto-restart occurs (see Section 14.4.4 "Auto-Restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [PxA/PxC] and [PxB/PxD].

The state of each pin pair is determined by the PSSxAC<1:0> and PSSxBD<1:0> bits of the ECCPxAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

Note 1: The auto-shutdown condition is a levelbased signal, not an edge-based signal. As long as the level is present, the autoshutdown will persist.

- 2: Writing to the CCPxASE bit is disabled while an auto-shutdown condition persists.

- 3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

| R/C/HS-0         | R/C/HS-0                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                              | R/W-0                                                                                      | R/W-0                                                                                           | R/W-0                                                       | R/W-0                                                             | R/W-0                                  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------|

| WCOL             | SSPxOV                                                                                                                                                                                                                                                               | SSPxEN                                                                                                                                             | CKP                                                                                        |                                                                                                 | SSPx                                                        | M<3:0>                                                            |                                        |

| bit 7            |                                                                                                                                                                                                                                                                      |                                                                                                                                                    |                                                                                            |                                                                                                 |                                                             |                                                                   | bit (                                  |

|                  |                                                                                                                                                                                                                                                                      |                                                                                                                                                    |                                                                                            |                                                                                                 |                                                             |                                                                   |                                        |

| Legend:          |                                                                                                                                                                                                                                                                      |                                                                                                                                                    |                                                                                            |                                                                                                 |                                                             |                                                                   |                                        |

| R = Readable b   | oit                                                                                                                                                                                                                                                                  | W = Writable b                                                                                                                                     | it                                                                                         | U = Unimpleme                                                                                   | ented bit, read as                                          | s 'O'                                                             |                                        |

| u = Bit is uncha | nged                                                                                                                                                                                                                                                                 | x = Bit is unkno                                                                                                                                   | own                                                                                        | -n/n = Value at                                                                                 | POR and BOR/\                                               | /alue at all other F                                              | Resets                                 |

| '1' = Bit is set |                                                                                                                                                                                                                                                                      | '0' = Bit is clea                                                                                                                                  | red                                                                                        | HS = Bit is set                                                                                 | by hardware                                                 | C = User cleare                                                   | d                                      |

| bit 7            | Master mode<br>1 = A write t<br>be starte<br>0 = No collis<br><u>Slave mode</u> :                                                                                                                                                                                    | o the SSPxBUF re<br>ed<br>sion<br>PxBUF register is w                                                                                              | egister was atte                                                                           |                                                                                                 |                                                             |                                                                   |                                        |

| bit 6            | $\begin{array}{rcl} & \underline{\text{In SPI mode:}} \\ 1 &= & A \text{ new by} \\ & & \text{in SSPx} \\ & & \text{if only tra} \\ & & \text{tion (and 0 = No over} \\ \hline & & \underline{\text{In I}^2 \text{C mode:}} \\ 1 &= & A \text{ byte is} \end{array}$ | yte is received whil<br>SR is lost. Overflow<br>ansmitting data, to a<br>I transmission) is in<br>flow<br>s received while th<br>t mode (must be c | e the SSPxBUF<br>can only occur<br>avoid setting ove<br>itiated by writin<br>ne SSPxBUF re | in Slave mode. In S<br>erflow. In Master m<br>g to the SSPxBUF<br>egister is still holdi        | Slave mode, the u<br>ode, the overflow<br>register (must be | ser must read the s<br>bit is not set since<br>cleared in softwar | SSPxBUF, ever<br>each new recep<br>e). |

| bit 5            | <b>SSPxEN:</b> Syn<br>In both mode<br>ln SPI mode:<br>1 = Enables<br>0 = Disables<br>$ln l^2C mode:$<br>1 = Enables                                                                                                                                                  | nchronous Serial I<br>s, when enabled,                                                                                                             | these pins mus<br>figures SCKx, s<br>onfigures these<br>configures the s                   | It be properly conf<br>SDOx, SDIx and $\overline{S}$<br>pins as I/O port p<br>SDAx and SCLx pir | Sx as the source opins                                      | of the serial port pi                                             |                                        |

| bit 4            | In SPI mode:<br>1 = Idle state<br>0 = Idle state<br>In I <sup>2</sup> C Slave r<br>SCLx release<br>1 = Enable cl                                                                                                                                                     | for clock is a high<br>for clock is a low<br>mode:<br>e control<br>ock<br>ck low (clock stret<br>mode:                                             | level                                                                                      | ensure data setup                                                                               | time.)                                                      |                                                                   |                                        |

#### REGISTER 15-3: SSPxCON1: SSPx CONTROL REGISTER 1

# PIC18(L)F2X/4XK22

| SRCLK<2:0> | Divider | Fosc = 20 MHz | Fosc = 16 MHz | Fosc = 8 MHz | Fosc = 4 MHz | Fosc = 1 MHz |

|------------|---------|---------------|---------------|--------------|--------------|--------------|

| 111        | 512     | 25.6 μs       | 32 μs         | 64 μs        | 128 μs       | 512 μs       |

| 110        | 256     | 12.8 μs       | 16 μs         | 32 µs        | 64 μs        | 256 μs       |

| 101        | 128     | 6.4 μs        | 8 μs          | 16 μs        | 32 μs        | 128 μs       |

| 100        | 64      | 3.2 μs        | 4 μs          | 8 μs         | 16 μs        | 64 μs        |

| 011        | 32      | 1.6 μs        | 2 μs          | 4 μs         | 8 μs         | 32 μs        |

| 010        | 16      | 0.8 μs        | 1 μs          | 2 μs         | 4 μs         | 16 μs        |

| 001        | 8       | 0.4 μs        | 0.5 μs        | 1 μs         | 2 μs         | 8 μs         |

| 000        | 4       | 0.2 μs        | 0.25 μs       | 0.5 μs       | 1 μs         | 4 μs         |

# TABLE 20-1: DIVSRCLK FREQUENCY TABLE

| U-0              | U-0   | U-0               | R/W-0 | R/W-0          | R/W-0            | R/W-0            | R/W-0       |

|------------------|-------|-------------------|-------|----------------|------------------|------------------|-------------|

| —                | —     | —                 |       |                | DACR<4:0>        |                  |             |

| bit 7            |       |                   |       |                |                  |                  | bit 0       |

|                  |       |                   |       |                |                  |                  |             |

| Legend:          |       |                   |       |                |                  |                  |             |

| R = Readable     | bit   | W = Writable      | bit   | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is uncha | anged | x = Bit is unkn   | nown  | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared  |                |                  |                  |             |

### REGISTER 22-2: VREFCON2: VOLTAGE REFERENCE CONTROL REGISTER 1

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DACR<4:0>: DAC Voltage Output Select bits VOUT = ((VSRC+) - (VSRC-))\*(DACR<4:0>/(2<sup>5</sup>)) + VSRC-

### TABLE 22-1: REGISTERS ASSOCIATED WITH DAC MODULE

| Name     | Bit 7 | Bit 6  | Bit 5     | Bit 4 | Bit 3 | Bit 2     | Bit 1 | Bit 0  | Register<br>on Page |

|----------|-------|--------|-----------|-------|-------|-----------|-------|--------|---------------------|

| VREFCON0 | FVREN | FVRST  | FVRS<1:0> |       | _     | _         | _     | _      | 332                 |

| VREFCON1 | DACEN | DACLPS | DACOE     | _     | DACPS | S<1:0>    | _     | DACNSS | 335                 |

| VREFCON2 | _     | _      | _         |       |       | DACR<4:0> |       |        | 336                 |

**Legend:** — = Unimplemented locations, read as '0'. Shaded bits are not used by the DAC module.

# 24.0 SPECIAL FEATURES OF THE CPU

PIC18(L)F2X/4XK22 devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in Section 2.0 "Oscillator Module (With Fail-Safe Clock Monitor)".

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, PIC18(L)F2X/4XK22 devices have a Watchdog Timer, which is either permanently enabled via the Configuration bits or software controlled (if configured as disabled).

The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

# 24.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In Normal operation mode, a TBLWT instruction with the TBLPTR pointing to the Configuration register sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration register. The Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 6.6 "Writing to Flash Program Memory".

| U-0                                    | U-0                                              | R/P-1            | R/P-1             | R/P-1             | R/P-1               | R/P-1           | R/P-1 |  |  |

|----------------------------------------|--------------------------------------------------|------------------|-------------------|-------------------|---------------------|-----------------|-------|--|--|

| _                                      | — WDTPS<3:0>                                     |                  |                   | PS<3:0>           | WDTEN<1:0>          |                 |       |  |  |

| bit 7                                  |                                                  |                  |                   |                   |                     |                 | bit   |  |  |

|                                        |                                                  |                  |                   |                   |                     |                 |       |  |  |

| Legend:                                |                                                  |                  |                   |                   |                     |                 |       |  |  |

| R = Readable                           | e bit                                            | P = Programma    | ble bit           | U = Unimpleme     | nted bit, read as ' | 0'              |       |  |  |

| -n = Value when device is unprogrammed |                                                  |                  |                   | x = Bit is unknow | wn                  |                 |       |  |  |

|                                        |                                                  |                  |                   |                   |                     |                 |       |  |  |

| bit 7-6                                | Unimplemented                                    | I: Read as '0'   |                   |                   |                     |                 |       |  |  |

| bit 5-2                                | WDTPS<3:0>: Watchdog Timer Postscale Select bits |                  |                   |                   |                     |                 |       |  |  |

|                                        | 1111 = 1:32,768                                  | •                |                   |                   |                     |                 |       |  |  |

|                                        | 1110 = 1:16,384                                  | Ļ                |                   |                   |                     |                 |       |  |  |

|                                        | 1101 = 1:8,192                                   |                  |                   |                   |                     |                 |       |  |  |

|                                        | 1100 = 1:4,096                                   |                  |                   |                   |                     |                 |       |  |  |

|                                        | 1011 = 1:2,048                                   |                  |                   |                   |                     |                 |       |  |  |

|                                        | 1010 = 1:1,024                                   |                  |                   |                   |                     |                 |       |  |  |

|                                        | 1001 = <b>1:512</b>                              |                  |                   |                   |                     |                 |       |  |  |

|                                        | 1000 <b>= 1:256</b>                              |                  |                   |                   |                     |                 |       |  |  |

|                                        | 0111 = <b>1:128</b>                              |                  |                   |                   |                     |                 |       |  |  |

|                                        | 0110 = 1:64                                      |                  |                   |                   |                     |                 |       |  |  |

|                                        | 0101 = 1:32                                      |                  |                   |                   |                     |                 |       |  |  |

|                                        | 0100 = 1:16                                      |                  |                   |                   |                     |                 |       |  |  |

|                                        | 0011 = 1:8                                       |                  |                   |                   |                     |                 |       |  |  |

|                                        | 0010 = 1:4                                       |                  |                   |                   |                     |                 |       |  |  |

|                                        | 0001 = 1:2                                       |                  |                   |                   |                     |                 |       |  |  |

|                                        | 0000 = 1:1                                       |                  |                   |                   |                     |                 |       |  |  |

| bit 1-0                                | WDTEN<1:0>: \                                    | Vatchdog Timer   | Enable bits       |                   |                     |                 |       |  |  |

|                                        | 11 = WDT enabl                                   | led in hardware; | SWDTEN bit dis    | abled             |                     |                 |       |  |  |

|                                        | 10 = WDT control                                 |                  |                   |                   |                     |                 |       |  |  |

|                                        | 01 = WDT enab                                    | led when device  | is active, disabl | ed when device is | in Sleep; SWDTE     | EN bit disabled |       |  |  |

|                                        |                                                  | led in hardware; |                   |                   | 1,7 -               |                 |       |  |  |

# REGISTER 24-3: CONFIG2H: CONFIGURATION REGISTER 2 HIGH

# 25.0 INSTRUCTION SET SUMMARY

PIC18(L)F2X/4XK22 devices incorporate the standard set of 75 PIC18 core instructions, as well as an extended set of eight new instructions, for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

## 25.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous  $PIC^{\circledast}$  MCU instruction sets, while maintaining an easy migration from these  $PIC^{\circledast}$  MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal operations

- Control operations

The PIC18 instruction set summary in Table 25-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 25-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction. The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All bit-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located. The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the four MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 25-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The Instruction Set Summary, shown in Table 25-2, lists the standard instructions recognized by the Microchip Assembler (MPASM<sup>™</sup>).

Section 25.1.1 "Standard Instruction Set" provides a description of each instruction.

# 25.2.5 SPECIAL CONSIDERATIONS WITH MICROCHIP MPLAB<sup>®</sup> IDE TOOLS

The latest versions of Microchip's software tools have been designed to fully support the extended instruction set of the PIC18(L)F2X/4XK22 family of devices. This includes the MPLAB C18 C compiler, MPASM assembly language and MPLAB Integrated Development Environment (IDE).

When selecting a target device for software development, MPLAB IDE will automatically set default Configuration bits for that device. The default setting for the XINST Configuration bit is '0', disabling the extended instruction set and Indexed Literal Offset Addressing mode. For proper execution of applications developed to take advantage of the extended instruction set, XINST must be set during programming.

To develop software for the extended instruction set, the user must enable support for the instructions and the Indexed Addressing mode in their language tool(s). Depending on the environment being used, this may be done in several ways:

- A menu option, or dialog box within the environment, that allows the user to configure the language tool and its settings for the project

- A command line option

- A directive in the source code

These options vary between different compilers, assemblers and development environments. Users are encouraged to review the documentation accompanying their development systems for the appropriate information.

### 27.9 Memory Programming Requirements

| DC CHARACTERISTICS |       |                                                                      | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |        |       |                                               |  |

|--------------------|-------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|--------|-------|-----------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                                                       | Min                                                                                                                      | Тур† | Мах    | Units | Conditions                                    |  |

|                    |       | Internal Program Memory<br>Programming Specifications <sup>(1)</sup> |                                                                                                                          |      |        |       |                                               |  |

| D170               | Vpp   | Voltage on MCLR/VPP pin                                              | 8                                                                                                                        | _    | 9      | V     | (Note 3), (Note 4)                            |  |

| D171               | IDDP  | Supply Current during<br>Programming                                 | —                                                                                                                        | —    | 10     | mA    |                                               |  |

|                    |       | Data EEPROM Memory                                                   |                                                                                                                          |      |        |       |                                               |  |

| D172               | ED    | Byte Endurance                                                       | 100K                                                                                                                     | —    | _      | E/W   | -40°C to +85°C                                |  |

| D173               | Vdrw  | VDD for Read/Write                                                   | Vddmin                                                                                                                   | —    | VDDMAX | V     | Using EECON to read/<br>write                 |  |

| D175               | TDEW  | Erase/Write Cycle Time                                               | _                                                                                                                        | 3    | 4      | ms    |                                               |  |

| D176               | Tretd | Characteristic Retention                                             | —                                                                                                                        | 40   | —      | Year  | Provided no other specifications are violated |  |

| D177               | Tref  | Number of Total Erase/Write<br>Cycles before Refresh <sup>(2)</sup>  | 1M                                                                                                                       | 10M  | —      | E/W   | -40°C to +85°C                                |  |

|                    |       | Program Flash Memory                                                 |                                                                                                                          |      |        |       |                                               |  |

| D178               | Еρ    | Cell Endurance                                                       | 10K                                                                                                                      | —    | _      | E/W   | -40°C to +85°C (Note 5)                       |  |

| D179               | Vpr   | VDD for Read                                                         | VDDMIN                                                                                                                   | —    | VDDMAX | V     |                                               |  |

| D181               | Viw   | VDD for Row Erase or Write                                           | 2.2                                                                                                                      | —    | VDDMAX | V     | PIC18LF24K22                                  |  |

| D182               | Viw   |                                                                      | VDDMIN                                                                                                                   | —    | VDDMAX | V     | PIC18(L)F26K22                                |  |

| D183               | Tiw   | Self-timed Write Cycle Time                                          | —                                                                                                                        | 2    | -      | ms    |                                               |  |

| D184               | TRETD | Characteristic Retention                                             | —                                                                                                                        | 40   | —      | Year  | Provided no other specifications are violated |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** These specifications are for programming the on-chip program memory through the use of table write instructions.

2: Refer to Section 7.8 "Using the Data EEPROM" for a more detailed discussion on data EEPROM endurance.

**3:** Required only if single-supply programming is disabled.

4: The MPLAB ICD 2 does not support variable VPP output. Circuitry to limit the MPLAB ICD 2 VPP voltage must be placed between the MPLAB ICD 2 and target system when programming or debugging with the MPLAB ICD 2.

5: Self-write and Block Erase.

# PIC18(L)F2X/4XK22

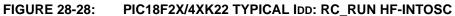

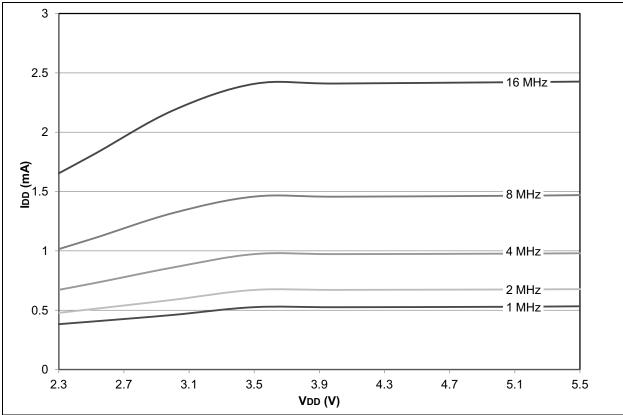

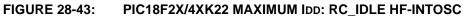

FIGURE 28-29: PIC18F2X/4XK22 MAXIMUM IDD: RC\_RUN HF-INTOSC

# PIC18(L)F2X/4XK22

© 2010-2016 Microchip Technology Inc.

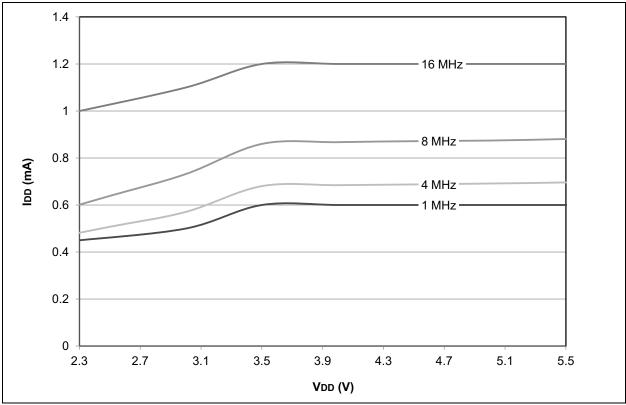

FIGURE 28-92: PIC18LF2X/4XK22 COMPARATOR OFFSET VOLTAGE, LOW-POWER MODE; VDD=1.8V

© 2010-2016 Microchip Technology Inc.

28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units     | Ν         | <b>/ILLIMETER</b> | S    |  |  |

|------------------------|-----------|-----------|-------------------|------|--|--|

| Dimensi                | on Limits | MIN       | NOM               | MAX  |  |  |

| Number of Pins         | N         | 28        |                   |      |  |  |

| Pitch                  | е         | 0.40 BSC  |                   |      |  |  |

| Overall Height         | Α         | 0.45      | 0.50              | 0.55 |  |  |

| Standoff               | A1        | 0.00      | 0.02              | 0.05 |  |  |

| Contact Thickness      | A3        | 0.127 REF |                   |      |  |  |

| Overall Width          | E         | 4.00 BSC  |                   |      |  |  |

| Exposed Pad Width      | E2        | 2.55      | 2.65              | 2.75 |  |  |

| Overall Length         | D         | 4.00 BSC  |                   |      |  |  |

| Exposed Pad Length     | D2        | 2.55      | 2.65              | 2.75 |  |  |

| Contact Width          | b         | 0.15      | 0.20              | 0.25 |  |  |

| Contact Length         | L         | 0.30      | 0.40              | 0.50 |  |  |

| Contact-to-Exposed Pad | K         | 0.20      | -                 | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-152A Sheet 2 of 2