Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 30x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46k22t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 2: | PIC18(L)F2XK22 PIN SUMMARY |

|----------|----------------------------|

|----------|----------------------------|

| IAD                       |              |     |        | FZANZZ     | 1 114 50 |          |                 |                                                  |         |              |                                               |            |         |              |

|---------------------------|--------------|-----|--------|------------|----------|----------|-----------------|--------------------------------------------------|---------|--------------|-----------------------------------------------|------------|---------|--------------|

| 28-SSOP, SOIC<br>28-SPDIP | 28-QFN, UQFN | 0/1 | Analog | Comparator | СТМИ     | SR Latch | Reference       | (E)CCP                                           | EUSART  | MSSP         | Timers                                        | Interrupts | dn-lluq | Basic        |

| 2                         | 27           | RA0 | AN0    | C12IN0-    |          |          |                 |                                                  |         |              |                                               |            |         |              |

| 3                         | 28           | RA1 | AN1    | C12IN1-    |          |          |                 |                                                  |         |              |                                               |            |         |              |

| 4                         | 1            | RA2 | AN2    | C2IN+      |          |          | VREF-<br>DACOUT |                                                  |         |              |                                               |            |         |              |

| 5                         | 2            | RA3 | AN3    | C1IN+      |          |          | VREF+           |                                                  |         |              |                                               |            |         |              |

| 6                         | 3            | RA4 |        | C1OUT      |          | SRQ      |                 | CCP5                                             |         |              | TOCKI                                         |            |         |              |

| 7                         | 4            | RA5 | AN4    | C2OUT      |          | SRNQ     | HLVDIN          |                                                  |         | SS1          |                                               |            |         |              |

| 10                        | 7            | RA6 |        |            |          |          |                 |                                                  |         |              |                                               |            |         | OSC2<br>CLKO |

| 9                         | 6            | RA7 |        |            |          |          |                 |                                                  |         |              |                                               |            |         | OSC1<br>CLKI |

| 21                        | 18           | RB0 | AN12   |            |          | SRI      |                 | CCP4<br>FLT0                                     |         | SS2          |                                               | INT0       | Y       |              |

| 22                        | 19           | RB1 | AN10   | C12IN3-    |          |          |                 | P1C                                              |         | SCK2<br>SCL2 |                                               | INT1       | Y       |              |

| 23                        | 20           | RB2 | AN8    |            | CTED1    |          |                 | P1B                                              |         | SDI2<br>SDA2 |                                               | INT2       | Y       |              |

| 24                        | 21           | RB3 | AN9    | C12IN2-    | CTED2    |          |                 | CCP2<br>P2A <sup>(1)</sup>                       |         | SDO2         |                                               |            | Y       |              |

| 25                        | 22           | RB4 | AN11   |            |          |          |                 | P1D                                              |         |              | T5G                                           | IOC        | Υ       |              |

| 26                        | 23           | RB5 | AN13   |            |          |          |                 | CCP3<br>P3A <sup>(4)</sup><br>P2B <sup>(3)</sup> |         |              | T1G<br>T3CKI <sup>(2)</sup>                   | IOC        | Y       |              |

| 27                        | 24           | RB6 |        |            |          |          |                 |                                                  | TX2/CK2 |              |                                               | IOC        | Y       | PGC          |

| 28                        | 25           | RB7 |        |            |          |          |                 |                                                  | RX2/DT2 |              |                                               | IOC        | Y       | PGD          |

| 11                        | 8            | RC0 |        |            |          |          |                 | P2B <sup>(3)</sup>                               |         |              | SOSCO<br>T1CKI<br>T3CKI <sup>(2)</sup><br>T3G |            |         |              |

| 12                        | 9            | RC1 |        |            |          |          |                 | CCP2<br>P2A <sup>(1)</sup>                       |         |              | SOSCI                                         |            |         |              |

| 13                        | 10           | RC2 | AN14   |            | CTPLS    |          |                 | CCP1<br>P1A                                      |         |              | T5CKI                                         |            |         |              |

| 14                        | 11           | RC3 | AN15   |            |          |          |                 |                                                  |         | SCK1<br>SCL1 |                                               |            |         |              |

| 15                        | 12           | RC4 | AN16   |            |          |          |                 |                                                  |         | SDI1<br>SDA1 |                                               |            |         |              |

| 16                        | 13           | RC5 | AN17   |            |          |          |                 |                                                  |         | SDO1         |                                               |            |         |              |

| 17                        | 14           | RC6 | AN18   |            |          |          |                 | CCP3<br>P3A <sup>(4)</sup>                       | TX1/CK1 |              |                                               |            |         |              |

| 18                        | 15           | RC7 | AN19   |            |          |          |                 | P3B                                              | RX1/DT1 |              |                                               |            |         |              |

| 1                         | 26           | RE3 |        |            |          |          |                 |                                                  |         |              |                                               |            |         | MCLR<br>VPP  |

| 8, 19<br>19               | 5, 16<br>16  | Vss |        |            |          |          |                 |                                                  |         |              |                                               |            |         | Vss          |

| 20                        | 17           | Vdd |        |            |          |          |                 |                                                  |         |              |                                               |            |         | Vdd          |

|                           |              |     |        |            |          |          |                 |                                                  |         |              |                                               |            |         |              |

CCP2/P2A multiplexed in fuses.

T3CKI multiplexed in fuses.

P2B multiplexed in fuses.

CCP3/P3A multiplexed in fuses. Note 1:

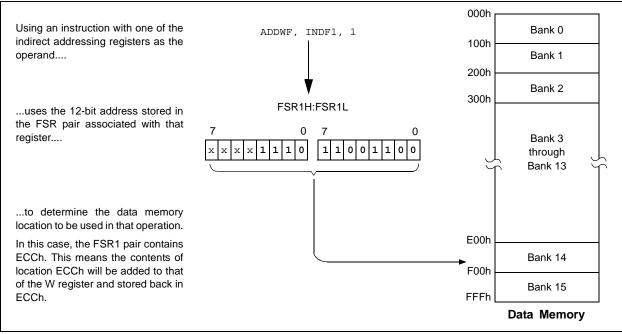

#### 5.6.3.1 FSR Registers and the INDF Operand

At the core of indirect addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. Each FSR pair holds a 12-bit value, therefore, the four upper bits of the FSRnH register are not used. The 12-bit FSR value can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers: they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because indirect addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

## 5.6.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers which cannot be directly read or written. Accessing these registers actually accesses the location to which the associated FSR register pair points, and also performs a specific action on the FSR value. They are:

- POSTDEC: accesses the location to which the FSR points, then automatically decrements the FSR by 1 afterwards

- POSTINC: accesses the location to which the FSR points, then automatically increments the FSR by 1 afterwards

- PREINC: automatically increments the FSR by one, then uses the location to which the FSR points in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the location to which the result points in the operation.

In this context, accessing an INDF register uses the value in the associated FSR register without changing it. Similarly, accessing a PLUSW register gives the FSR value an offset by that in the W register; however, neither W nor the FSR is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR register.

## FIGURE 5-10: INDIRECT ADDRESSING

| REGISTER          |                                                                                                                                 |                                    |                 |                  |                  | <b>D</b> # • • • •           | <b>D</b> 4 + 1 - 2 |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|------------------|------------------|------------------------------|--------------------|--|--|--|--|

| R/W-0             | R/W-0                                                                                                                           | R/W-0                              | R/W-0           | R/W-0            | R/W-0            | R/W-0                        | R/W-0              |  |  |  |  |

| SSP2IF            | BCL2IF                                                                                                                          | RC2IF                              | TX2IF           | CTMUIF           | TMR5GIF          | TMR3GIF                      | TMR1GIF            |  |  |  |  |

| bit 7             |                                                                                                                                 |                                    |                 |                  |                  |                              | bit 0              |  |  |  |  |

| Legend:           |                                                                                                                                 |                                    |                 |                  |                  |                              |                    |  |  |  |  |

| R = Readabl       | e bit                                                                                                                           | W = Writable                       | bit             | U = Unimplei     | mented bit, read | d as '0'                     |                    |  |  |  |  |

| -n = Value at POR |                                                                                                                                 | '1' = Bit is set                   |                 | '0' = Bit is cle | eared            | x = Bit is unkr              | nown               |  |  |  |  |

| bit 7             | SSP2IF: Svn                                                                                                                     | chronous Seria                     | l Port Interrup | ot Flag bit      |                  |                              |                    |  |  |  |  |

|                   | 1 = The trans                                                                                                                   |                                    | tion is comple  | •                | eared in softwa  | re)                          |                    |  |  |  |  |

| bit 6             | BCL2IF: MSS                                                                                                                     | SP2 Bus Collis                     | ion Interrupt F | lag bit          |                  |                              |                    |  |  |  |  |

|                   | (must be                                                                                                                        | cleared in soft                    | ware)           | e SSP2 modu      | le configured ir | n I <sup>2</sup> C master wa | as transmitting    |  |  |  |  |

|                   |                                                                                                                                 | collision occurre                  |                 |                  |                  |                              |                    |  |  |  |  |

| bit 5             | <b>RC2IF:</b> EUSART2 Receive Interrupt Flag bit<br>1 = The EUSART2 receive buffer, RCREG2, is full (cleared by reading RCREG2) |                                    |                 |                  |                  |                              |                    |  |  |  |  |

|                   |                                                                                                                                 | SART2 receive                      |                 |                  | red by reading   | RGREGZ)                      |                    |  |  |  |  |

| bit 4             | <b>TX2IF:</b> EUSART2 Transmit Interrupt Flag bit                                                                               |                                    |                 |                  |                  |                              |                    |  |  |  |  |

|                   |                                                                                                                                 | SART2 transmit<br>SART2 transmit   |                 | G2, is empty (   | cleared by writi | ng TXREG2)                   |                    |  |  |  |  |

| bit 3             | CTMUIF: CT                                                                                                                      | CTMUIF: CTMU Interrupt Flag bit    |                 |                  |                  |                              |                    |  |  |  |  |

|                   |                                                                                                                                 | terrupt occurre<br>U interrupt occ |                 | eared in softwa  | are)             |                              |                    |  |  |  |  |

| bit 2             | TMR5GIF: T                                                                                                                      | MR5 Gate Inter                     | rupt Flag bits  |                  |                  |                              |                    |  |  |  |  |

|                   | 0                                                                                                                               | e interrupt occ<br>gate occurred   | urred (must be  | e cleared in sof | ftware)          |                              |                    |  |  |  |  |

| bit 1             | TMR3GIF: T                                                                                                                      | MR3 Gate Inter                     | rupt Flag bits  |                  |                  |                              |                    |  |  |  |  |

|                   |                                                                                                                                 | e interrupt occ<br>gate occurred   | urred (must be  | e cleared in sof | itware)          |                              |                    |  |  |  |  |

| bit 0             | TMR1GIF: T                                                                                                                      | MR1 Gate Inter                     | rupt Flag bits  |                  |                  |                              |                    |  |  |  |  |

|                   | 1 = TMR gat<br>0 = No TMR                                                                                                       |                                    | urred (must be  | e cleared in sof | ftware)          |                              |                    |  |  |  |  |

### REGISTER 9-6: PIR3: PERIPHERAL INTERRUPT (FLAG) REGISTER 3

| R/W-1         | R/W-1                                           | R/W-1                       | R/W-1            | R/W-1            | R/W-1            | R/W-1           | R/W-1  |

|---------------|-------------------------------------------------|-----------------------------|------------------|------------------|------------------|-----------------|--------|

| OSCFIP        | C1IP                                            | C2IP                        | EEIP             | BCL1IP           | HLVDIP           | TMR3IP          | CCP2IP |

| bit 7         | ÷                                               | ·                           |                  | •                |                  | •               | bit (  |

| Legend:       |                                                 |                             |                  |                  |                  |                 |        |

| R = Readabl   | e bit                                           | W = Writable                | bit              | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at | POR                                             | '1' = Bit is set            | :                | '0' = Bit is cle |                  | x = Bit is unkr | nown   |

| bit 7         | <b>OSCFIP:</b> O<br>1 = High pr<br>0 = Low pri  | •                           | rrupt Priority I | bit              |                  |                 |        |

| bit 6         | <b>C1IP:</b> Comp<br>1 = High pr<br>0 = Low pri |                             | upt Priority bit |                  |                  |                 |        |

| bit 5         | <b>C2IP:</b> Comp<br>1 = High pr<br>0 = Low pri |                             | upt Priority bit | :                |                  |                 |        |

| bit 4         | EEIP: Data<br>1 = High pr<br>0 = Low pri        | •                           | Write Operat     | ion Interrupt Pr | iority bit       |                 |        |

| bit 3         | <b>BCL1IP:</b> M3<br>1 = High pr<br>0 = Low pri |                             | ion Interrupt F  | Priority bit     |                  |                 |        |

| bit 2         | <b>HLVDIP:</b> Lo<br>1 = High pr<br>0 = Low pri |                             | ct Interrupt Pri | ority bit        |                  |                 |        |

| bit 1         | -                                               | MR3 Overflow In<br>iority   | terrupt Priority | / bit            |                  |                 |        |

| bit 0         | -                                               | CP2 Interrupt Pri<br>iority | ority bit        |                  |                  |                 |        |

#### REGISTER 9-15: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

- 6. Configure and start the 8-bit TimerX resource:

- Clear the TMRxIF interrupt flag bit of the PIR2 or PIR4 register. See Note 1 below.

- Configure the TxCKPS bits of the TxCON register with the Timer prescale value.

- Enable the Timer by setting the TMRxON bit of the TxCON register.

- 7. Enable PWM output pin:

- Wait until the Timer overflows and the TMRxIF bit of the PIR2 or PIR4 register is set. See Note 1 below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

| Note 1: | In order to send a complete duty cycle         |

|---------|------------------------------------------------|

|         | and period on the first PWM output, the        |

|         | above steps must be included in the            |

|         | setup sequence. If it is not critical to start |

|         | with a complete PWM signal on the first        |

|         | output, then step 6 may be ignored.            |

## 14.3.3 PWM TIMER RESOURCE

The PWM standard mode makes use of one of the 8-bit Timer2/4/6 timer resources to specify the PWM period.

Configuring the CxTSEL<1:0> bits in the CCPTMRS0 or CCPTMRS1 register selects which Timer2/4/6 timer is used.

## 14.3.4 PWM PERIOD

The PWM period is specified by the PRx register of 8-bit TimerX. The PWM period can be calculated using the formula of Equation 14-1.

## EQUATION 14-1: PWM PERIOD

$PWM Period = [(PRx) + 1] \bullet 4 \bullet Tosc \bullet$ (TMRx Prescale Value)

**Note 1:** Tosc = 1/Fosc

When TMRx is equal to PRx, the following three events occur on the next increment cycle:

- TMRx is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPRxL into CCPRxH.

Note: The Timer postscaler (see Section 13.0 "Timer2/4/6 Module") is not used in the determination of the PWM frequency.

## 14.3.5 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPRxL register and DCxB<1:0> bits of the CCPxCON register. The CCPRxL contains the eight MSbs and the DCxB<1:0> bits of the CCPxCON register contain the two LSbs. CCPRxL and DCxB<1:0> bits of the CCPxCON register can be written to at any time. The duty cycle value is not latched into CCPRxH until after the period completes (i.e., a match between PRx and TMRx registers occurs). While using the PWM, the CCPRxH register is read-only.

Equation 14-2 is used to calculate the PWM pulse width.

Equation 14-3 is used to calculate the PWM duty cycle ratio.

## EQUATION 14-2: PULSE WIDTH

$$Pulse Width = (CCPRxL:CCPxCON < 5:4>) \bullet$$

TOSC • (TMRx Prescale Value)

## EQUATION 14-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(CCPRxL:CCPxCON < 5:4>)}{4(PRx + 1)}$

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMRx register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the TimerX prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 14-4).

#### **Register Definitions: ECCP Control** 14.5

#### REGISTER 14-1: CCPxCON: STANDARD CCPx CONTROL REGISTER

| U-0                           | U-0                         | R/W-0                                                           | R/W-0           | R/W-0                                                 | R/W-0            | R/W-0         | R/W-0       |  |  |  |  |

|-------------------------------|-----------------------------|-----------------------------------------------------------------|-----------------|-------------------------------------------------------|------------------|---------------|-------------|--|--|--|--|

| _                             | _                           | DCxB                                                            | <1:0>           | CCPxM<3:0>                                            |                  |               |             |  |  |  |  |

| pit 7                         |                             |                                                                 |                 |                                                       |                  |               | bit         |  |  |  |  |

| ogondi                        |                             |                                                                 |                 |                                                       |                  |               |             |  |  |  |  |

| L <b>egend:</b><br>R = Readal | ble bit                     | W = Writable                                                    | hit             | U = Unimpler                                          | mented bit, read | 1 as '0'      |             |  |  |  |  |

| u = Bit is ur                 |                             | x = Bit is unkr                                                 |                 | •                                                     | at POR and BO    |               | other Reset |  |  |  |  |

| "1' = Bit is s                | -                           | '0' = Bit is clea                                               |                 |                                                       |                  |               |             |  |  |  |  |

|                               |                             |                                                                 |                 |                                                       |                  |               |             |  |  |  |  |

| bit 7-6                       | Unused                      |                                                                 |                 |                                                       |                  |               |             |  |  |  |  |

| bit 5-4                       | DCxB<1:0:                   | >: PWM Duty Cyc                                                 | cle Least Sigr  | nificant bits                                         |                  |               |             |  |  |  |  |

|                               | <u>Capture mo</u><br>Unused | ode:                                                            |                 |                                                       |                  |               |             |  |  |  |  |

|                               | <u>Compare m</u><br>Unused  | node:                                                           |                 |                                                       |                  |               |             |  |  |  |  |

|                               | PWM mode                    | <u>ə:</u>                                                       |                 |                                                       |                  |               |             |  |  |  |  |

|                               | These bits                  | are the two LSbs                                                | of the PWM      | duty cycle. The                                       | eight MSbs are   | found in CCP  | RxL.        |  |  |  |  |

| bit 3-0                       | CCPxM<3:                    | CCPxM<3:0>: ECCPx Mode Select bits                              |                 |                                                       |                  |               |             |  |  |  |  |

|                               |                             | <ul> <li>Capture/Compare/PWM off (resets the module)</li> </ul> |                 |                                                       |                  |               |             |  |  |  |  |

|                               | 0001 = Re                   |                                                                 |                 |                                                       |                  |               |             |  |  |  |  |

|                               | 0010 = Co<br>0011 = Re      | mpare mode: tog<br>served                                       | gle output on   | match                                                 |                  |               |             |  |  |  |  |

|                               |                             | pture mode: ever                                                |                 | 1                                                     |                  |               |             |  |  |  |  |

|                               |                             | pture mode: ever                                                |                 |                                                       |                  |               |             |  |  |  |  |

|                               |                             | pture mode: ever                                                |                 |                                                       |                  |               |             |  |  |  |  |

|                               | 0111 = Ca                   | pture mode: ever                                                | y 16th rising ( | edge                                                  |                  |               |             |  |  |  |  |

|                               | 1000 <b>= Co</b>            | mpare mode: set                                                 | output on co    | mpare match (C                                        | CPx pin is set,  | CCPxIF is set | )           |  |  |  |  |

|                               |                             | mpare mode: clea                                                |                 |                                                       |                  |               |             |  |  |  |  |

|                               | CC                          | mpare mode: ge<br>PxIF is set)                                  |                 |                                                       | •                |               |             |  |  |  |  |

|                               | 1011 <b>= Co</b>            |                                                                 | rX (selected b  | igger (CCPx pir<br>by CxTSEL bits)<br>ing A/D convers | is reset         |               |             |  |  |  |  |

|                               | 11xx =: PV                  |                                                                 | 1 10 00t, 5tart |                                                       |                  |               |             |  |  |  |  |

| Note 1:                       | This feature is a           | vailable on CCP5                                                | 5 only.         |                                                       |                  |               |             |  |  |  |  |

**Note 1:** This feature is available on CCP5 only.

### 15.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCLx line low effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCLx.

The CKP bit of the SSPxCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCLx line to go low and then hold it. Setting CKP will release SCLx and allow more communication.

#### 15.5.6.1 Normal Clock Stretching

Following an ACK if the R/W bit of SSPxSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPxBUF with data to transfer to the master. If the SEN bit of SSPxCON2 is set, the slave hardware will always stretch the clock after the ACK sequence. Once the slave is ready; CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on whether the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPxBUF was read before the 9th falling edge of SCLx.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSPxBUF was loaded before the 9th falling edge of SCLx. It is now always cleared for read requests.

#### 15.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set, the clock is always stretched. This is the only time the SCLx is stretched without CKP being cleared. SCLx is released immediately after a write to SSPxADD.

**Note:** Previous versions of the module did not stretch the clock if the second address byte did not match.

#### 15.5.6.3 Byte NACKing

When the AHEN bit of SSPxCON3 is set; CKP is cleared by hardware after the 8th falling edge of SCLx for a received matching address byte. When the DHEN bit of SSPxCON3 is set; CKP is cleared after the 8th falling edge of SCLx for received data.

Stretching after the 8th falling edge of SCLx allows the slave to look at the received address or data and decide if it wants to ACK the received data.

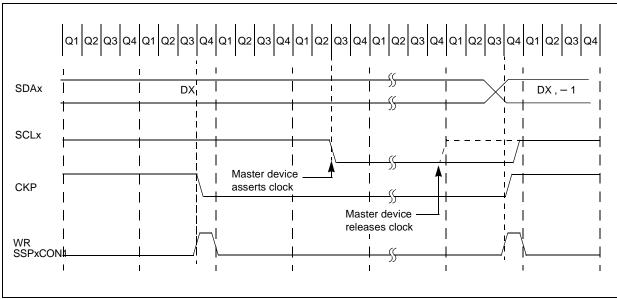

#### 15.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCLx line to go low and then hold it. However, clearing the CKP bit will not assert the SCLx output low until the SCLx output is already sampled low. Therefore, the CKP bit will not assert the SCLx line until an external I<sup>2</sup>C master device has already asserted the SCLx line. The SCLx output will remain low until the CKP bit is set and all other devices on the I<sup>2</sup>C bus have released SCLx. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCLx (see Figure 15-23).

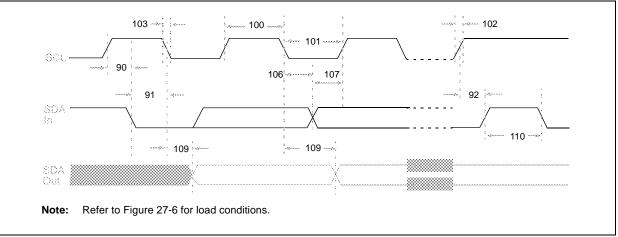

#### FIGURE 15-23: CLOCK SYNCHRONIZATION TIMING

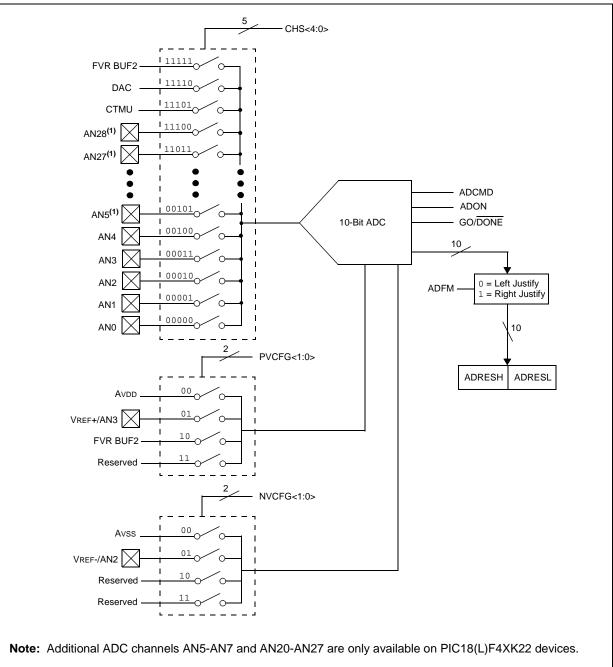

## 17.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH). The ADC voltage reference is software selectable to either VDD or a voltage applied to the external reference pins.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

Figure 17-1 shows the block diagram of the ADC.

## FIGURE 17-1: ADC BLOCK DIAGRAM

| R/W-0                                                       | U-0                                                                                                      | U-0              | U-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------|---------------|-------------------|-----------------|-----------------|-------|--|--|--|

| TRIGSEL                                                     | —                                                                                                        | —                | _             | PVCF              | G<1:0>          | <1:0> NVCFG<1:  |       |  |  |  |

| bit 7                                                       |                                                                                                          |                  |               |                   |                 |                 | bit   |  |  |  |

|                                                             |                                                                                                          |                  |               |                   |                 |                 |       |  |  |  |

| Legend:                                                     |                                                                                                          |                  |               |                   |                 |                 |       |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read |                                                                                                          |                  |               |                   |                 | d as '0'        |       |  |  |  |

| -n = Value at                                               | POR                                                                                                      | '1' = Bit is set |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |

|                                                             |                                                                                                          |                  |               |                   |                 |                 |       |  |  |  |

| bit 7                                                       |                                                                                                          | ecial Trigger S  |               |                   |                 |                 |       |  |  |  |

|                                                             | <ol> <li>Selects the special trigger from CTMU</li> <li>Selects the special trigger from CCP5</li> </ol> |                  |               |                   |                 |                 |       |  |  |  |

| <b>h</b> it <b>O A</b>                                      |                                                                                                          |                  |               |                   |                 |                 |       |  |  |  |

| bit 6-4                                                     | -                                                                                                        | ted: Read as '   |               |                   |                 |                 |       |  |  |  |

| bit 3-2                                                     | PVCFG<1:0>                                                                                               | : Positive Volta | ge Reference  | Configuration I   | oits            |                 |       |  |  |  |

|                                                             | 00 = A/D VREF+ connected to internal signal, AVDD                                                        |                  |               |                   |                 |                 |       |  |  |  |

|                                                             | 01 = A/D VREF+ connected to external pin, VREF+                                                          |                  |               |                   |                 |                 |       |  |  |  |

|                                                             | 10 = A/D VREF+ connected to internal signal, FVR BUF2                                                    |                  |               |                   |                 |                 |       |  |  |  |

|                                                             | 11 = Reserve                                                                                             | d (by default, A | /D VREF+ con  | nected to interr  | nal signal, AVD | D)              |       |  |  |  |

| bit 1-0                                                     | NVCFG<1:0>                                                                                               | : Negative Volt  | age Reference | e Configuration   | bits            |                 |       |  |  |  |

|                                                             | 00 = A/D VREF- connected to internal signal, AVss                                                        |                  |               |                   |                 |                 |       |  |  |  |

|                                                             | 01 = A/D VREF- connected to external pin, VREF-                                                          |                  |               |                   |                 |                 |       |  |  |  |

|                                                             | 10 = Reserve                                                                                             | d (by default, A | /D VREF- conr | nected to intern  | al signal, AVs  | 5)              |       |  |  |  |

|                                                             | 11 = Reserve                                                                                             | d (by default, A | D VREE- conr  | nected to intern  | al signal AV/se | 3)              |       |  |  |  |

#### REGISTER 17-2: ADCON1: A/D CONTROL REGISTER 1

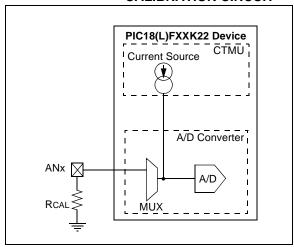

## 19.3 Calibrating the CTMU Module

The CTMU requires calibration for precise measurements of capacitance and time, as well as for accurate time delay. If the application only requires measurement of a relative change in capacitance or time, calibration is usually not necessary. An example of this type of application would include a capacitive touch switch, in which the touch circuit has a baseline capacitance, and the added capacitance of the human body changes the overall capacitance of a circuit.

If actual capacitance or time measurement is required, two hardware calibrations must take place: the current source needs calibration to set it to a precise current, and the circuit being measured needs calibration to measure and/or nullify all other capacitance other than that to be measured.

### 19.3.1 CURRENT SOURCE CALIBRATION

The current source on the CTMU module is trimable. Therefore, for precise measurements, it is possible to measure and adjust this current source by placing a high precision resistor, RCAL, onto an unused analog channel. An example circuit is shown in Figure 19-2. The current source measurement is performed using the following steps:

- 1. Initialize the A/D Converter.

- 2. Initialize the CTMU.

- Enable the current source by setting EDG1STAT (CTMUCONL<0>).

- 4. Issue settling time delay.

- 5. Perform A/D conversion.

- 6. Calculate the current source current using I = V/RCAL, where RCAL is a high precision resistance and *V* is measured by performing an A/D conversion.

The CTMU current source may be trimmed with the trim bits in CTMUICON using an iterative process to get an exact desired current. Alternatively, the nominal value without adjustment may be used; it may be stored by the software for use in all subsequent capacitive or time measurements.

To calculate the value for *RCAL*, the nominal current must be chosen, and then the resistance can be calculated. For example, if the A/D Converter reference voltage is 3.3V, use 70% of full scale, or 2.31V as the desired approximate voltage to be read by the A/D Converter. If the range of the CTMU current source is selected to be 0.55  $\mu$ A, the resistor value needed is calculated as *RCAL* = 2.31V/0.55  $\mu$ A, for a value of 4.2 MΩ. Similarly, if the current source is chosen to be 5.5  $\mu$ A, *RCAL* would be 420,000Ω, and 42,000Ω if the current source is set to 55  $\mu$ A.

#### FIGURE 19-2: CTMU CURRENT SOURCE CALIBRATION CIRCUIT

A value of 70% of full-scale voltage is chosen to make sure that the A/D Converter was in a range that is well above the noise floor. Keep in mind that if an exact current is chosen, that is to incorporate the trimming bits from CTMUICON, the resistor value of RCAL may need to be adjusted accordingly. RCAL may also be adjusted to allow for available resistor values. RCAL should be of the highest precision available, keeping in mind the amount of precision needed for the circuit that the CTMU will be used to measure. A recommended minimum would be 0.1% tolerance.

The following examples show one typical method for performing a CTMU current calibration. Example 19-1 demonstrates how to initialize the A/D Converter and the CTMU; this routine is typical for applications using both modules. Example 19-2 demonstrates one method for the actual calibration routine.

## 21.3 Register Definitions: FVR Control

| REGISTER                                | <u> 21-1: VREF</u>                                        | CON0: FIXED                                                                                 |                                                                 | REFERENC                                                               | E CONTROL F      | REGISTER         |              |

|-----------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------|------------------|------------------|--------------|

| R/W-0                                   | R/W-0                                                     | R/W-0                                                                                       | R/W-1                                                           | U-0                                                                    | U-0              | U-0              | U-0          |

| FVREN                                   | FVRST                                                     | FVRS<1:0>                                                                                   |                                                                 | —                                                                      | —                | —                | —            |

| bit 7                                   |                                                           | ·                                                                                           |                                                                 | -                                                                      |                  |                  | bit          |

| Legend:                                 |                                                           |                                                                                             |                                                                 |                                                                        |                  |                  |              |

| R = Readable bit W = Writable bit       |                                                           |                                                                                             |                                                                 | U = Unimplei                                                           | mented bit, read | as '0'           |              |

| u = Bit is unchanged x = Bit is unknown |                                                           |                                                                                             |                                                                 | -n/n = Value                                                           | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is s                          | et                                                        | '0' = Bit is cle                                                                            | ared                                                            |                                                                        |                  |                  |              |

| bit 6                                   | 0 = Fixed V                                               | ed Voltage Refe<br>oltage Referenc<br>oltage Referenc                                       | e output is no                                                  | ot ready or not e                                                      | enabled          |                  |              |

| bit 5-4                                 | FVRS<1:0><br>00 = Fixed \<br>01 = Fixed \<br>10 = Fixed \ | : Fixed Voltage<br>/oltage Referen<br>/oltage Referen<br>/oltage Referen<br>/oltage Referen | Reference Se<br>ce Peripheral<br>ce Peripheral<br>ce Peripheral | election bits<br>output is off<br>output is 1x (1,<br>output is 2x (2, | .048V)(1)        |                  |              |

| bit 3-2                                 |                                                           | Read as '0'. Mai                                                                            | •                                                               | •                                                                      |                  |                  |              |

| bit 1-0                                 | Unimpleme                                                 | nted: Read as '                                                                             | 0'.                                                             |                                                                        |                  |                  |              |

| Note 1.                                 | Fixed Voltage B                                           |                                                                                             |                                                                 |                                                                        |                  |                  |              |

### REGISTER 21-1: VREFCON0: FIXED VOLTAGE REFERENCE CONTROL REGISTER

Note 1: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name     | Bit 7 | Bit 6 | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|----------|-------|-------|-----------|-------|-------|-------|-------|-------|---------------------|

| VREFCON0 | FVREN | FVRST | FVRS<1:0> |       | _     |       |       |       | 332                 |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by the FVR module.

## 23.3 HLVD Setup

To set up the HLVD module:

- 1. Select the desired HLVD trip point by writing the value to the HLVDL<3:0> bits.

- 2. Set the VDIRMAG bit to detect high voltage (VDIRMAG = 1) or low voltage (VDIRMAG = 0).

- 3. Enable the HLVD module by setting the HLVDEN bit.

- 4. Clear the HLVD interrupt flag (PIR2<2>), which may have been set from a previous interrupt.

- If interrupts are desired, enable the HLVD interrupt by setting the HLVDIE and GIE/GIEH bits (PIE2<2> and INTCON<7>, respectively).

An interrupt will not be generated until the IRVST bit is set.

**Note:** Before changing any module settings (VDIRMAG, HLVDL<3:0>), first disable the module (HLVDEN = 0), make the changes and re-enable the module. This prevents the generation of false HLVD events.

## 23.4 Current Consumption

When the module is enabled, the HLVD comparator and voltage divider are enabled and consume static current. The total current consumption, when enabled, is specified in **Section 27.0** "**Electrical Specifications**". Depending on the application, the HLVD module does not need to operate constantly. To reduce current requirements, the HLVD circuitry may only need to be enabled for short periods where the voltage is checked. After such a check, the module could be disabled.

## 23.5 HLVD Start-up Time

The internal reference voltage of the HLVD module, specified in **Section 27.0 "Electrical Specifications**", may be used by other internal circuitry, such as the programmable Brown-out Reset. If the HLVD or other circuits using the voltage reference are disabled to lower the device's current consumption, the reference voltage circuit will require time to become stable before a low or high-voltage condition can be reliably detected. This start-up time, TIRVST, is an interval that is independent of device clock speed.

The HLVD interrupt flag is not enabled until TIRVST has expired and a stable reference voltage is reached. For this reason, brief excursions beyond the set point may not be detected during this interval (see Figure 23-2 or Figure 23-3).

| Mnemo     | onic,  | Description                     | Cycles | 16-Bit Instruction Word |      |      |      | Status          | Notes |

|-----------|--------|---------------------------------|--------|-------------------------|------|------|------|-----------------|-------|

| Opera     | nds    | Description                     | Cycles | MSb                     |      |      | LSb  | Affected        | Notes |

| LITERAL O | OPERAT | TIONS                           |        |                         |      |      |      |                 |       |

| ADDLW     | k      | Add literal and WREG            | 1      | 0000                    | 1111 | kkkk | kkkk | C, DC, Z, OV, N |       |

| ANDLW     | k      | AND literal with WREG           | 1      | 0000                    | 1011 | kkkk | kkkk | Z, N            |       |

| IORLW     | k      | Inclusive OR literal with WREG  | 1      | 0000                    | 1001 | kkkk | kkkk | Z, N            |       |

| LFSR      | f, k   | Move literal (12-bit) 2nd word  | 2      | 1110                    | 1110 | 00ff | kkkk | None            |       |

|           |        | to FSR(f) 1st word              |        | 1111                    | 0000 | kkkk | kkkk |                 |       |

| MOVLB     | k      | Move literal to BSR<3:0>        | 1      | 0000                    | 0001 | 0000 | kkkk | None            |       |

| MOVLW     | k      | Move literal to WREG            | 1      | 0000                    | 1110 | kkkk | kkkk | None            |       |

| MULLW     | k      | Multiply literal with WREG      | 1      | 0000                    | 1101 | kkkk | kkkk | None            |       |

| RETLW     | k      | Return with literal in WREG     | 2      | 0000                    | 1100 | kkkk | kkkk | None            |       |

| SUBLW     | k      | Subtract WREG from literal      | 1      | 0000                    | 1000 | kkkk | kkkk | C, DC, Z, OV, N |       |

| XORLW     | k      | Exclusive OR literal with WREG  | 1      | 0000                    | 1010 | kkkk | kkkk | Z, N            |       |

| DATA MEN  | IORY ← | PROGRAM MEMORY OPERATIO         | NS     |                         |      |      |      |                 |       |

| TBLRD*    |        | Table Read                      | 2      | 0000                    | 0000 | 0000 | 1000 | None            |       |

| TBLRD*+   |        | Table Read with post-increment  |        | 0000                    | 0000 | 0000 | 1001 | None            |       |

| TBLRD*-   |        | Table Read with post-decrement  |        | 0000                    | 0000 | 0000 | 1010 | None            |       |

| TBLRD+*   |        | Table Read with pre-increment   |        | 0000                    | 0000 | 0000 | 1011 | None            |       |

| TBLWT*    |        | Table Write                     | 2      | 0000                    | 0000 | 0000 | 1100 | None            |       |

| TBLWT*+   |        | Table Write with post-increment |        | 0000                    | 0000 | 0000 | 1101 | None            |       |

| TBLWT*-   |        | Table Write with post-decrement |        | 0000                    | 0000 | 0000 | 1110 | None            |       |

| TBLWT+*   |        | Table Write with pre-increment  |        | 0000                    | 0000 | 0000 | 1111 | None            |       |

#### TABLE 25-2: PIC18(L)F2X/4XK22 INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| $RLNCF \\ 0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f {,d {,a}]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RLNCF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |