Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 19x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf23k22-e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

#### 5.3.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as either two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSb = 0). To maintain alignment with instruction boundaries, the PC increments in steps of two and the LSb will always read '0' (see Section 5.1.1 "Program Counter").

Figure 5-4 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 5-4 shows how the instruction GOTO 0006h is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. Section 25.0 "Instruction Set Summary" provides further details of the instruction set.

|                |           |            | <b>LSB =</b> 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|-----------|------------|----------------|---------|---------------------------|

|                | Program M |            |                | 000000h |                           |

|                |           |            | 000002h        |         |                           |

|                |           |            |                |         | 000004h                   |

|                |           |            |                |         | 000006h                   |

| Instruction 1: | MOVLW     | 055h       | 0Fh            | 55h     | 000008h                   |

| Instruction 2: | GOTO      | 0006h      | EFh            | 03h     | 00000Ah                   |

|                |           |            | F0h            | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF     | 123h, 456h | C1h            | 23h     | 00000Eh                   |

|                |           |            | F4h            | 56h     | 000010h                   |

|                |           |            |                |         | 000012h                   |

|                |           |            |                |         | 000014h                   |

## FIGURE 5-4: INSTRUCTIONS IN PROGRAM MEMORY

## 5.3.4 TWO-WORD INSTRUCTIONS

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instruction always has '1111' as its four Most Significant bits; the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence – immediately after the first word – the data in the second word is accessed and used by the instruction sequence.

If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 5-4 shows how this works.

| Note: | See Section 5.8 "PIC18 Instruction<br>Execution and the Extended |

|-------|------------------------------------------------------------------|

|       | Instruction Set" for information on                              |

|       | two-word instructions in the extended instruction set.           |

| CASE 1:             |                  |                              |  |  |  |  |  |  |  |

|---------------------|------------------|------------------------------|--|--|--|--|--|--|--|

| Object Code         | Source Code      |                              |  |  |  |  |  |  |  |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |  |  |  |  |  |  |  |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; No, skip this word         |  |  |  |  |  |  |  |

| 1111 0100 0101 0110 |                  | ; Execute this word as a NOP |  |  |  |  |  |  |  |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |  |  |  |  |  |  |  |

| CASE 2:             |                  |                              |  |  |  |  |  |  |  |

| Object Code         | Source Code      |                              |  |  |  |  |  |  |  |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |  |  |  |  |  |  |  |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; Yes, execute this word     |  |  |  |  |  |  |  |

| 1111 0100 0101 0110 |                  | ; 2nd word of instruction    |  |  |  |  |  |  |  |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |  |  |  |  |  |  |  |

## EXAMPLE 5-4: TWO-WORD INSTRUCTIONS

## 6.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed one byte at a time. A write to program memory is executed on blocks of 64 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation cannot be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

## 6.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

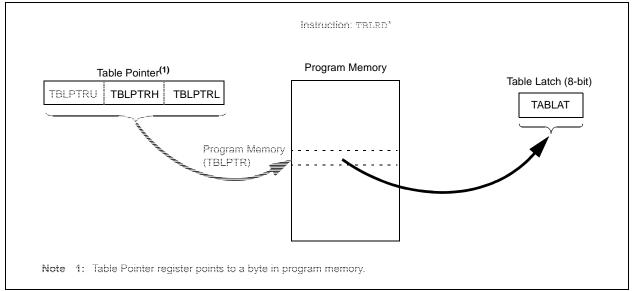

The table read operation retrieves one byte of data directly from program memory and places it into the TABLAT register. Figure 6-1 shows the operation of a table read.

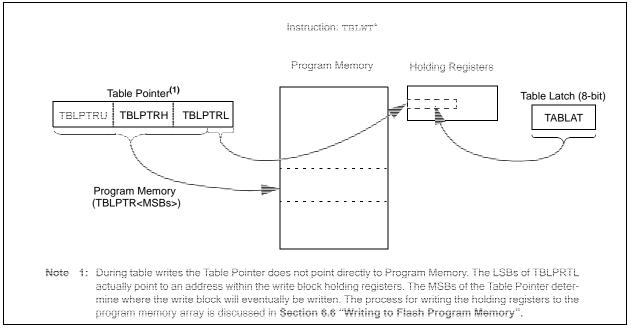

The table write operation stores one byte of data from the TABLAT register into a write block holding register. The procedure to write the contents of the holding registers into program memory is detailed in **Section 6.6 "Writing to Flash Program Memory"**. Figure 6-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. Tables containing data, rather than program instructions, are not required to be word aligned. Therefore, a table can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

#### FIGURE 6-1: TABLE READ OPERATION

## 6.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

## 6.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 6-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When EEPGD is clear, any subsequent operations will operate on the data EEPROM memory. When EEPGD is set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When CFGS is set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 24.0 "Special Features of the CPU"**). When CFGS is clear, memory selection access is determined by EEPGD. The FREE bit allows the program memory erase operation. When FREE is set, an erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. The WREN bit is clear on power-up.

The WRERR bit is set by hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

Note: During normal operation, the WRERR is read as '1'. This can indicate that a write operation was prematurely terminated by a Reset, or a write operation was attempted improperly.

The WR control bit initiates write operations. The WR bit cannot be cleared, only set, by firmware. Then WR bit is cleared by hardware at the completion of the write operation.

Note: The EEIF interrupt flag bit of the PIR2 register is set when the write is complete. The EEIF flag stays set until cleared by firmware.

## 8.0 8 x 8 HARDWARE MULTIPLIER

## 8.1 Introduction

All PIC18 devices include an 8 x 8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 8-1.

### 8.2 Operation

Example 8-1 shows the instruction sequence for an 8 x 8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 8-2 shows the sequence to do an 8 x 8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 8-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MULWF ARG2 ; ARG1 * ARG2 -><br>; PRODH:PRODL | MOVF  | ARG1, | W | ; |             |   |      |    |  |

|----------------------------------------------|-------|-------|---|---|-------------|---|------|----|--|

| ; PRODH:PRODL                                | MULWF | ARG2  |   | ; | ARG1        | * | ARG2 | -> |  |

|                                              |       |       |   | ; | PRODH:PRODL |   |      |    |  |

## EXAMPLE 8-2: 8 x 8 SIGNED MULTIPLY

| MOVF  | ARG1, W  |   |                |

|-------|----------|---|----------------|

| MULWF | ARG2     | ; | ARG1 * ARG2 -> |

|       |          | ; | PRODH:PRODL    |

| BTFSC | ARG2, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG1         |

| MOVF  | ARG2, W  |   |                |

| BTFSC | ARG1, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG2         |

|       |          |   |                |

|                  |                           | Program           | Cycles | Time     |          |          |         |  |

|------------------|---------------------------|-------------------|--------|----------|----------|----------|---------|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 64 MHz | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |

| Q v Q unoignod   | Without hardware multiply | 13                | 69     | 4.3 μs   | 6.9 μs   | 27.6 μs  | 69 μs   |  |

| 8 x 8 unsigned   | Hardware multiply         | 1                 | 1      | 62.5 ns  | 100 ns   | 400 ns   | 1 μs    |  |

| Q v Q aignad     | Without hardware multiply | 33                | 91     | 5.7 μs   | 9.1 μs   | 36.4 μs  | 91 μs   |  |

| 8 x 8 signed     | Hardware multiply         | 6                 | 6      | 375 ns   | 600 ns   | 2.4 μs   | 6 μs    |  |

| 16 x 16 uppigpod | Without hardware multiply | 21                | 242    | 15.1 μs  | 24.2 μs  | 96.8 μs  | 242 μs  |  |

| 16 x 16 unsigned | Hardware multiply         | 28                | 28     | 1.8 μs   | 2.8 μs   | 11.2 μs  | 28 μs   |  |

| 16 x 16 signed   | Without hardware multiply | 52                | 254    | 15.9 μs  | 25.4 μs  | 102.6 μs | 254 μs  |  |

| 16 x 16 signed   | Hardware multiply         | 35                | 40     | 2.5 μs   | 4.0 μs   | 16.0 μs  | 40 µs   |  |

## TABLE 8-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

|          |         |        |          |        | -                  |           |        |        |                     |

|----------|---------|--------|----------|--------|--------------------|-----------|--------|--------|---------------------|

| Name     | Bit 7   | Bit 6  | Bit 5    | Bit 4  | Bit 3              | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |

| ANSELA   | —       | _      | ANSA5    | _      | ANSA3              | ANSA2     | ANSA1  | ANSA0  | 149                 |

| CM1CON0  | C1ON    | C10UT  | C10E     | C1POL  | C1SP               | C1R       | C1CH   | l<1:0> | 308                 |

| CM2CON0  | C2ON    | C2OUT  | C2OE     | C2POL  | C2SP               | C2R       | C2CH   | l<1:0> | 308                 |

| LATA     | LATA7   | LATA6  | LATA5    | LATA4  | LATA3              | LATA2     | LATA1  | LATA0  | 152                 |

| VREFCON1 | DACEN   | DACLPS | DACOE    | —      | DACP               | SS<1:0>   | —      | DACNSS | 335                 |

| VREFCON2 | —       | —      | _        |        |                    | DACR<4:0> |        |        | 336                 |

| HLVDCON  | VDIRMAG | BGVST  | IRVST    | HLVDEN |                    | HLVDL     | <3:0>  |        | 337                 |

| PORTA    | RA7     | RA6    | RA5      | RA4    | RA3                | RA2       | RA1    | RA0    | 148                 |

| SLRCON   | —       | —      | _        | SLRE   | SLRD               | SLRC      | SLRB   | SLRA   | 153                 |

| SRCON0   | SRLEN   | S      | RCLK<2:0 | >      | SRQEN              | SRNQEN    | SRPS   | SRPR   | 329                 |

| SSP1CON1 | WCOL    | SSPOV  | SSPEN    | CKP    | CKP SSPM<3:0>      |           |        |        |                     |

| T0CON    | TMR0ON  | T08BIT | TOCS     | T0SE   | TOSE PSA TOPS<2:0> |           |        |        | 154                 |

| TRISA    | TRISA7  | TRISA6 | TRISA5   | TRISA4 | TRISA3             | TRISA2    | TRISA1 | TRISA0 | 151                 |

|          |         |        |          |        |                    |           |        |        |                     |

TABLE 10-2: REGISTERS ASSOCIATED WITH PORTA

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTA.

## TABLE 10-3: CONFIGURATION REGISTERS ASSOCIATED WITH PORTA

| Name                                                                              | Bit 7 | Bit 6 | Bit 5    | Bit 4  | Bit 3 | Bit 2     | Bit 1 | Bit 0 | Register<br>on Page |

|-----------------------------------------------------------------------------------|-------|-------|----------|--------|-------|-----------|-------|-------|---------------------|

| CONFIG1H                                                                          | IESO  | FCMEN | PRICLKEN | PLLCFG |       | FOSC<3:0> |       |       | 345                 |

| Levende unimplemented levetions, read as (2). Checked hits are not used for DODTA |       |       |          |        |       |           |       |       |                     |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTA.

## 10.1.1 PORTA OUTPUT PRIORITY

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the higher priority. Table 10-4 lists the PORTA pin functions from the highest to the lowest priority.

Analog input functions, such as ADC and comparator, are not shown in the priority lists.

These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below.

| D I. M   | Port Function Priority by Port Pin |                     |                     |                      |                      |  |  |  |  |  |

|----------|------------------------------------|---------------------|---------------------|----------------------|----------------------|--|--|--|--|--|

| Port bit | PORTA                              | PORTB               | PORTC               | PORTD <sup>(2)</sup> | PORTE <sup>(2)</sup> |  |  |  |  |  |

| 0        | RA0                                | CCP4 <sup>(1)</sup> | SOSCO               | SCL2                 | CCP3 <sup>(8)</sup>  |  |  |  |  |  |

|          |                                    | RB0                 | P2B <sup>(6)</sup>  | SCK2                 | P3A <sup>(8)</sup>   |  |  |  |  |  |

|          |                                    |                     | RC0                 | RD0                  | RE0                  |  |  |  |  |  |

| 1        | RA1                                | SCL2 <sup>(1)</sup> | SOSCI               | SDA2                 | P3B                  |  |  |  |  |  |

|          |                                    | SCK2 <sup>(1)</sup> | CCP2 <sup>(3)</sup> | CCP4                 | RE1                  |  |  |  |  |  |

|          |                                    | P1C <sup>(1)</sup>  | P2A <sup>(3)</sup>  | RD1                  |                      |  |  |  |  |  |

|          |                                    | RB1                 | RC1                 |                      |                      |  |  |  |  |  |

| 2        | RA2                                | SDA2 <sup>(1)</sup> | CCP1                | P2B                  | CCP5                 |  |  |  |  |  |

|          |                                    | P1B <sup>(1)</sup>  | P1A                 | RD2 <sup>(4)</sup>   | RE2                  |  |  |  |  |  |

|          |                                    | RB2                 | CTPLS               |                      |                      |  |  |  |  |  |

|          |                                    |                     | RC2                 |                      |                      |  |  |  |  |  |

| 3        | RA3                                | SDO2 <sup>(1)</sup> | SCL1                | P2C                  | MCLR                 |  |  |  |  |  |

|          |                                    | CCP2 <sup>(6)</sup> | SCK1                | RD3                  | Vpp                  |  |  |  |  |  |

|          |                                    | P2A <sup>(6)</sup>  | RC3                 |                      | RE3                  |  |  |  |  |  |

|          |                                    | RB3                 |                     |                      |                      |  |  |  |  |  |

| 4        | SRQ                                | P1D <sup>(1)</sup>  | SDA1                | SDO2                 |                      |  |  |  |  |  |

|          | C1OUT                              | RB4                 | RC4                 | P2D                  |                      |  |  |  |  |  |

|          | CCP5 <sup>(1)</sup>                |                     |                     | RD4                  |                      |  |  |  |  |  |

|          | RA4                                |                     |                     |                      |                      |  |  |  |  |  |

### TABLE 10-4: PORT PIN FUNCTION PRIORITY

Note 1: PIC18(L)F2XK22 devices.

2: PIC18(L)F4XK22 devices.

- **3:** Function default pin.

- **4:** Function default pin (28-pin devices).

- **5:** Function default pin (40/44-pin devices).

- **6:** Function alternate pin.

- 7: Function alternate pin (28-pin devices).

- 8: Function alternate pin (40/44-pin devices)

## 14.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 14-1 demonstrates the code to perform this function.

#### EXAMPLE 14-1: CHANGING BETWEEN CAPTURE PRESCALERS

| #define NEW_CAPT_PS 0x06 | //Capture          |

|--------------------------|--------------------|

|                          | // Prescale 4th    |

|                          | // rising edge     |

| CCPxCON = 0;             | // Turn the CCP    |

|                          | // Module Off      |

| CCPxCON = NEW_CAPT_PS;   | // Turn CCP module |

|                          | // on with new     |

|                          | // prescale value  |

## 14.1.5 CAPTURE DURING SLEEP

Capture mode requires a 16-bit TimerX module for use as a time base. There are four options for driving the 16-bit TimerX module in Capture mode. It can be driven by the system clock (Fosc), the instruction clock (Fosc/ 4), or by the external clock sources, the Secondary Oscillator (Sosc), or the TxCKI clock input. When the 16-bit TimerX resource is clocked by Fosc or Fosc/4, TimerX will not increment during Sleep. When the device wakes from Sleep, TimerX will continue from its previous state. Capture mode will operate during Sleep when the 16-bit TimerX resource is clocked by one of the external clock sources (Sosc or the TxCKI pin).

### TABLE 14-3: REGISTERS ASSOCIATED WITH CAPTURE

| Name     | Bit 7                                          | Bit 6                                         | Bit 5                       | Bit 4                       | Bit 3              | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |

|----------|------------------------------------------------|-----------------------------------------------|-----------------------------|-----------------------------|--------------------|-----------|--------|--------|---------------------|

| CCP1CON  | P1M<1:0> DC1B<1:0>                             |                                               |                             |                             |                    | 198       |        |        |                     |

| CCP2CON  | P2M-                                           | <1:0>                                         | DC2B                        | <1:0>                       |                    | 198       |        |        |                     |

| CCP3CON  | P3M-                                           | <1:0>                                         | DC3B                        | <1:0>                       |                    | CCP3M<    | 3:0>   |        | 198                 |

| CCP4CON  | —                                              | _                                             | DC4B                        | <1:0>                       |                    | CCP4M<    | 3:0>   |        | 198                 |

| CCP5CON  | —                                              | —                                             | DC5B                        | <1:0>                       |                    | CCP5M<    | 3:0>   |        | 198                 |

| CCPR1H   | Capture/Compare/PWM Register 1 High Byte (MSB) |                                               |                             |                             |                    |           |        |        | _                   |

| CCPR1L   |                                                | Capture/Compare/PWM Register 1 Low Byte (LSB) |                             |                             |                    |           |        |        |                     |

| CCPR2H   | Capture/Compare/PWM Register 2 High Byte (MSB) |                                               |                             |                             |                    |           |        |        | _                   |

| CCPR2L   | Capture/Compare/PWM Register 2 Low Byte (LSB)  |                                               |                             |                             |                    |           |        |        | _                   |

| CCPR3H   | Capture/Compare/PWM Register 3 High Byte (MSB) |                                               |                             |                             |                    |           |        |        | _                   |

| CCPR3L   | Capture/Compare/PWM Register 3 Low Byte (LSB)  |                                               |                             |                             |                    |           |        |        | _                   |

| CCPR4H   | Capture/Compare/PWM Register 4 High Byte (MSB) |                                               |                             |                             |                    |           |        |        | _                   |

| CCPR4L   | Capture/Compare/PWM Register 4 Low Byte (LSB)  |                                               |                             |                             |                    |           |        |        | _                   |

| CCPR5H   |                                                |                                               | Capture/Co                  | mpare/PWM F                 | Register 5 High By | te (MSB)  |        |        | —                   |

| CCPR5L   |                                                |                                               | Capture/Co                  | ompare/PWM                  | Register 5 Low By  | rte (LSB) |        |        | _                   |

| CCPTMRS0 | C3TSE                                          | :L<1:0>                                       | - C2TSEL<1:0> - C1TSEL<1:0> |                             |                    |           | 201    |        |                     |

| CCPTMRS1 | —                                              | _                                             | _                           | — — C5TSEL<1:0> C4TSEL<1:0> |                    |           |        | 201    |                     |

| INTCON   | GIE/GIEH                                       | PEIE/GIEL                                     | TMR0IE                      | INTOIE                      | RBIE               | TMR0IF    | INT0IF | RBIF   | 109                 |

| IPR1     | —                                              | ADIP                                          | RC1IP                       | TX1IP                       | SSP1IP             | CCP1IP    | TMR2IP | TMR1IP | 121                 |

| IPR2     | OSCFIP                                         | C1IP                                          | C2IP                        | EEIP                        | BCL1IP             | HLVDIP    | TMR3IP | CCP2IP | 122                 |

| IPR4     | —                                              | —                                             | —                           | —                           | —                  | CCP5IP    | CCP4IP | CCP3IP | 124                 |

| PIE1     | —                                              | ADIE                                          | RC1IE                       | TX1IE                       | SSP1IE             | CCP1IE    | TMR2IE | TMR1IE | 117                 |

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Capture mode.

**Note 1:** These registers/bits are available on PIC18(L)F4XK22 devices.

#### 14.4.8 SETUP FOR ECCP PWM OPERATION USING ECCP1 AND TIMER2

The following steps should be taken when configuring the ECCP1 module for PWM operation using Timer2:

- 1. Configure the PWM pins to be used (P1A, P1B, P1C, and P1D):

- Configure PWM outputs to be used as inputs by setting the corresponding TRIS bits. This prevents spurious outputs during setup.

- Set the PSTR1CON bits for each PWM output to be used.

- Select Timer2 as the period timer by configuring CCPTMR0 register bits C1TSEL<1:0> = '00'.

- 3. Set the PWM period by loading the PR2 register.

- 4. Configure auto-shutdown as OFF or select the source with the CCP1AS<2:0> bits of the ECCP1AS register.

- 5. Configure the auto-shutdown sources as needed:

- Configure each comparator used.

- Configure the comparator inputs as analog.

- Configure the FLT0 input pin and clear ANSB0.

- 6. Force a shutdown condition (OFF included):

- Configure safe starting output levels by setting the default shutdown drive states with the PSS1AC<1:0> and PSS1BD<1:0> bits of the ECCP1AS register.

- Clear the P1RSEN bit of the PWM1CON register.

- Set the CCP1AS bit of the ECCP1AS register.

- Configure the ECCP1 module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M<1:0> bits.

- Select the polarities of the PWM output signals with the CCP1M<3:0> bits.

- 8. Set the 10-bit PWM duty cycle:

- Load the eight MSbs into the CCPR1L register.

- Load the two LSbs into the DC<1:0> bits of the CCP1CON register.

- For Half-Bridge Output mode, set the deadband delay by loading P1DC<6:0> bits of the PWM1CON register with the appropriate value.

- 10. Configure and start TMR2:

- Set the TMR2 prescale value by loading the T2CKPS bits of the T2CON register.

- Start Timer2 by setting the TMR2ON bit.

- 11. Enable the ECCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- 12. Start the PWM:

- If shutdown auto-restart is used, then set the P1RSEN bit of the PWM1CON register.

- If shutdown auto-restart is not used, then clear the CCP1ASE bit of the ECCP1AS register.

### 15.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCLx pin is held low (see **Section 15.5.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then the SCLx pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCLx input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes Idle and waits for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCLx pin must be released by setting bit CKP.

An MSSPx interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 15.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDAx line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIRx register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

#### 15.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 15-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDAx and SCLx.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit set is received by the slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCLx, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

**Note 1:** If the master ACKs the clock will be stretched.

**2:** ACKSTAT is the only bit updated on the rising edge of SCLx (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

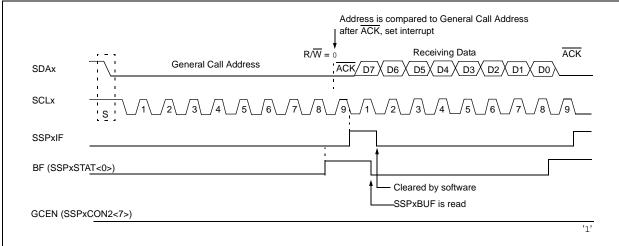

## 15.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^2C$  protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically  $\overline{ACK}$  the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 15-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the 8th falling edge of SCLx. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

## FIGURE 15-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

#### 15.5.9 SSPx MASK REGISTER

An SSPx Mask (SSPxMSK) register (Register 15-6) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPxSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSPx operation until written with a mask value.

The SSPx Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSPx mask has no effect during the reception of the first (high) byte of the address.

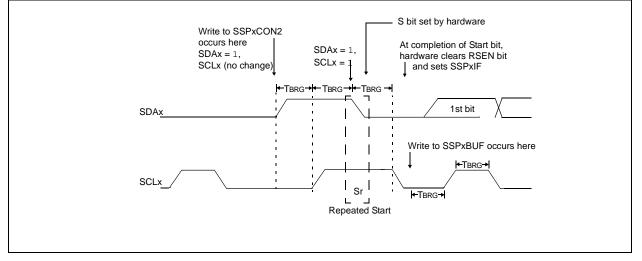

## 15.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 15-27) occurs when the RSEN bit of the SSPxCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. SCLx is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

## FIGURE 15-27: REPEAT START CONDITION WAVEFORM

| R/W-0            | R/W-0 | R/W-0                | R/W-0 | R/W-0          | R/W-0            | R/W-0          | R/W-0        |

|------------------|-------|----------------------|-------|----------------|------------------|----------------|--------------|

|                  |       |                      | ADD   | <7:0>          |                  |                |              |

| bit 7            |       |                      |       |                |                  |                | bit 0        |

|                  |       |                      |       |                |                  |                |              |

| Legend:          |       |                      |       |                |                  |                |              |

| R = Readable b   | bit   | W = Writable bit     |       | U = Unimpler   | mented bit, read | d as '0'       |              |

| u = Bit is uncha | inged | x = Bit is unknow    | n     | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |       | '0' = Bit is cleared | ł     |                |                  |                |              |

## REGISTER 15-7: SSPxADD: MSSPx ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

#### Master mode:

bit 7-0 ADD<7:0>: Baud Rate Clock Divider bits SCLx pin clock period = ((ADD<7:0> + 1) \*4)/Fosc

#### <u>10-Bit Slave mode — Most Significant Address byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### <u>10-Bit Slave mode — Least Significant Address byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

## 16.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- Half-duplex synchronous slave

- · Programmable clock and data polarity

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

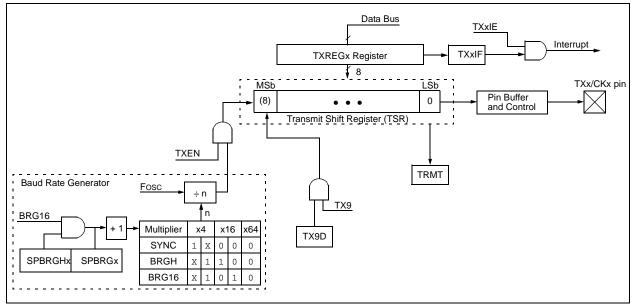

Block diagrams of the EUSART transmitter and receiver are shown in Figure 16-1 and Figure 16-2.

## FIGURE 16-1: EUSART TRANSMIT BLOCK DIAGRAM

**Branch if Not Zero**

0001

incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

2-cycle instruction.

If the ZERO bit is '0', then the program

The 2's complement number '2n' is added to the PC. Since the PC will have

Q3

Process

Data

No

operation

Q3

Process

Data

BNZ Jump

address (HERE)

address (Jump)

1; address (HERE + 2)

nnnn

nnnn

Q4

Write to PC

No

operation

Q4

No

operation

BNZ n  $\textbf{-128} \leq n \leq 127$ if ZERO bit is '0'  $(PC) + 2 + 2n \rightarrow PC$

| BNC         | <b>DV</b>                                             | Branch if                                                                 | Not Overflo                                                                          | w                                                      | BNZ   | 2                                                   | Brand                  | ch if                                                                                                                       |  |

|-------------|-------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------|-------|-----------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Synta       | ax:                                                   | BNOV n                                                                    |                                                                                      |                                                        | Synt  | ax:                                                 | BNZ                    | n                                                                                                                           |  |

| Oper        | ands:                                                 | -128 ≤ n ≤ 1                                                              | 127                                                                                  |                                                        | Ope   | rands:                                              | <b>-</b> 128 ≤         | n ≤ 1                                                                                                                       |  |

| Oper        | ation:                                                | if OVERFL0<br>(PC) + 2 + 2                                                |                                                                                      |                                                        | Ope   | ration:                                             | if ZER<br>(PC) +       |                                                                                                                             |  |

| Statu       | is Affected:                                          | None                                                                      |                                                                                      |                                                        | Statu | is Affected:                                        | None                   |                                                                                                                             |  |

| Enco        | oding:                                                | 1110                                                                      | 0101 nn                                                                              | nn nnnn                                                | Enco  | oding:                                              | 1110                   |                                                                                                                             |  |

| Desc        | ription:                                              | program wil<br>The 2's con<br>added to the<br>incrementer<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the<br>the new addro<br>n. This instruc | iber '2n' is<br>he PC will have<br>next<br>ess will be |       | Description:                                        |                        | If the ZERO<br>will branch.<br>The 2's corr<br>added to the<br>incremented<br>instruction,<br>PC + 2 + 2r<br>2-cycle instru |  |

| Word        | ds:                                                   | 1                                                                         |                                                                                      |                                                        | Word  | ds:                                                 | 1                      |                                                                                                                             |  |

| Cycle       | es:                                                   | 1(2)                                                                      |                                                                                      |                                                        | Cycl  | es:                                                 | 1(2)                   |                                                                                                                             |  |

|             | ycle Activity:<br>Imp:                                |                                                                           |                                                                                      |                                                        |       | ycle Activity:<br>Imp:                              |                        |                                                                                                                             |  |

|             | Q1                                                    | Q2                                                                        | Q3                                                                                   | Q4                                                     | _     | Q1                                                  | Q2                     |                                                                                                                             |  |

|             | Decode                                                | Read literal<br>'n'                                                       | Process<br>Data                                                                      | Write to PC                                            |       | Decode                                              | Read lit<br>'n'        | eral                                                                                                                        |  |

|             | No<br>operation                                       | No<br>operation                                                           | No<br>operation                                                                      | No<br>operation                                        |       | No<br>operation                                     | No<br>operati          | ion                                                                                                                         |  |

| If No       | o Jump:                                               |                                                                           | •                                                                                    | •                                                      | If N  | o Jump:                                             |                        |                                                                                                                             |  |

|             | Q1                                                    | Q2                                                                        | Q3                                                                                   | Q4                                                     | _     | Q1                                                  | Q2                     |                                                                                                                             |  |

|             | Decode                                                | Read literal<br>'n'                                                       | Process<br>Data                                                                      | No<br>operation                                        |       | Decode                                              | Read lit<br>'n'        | eral                                                                                                                        |  |

| <u>Exar</u> | nple:                                                 | HERE                                                                      | BNOV Jump                                                                            | )                                                      | Exar  | nple:                                               | HERE                   |                                                                                                                             |  |

|             | Before Instruc<br>PC                                  | = ad                                                                      | dress (here                                                                          | )                                                      |       | Before Instruc<br>PC                                | =                      | ade                                                                                                                         |  |

|             | After Instruction<br>If OVERI<br>PC<br>If OVERI<br>PC | FLOW = 0;<br>= ad<br>FLOW = 1;                                            | dress (Jump<br>dress (HERE                                                           |                                                        |       | After Instruction<br>If ZERO<br>PC<br>If ZERO<br>PC | on<br>=<br>=<br>=<br>= | 0;<br>ado<br>1;<br>ado                                                                                                      |  |

| TBL   | RD            | Table Rea                                                                                                                                                                                                                                                                                                                                                                                | d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |               |   |                                           |

|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------|---|-------------------------------------------|

| Synta | ax:           | TBLRD ( *; *                                                                                                                                                                                                                                                                                                                                                                             | *+; *-;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | +*) |               |   |                                           |

| Oper  | ands:         | None                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |               |   |                                           |

| Oper  | ation:        | if TBLRD *,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>TBLPTR – No Change;<br>if TBLRD *+,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>if TBLRD *-,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>(TBLPTR) – 1 $\rightarrow$ TBLPTR;<br>if TBLRD +*,<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT; |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |               |   |                                           |

| Statu | s Affected:   | None                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |               |   |                                           |

| Enco  | ding:         | 0000                                                                                                                                                                                                                                                                                                                                                                                     | 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00  | 0000          | ) | 10nn<br>nn=0 *<br>=1 *+<br>=2 *-<br>=3 +* |

| Desc  | ription:      | of Program<br>program me<br>Pointer (TBI<br>The TBLPT<br>each byte in<br>has a 2-Mby<br>TBLPT<br>TBLPT<br>TBLPT<br>TBLPT<br>The TBLRD<br>of TBLPTR<br>• no chang<br>• post-incre                                                                                                                                                                                                         | is instruction is used to read the contents<br>Program Memory (P.M.). To address the<br>ogram memory, a pointer called Table<br>binter (TBLPTR) is used.<br>TBLPTR (a 21-bit pointer) points to<br>ach byte in the program memory. TBLPTR<br>as a 2-Mbyte address range.<br>TBLPTR[0] = 0: Least Significant Byte<br>of Program Memory<br>Word<br>TBLPTR[0] = 1: Most Significant Byte<br>of Program Memory<br>Word<br>TBLPTR as follows:<br>no change<br>post-increment<br>post-decrement |     |               |   |                                           |

| Word  | ls:           | 1                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |               |   |                                           |

| Cycle |               | 2                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |               |   |                                           |

|       | ycle Activity |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |               |   |                                           |

| 20    | Q1            | Q2                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | Q3            |   | Q4                                        |

|       | Decode        | No<br>operatio                                                                                                                                                                                                                                                                                                                                                                           | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | оре | No<br>eration |   | No<br>operation                           |

|       |               | 1                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |               |   |                                           |

No operation (Read Program

Memory)

No

operation

No operation

(Write TABLAT)

| TBLRD | Table Read | (Continued) |

|-------|------------|-------------|

|-------|------------|-------------|

| Example1:                                                                       | TBLRD *+  | + ;         |                       |

|---------------------------------------------------------------------------------|-----------|-------------|-----------------------|

| Before Instruction                                                              | n         |             |                       |

| TABLAT                                                                          |           | =           | 55h                   |

| TBLPTR<br>MEMORY                                                                | (00A356h) | =           | 00A356h<br>34h        |

| After Instruction                                                               | (,        |             | •                     |

| TABLAT                                                                          |           | =           | 34h                   |

| TBLPTR                                                                          |           | =           | 00A357h               |

| Example2:                                                                       | TBLRD +*  | * ;         |                       |

| Examples.                                                                       |           | '           |                       |

| Before Instruction                                                              | 102100    | ,           |                       |

| Before Instructio                                                               | 102100    | =           | AAh                   |

| Before Instruction<br>TABLAT<br>TBLPTR                                          | on .      | =           | 01A357h               |

| Before Instructio                                                               | (01A357h) | =           |                       |

| Before Instruction<br>TABLAT<br>TBLPTR<br>MEMORY<br>MEMORY<br>After Instruction | (01A357h) | =<br>=<br>= | 01A357h<br>12h<br>34h |

| Before Instruction<br>TABLAT<br>TBLPTR<br>MEMORY<br>MEMORY                      | (01A357h) | =<br>=<br>= | 01A357h<br>12h        |

No

operation

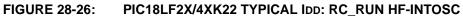

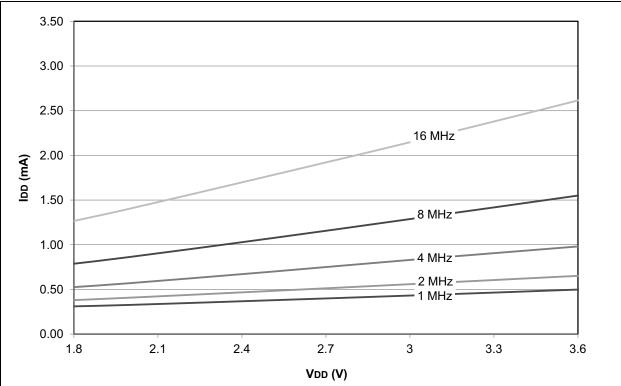

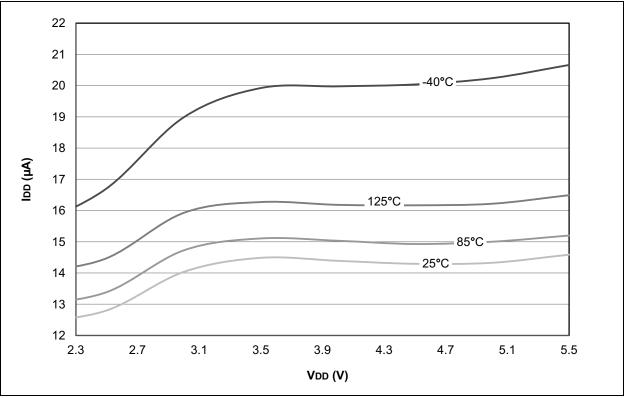

FIGURE 28-27: PIC18LF2X/4XK22 MAXIMUM IDD: RC\_RUN HF-INTOSC

© 2010-2016 Microchip Technology Inc.

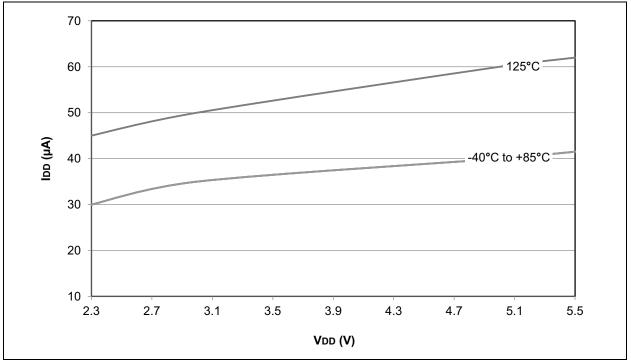

FIGURE 28-37: PIC18F2X/4XK22 MAXIMUM IDD: RC\_IDLE LF-INTOSC 31 kHz

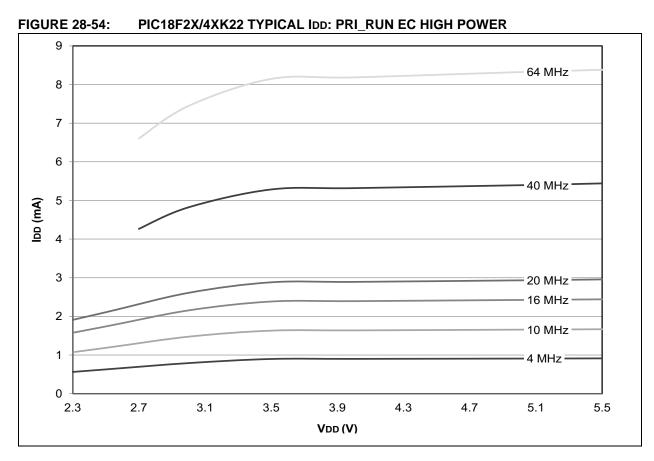

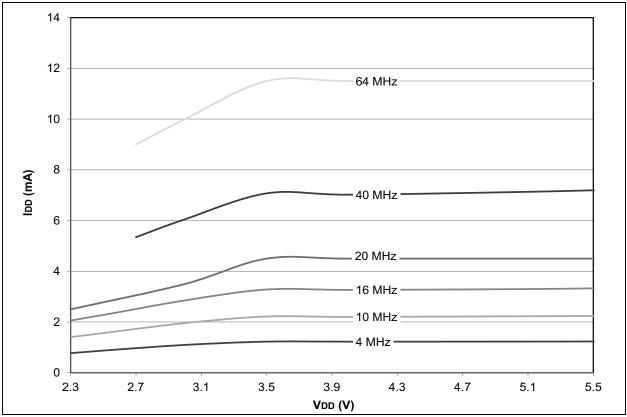

FIGURE 28-55: PIC18F2X/4XK22 MAXIMUM IDD: PRI\_RUN EC HIGH POWER

© 2010-2016 Microchip Technology Inc.

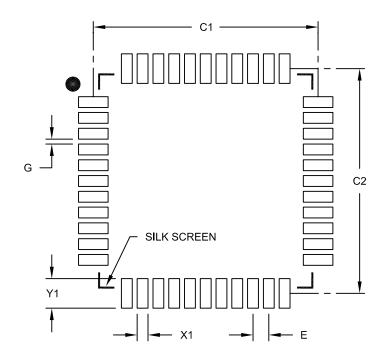

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |       |      |

|--------------------------|-------------|----------|-------|------|

| Dimensio                 | MIN         | NOM      | MAX   |      |

| Contact Pitch            | E           | 0.80 BSC |       |      |

| Contact Pad Spacing      | C1          |          | 11.40 |      |

| Contact Pad Spacing      | C2          |          | 11.40 |      |

| Contact Pad Width (X44)  | X1          |          |       | 0.55 |

| Contact Pad Length (X44) | Y1          |          |       | 1.50 |

| Distance Between Pads    | G           | 0.25     |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B