Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 19x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

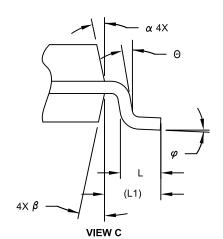

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf23k22-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

## 2.12.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin executing by the internal oscillator at the frequency set in the IRCF<2:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 external clock cycles.

- 4. OST timed out. External clock is ready.

- 5. OSTS is set.

- 6. Clock switch finishes according to Figure 2-9

### 2.12.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCCON register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in CONFIG1H Configuration register, or the internal oscillator. OSTS = 0 when the external oscillator is not ready, which indicates that the system is running from the internal oscillator.

| Old Clock                  |                             |             |              |       |       |                                              |

|----------------------------|-----------------------------|-------------|--------------|-------|-------|----------------------------------------------|

|                            | Enal-ob Jané <sub>i 8</sub> | Crock -     | <u> Syna</u> |       | Bares | <u>oğ</u>                                    |

| New Clock                  |                             |             |              | ····· |       | ····                                         |

| Rew Cik Ready 🛄            |                             |             |              |       |       |                                              |

| IRCF <2:0>                 | ien Oist 🗴 - Beien Gew      |             |              |       |       |                                              |

| System Clock               |                             |             |              |       |       |                                              |

|                            |                             |             |              |       |       |                                              |

| Low Speed Sig              | y Sibood                    |             |              |       |       |                                              |

| Low Spind Hig<br>Old Clock | 8 8peed<br><br>8en-oo Time9 | Clock Sync  |              |       |       |                                              |

|                            |                             | Ciccix Sync |              |       |       | <u>`````````````````````````````````````</u> |

| Old Oock                   |                             | Clock Syno  |              |       | Rumi  | N9<br>                                       |

| Gis Clock                  |                             | Cieck Syno  |              |       |       | ¥2                                           |

## FIGURE 2-9: CLOCK SWITCH TIMING

# EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR      |

|-----------------|-------------------------|

|                 | ;SAVED IN FAST REGISTER |

|                 | ; STACK                 |

| •               |                         |

| •               |                         |

|                 |                         |

| SUB1 •          |                         |

| •               |                         |

| RETURN, FAST    |                         |

|                 | ;IN FAST REGISTER STACK |

### 5.2.2 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

### 5.2.2.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of two (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

## EXAMPLE 5-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, | W |

|-------|-------|---------|---|

|       | CALL  | TABLE   |   |

| ORG   | nn00h |         |   |

| TABLE | ADDWF | PCL     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | •     |         |   |

|       | •     |         |   |

|       | •     |         |   |

|       |       |         |   |

## 5.2.2.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 6.1 "Table Reads and Table Writes".

| R/W-0         | R/W-0                                                         | R/W-0            | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |

|---------------|---------------------------------------------------------------|------------------|----------------|------------------|------------------|-----------------|---------|--|--|

| SSP2IE        | BCL2IE                                                        | RC2IE            | TX2IE          | CTMUIE           | TMR5GIE          | TMR3GIE         | TMR1GIE |  |  |

| bit 7         |                                                               |                  |                |                  |                  |                 | bit 0   |  |  |

| <del></del>   |                                                               |                  |                |                  |                  |                 |         |  |  |

| Legend:       |                                                               |                  |                |                  |                  |                 |         |  |  |

| R = Readable  |                                                               | W = Writable bit |                | -                | nented bit, read |                 |         |  |  |

| -n = Value at | POR                                                           | '1' = Bit is set |                | '0' = Bit is cle | ared             | x = Bit is unkr | IOWN    |  |  |

| bit 7         | SSP2IE: Mas                                                   | ster Synchrono   | us Serial Port | 2 Interrupt Ena  | able bit         |                 |         |  |  |

|               |                                                               | the MSSP2 inte   |                | opt              |                  |                 |         |  |  |

|               |                                                               | the MSSP2 int    |                |                  |                  |                 |         |  |  |

| bit 6         | BCL2IE: Bus                                                   | Collision Interi | upt Enable bi  | it               |                  |                 |         |  |  |

|               | 1 = Enabled<br>0 = Disabled                                   |                  |                |                  |                  |                 |         |  |  |

| bit 5         |                                                               | ART2 Receive     | ntorrunt Engl  | olo hit          |                  |                 |         |  |  |

| DIL 5         | 1 = Enabled                                                   |                  |                |                  |                  |                 |         |  |  |

|               | 0 = Disabled                                                  |                  |                |                  |                  |                 |         |  |  |

| bit 4         | TX2IE: EUSA                                                   | ART2 Transmit    | Interrupt Enal | ble bit          |                  |                 |         |  |  |

|               | 1 = Enabled                                                   |                  |                |                  |                  |                 |         |  |  |

|               | 0 = Disabled                                                  | 1                |                |                  |                  |                 |         |  |  |

| bit 3         |                                                               | MU Interrupt E   | nable bit      |                  |                  |                 |         |  |  |

|               | 1 = Enabled                                                   |                  |                |                  |                  |                 |         |  |  |

| h 11 O        | 0 = Disabled                                                  |                  |                | :.               |                  |                 |         |  |  |

| bit 2         | 1 = Enabled                                                   | MR5 Gate Inter   | rupt Enable b  | DIT              |                  |                 |         |  |  |

|               | 0 = Disabled                                                  |                  |                |                  |                  |                 |         |  |  |

| bit 1         | TMR3GIE: T                                                    | MR3 Gate Inter   | rupt Enable b  | bit              |                  |                 |         |  |  |

|               | <b>TMR3GIE:</b> TMR3 Gate Interrupt Enable bit<br>1 = Enabled |                  |                |                  |                  |                 |         |  |  |

|               | 0 = Disabled                                                  | 1                |                |                  |                  |                 |         |  |  |

| bit 0         | TMR1GIE: T                                                    | MR1 Gate Inter   | rupt Enable b  | oit              |                  |                 |         |  |  |

|               | 1 = Enabled                                                   |                  |                |                  |                  |                 |         |  |  |

|               | 0 = Disabled                                                  | 1                |                |                  |                  |                 |         |  |  |

### REGISTER 9-11: PIE3: PERIPHERAL INTERRUPT ENABLE (FLAG) REGISTER 3

| Name                 | Bit 7   | Bit 6   |                 | Bit 4           |                     | Bit 2                 |                       | Bit 0                 | Register |

|----------------------|---------|---------|-----------------|-----------------|---------------------|-----------------------|-----------------------|-----------------------|----------|

| Name                 | Bit /   | BIT 6   | Bit 5           | Bit 4           | Bit 3               | Bit 2                 | Bit 1                 | Bit U                 | on Page  |

| PIE2                 | OSCFIE  | C1IE    | C2IE            | EEIE            | BCL1IE              | HLVDIE                | TMR3IE                | CCP2IE                | 118      |

| PIE4                 | _       | —       | _               | —               | —                   | CCP5IE                | CCP4IE                | CCP3IE                | 120      |

| PIR1                 | _       | ADIF    | RC1IF           | TX1IF           | SSP1IF              | CCP1IF                | TMR2IF                | TMR1IF                | 112      |

| PIR2                 | OSCFIF  | C1IF    | C2IF            | EEIF            | BCL1IF              | HLVDIF                | TMR3IF                | CCP2IF                | 113      |

| PIR4                 | —       | —       | _               | —               | —                   | CCP5IF                | CCP4IF                | CCP3IF                | 115      |

| PMD0                 | UART2MD | UART1MD | TMR6MD          | TMR5MD          | TMR4MD              | TMR3MD                | TMR2MD                | TMR1MD                | 52       |

| PMD1                 | MSSP2MD | MSSP1MD | _               | CCP5MD          | CCP4MD              | CCP3MD                | CCP2MD                | CCP1MD                | 53       |

| T1CON                | TMR1C   | S<1:0>  | T1CKP           | S<1:0>          | T1SOSCEN            | T1SYNC                | T1RD16                | TMR10N                | 166      |

| T1GCON               | TMR1GE  | T1GPOL  | T1GTM           | T1GSPM          | T1GGO/DONE          | T1GVAL                | T1GSS                 | <1:0>                 | 167      |

| T3CON                | TMR3C   | S<1:0>  | T3CKP           | S<1:0>          | T3SOSCEN            | T3SYNC                | T3RD16                | TMR3ON                | 166      |

| T3GCON               | TMR3GE  | T3GPOL  | T3GTM           | T3GSPM          | T3GGO/DONE          | T3GVAL                | T3GSS                 | <1:0>                 | 167      |

| T5CON                | TMR5C   | S<1:0>  | T5CKP           | S<1:0>          | T5SOSCEN            | T5SYNC                | T5RD16                | TMR5ON                | 166      |

| T5GCON               | TMR5GE  | T5GPOL  | T5GTM           | T5GSPM          | T5GGO/DONE          | T5GVAL                | T5GSS                 | <1:0>                 | 167      |

| TMR1H                |         | Holding | Register for th | e Most Signifi  | cant Byte of the 10 | 6-bit TMR1 Re         | egister               |                       | _        |

| TMR1L                |         |         | Least Sign      | ificant Byte of | the 16-bit TMR1 I   | Register              |                       |                       | _        |

| TMR3H                |         | Holding | Register for th | e Most Signifi  | cant Byte of the 10 | 6-bit TMR3 Re         | egister               |                       | —        |

| TMR3L                |         |         | Least Sign      | ificant Byte of | the 16-bit TMR3 I   | Register              |                       |                       | —        |

| TMR5H                |         | Holding | Register for th | e Most Signifi  | cant Byte of the 10 | 6-bit TMR5 Re         | egister               |                       | —        |

| TMR5L                |         |         | Least Sign      | ificant Byte of | the 16-bit TMR5 I   | Register              |                       |                       | —        |

| TRISA                | TRISA7  | TRISA6  | TRISA5          | TRISA4          | TRISA3              | TRISA2                | TRISA1                | TRISA0                | 151      |

| TRISB                | TRISB7  | TRISB6  | TRISB5          | TRISB4          | TRISB3              | TRISB2                | TRISB1                | TRISB0                | 151      |

| TRISC                | TRISC7  | TRISC6  | TRISC5          | TRISC4          | TRISC3              | TRISC2                | TRISC1                | TRISC0                | 151      |

| TRISD <sup>(1)</sup> | TRISD7  | TRISD6  | TRISD5          | TRISD4          | TRISD3              | TRISD2                | TRISD1                | TRISD0                | 151      |

| TRISE                | WPUE3   | —       | —               | —               | —                   | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 151      |

## TABLE 14-3: REGISTERS ASSOCIATED WITH CAPTURE (CONTINUED)

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Capture mode.

**Note 1:** These registers/bits are available on PIC18(L)F4XK22 devices.

## TABLE 14-4: CONFIGURATION REGISTERS ASSOCIATED WITH CAPTURE

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| CONFIG3H | MCLRE | —     | P2BMX | T3CMX | HFOFST | CCP3MX | PBADEN | CCP2MX | 348                 |

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Capture mode.

## 14.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PRx is 255. The resolution is a function of the PRx register value as shown by Equation 14-4.

## EQUATION 14-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PRx+1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

# TABLE 14-7: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 32 MHz)

| PWM Frequency             | 1.95 kHz | 7.81 kHz | 31.25 kHz | 125 kHz | 250 kHz | 333.3 kHz |

|---------------------------|----------|----------|-----------|---------|---------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1       | 1       | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F    | 0x1F    | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8       | 7       | 6.6       |

## TABLE 14-8: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

## TABLE 14-9: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PRx Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

## 14.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMRx register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMRx will continue from its previous state.

### 14.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 2.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

## 14.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

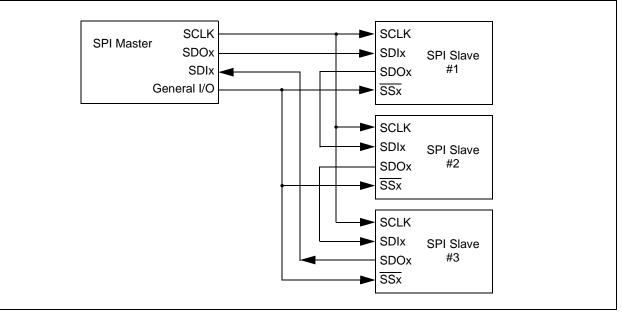

# FIGURE 15-7: SPI DAISY-CHAIN CONNECTION

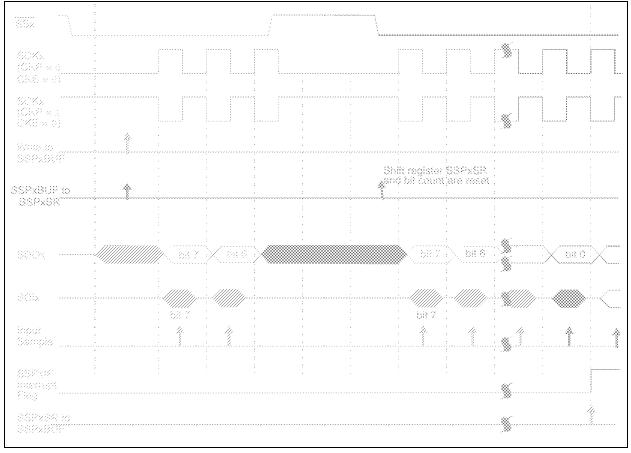

# FIGURE 15-8: SLAVE SELECT SYNCHRONOUS WAVEFORM

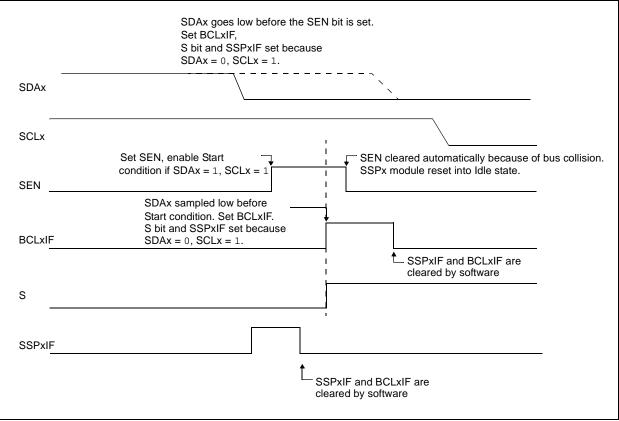

### 15.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDAx or SCLx are sampled low at the beginning of the Start condition (Figure 15-33).

- b) SCLx is sampled low before SDAx is asserted low (Figure 15-34).

During a Start condition, both the SDAx and the SCLx pins are monitored.

If the SDAx pin is already low, or the SCLx pin is already low, then all of the following occur:

- · the Start condition is aborted,

- the BCLxIF flag is set and

- the MSSPx module is reset to its Idle state (Figure 15-33).

The Start condition begins with the SDAx and SCLx pins deasserted. When the SDAx pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCLx pin is sampled low while SDAx is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDAx pin is sampled low during this count, the BRG is reset and the SDAx line is asserted early (Figure 15-35). If, however, a '1' is sampled on the SDAx pin, the SDAx pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCLx pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCLx pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDAx before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

# FIGURE 15-33: BUS COLLISION DURING START CONDITION (SDAx ONLY)

# 16.3 Register Definitions: EUSART Control

# REGISTER 16-1: TxSTAx: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-0                           | R/W-0                       | R/W-0                                         | R/W-0            | R/W-0             | R/W-0              | R-1              | R/W-0 |  |  |  |  |

|---------------------------------|-----------------------------|-----------------------------------------------|------------------|-------------------|--------------------|------------------|-------|--|--|--|--|

| CSRC                            | TX9                         | TXEN <sup>(1)</sup>                           | SYNC             | SENDB             | BRGH               | TRMT             | TX9D  |  |  |  |  |

| pit 7                           |                             |                                               |                  |                   |                    |                  | bit ( |  |  |  |  |

|                                 |                             |                                               |                  |                   |                    |                  |       |  |  |  |  |

| L <b>egend:</b><br>R = Readable | hit                         | W = Writable b                                | i+               | II – Unimplem     | ented bit, read as | · 'O'            |       |  |  |  |  |

| -n = Value at I                 |                             | '1' = Bit is set                              | it.              | '0' = Bit is clea |                    | x = Bit is unkno | WD    |  |  |  |  |

| -ii – value al i                | OR                          |                                               |                  |                   | ieu                |                  |       |  |  |  |  |

| bit 7                           | CSRC: Clock                 | Source Select bit                             |                  |                   |                    |                  |       |  |  |  |  |

|                                 | Asynchronous                |                                               |                  |                   |                    |                  |       |  |  |  |  |

|                                 | Don't care                  |                                               |                  |                   |                    |                  |       |  |  |  |  |

|                                 | Synchronous r               | <u>mode</u> :                                 |                  |                   |                    |                  |       |  |  |  |  |

|                                 | 1 = Master m                | node (clock gene                              | rated internally | from BRG)         |                    |                  |       |  |  |  |  |

|                                 | 0 = Slave mo                | ode (clock from e                             | xternal source)  |                   |                    |                  |       |  |  |  |  |

| oit 6                           | TX9: 9-bit Trar             | nsmit Enable bit                              |                  |                   |                    |                  |       |  |  |  |  |

|                                 |                             | -bit transmission                             |                  |                   |                    |                  |       |  |  |  |  |

|                                 |                             | 3-bit transmission                            |                  |                   |                    |                  |       |  |  |  |  |

| oit 5                           | TXEN: Transm                |                                               |                  |                   |                    |                  |       |  |  |  |  |

|                                 |                             | 1 = Transmit enabled<br>0 = Transmit disabled |                  |                   |                    |                  |       |  |  |  |  |

|                                 |                             |                                               |                  |                   |                    |                  |       |  |  |  |  |

| bit 4                           |                             | SYNC: EUSART Mode Select bit                  |                  |                   |                    |                  |       |  |  |  |  |

|                                 |                             | 1 = Synchronous mode<br>0 = Asynchronous mode |                  |                   |                    |                  |       |  |  |  |  |

| oit 3                           | ,                           | Break Character                               | - bit            |                   |                    |                  |       |  |  |  |  |

| UIL S                           | Asynchronous                |                                               | DI               |                   |                    |                  |       |  |  |  |  |

|                                 |                             |                                               | transmission (c  | leared by bardwa  | are upon complet   | ion)             |       |  |  |  |  |

|                                 | ,                           | ak transmission of                            | •                |                   |                    |                  |       |  |  |  |  |

|                                 | Synchronous r               |                                               | ·                |                   |                    |                  |       |  |  |  |  |

|                                 | Don't care                  |                                               |                  |                   |                    |                  |       |  |  |  |  |

| oit 2                           | BRGH: High B                | aud Rate Select                               | bit              |                   |                    |                  |       |  |  |  |  |

|                                 | <u>Asynchronous</u>         | mode:                                         |                  |                   |                    |                  |       |  |  |  |  |

|                                 | 1 = High spee               |                                               |                  |                   |                    |                  |       |  |  |  |  |

|                                 | 0 = Low spee                |                                               |                  |                   |                    |                  |       |  |  |  |  |

|                                 |                             | Synchronous mode:                             |                  |                   |                    |                  |       |  |  |  |  |

|                                 | Unused in this              |                                               | <b>.</b>         |                   |                    |                  |       |  |  |  |  |

| bit 1                           |                             | hit Shift Register                            | Status bit       |                   |                    |                  |       |  |  |  |  |

|                                 | 1 = TSR emp<br>0 = TSR full | ty                                            |                  |                   |                    |                  |       |  |  |  |  |

| hit 0                           |                             | it of Transmit Dat                            | 2                |                   |                    |                  |       |  |  |  |  |

| bit 0                           |                             | it of fransmit Dat                            | a                |                   |                    |                  |       |  |  |  |  |

|                                 | Can be addres               | s/data bit or a pa                            | rity bit         |                   |                    |                  |       |  |  |  |  |

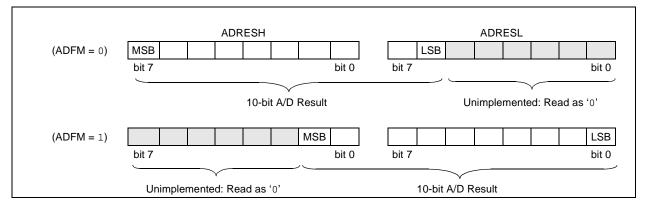

# 17.1.7 RESULT FORMATTING

The 10-bit A/D conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON2 register controls the output format.

Figure 17-2 shows the two output formats.

# FIGURE 17-2: 10-BIT A/D CONVERSION RESULT FORMAT

# 17.4 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 17-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 17-5. The maximum recommended impedance for analog sources is  $3 \ k\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D

acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 17-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

# EQUATION 17-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature = 50°C and external impedance of 10k

$$\Omega$$

3.0V VDD

$$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

= 5µs + TC + [(Temperature - 25°C)(0.05µs/°C)]

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{2047}\right) = V_{CHOLD} \qquad :[1] V_{CHOLD} charged to within 1/2 lsb

$$V_{APPLIED}\left(1 - e^{-\frac{TC}{RC}}\right) = V_{CHOLD} \qquad :[2] V_{CHOLD} charge response to VAPPLIED

$$V_{APPLIED}\left(1 - e^{-\frac{TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{2047}\right) \qquad :combining [1] and [2]$$

Solving for Tc:

$$T_{C} = -CHOLD(RIC + RSS + RS) ln(1/2047)$$

$$= -13.5pF(Ik\Omega + 700\Omega + 10k\Omega) ln(0.0004885)$$

$$= 1.20\mu s$$$$$$$$

$TACQ = 5\mu s + 1.20\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$ = 7.45\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

CNT Z C DC

After Instruction

CNT Z C DC

FFh 0 ? ?

00h

= = = =

= = = 1 1 1

| GOTO                                   | Uncondit                                                                                                                                                                                            | ional Bran      | ch                                                                                                                                                                                                                                                                |                                        | INCF              | Incremen                                   | t f                                       |              |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------|--------------------------------------------|-------------------------------------------|--------------|

| Syntax:                                | GOTO k                                                                                                                                                                                              |                 |                                                                                                                                                                                                                                                                   |                                        | Syntax:           | INCF f{,c                                  | d {,a}}                                   |              |

| Operands:                              | $0 \le k \le 104$                                                                                                                                                                                   | 8575            |                                                                                                                                                                                                                                                                   |                                        | Operands:         | $0 \leq f \leq 255$                        |                                           |              |

| Operation:                             | $k \rightarrow PC < 20$                                                                                                                                                                             | ):1>            |                                                                                                                                                                                                                                                                   |                                        |                   | d ∈ [0,1]<br>a ∈ [0,1]                     |                                           |              |

| Status Affected:                       | None                                                                                                                                                                                                | None            |                                                                                                                                                                                                                                                                   |                                        | Operation:        | $a \in [0, 1]$<br>(f) + 1 $\rightarrow$ de | act                                       |              |

| Encoding:                              |                                                                                                                                                                                                     |                 |                                                                                                                                                                                                                                                                   |                                        | Status Affected:  | $(1) \neq 1 \rightarrow 0$<br>C, DC, N,    |                                           |              |

| 1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110<br>1111                                                                                                                                                                                        |                 | 7kkk<br>kkk                                                                                                                                                                                                                                                       | kkkk <sub>0</sub><br>kkkk <sub>8</sub> | Encoding:         | 0010                                       | 10da ff                                   | ff ffff      |

| Description:                           | n: GOTO allows an unconditional branch Description:<br>anywhere within entire<br>2-Mbyte memory range. The 20-bit<br>value 'k' is loaded into PC<20:1>.<br>GOTO is always a 2-cycle<br>instruction. | Description:    | The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank is selecter<br>If 'a' is '1', the BSR is used to select th |                                        |                   |                                            |                                           |              |

| Words:                                 | 2                                                                                                                                                                                                   |                 |                                                                                                                                                                                                                                                                   |                                        |                   | GPR bank.                                  |                                           |              |

| Cycles:                                | 2                                                                                                                                                                                                   |                 |                                                                                                                                                                                                                                                                   |                                        |                   |                                            | and the extend                            |              |

| Q Cycle Activity:                      |                                                                                                                                                                                                     |                 |                                                                                                                                                                                                                                                                   |                                        |                   | in Indexed                                 | Literal Offset A                          | Addressing   |

| Q1                                     | Q2                                                                                                                                                                                                  | Q3              |                                                                                                                                                                                                                                                                   | Q4                                     |                   |                                            | never f ≤ 95 (5<br>5 <b>.2.3 "Byte-Or</b> |              |

| Decode                                 | Read literal<br>'k'<7:0>,                                                                                                                                                                           | No<br>operation | 'k'                                                                                                                                                                                                                                                               | ad literal<br>2<19:8>,<br>rite to PC   |                   | Bit-Oriente                                | ed Instruction<br>set Mode" for           | s in Indexed |

| No                                     | No                                                                                                                                                                                                  | No              |                                                                                                                                                                                                                                                                   | No                                     | Words:            | 1                                          |                                           |              |

| operation                              | operation                                                                                                                                                                                           | operation       | op                                                                                                                                                                                                                                                                | peration                               | Cycles:           | 1                                          |                                           |              |

|                                        |                                                                                                                                                                                                     |                 |                                                                                                                                                                                                                                                                   |                                        | Q Cycle Activity: |                                            |                                           |              |

| Example:                               | GOTO THE                                                                                                                                                                                            | RE              |                                                                                                                                                                                                                                                                   |                                        | Q1                | Q2                                         | Q3                                        | Q4           |

| After Instruction<br>PC =              | After Instruction<br>PC = Address (THERE)                                                                                                                                                           |                 | Decode                                                                                                                                                                                                                                                            | Read<br>register 'f'                   | Process<br>Data   | Write to destination                       |                                           |              |

|                                        |                                                                                                                                                                                                     |                 |                                                                                                                                                                                                                                                                   |                                        | Example:          | INCF                                       | CNT, 1, 0                                 |              |

|                                        |                                                                                                                                                                                                     |                 |                                                                                                                                                                                                                                                                   | Before Instruc                         | ction             |                                            |                                           |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RLNCF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| $(f < n >) \rightarrow dest < n + 1 >,$<br>$(f < 7 >) \rightarrow dest < 0 >$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |