Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 19x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf23k22-i-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: **DEVICE FEATURES**

| Features                                       | PIC18F23K22<br>PIC18LF23K22                                                                        | PIC18F24K22<br>PIC18LF24K22                                            | PIC18F25K22<br>PIC18(L)F25K22                           | PIC18F26K22<br>PIC18LF26K22                             | PIC18F43K22<br>PIC18LF43K22                             | PIC18F44K22<br>PIC18LF44K22                             | PIC18F45K22<br>PIC18LF45K22                             | PIC18F46K22<br>PIC18LF46K22                             |

|------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Program Memory (Bytes)                         | 8192                                                                                               | 16384                                                                  | 32768                                                   | 65536                                                   | 8192                                                    | 16384                                                   | 32768                                                   | 65536                                                   |

| Program Memory<br>(Instructions)               | 4096                                                                                               | 8192                                                                   | 16384                                                   | 32768                                                   | 4096                                                    | 8192                                                    | 16384                                                   | 32768                                                   |

| Data Memory (Bytes)                            | 512                                                                                                | 768                                                                    | 1536                                                    | 3896                                                    | 512                                                     | 768                                                     | 1536                                                    | 3896                                                    |

| Data EEPROM Memory (Bytes)                     | 256                                                                                                | 256                                                                    | 256                                                     | 1024                                                    | 256                                                     | 256                                                     | 256                                                     | 1024                                                    |

| I/O Ports                                      | A, B, C, E <sup>(1)</sup>                                                                          | A, B, C, E <sup>(1)</sup>                                              | A, B, C, E <sup>(1)</sup>                               | A, B, C, E <sup>(1)</sup>                               | A, B, C, D, E                                           |

| Capture/Compare/PWM Modules<br>(CCP)           | 2                                                                                                  | 2                                                                      | 2                                                       | 2                                                       | 2                                                       | 2                                                       | 2                                                       | 2                                                       |

| Enhanced CCP Modules (ECCP) -<br>Half Bridge   | 2                                                                                                  | 2                                                                      | 2                                                       | 2                                                       | 1                                                       | 1                                                       | 1                                                       | 1                                                       |

| Enhanced CCP Modules (ECCP) -<br>Full Bridge   | 1                                                                                                  | 1                                                                      | 1                                                       | 1                                                       | 2                                                       | 2                                                       | 2                                                       | 2                                                       |

| 10-bit Analog-to-Digital Module (ADC)          | 2 internal<br>17 input                                                                             | 2 internal<br>17 input                                                 | 2 internal<br>17 input                                  | 2 internal<br>17 input                                  | 2 internal<br>28 input                                  | 2 internal<br>28 input                                  | 2 internal<br>28 input                                  | 2 internal<br>28 input                                  |

| Packages                                       | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN<br>28-pin UQFN                             | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN<br>28-pin UQFN | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>40-pin UQFN<br>44-pin QFN<br>44-pin TQFP |

| Interrupt Sources                              |                                                                                                    |                                                                        |                                                         | 3                                                       | 33                                                      |                                                         |                                                         |                                                         |

| Timers (16-bit)                                |                                                                                                    |                                                                        |                                                         |                                                         | 4                                                       |                                                         |                                                         |                                                         |

| Serial Communications                          |                                                                                                    |                                                                        |                                                         |                                                         | SSP,<br>SART                                            |                                                         |                                                         |                                                         |

| SR Latch                                       |                                                                                                    |                                                                        |                                                         | Y                                                       | es                                                      |                                                         |                                                         |                                                         |

| Charge Time Measurement Unit<br>Module (CTMU)  |                                                                                                    |                                                                        |                                                         | Y                                                       | es                                                      |                                                         |                                                         |                                                         |

| Programmable<br>High/Low-Voltage Detect (HLVD) |                                                                                                    |                                                                        |                                                         | Y                                                       | es                                                      |                                                         |                                                         |                                                         |

| Programmable Brown-out Reset (BOR)             |                                                                                                    |                                                                        |                                                         | Y                                                       | es                                                      |                                                         |                                                         |                                                         |

| Resets (and Delays)                            | POR, BOR,<br>RESET Instruction,<br>Stack Overflow,<br>Stack Underflow<br>(PWRT, OST),<br>MCLR, WDT |                                                                        |                                                         |                                                         |                                                         |                                                         |                                                         |                                                         |

| Instruction Set                                |                                                                                                    |                                                                        |                                                         |                                                         | ructions;<br>struction Set enabled                      |                                                         |                                                         |                                                         |

| Operating Frequency                            |                                                                                                    |                                                                        |                                                         | DC - 6                                                  | 64 MHz                                                  |                                                         |                                                         |                                                         |

Note 1: PORTE contains the single RE3 read-only bit.

DS40001412G-page 13

PIC18(L)F2X/4XK22

#### 2.9 Effects of Power-Managed Modes on the Various Clock Sources

For more information about the modes discussed in this section see **Section 3.0** "**Power-Managed Modes**". A quick reference list is also available in Table 3-1.

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin, if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the secondary oscillator (SOSC) is operating and providing the device clock. The secondary oscillator may also run in all power-managed modes if required to clock Timer1, Timer3 or Timer5.

In internal oscillator modes (INTOSC\_RUN and INTOSC\_IDLE), the internal oscillator block provides the device clock source. The 31.25 kHz LFINTOSC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the power-managed mode (see Section 24.3 "Watchdog Timer (WDT)", Section 2.12 "Two-Speed Clock Start-up Mode" and Section 2.13 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up). The HFINTOSC and MFINTOSC outputs may be used directly to clock the device or may be divided down by the postscaler. The HFINTOSC and MFINTOSC outputs are disabled when the clock is provided directly from the LFINTOSC output.

When the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The LFINTOSC is required to support WDT operation. Other features may be operating that do not require a device clock source (i.e., SSP slave, PSP, INTn pins and others). Peripherals that may add significant current consumption are listed in Section 27.8 "DC Characteristics: Input/Output Characteristics, PIC18(L)F2X/4XK22".

#### 2.10 Power-up Delays

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 4.6** "**Device Reset Timers**".

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up. It is enabled by clearing (= 0) the PWRTEN Configuration bit.

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the PLL is enabled with external oscillator modes, the device is kept in Reset for an additional 2 ms, following the OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of interval TCSD, following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIOSC modes are used as the primary clock source.

When the HFINTOSC is selected as the primary clock, the main system clock can be delayed until the HFINTOSC is stable. This is user selectable by the HFOFST bit of the CONFIG3H Configuration register. When the HFOFST bit is cleared, the main system clock is delayed until the HFINTOSC is stable. When the HFOFST bit is set, the main system clock starts immediately.

In either case, the HFIOFS bit of the OSCCON register can be read to determine whether the HFINTOSC is operating and stable.

#### 2.11.3 CLOCK SWITCH TIMING

When switching between one oscillator and another, the new oscillator may not be operating which saves power (see Figure 2-9). If this is the case, there is a delay after the SCS<1:0> bits of the OSCCON register are modified before the frequency change takes place. The OSTS and IOFS bits of the OSCCON register will reflect the current active status of the external and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- 1. SCS<1:0> bits of the OSCCON register are modified.

- 2. The old clock continues to operate until the new clock is ready.

- 3. Clock switch circuitry waits for two consecutive rising edges of the old clock after the new clock ready signal goes true.

- 4. The system clock is held low starting at the next falling edge of the old clock.

- 5. Clock switch circuitry waits for an additional two rising edges of the new clock.

- 6. On the next falling edge of the new clock the low hold on the system clock is released and new clock is switched in as the system clock.

- 7. Clock switch is complete.

See Figure 2-1 for more details.

If the HFINTOSC is the source of both the old and new frequency, there is no start-up delay before the new frequency is active. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in **Section 27.0 "Electrical Specifications**", under AC Specifications (Oscillator Module).

#### 2.12 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device.

This mode allows the application to wake-up from Sleep, perform a few instructions using the HFINTOSC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

Note: Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCCON register to remain clear.

When the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) is enabled (see **Section 2.5.1 "Oscillator Start-up Timer (OST)**"). The OST will suspend program execution until 1024 oscillations are counted. Two-Speed Start-up mode minimizes the delay in code execution by operating from the internal oscillator as the OST is counting. When the OST count reaches 1024 and the OSTS bit of the OSCCON register is set, program execution switches to the external oscillator.

#### 2.12.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is enabled when all of the following settings are configured as noted:

- Two-Speed Start-up mode is enabled when the IESO of the CONFIG1H Configuration register is set.

- SCS<1:0> (of the OSCCON register) = 00.

- FOSC<2:0> bits of the CONFIG1H Configuration register are configured for LP, XT or HS mode.

Two-Speed Start-up mode becomes active after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

#### TABLE 4-2: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator     | Power-up <sup>(2)</sup> ar                             | Power-up <sup>(2)</sup> and Brown-out |                                 |  |  |  |

|----------------|--------------------------------------------------------|---------------------------------------|---------------------------------|--|--|--|

| Configuration  | <b>PWRTEN</b> = 0                                      | PWRTEN = 1                            | Power-Managed Mode              |  |  |  |

| HSPLL          | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup>       | 1024 Tosc + 2 ms <sup>(2)</sup> |  |  |  |

| HS, XT, LP     | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                             | 1024 Tosc                       |  |  |  |

| EC, ECIO       | 66 ms <sup>(1)</sup>                                   | _                                     | —                               |  |  |  |

| RC, RCIO       | 66 ms <sup>(1)</sup>                                   | _                                     | —                               |  |  |  |

| INTIO1, INTIO2 | 66 ms <sup>(1)</sup>                                   |                                       | —                               |  |  |  |

Note 1: 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.2: 2 ms is the nominal time required for the PLL to lock.

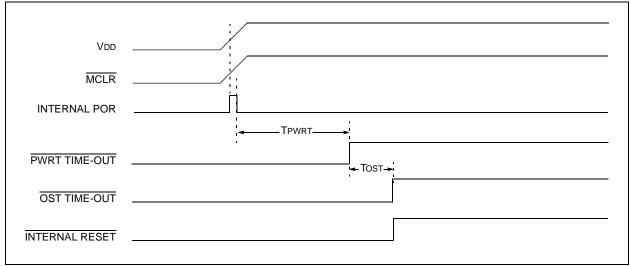

#### FIGURE 4-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD, VDD RISE < TPWRT)

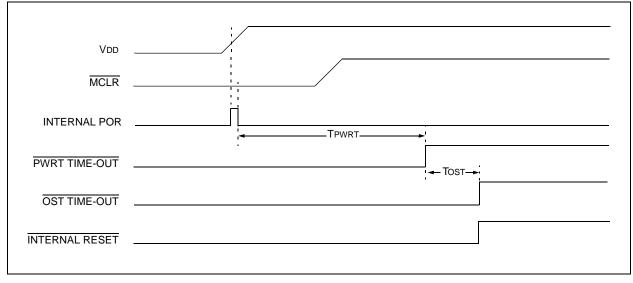

### FIGURE 4-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

# PIC18(L)F2X/4XK22

| Address | Name                  | Bit 7   | Bit 6                                     | Bit 5                        | Bit 4            | Bit 3                   | Bit 2               | Bit 1                        | Bit 0     | <u>Value on</u><br>POR, BOR |

|---------|-----------------------|---------|-------------------------------------------|------------------------------|------------------|-------------------------|---------------------|------------------------------|-----------|-----------------------------|

| FD1h    | WDTCON                | _       | —                                         | —                            | _                | _                       |                     | —                            | SWDTEN    | 0                           |

| FD0h    | RCON                  | IPEN    | SBOREN                                    | _                            | RI               | TO                      | PD                  | POR                          | BOR       | 01-1 1100                   |

| FCFh    | TMR1H                 |         | Holding R                                 | egister for the              | Most Significa   | ant Byte of the         | 16-bit TMR1 R       | egister                      | •         | xxxx xxxx                   |

| FCEh    | TMR1L                 |         |                                           | Least Signif                 | icant Byte of th | ne 16-bit TMR1          | Register            |                              |           | xxxx xxxx                   |

| FCDh    | T1CON                 | TMR1C   | S<1:0>                                    | T1CKF                        | PS<1:0>          | T1SOSCEN                | T1SYNC              | T1RD16                       | TMR10N    | 0000 0000                   |

| FCCh    | T1GCON                | TMR1GE  | T1GPOL                                    | T1GTM                        | T1GSPM           | T <u>1GGO</u> /<br>DONE | T1GVAL              | T1GS                         | S<1:0>    | 0000 xx00                   |

| FCBh    | SSP1CON3              | ACKTIM  | PCIE                                      | SCIE                         | BOEN             | SDAHT                   | SBCDE               | AHEN                         | DHEN      | 0000 0000                   |

| FCAh    | SSP1MSK               |         |                                           |                              | SSP1 MASK F      | Register bits           |                     |                              |           | 1111 1111                   |

| FC9h    | SSP1BUF               |         |                                           | SSP1                         | Receive Buffer   | r/Transmit Reg          | ister               |                              |           | xxxx xxxx                   |

| FC8h    | SSP1ADD               | SSP1    | Address Regis                             | ster in I <sup>2</sup> C Sla | ve Mode. SSP     | 1 Baud Rate R           | eload Register      | r in I <sup>2</sup> C Master | Mode      | 0000 0000                   |

| FC7h    | SSP1STAT              | SMP     | CKE                                       | CKE D/Ā P S R/W UA BF        |                  |                         |                     | BF                           | 0000 0000 |                             |

| FC6h    | SSP1CON1              | WCOL    | SSPOV                                     | SSPEN                        | CKP              |                         | SSPM                | <3:0>                        |           | 0000 0000                   |

| FC5h    | SSP1CON2              | GCEN    | ACKSTAT                                   | ACKDT                        | ACKEN            | RCEN                    | PEN                 | RSEN                         | SEN       | 0000 0000                   |

| FC4h    | ADRESH                |         |                                           |                              | A/D Result,      | High Byte               |                     |                              |           | xxxx xxxx                   |

| FC3h    | ADRESL                |         |                                           |                              | A/D Result,      | Low Byte                |                     |                              |           | xxxx xxxx                   |

| FC2h    | ADCON0                | _       |                                           |                              | CHS<4:0>         |                         |                     | GO/DONE                      | ADON      | 00 0000                     |

| FC1h    | ADCON1                | TRIGSEL | _                                         | _                            | _                | PVCF                    | G<1:0>              | NVCF                         | G<1:0>    | 0 0000                      |

| FC0h    | ADCON2                | ADFM    | _                                         |                              | ACQT<2:0>        |                         |                     | ADCS<2:0>                    |           | 0-00 0000                   |

| FBFh    | CCPR1H                |         | Capture/Compare/PWM Register 1, High Byte |                              |                  |                         |                     |                              |           | xxxx xxxx                   |

| FBEh    | CCPR1L                |         |                                           | Captur                       | e/Compare/PV     | VM Register 1,          | Low Byte            |                              |           | xxxx xxxx                   |

| FBDh    | CCP1CON               | P1M<    | <1:0>                                     | DC1E                         | 3<1:0>           |                         | CCP1N               | 1<3:0>                       |           | 0000 0000                   |

| FBCh    | TMR2                  |         |                                           |                              | Timer2 F         | Register                |                     |                              |           | 0000 0000                   |

| FBBh    | PR2                   |         |                                           |                              | Timer2 Peri      | od Register             |                     |                              |           | 1111 1111                   |

| FBAh    | T2CON                 | _       |                                           | T2OUT                        | PS<3:0>          |                         | TMR2ON T2CKPS<1:0>  |                              |           | -000 0000                   |

| FB9h    | PSTR1CON              | _       | _                                         | _                            | STR1SYNC         | STR1D                   | STR1C               | STR1B                        | STR1A     | 0 0001                      |

| FB8h    | BAUDCON1              | ABDOVF  | RCIDL                                     | DTRXP                        | CKTXP            | BRG16                   | _                   | WUE                          | ABDEN     | 0100 0-00                   |

| FB7h    | PWM1CON               | P1RSEN  |                                           |                              |                  | P1DC<6:0>               |                     |                              |           | 0000 0000                   |

| FB6h    | ECCP1AS               | CCP1ASE |                                           | CCP1AS<2:0                   | >                | PSS1A                   | AC<1:0> PSS1BD<1:0> |                              |           | 0000 0000                   |

| FB4h    | T3GCON                | TMR3GE  | T3GPOL                                    | T3GTM                        | T3GSPM           | T <u>3GGO</u> /<br>DONE | T3GVAL              | T3GS                         | S<1:0>    | 00x0 0x00                   |

| FB3h    | TMR3H                 |         | Holding R                                 | egister for the              | Most Significa   | ant Byte of the         | 16-bit TMR3 R       | egister                      |           | xxxx xxxx                   |

| FB2h    | TMR3L                 |         |                                           | Least Signif                 | icant Byte of th | ne 16-bit TMR3          | Register            |                              |           | xxxx xxxx                   |

| FB1h    | T3CON                 | TMR3C   | S<1:0>                                    | T3CKF                        | PS<1:0>          | T3SOSCEN                | T3SYNC              | T3RD16                       | TMR3ON    | 0000 0000                   |

| FB0h    | SPBRGH1               |         |                                           | EUSAR                        | T1 Baud Rate     | Generator, Hig          | h Byte              |                              |           | 0000 0000                   |

| FAFh    | SPBRG1                |         |                                           | EUSAR                        | T1 Baud Rate     | Generator, Lov          | w Byte              |                              |           | 0000 0000                   |

| FAEh    | RCREG1                |         |                                           |                              | T1 Receive Re    |                         |                     |                              |           | 0000 0000                   |

| FADh    | TXREG1                |         |                                           | EUSAR                        | T1 Transmit R    | egister                 |                     |                              |           | 0000 0000                   |

| FACh    | TXSTA1                | CSRC    | TX9                                       | TXEN                         | SYNC             | SENDB                   | BRGH                | TRMT                         | TX9D      | 0000 0010                   |

| FABh    | RCSTA1                | SPEN    | RX9                                       | SREN                         | CREN             | ADDEN                   | FERR                | OERR                         | RX9D      | 0000 000x                   |

| FAAh    | EEADRH <sup>(5)</sup> | _       | _                                         | _                            | _                | _                       | _                   |                              | R<9:8>    | 00                          |

| FA9h    | EEADR                 |         |                                           | 1                            | EEAD             | R<7:0>                  |                     |                              |           | 0000 0000                   |

| FA8h    | EEDATA                |         |                                           |                              | EEPROM Da        |                         |                     |                              |           | 0000 0000                   |

| FA7h    | EECON2                |         |                                           | EEPROM Co                    |                  | 2 (not a physic         | cal register)       |                              |           | 00                          |

| FA6h    | EECON1                | EEPGD   | CFGS                                      | _                            | FREE             | WRERR                   | WREN                | WR                           | RD        | xx-0 x000                   |

| FA5h    | IPR3                  | SSP2IP  | BCL2IP                                    | RC2IP                        | TX2IP            | CTMUIP                  | TMR5GIP             | TMR3GIP                      | TMR1GIP   | 0000 0000                   |

| FA4h    | PIR3                  | SSP2IF  | BCL2IF                                    | RC2IF                        | TX2IF            | CTMUIF                  | TMR5GIF             | TMR3GIF                      | TMR1GIF   | 0000 0000                   |

| FA3h    | PIE3                  | SSP2IE  | BCL2IE                                    | RC2IE                        | TX2IE            | CTMUIE                  | TMR5GIE             | TMR3GIE                      | TMR1GIE   | 0000 0000                   |

#### **TABLE 5-2:** REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES (CONTINUED)

Legend:  $\mathbf{x}$  = unknown,  $\mathbf{u}$  = unchanged, — = unimplemented,  $\mathbf{q}$  = value depends on condition

PIC18(L)F4XK22 devices only. Note 1:

PIC18(L)F2XK22 devices only. 2:

PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only. PIC18(L)F26K22 and PIC18(L)F46K22 devices only. 3:

4:

DS40001412G-page 80

| TABLE 5-2:       REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES (CONTINUED) |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | <u>Value on</u><br>POR, BOR |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------------|

| F3Ah    | ANSELC | ANSC7 | ANSC6 | ANSC5 | ANSC4 | ANSC3 | ANSC2 | _     |       | 1111 11                     |

| F39h    | ANSELB | _     | _     | ANSB5 | ANSB4 | ANSB3 | ANSB2 | ANSB1 | ANSB0 | 11 1111                     |

| F38h    | ANSELA |       | -     | ANSA5 |       | ANSA3 | ANSA2 | ANSA1 | ANSA0 | 1- 1111                     |

**Legend:** x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: PIC18(L)F4XK22 devices only.

2: PIC18(L)F2XK22 devices only.

3: PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

#### 12.1 Timer1/3/5 Operation

The Timer1/3/5 module is a 16-bit incrementing counter which is accessed through the TMRxH:TMRxL register pair. Writes to TMRxH or TMRxL directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1/3/5 is enabled by configuring the TMRxON and TMRxGE bits in the TxCON and TxGCON registers, respectively. Table 12-1 displays the Timer1/3/5 enable selections.

## TABLE 12-1:TIMER1/3/5 ENABLESELECTIONS

| TMRXON | TMRxGE | Timer1/3/5<br>Operation |

|--------|--------|-------------------------|

| 0      | 0      | Off                     |

| 0      | 1      | Off                     |

| 1      | 0      | Always On               |

| 1      | 1      | Count Enabled           |

#### 12.2 Clock Source Selection

The TMRxCS<1:0> and TxSOSCEN bits of the TxCON register are used to select the clock source for Timer1/3/5. The dedicated Secondary Oscillator circuit can be used as the clock source for Timer1, Timer3 and Timer5, simultaneously. Any of the TxSOSCEN bits will enable the Secondary Oscillator circuit and select it as the clock source for that particular timer. Table 12-2 displays the clock source selections.

#### 12.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMRxH:TMRxL register pair will increment on multiples of Fosc as determined by the Timer1/3/5 prescaler.

When the Fosc internal clock source is selected, the Timer1/3/5 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1/3/5 value. To utilize the full resolution of Timer1/3/5, an asynchronous input signal must be used to gate the Timer1/3/5 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the TxG pin to Timer1/3/5 Gate

- C1 or C2 comparator input to Timer1/3/5 Gate

#### 12.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1/3/5 module may work as a timer or a counter.

When enabled to count, Timer1/3/5 is incremented on the rising edge of the external clock input of the TxCKI pin. This external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated secondary internal oscillator circuit.

| In Counter mode, a falling edge must be      |

|----------------------------------------------|

| registered by the counter prior to the first |

| incrementing rising edge after any one or    |

| more of the following conditions:            |

|                                              |

- Timer1/3/5 enabled after POR

- Write to TMRxH or TMRxL

- Timer1/3/5 is disabled

- Timer1/3/5 is disabled (TMRxON = 0) when TxCKI is high then Timer1/3/5 is enabled (TMRxON=1) when TxCKI is low.

| TMRxCS1 | TMRxCS0 | TxSOSCEN | Clock Source                    |

|---------|---------|----------|---------------------------------|

| 0       | 1       | х        | System Clock (FOSC)             |

| 0       | 0       | х        | Instruction Clock (Fosc/4)      |

| 1       | 0       | 0        | External Clocking on TxCKI Pin  |

| 1       | 0       | 1        | Osc.Circuit On SOSCI/SOSCO Pins |

#### TABLE 12-2: CLOCK SOURCE SELECTIONS

| FIGURE 12-7:           | TIMER1/3/5 GATE SING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LE-PULSE AND TOGGLE COMBINED MODE                   |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| TMRxGE                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGPOL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGSPM                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGTM                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGG <u>O/</u><br>DONE | <ul> <li>Set by software</li> <li>Counting enabled of the set of the</li></ul> | Cleared by hardware on falling edge of TxGVAL       |

| TxG_IN                 | rising edge of TxG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

| ТхСКІ                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGVAL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TIMER1/3/5             | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>N + 1</u> <u>N + 2</u> <u>N + 3</u> <u>N + 4</u> |

| TMRxGIF                | Cleared by software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Set by hardware on<br>falling edge of TxGVAL        |

#### 12.12 Peripheral Module Disable

When a peripheral module is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bits for Timer1 (TMR1MD), Timer3 (TMR3MD) and Timer5 (TMR5MD) are in the PMD0 Register. See Section 3.0 "Power-Managed Modes" for more information.

| R/W-0/u                                                                                                                                                                                                                                                             | R/W-0/u                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0/u                                                                   | R/W-0/u                          | R/W/HC-0/u                            | R-x/x           | R/W-0/u          | R/W-0/u    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------|---------------------------------------|-----------------|------------------|------------|--|

| TMRxGE                                                                                                                                                                                                                                                              | TxGPOL                                                                                                                                                                                                                                                                                                                                                                                            | TxGTM                                                                     | TxGSPM                           | TxGGO/DONE                            | TxGVAL          | TxGSS            | S<1:0>     |  |

| bit 7                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |                                  |                                       |                 |                  | bit 0      |  |

|                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |                                  |                                       |                 |                  |            |  |

| Legend:                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |                                  |                                       |                 |                  |            |  |

| R = Readable                                                                                                                                                                                                                                                        | bit                                                                                                                                                                                                                                                                                                                                                                                               | W = Writable                                                              | bit                              | U = Unimplemer                        |                 |                  |            |  |

| u = Bit is unch                                                                                                                                                                                                                                                     | nanged                                                                                                                                                                                                                                                                                                                                                                                            | x = Bit is unkr                                                           | nown                             | -n/n = Value at P                     | OR and BOR      | /Value at all ot | her Resets |  |

| '1' = Bit is set                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                   | '0' = Bit is clea                                                         | ared                             | HC = Bit is clear                     | ed by hardwa    | re               |            |  |

| bit 7 <b>TMRxGE:</b> Timer1/3/5 Gate Enable bit<br><u>If TMRxON = 0</u> :<br>This bit is ignored<br><u>If TMRxON = 1</u> :<br>1 = Timer1/3/5 counting is controlled by the Timer1/3/5 gate function<br>0 = Timer1/3/5 counts regardless of Timer1/3/5 gate function |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |                                  |                                       |                 |                  |            |  |

| bit 6                                                                                                                                                                                                                                                               | 1 = Timer1/3<br>0 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                      | /5 gate is activ                                                          | e-high (Timer1<br>e-low (Timer1/ | /3/5 counts when<br>3/5 counts when g |                 |                  |            |  |

| bit 5                                                                                                                                                                                                                                                               | 1 = Timer1/3<br>0 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                      | er1/3/5 Gate To<br>/5 Gate Toggle<br>/5 Gate Toggle<br>ate flip-flop togg | mode is enab                     | led<br>bled and toggle flip           | -flop is cleare | d                |            |  |

| bit 4                                                                                                                                                                                                                                                               | 1 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           | Pulse mode is                    | enabled and is co                     | ontrolling Time | r1/3/5 gate      |            |  |

| bit 3                                                                                                                                                                                                                                                               | <ul> <li>0 = Timer1/3/5 gate Single-Pulse mode is disabled</li> <li>TxGGO/DONE: Timer1/3/5 Gate Single-Pulse Acquisition Status bit</li> <li>1 = Timer1/3/5 gate single-pulse acquisition is ready, waiting for an edge</li> <li>0 = Timer1/3/5 gate single-pulse acquisition has completed or has not been started</li> <li>This bit is automatically cleared when TxGSPM is cleared.</li> </ul> |                                                                           |                                  |                                       |                 |                  |            |  |