Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 19x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k22-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| dress<br>F5Fh<br>F5Eh<br>F5Dh<br>F5Ch<br>F5Bh<br>F58h<br>F57h<br>F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F54h | Name<br>CCPR3H<br>CCPR3L<br>CCP3CON<br>PWM3CON<br>ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCPR4L<br>CCPR5H<br>CCPR5H<br>CCPR5L<br>CCP5CON |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| F5Eh<br>F5Dh<br>F5Ch<br>F5Bh<br>F58h<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F55h<br>F54h<br>F53h          | CCPR3L<br>CCP3CON<br>PWM3CON<br>ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                       |

| F5Dh<br>F5Ch<br>F5Bh<br>F5Ah<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F53h                          | CCP3CON<br>PWM3CON<br>ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                 |

| F5Ch<br>F5Bh<br>F5Ah<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F53h                                  | PWM3CON<br>ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                            |

| F5Bh<br>F5Ah<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F55h<br>F53h                                          | ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                                       |

| F5Ah<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F55h<br>F53h                                                  | PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                                                  |

| F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F53h                                                          | CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                                                              |

| F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F53h                                                                  | CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                                                                        |

| F57h<br>F56h<br>F55h<br>F54h<br>F53h                                                                          | CCP4CON<br>CCPR5H<br>CCPR5L                                                                                                                  |

| F56h<br>F55h<br>F54h<br>F53h                                                                                  | CCPR5H<br>CCPR5L                                                                                                                             |

| F55h<br>F54h<br>F53h                                                                                          | CCPR5L                                                                                                                                       |

| F54h<br>F53h                                                                                                  |                                                                                                                                              |

| F53h                                                                                                          | CCF5CON                                                                                                                                      |

|                                                                                                               | TMR4                                                                                                                                         |

| EEDh                                                                                                          | PR4                                                                                                                                          |

| F52h<br>F51h                                                                                                  | T4CON                                                                                                                                        |

|                                                                                                               | T4CON<br>TMR5H                                                                                                                               |

|                                                                                                               | TMR5L                                                                                                                                        |

|                                                                                                               | T5CON                                                                                                                                        |

|                                                                                                               | T5GCON                                                                                                                                       |

|                                                                                                               | TMR6                                                                                                                                         |

|                                                                                                               | PR6                                                                                                                                          |

|                                                                                                               | T6CON                                                                                                                                        |

|                                                                                                               | CCPTMRS0                                                                                                                                     |

|                                                                                                               | CCPTMRS1                                                                                                                                     |

|                                                                                                               | SRCON0                                                                                                                                       |

|                                                                                                               | SRCON1                                                                                                                                       |

|                                                                                                               | CTMUCONH                                                                                                                                     |

|                                                                                                               | CTMUCONL                                                                                                                                     |

|                                                                                                               | CTMUICON                                                                                                                                     |

|                                                                                                               | VREFCON0                                                                                                                                     |

|                                                                                                               | VREFCON1                                                                                                                                     |

| F40h                                                                                                          | VREFCON2                                                                                                                                     |

| F3Fh                                                                                                          | PMD0                                                                                                                                         |

| F3Eh                                                                                                          | PMD1                                                                                                                                         |

| F3Dh                                                                                                          | PMD2                                                                                                                                         |

| F3Ch                                                                                                          | ANSELE                                                                                                                                       |

| F3Bh                                                                                                          | ANSELD                                                                                                                                       |

| F3Ah                                                                                                          | ANSELC                                                                                                                                       |

| F39h                                                                                                          | ANSELB                                                                                                                                       |

| F38h                                                                                                          | ANSELA                                                                                                                                       |

|                                                                                                               | F3Fh<br>F3Eh<br>F3Dh<br>F3Ch<br>F3Bh<br>F3Ah<br>F39h                                                                                         |

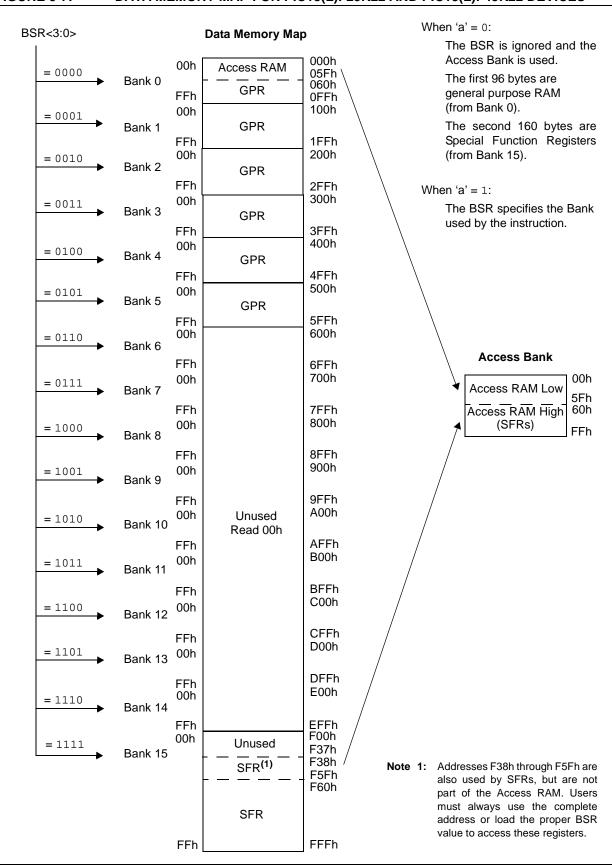

# TABLE 5-1: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F2X/4XK22 DEVICES

**Note 1:** This is not a physical register.

2: Unimplemented registers are read as '0'.

3: PIC18(L)F4XK22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

# TABLE 10-14: PORTE I/O SUMMARY

| Pin              | Function            | TRIS<br>Setting | ANSEL<br>Setting | Pin<br>Type | Buffer<br>Type | Description                                                                             |

|------------------|---------------------|-----------------|------------------|-------------|----------------|-----------------------------------------------------------------------------------------|

| RE0/P3A/CCP3/AN5 | RE0                 | 0               | 0                | 0           | DIG            | LATE<0> data output; not affected by analog input.                                      |

|                  |                     | 1               | 0                | I           | ST             | PORTE<0> data input; disabled when analog input<br>enabled.                             |

|                  | P3A <sup>(1)</sup>  | 0               | 0                | 0           | DIG            | Enhanced CCP3 PWM output.                                                               |

|                  | CCP3 <sup>(1)</sup> | 0               | 0                | 0           | DIG            | Compare 3 output/PWM 3 output.                                                          |

|                  |                     | 1               | 0                | I           | ST             | Capture 3 input.                                                                        |

|                  | AN5                 | 1               | 1                | I           | AN             | Analog input 5.                                                                         |

| RE1/P3B/AN6      | RE1                 | 0               | 0                | 0           | DIG            | LATE<1> data output; not affected by analog input.                                      |

|                  |                     | 1               | 0                | I           | ST             | PORTE<1> data input; disabled when analog input<br>enabled.                             |

|                  | P3B                 | 0               | 0                | 0           | DIG            | Enhanced CCP3 PWM output.                                                               |

|                  | AN6                 | 1               | 1                | -           | AN             | Analog input 6.                                                                         |

| RE2/CCP5/AN7     | RE2                 | 0               | 0                | 0           | DIG            | LATE<2> data output; not affected by analog input.                                      |

|                  |                     | 1               | 0                | Ι           | ST             | PORTE<2> data input; disabled when analog input<br>enabled.                             |

|                  | CCP5                | 0               | 0                | 0           | DIG            | Compare 5 output/PWM 5 output.                                                          |

|                  |                     | 1               | 0                | -           | ST             | Capture 5 input.                                                                        |

|                  | AN7                 | 1               | 1                | -           | AN             | Analog input 7.                                                                         |

| RE3/VPP/MCLR     | RE3                 | _               | _                | Ι           | ST             | PORTE<3> data input; enabled when Configuration bit<br>MCLRE = 0.                       |

|                  | Vpp                 | _               | —                | Р           | AN             | Programming voltage input; always available                                             |

|                  | MCLR                | _               | _                | Ι           | ST             | Active-low Master Clear (device Reset) input; enabled when configuration bit MCLRE = 1. |

Legend:AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS =<br/>CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;  $I^2C$  = Schmitt Trigger input with  $I^2C$ .

**Note 1:** Alternate pin assignment for P3A/CCP3 when Configuration bit CCP3MX is clear.

| ECCP Mode            | PxM<1:0> | CCPx/PxA           | PxB                | PxC                | PxD                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

# TABLE 14-12: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

**Note 1:** PWM Steering enables outputs in Single mode.

### **FIGURE 14-6: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH** STATE)

| PxM<1:0>               | Signal        | 0 ◀ Pulse Width          | PRX+1                |

|------------------------|---------------|--------------------------|----------------------|

|                        |               | -                        | — Period →           |

| 00 (Single Output)     | PxA Modulated | <br>Delay <sup>(1)</sup> | Delaý <sup>(1)</sup> |

|                        | PxA Modulated |                          |                      |

| 10 (Half-Bridge)       | PxB Modulated | _ '<br>_ <u>'</u>        |                      |

|                        | PxA Active    |                          |                      |

| (Full-Bridge,          | PxB Inactive  |                          |                      |

| <sup>01</sup> Forward) | PxC Inactive  |                          |                      |

|                        | PxD Modulated |                          |                      |

|                        | PxA Inactive  |                          |                      |

| 11 (Full-Bridge,       | PxB Modulated |                          |                      |

| Reverse)               | PxC Active    |                          |                      |

|                        | PxD Inactive  |                          |                      |

Period = 4 \* Tosc \* (PRx + 1) \* (TMRx Prescale Value)

Pulse Width = Tosc \* (CCPRxL<7:0>:CCPxCON<5:4>) \* (TMRx Prescale Value)

Delay = 4 \* Tosc \* (PWMxCON<6:0>)

Note 1: Dead-band delay is programmed using the PWMxCON register (Section 14.4.5 "Programmable Dead-Band Delay Mode").

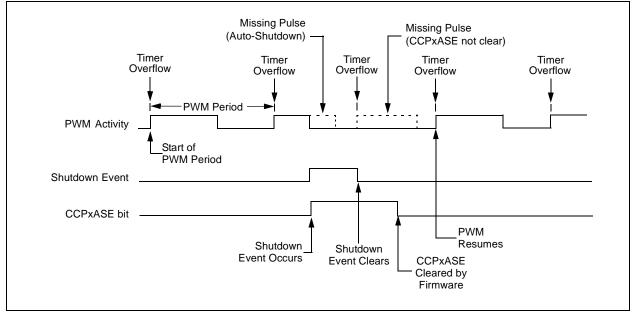

### 14.4.4 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PxRSEN bit in the PWMxCON register.

If auto-restart is enabled, the CCPxASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the CCPxASE bit will be cleared via hardware and normal operation will resume.

| FIGURE 15-9:                               | SPI N            | IODE W                        | /AVEFO                | RM (SL                | AVE MC                                                 | DE WIT                                           | HCKE                       | = 0)                                             |                        |            |                                       |

|--------------------------------------------|------------------|-------------------------------|-----------------------|-----------------------|--------------------------------------------------------|--------------------------------------------------|----------------------------|--------------------------------------------------|------------------------|------------|---------------------------------------|

|                                            | \<br>\           |                               |                       |                       |                                                        |                                                  |                            |                                                  |                        |            | <br><br>                              |

|                                            | 2<br>2<br>2<br>2 |                               |                       |                       |                                                        |                                                  | -<br>                      |                                                  |                        |            | ·<br>·<br>·<br>·                      |

| - 80%x<br>- (CKF = 0,<br>- CKF = 0)        | ·                |                               |                       |                       |                                                        |                                                  |                            |                                                  |                        |            | 3<br>                                 |

| 980908-00<br>SURPARATE<br>VISIRE           | •                |                               | 2<br>2<br>2<br>2<br>4 | 2<br>5<br>5<br>5<br>7 | 4<br>6<br>5<br>6<br>                                   | ·<br>·<br>·<br>· · · · · · · · · · · · · · · · · | 2<br>2<br>2<br>2<br>2<br>2 | ·<br>·<br>·<br>· · · · · · · · · · · · · · · · · | <pre>&lt;</pre>        |            | •<br>•<br>•<br>•<br>•                 |

| - \$5X0x<br>- \$50%                        |                  | 1. 232. 7<br>                 |                       |                       | × 1931 4.<br>                                          | X 88.3                                           | 7. 398. 2.                 | /                                                |                        | 68 0<br>Ma | · · · · · · · · · · · · · · · · · · · |

| incuá<br>Secoles                           |                  | - 1997<br>- 1995, 12<br>- 120 |                       |                       |                                                        | , ""/////<br>. 4, .                              |                            |                                                  |                        | ////<br>-3 | ·<br>·                                |

| - SSPXH                                    |                  |                               | 2                     |                       | (                                                      | ·                                                | 2                          |                                                  | 5                      |            |                                       |

| inierrup:<br>Pieg<br>SSPXSR to<br>SSPXSR)F | •                | ·<br>·<br>·                   | 2<br>2<br>2<br>2      | <br>2<br>2<br>2       | \$<br>5<br>5<br>5<br>• • • • • • • • • • • • • • • • • | ·<br>·<br>·<br>·                                 | 2                          |                                                  | 6<br>6 5<br>6 5<br>5 5 | :<br>//p.  |                                       |

| Varias Codiscon<br>detection activa        |                  |                               |                       |                       |                                                        |                                                  |                            |                                                  | . ,                    |            | ~~                                    |

# FIGURE 15-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

|                                     |                       |                       |                  |                       |                  |                       |                       | /                |       |                       |  |

|-------------------------------------|-----------------------|-----------------------|------------------|-----------------------|------------------|-----------------------|-----------------------|------------------|-------|-----------------------|--|

| SSx<br>Nex Optional                 |                       |                       |                  |                       |                  |                       |                       |                  |       | /                     |  |

| SCKx<br>(CKP = <u>0</u><br>CKE = 1) | ,<br>,<br>,<br>,<br>, |                       |                  |                       |                  |                       |                       |                  |       |                       |  |

| SCKx<br>(CKP = 1<br>CKE = 1)        | ;<br>;<br>;<br>;      |                       |                  |                       |                  |                       |                       |                  |       |                       |  |

| Write to<br>SSPxBUF                 | <br> <br> <br>        | 1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 | <br> <br> <br> <br>   | <br> <br> <br>   | <br> <br> <br> <br>   | 1<br>1<br>1<br>1      | <br> <br> <br>   |       |                       |  |

| SDOx                                | <u> </u>              | bit 7                 | bit 6            | bit 5                 | bit 4            | bit 3                 | bit 2                 | bit 1            | bit 0 |                       |  |

| SDIx ———                            |                       | bit 7                 | $\bigcirc$       |                       | $\sim$           |                       | $\rightarrow$         | $\sim$           | bit 0 | ,<br>,<br>,<br>,<br>, |  |

| Input<br>Sample                     | 1<br>1<br>1<br>1      | 1                     | 1                | 1                     | 1                | 1                     | 1                     | 1                | 1     |                       |  |

| SSPxIF<br>Interrupt<br>Flag         | 1<br>1<br>1<br>1<br>1 |                       |                  | ,<br>,<br>,<br>,<br>, | <br> <br> <br>   | ,<br>,<br>,<br>,<br>, | 1<br>1<br>1<br>1<br>1 | <br> <br> <br>   |       |                       |  |

| SSPxSR to<br>SSPxBUF                | 1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1 |                  | <br> <br> <br>        | 1<br>1<br>1<br>1 | <br> <br> <br>        | ,<br>,<br>,<br>,      | 1<br>1<br>1<br>1 |       | ×                     |  |

| Wille Collector<br>detection police | 1                     | •                     |                  |                       | •                |                       | •                     |                  |       |                       |  |

|                                     |                       |                       |                  |                       |                  |                       |                       |                  |       |                       |  |

# © 2010-2016 Microchip Technology Inc

DS40001412G-page 226

| Name     | Bit 7   | Bit 6   | Bit 5   | Bit 4       | Bit 3         | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on Page |

|----------|---------|---------|---------|-------------|---------------|---------|---------|---------|----------------------------|

| BAUDCON1 | ABDOVF  | RCIDL   | DTRXP   | CKTXP       | BRG16         | —       | WUE     | ABDEN   | 271                        |

| BAUDCON2 | ABDOVF  | RCIDL   | DTRXP   | CKTXP       | BRG16         | _       | WUE     | ABDEN   | 271                        |

| PMD0     | UART2MD | UART1MD | TMR6MD  | TMR5MD      | TMR4MD        | TMR3MD  | TMR2MD  | TMR1MD  | 52                         |

| RCSTA1   | SPEN    | RX9     | SREN    | CREN        | ADDEN         | FERR    | OERR    | RX9D    | 270                        |

| RCSTA2   | SPEN    | RX9     | SREN    | CREN        | ADDEN         | FERR    | OERR    | RX9D    | 270                        |

| SPBRG1   |         |         | EUSART1 | Baud Rate C | Generator, Lo | w Byte  |         |         | _                          |

| SPBRGH1  |         |         | EUSART1 | Baud Rate ( | Generator, Hi | gh Byte |         |         | _                          |

| SPBRG2   |         |         | EUSART2 | Baud Rate C | Generator, Lo | w Byte  |         |         | _                          |

| SPBRGH2  |         |         | EUSART2 | Baud Rate ( | Generator, Hi | gh Byte |         |         | _                          |

| PIR1     | _       | ADIF    | RC1IF   | TX1IF       | SSP1IF        | CCP1IF  | TMR2IF  | TMR1IF  | 112                        |

| PIR3     | SSP2IF  | BCL2IF  | RC2IF   | TX2IF       | CTMUIF        | TMR5GIF | TMR3GIF | TMR1GIF | 114                        |

| TXSTA1   | CSRC    | TX9     | TXEN    | SYNC        | SENDB         | BRGH    | TRMT    | TX9D    | 269                        |

| TXSTA2   | CSRC    | TX9     | TXEN    | SYNC        | SENDB         | BRGH    | TRMT    | TX9D    | 269                        |

### TABLE 16-4: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

Legend: — = unimplemented, read as '0'. Shaded bits are not used by the BRG.

## TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                |            |                              |                   | S          | YNC = 0, BRC                 | GH = 0, BRC    | <b>∋16 =</b> 0 |                              |                    |            |                              |

|--------|----------------|------------|------------------------------|-------------------|------------|------------------------------|----------------|----------------|------------------------------|--------------------|------------|------------------------------|

| BAUD   | Fos            | c = 64.00  | 0 MHz                        | Fosc = 18.432 MHz |            |                              | Fos            | c = 16.00      | 0 MHz                        | Fosc = 11.0592 MHz |            |                              |

| RATE   | Actual<br>Rate | %<br>Error | SPBRxG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRGx<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRGx<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRGx<br>value<br>(decimal) |

| 300    | —              | _          | _                            | —                 | _          | _                            | _              | _              | _                            | _                  | _          | _                            |

| 1200   | _              | _          | _                            | 1200              | 0.00       | 239                          | 1202           | 0.16           | 207                          | 1200               | 0.00       | 143                          |

| 2400   | _              | _          | _                            | 2400              | 0.00       | 119                          | 2404           | 0.16           | 103                          | 2400               | 0.00       | 71                           |

| 9600   | 9615           | 0.16       | 103                          | 9600              | 0.00       | 29                           | 9615           | 0.16           | 25                           | 9600               | 0.00       | 17                           |

| 10417  | 10417          | 0.00       | 95                           | 10286             | -1.26      | 27                           | 10417          | 0.00           | 23                           | 10165              | -2.42      | 16                           |

| 19.2k  | 19.23k         | 0.16       | 51                           | 19.20k            | 0.00       | 14                           | 19.23k         | 0.16           | 12                           | 19.20k             | 0.00       | 8                            |

| 57.6k  | 58.82k         | 2.12       | 16                           | 57.60k            | 0.00       | 7                            | _              | _              | _                            | 57.60k             | 0.00       | 2                            |

| 115.2k | 111.11k        | -3.55      | 8                            | —                 | —          | —                            | _              | —              | —                            |                    | —          | —                            |

|        |                |            |                              |                  | S          | YNC = 0, BRC                 | GH = 0, BRO    | <b>G16 =</b> 0    |                              |                |                  |                              |  |

|--------|----------------|------------|------------------------------|------------------|------------|------------------------------|----------------|-------------------|------------------------------|----------------|------------------|------------------------------|--|

| BAUD   | Fos            | SC = 8.00  | ) MHz                        | Fosc = 4.000 MHz |            |                              | Fos            | Fosc = 3.6864 MHz |                              |                | Fosc = 1.000 MHz |                              |  |

| RATE   | Actual<br>Rate | %<br>Error | SPBRGx<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRGx<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRGx<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRGx<br>value<br>(decimal) |  |

| 300    | —              | _          | _                            | 300              | 0.16       | 207                          | 300            | 0.00              | 191                          | 300            | 0.16             | 51                           |  |

| 1200   | 1202           | 0.16       | 103                          | 1202             | 0.16       | 51                           | 1200           | 0.00              | 47                           | 1202           | 0.16             | 12                           |  |

| 2400   | 2404           | 0.16       | 51                           | 2404             | 0.16       | 25                           | 2400           | 0.00              | 23                           | —              | _                | _                            |  |

| 9600   | 9615           | 0.16       | 12                           | _                | _          | _                            | 9600           | 0.00              | 5                            | _              | _                | _                            |  |

| 10417  | 10417          | 0.00       | 11                           | 10417            | 0.00       | 5                            | _              | _                 | _                            | _              | _                | _                            |  |

| 19.2k  | _              | _          | _                            | _                | _          | _                            | 19.20k         | 0.00              | 2                            | _              | _                | _                            |  |

| 57.6k  | —              | —          | —                            | —                | —          | —                            | 57.60k         | 0.00              | 0                            | —              | —                | —                            |  |

| 115.2k | —              | —          | _                            | —                | _          | _                            | —              | —                 | _                            | —              | _                | _                            |  |

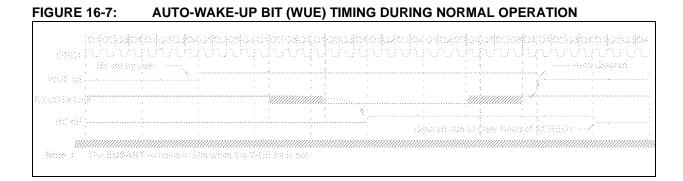

# FIGURE 16-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

|                 | [03[03[03]         | 404(0402    | 609030900                    | 03924                 | Q3                                     |                         | <u>koskosko</u> ( | 028090                                 | 603666                                | 3043  | osiozios  | 404,046           | 20303       |

|-----------------|--------------------|-------------|------------------------------|-----------------------|----------------------------------------|-------------------------|-------------------|----------------------------------------|---------------------------------------|-------|-----------|-------------------|-------------|

| COSX            | A JULIUN.<br>Beise |             | nunyunu<br>''''''            |                       |                                        |                         | nininin           | nunun<br>İ                             | Yunun                                 |       |           | AUQUA<br>Sectores | 2           |

| WEBE :          | ×.                 | :<br>       | میں ہے۔<br>رینینی کاریک<br>چ | ······<br>·<br>·<br>· |                                        | • • • • • • • • • • • • |                   | ······································ | · · · · · · · · · · · · · · · · · · · |       |           | :                 | ,<br>,<br>, |

| RIGERY R<br>RGS | uni<br>Mi          | -<br>-<br>- | ;                            | ,<br>,<br>,           |                                        | N<br>Ž                  |                   |                                        |                                       |       | 525-5<br> |                   |             |

|                 | ,                  | States Co   | voreand Exerc                | uteri 🏅               | Steep Hods                             |                         | Cierre            | වේ රිස්ම ස                             | e (Fear Re:                           | 94 OÚ | ROREGA    | 2                 | ,           |

| 26660-31        |                    |             |                              |                       | arrieg deta, itea<br>et die presanca d |                         |                   | x dhe Wi                               | .48 ost cart                          | 66066 | wwie to   | ta e opera        | e signa is  |

| 2               | 1356 8933          | alle cocco  | ins in the wol               | la dha MARE d         | 28.26 5682                             |                         |                   |                                        |                                       |       |           |                   |             |

| R/W-0        | R/W-0                                               | R/W-0                                                                                                     | R/W-0                                        | R/W-0                             | R/W-0           | R/W-0           | R/W-0  |

|--------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------|-----------------|-----------------|--------|

|              |                                                     | ITRIM                                                                                                     | <5:0>                                        |                                   |                 | IRNG            | i<1:0> |

| bit 7        |                                                     |                                                                                                           |                                              |                                   |                 |                 | bit (  |

| Legend:      |                                                     |                                                                                                           |                                              |                                   |                 |                 |        |

| R = Readal   | ble bit                                             | W = Writable I                                                                                            | bit                                          | U = Unimplen                      | nented bit, rea | d as '0'        |        |

| -n = Value a | at POR                                              | '1' = Bit is set                                                                                          |                                              | '0' = Bit is clea                 | ared            | x = Bit is unkr | nown   |

| bit 7-2      | 011111 = M<br>011110                                | Current Source Maximum positive Minimum positive Nominal current o Minimum negative                       | change from<br>change from<br>utput specifie | nominal current<br>d by IRNG<1:0> |                 |                 |        |

| bit 1-0      | IRNG<1:0><br>11 = 100 ×<br>10 = 10 × E<br>01 = Base | Maximum negative<br>Current Source<br>Base current<br>Base current<br>current level<br>nt source disabled | Range Selec                                  |                                   |                 |                 |        |

### REGISTER 19-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

| Name     | Bit 7      | Bit 6  | Bit 5    | Bit 4   | Bit 3  | Bit 2     | Bit 1             | Bit 0   | Reset<br>Values<br>on Page |

|----------|------------|--------|----------|---------|--------|-----------|-------------------|---------|----------------------------|

| CTMUCONH | CTMUEN     | _      | CTMUSIDL | TGEN    | EDGEN  | EDGSEQEN  | IDISSEN           | CTTRIG  | 323                        |

| CTMUCONL | EDG2POL    | EDG2SE | L<1:0>   | EDG1POL | EDG1S  | EL<1:0>   | EDG2STAT EDG1STAT |         | 324                        |

| CTMUICON | ITRIM<5:0> |        |          |         |        | IRNG<1:0> |                   | 325     |                            |

| IPR3     | SSP2IP     | BCL2IP | RC2IP    | TX2IP   | CTMUIP | TMR5GIP   | TMR3GIP           | TMR1GIP | 123                        |

| PIE3     | SSP2IE     | BCL2IE | RC2IE    | TX2IE   | CTMUIE | TMR5GIE   | TMR3GIE           | TMR1GIE | 119                        |

| PIR3     | SSP2IF     | BCL2IF | RC2IF    | TX2IF   | CTMUIF | TMR5GIF   | TMR3GIF           | TMR1GIF | 114                        |

| PMD2     | —          |        | —        | -       | CTMUMD | CMP2MD    | CMP1MD            | ADCMD   | 54                         |

**Legend:** — = unimplemented, read as '0'. Shaded bits are not used during CTMU operation.

| ADDWF                                                          | ADD W to Indexed<br>(Indexed Literal Offset mode)                 |                                                                                                                                                                                                                          |      |                       |  |  |  |  |

|----------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|--|--|--|--|

| Syntax:                                                        | ADDWF                                                             | [k] {,d}                                                                                                                                                                                                                 |      |                       |  |  |  |  |

| Operands:                                                      | $\begin{array}{l} 0 \leq k \leq 95 \\ d  \in  [0,1] \end{array}$  |                                                                                                                                                                                                                          |      |                       |  |  |  |  |

| Operation:                                                     | (W) + ((FSF                                                       | $(2) + k) \rightarrow ($                                                                                                                                                                                                 | dest |                       |  |  |  |  |

| Status Affected:                                               | N, OV, C, D                                                       | C, Z                                                                                                                                                                                                                     |      |                       |  |  |  |  |

| Encoding:                                                      | 0010                                                              | 01d0 1                                                                                                                                                                                                                   | kkkk | kkkk                  |  |  |  |  |

| Description:                                                   | contents of<br>FSR2, offse<br>If 'd' is '0', th<br>is '1', the re | The contents of W are added to the contents of the register indicated by FSR2, offset by the value 'k'.<br>If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f' (default). |      |                       |  |  |  |  |

| Words:                                                         | 1                                                                 |                                                                                                                                                                                                                          |      |                       |  |  |  |  |

| Cycles:                                                        | 1                                                                 |                                                                                                                                                                                                                          |      |                       |  |  |  |  |

| Q Cycle Activity:                                              |                                                                   |                                                                                                                                                                                                                          |      |                       |  |  |  |  |

| Q1                                                             | Q2                                                                | Q3                                                                                                                                                                                                                       |      | Q4                    |  |  |  |  |

| Decode                                                         | Read 'k'                                                          | Process<br>Data                                                                                                                                                                                                          |      | Vrite to<br>stination |  |  |  |  |

| Example:                                                       | ADDWF [                                                           | OFST],                                                                                                                                                                                                                   | 0    |                       |  |  |  |  |

| Before Instructi                                               | ion                                                               |                                                                                                                                                                                                                          |      |                       |  |  |  |  |

| W<br>OFST<br>FSR2<br>Contents<br>of 0A2Ch<br>After Instruction | =<br>=<br>=<br>1                                                  | 17h<br>2Ch<br>0A00h<br>20h                                                                                                                                                                                               |      |                       |  |  |  |  |

| W<br>Contents<br>of 0A2Ch                                      | =                                                                 | 37h<br>20h                                                                                                                                                                                                               |      |                       |  |  |  |  |

| BSF          | :                              | Bit Set Indexed<br>(Indexed Literal Offset mode)                   |                                                                             |      |                        |  |  |  |  |

|--------------|--------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------|------|------------------------|--|--|--|--|

| Synt         | ax:                            | BSF [k], k                                                         | )                                                                           |      |                        |  |  |  |  |

| Operands:    |                                | $\begin{array}{l} 0 \leq f \leq 95 \\ 0 \leq b \leq 7 \end{array}$ | 0 = 1 = 00                                                                  |      |                        |  |  |  |  |

| Oper         | ration:                        | $1 \rightarrow ((FSR)$                                             | 2) + k) <b< td=""><td>&gt;</td><td></td></b<>                               | >    |                        |  |  |  |  |

| Statu        | is Affected:                   | None                                                               |                                                                             |      |                        |  |  |  |  |

| Enco         | oding:                         | 1000                                                               | bbb0                                                                        | kkkk | kkkk                   |  |  |  |  |

| Description: |                                |                                                                    | Bit 'b' of the register indicated by FSR2, offset by the value 'k', is set. |      |                        |  |  |  |  |

| Word         | ds:                            | 1                                                                  |                                                                             |      |                        |  |  |  |  |

| Cycle        | es:                            | 1                                                                  |                                                                             |      |                        |  |  |  |  |

| QC           | ycle Activity:                 |                                                                    |                                                                             |      |                        |  |  |  |  |

|              | Q1                             | Q2                                                                 | Q3                                                                          |      | Q4                     |  |  |  |  |

|              | Decode                         | Read<br>register 'f'                                               | Proce<br>Data                                                               |      | Write to<br>estination |  |  |  |  |

|              |                                | U                                                                  |                                                                             | ~ ~  | Sunation               |  |  |  |  |

| <u>Exar</u>  | <u>nple:</u><br>Before Instruc |                                                                    | [FLAG_O                                                                     |      |                        |  |  |  |  |

| SET          | F                                                                                                   | •••              | Set Indexed<br>(Indexed Literal Offset mode) |                          |     |   |                    |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------|------------------|----------------------------------------------|--------------------------|-----|---|--------------------|--|--|--|

| Syntax:      |                                                                                                     | SETF             | SETF [k]                                     |                          |     |   |                    |  |  |  |

| Oper         | ands:                                                                                               | $0 \leq k \leq$  | 95                                           |                          |     |   |                    |  |  |  |

| Oper         | ation:                                                                                              | $FFh \to$        | ((F                                          | SR2) + k)                | )   |   |                    |  |  |  |

| Statu        | s Affected:                                                                                         | None             |                                              |                          |     |   |                    |  |  |  |

| Enco         | ding:                                                                                               | 0110             | )                                            | 1000                     | kkk | k | kkkk               |  |  |  |

| Description: |                                                                                                     |                  |                                              | nts of the<br>et by 'k', | •   |   | licated by<br>FFh. |  |  |  |

| Words:       |                                                                                                     | 1                |                                              |                          |     |   |                    |  |  |  |

| Cycle        | es:                                                                                                 | 1                |                                              |                          |     |   |                    |  |  |  |

| QC           | ycle Activity:                                                                                      |                  |                                              |                          |     |   |                    |  |  |  |

|              | Q1                                                                                                  | Q2               |                                              | Q                        | 3   |   | Q4                 |  |  |  |

|              | Decode                                                                                              | Read 'I          | ٢'                                           | Proce<br>Dat             |     | r | Write<br>egister   |  |  |  |

| <u>Exan</u>  | nple:                                                                                               | SETF             |                                              | [OFST]                   |     |   |                    |  |  |  |

|              | Before Instruct<br>OFST<br>FSR2<br>Contents<br>of 0A2Ch<br>After Instructio<br>Contents<br>of 0A2Ch | =<br>=<br>=<br>n | 0/                                           | Ch<br>AOOh<br>Dh<br>Fh   |     |   |                    |  |  |  |

# 26.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 26.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

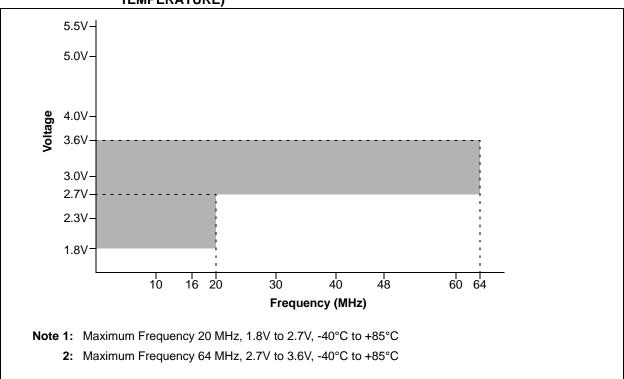

# FIGURE 27-1: PIC18LF2X/4XK22 FAMILY VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL TEMPERATURE)

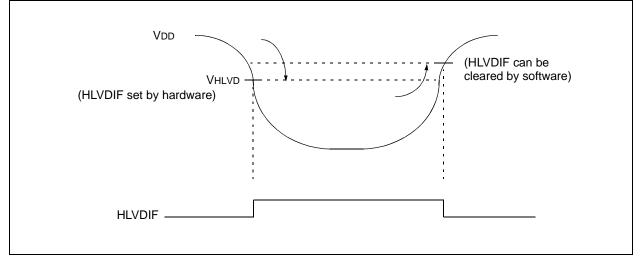

# TABLE 27-5: HIGH/LOW-VOLTAGE DETECT CHARACTERISTICS

Г

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |        |                        |            |      |          |      |       |            |

|--------------------------------------------------------------------------------------------------------------------------|--------|------------------------|------------|------|----------|------|-------|------------|

| Param<br>No.                                                                                                             | Symbol | Characteristic         | HLVDL<3:0> | Min  | Тур†     | Max  | Units | Conditions |

|                                                                                                                          |        | HLVD Voltage on VDD    | 0000       | 1.69 | 1.84     | 1.99 | V     |            |

|                                                                                                                          |        | Transition High-to-Low | 0001       | 1.92 | 2.07     | 2.22 | V     |            |

|                                                                                                                          |        |                        | 0010       | 2.08 | 2.28     | 2.48 | V     |            |

|                                                                                                                          |        |                        | 0011       | 2.24 | 2.44     | 2.64 | V     |            |

|                                                                                                                          |        |                        | 0100       | 2.34 | 2.54     | 2.74 | V     |            |

|                                                                                                                          |        |                        | 0101       | 2.54 | 2.74     | 2.94 | V     |            |

|                                                                                                                          |        |                        | 0110       | 2.62 | 2.87     | 3.12 | V     |            |

|                                                                                                                          |        |                        | 0111       | 2.76 | 3.01     | 3.26 | V     |            |

|                                                                                                                          |        |                        | 1000       | 3.00 | 3.30     | 3.60 | V     |            |

|                                                                                                                          |        |                        | 1001       | 3.18 | 3.48     | 3.78 | V     |            |

|                                                                                                                          |        |                        | 1010       | 3.44 | 3.69     | 3.94 | V     |            |

|                                                                                                                          |        |                        | 1011       | 3.66 | 3.91     | 4.16 | V     |            |

|                                                                                                                          |        |                        | 1100       | 3.90 | 4.15     | 4.40 | V     |            |

|                                                                                                                          |        |                        | 1101       | 4.11 | 4.41     | 4.71 | V     |            |

|                                                                                                                          |        |                        | 1110       | 4.39 | 4.74     | 5.09 | V     |            |

|                                                                                                                          |        |                        | 1111       | V(H  | ILVDIN p | oin) | v     |            |

† Production tested at TAMB = 25°C. Specifications over temperature limits ensured by characterization.

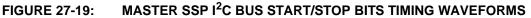

| Param.<br>No. | Symbol  | Characte        | eristic      | Min  | Max | Units | Conditions                   |  |

|---------------|---------|-----------------|--------------|------|-----|-------|------------------------------|--|

| 90            | TSU:STA | Start Condition | 100 kHz mode | 4700 | _   | ns    | Only relevant for Repeated   |  |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       | Start condition              |  |

| 91            | THD:STA | Start Condition | 100 kHz mode | 4000 | _   | ns    | After this period, the first |  |

|               |         | Hold Time       | 400 kHz mode | 600  | _   |       | clock pulse is generated     |  |

| 92            | Tsu:sto | Stop Condition  | 100 kHz mode | 4700 | _   | ns    |                              |  |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       |                              |  |

| 93            | THD:STO | Stop Condition  | 100 kHz mode | 4000 | _   | ns    |                              |  |

|               |         | Hold Time       | 400 kHz mode | 600  |     | 1     |                              |  |

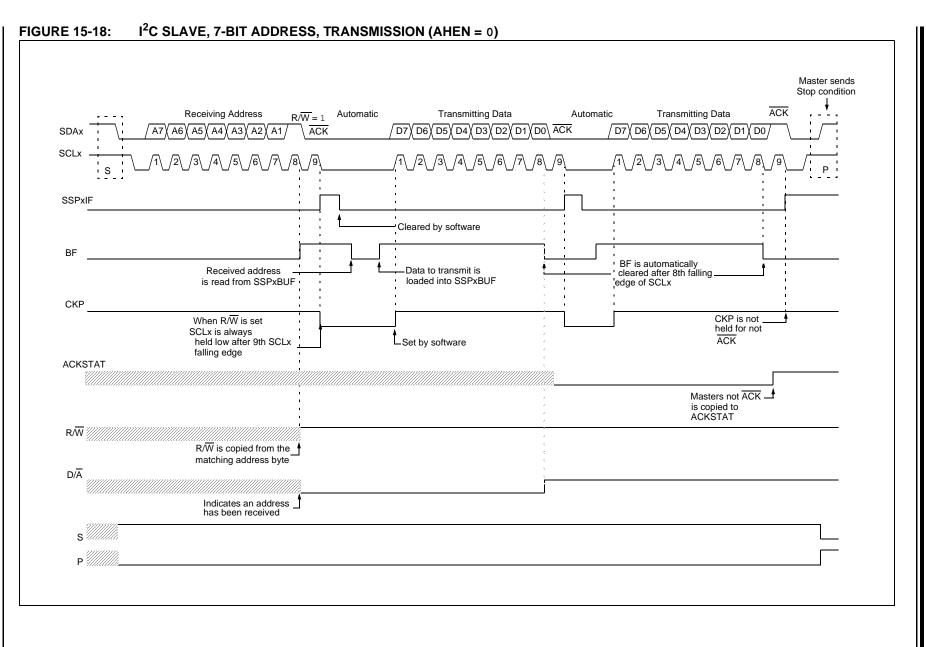

# TABLE 27-15: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

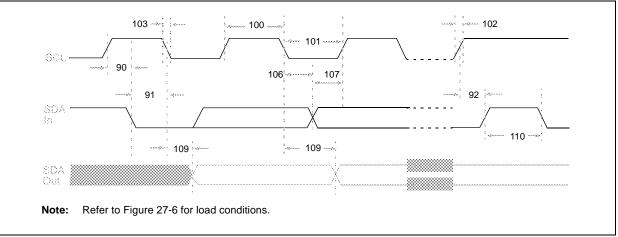

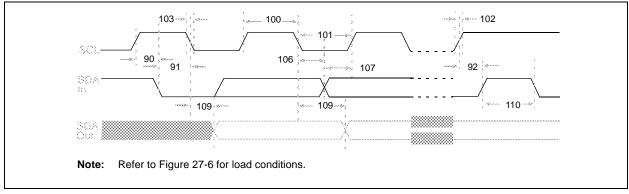

# FIGURE 27-18: I<sup>2</sup>C BUS DATA TIMING

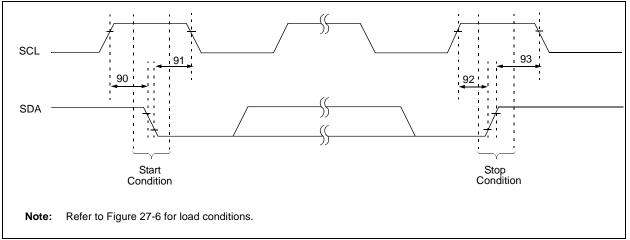

| Param.<br>No. | Symbol  | I Characteristic |                           | Min              | Max | Units | Conditions                  |

|---------------|---------|------------------|---------------------------|------------------|-----|-------|-----------------------------|

| 90            | TSU:STA | Start Condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    | Only relevant for           |

|               |         | Setup Time       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _   |       | Repeated Start<br>condition |

|               |         |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _   |       | condition                   |

| 91            | THD:STA | Start Condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    | After this period, the      |

|               |         | Hold Time        | 400 kHz mode              | 2(Tosc)(BRG + 1) | _   |       | first clock pulse is        |

|               |         |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _   |       | generated                   |

| 92            | TSU:STO | Stop Condition   | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    |                             |

|               |         | Setup Time       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _   |       |                             |

|               |         |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _   |       |                             |

| 93            | THD:STO | Stop Condition   | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    |                             |

|               |         | Hold Time        | 400 kHz mode              | 2(Tosc)(BRG + 1) | —   |       |                             |

|               |         |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _   |       |                             |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins.

# FIGURE 27-20: MASTER SSP I<sup>2</sup>C BUS DATA TIMING

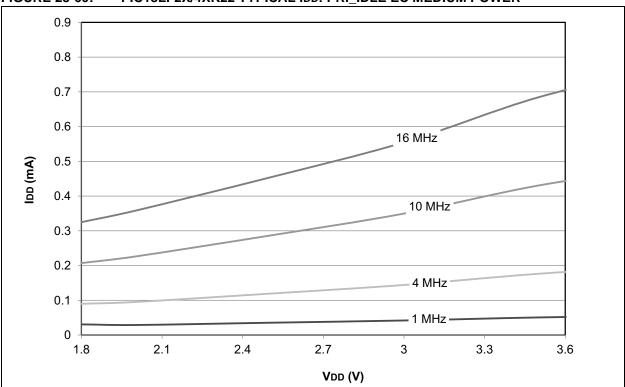

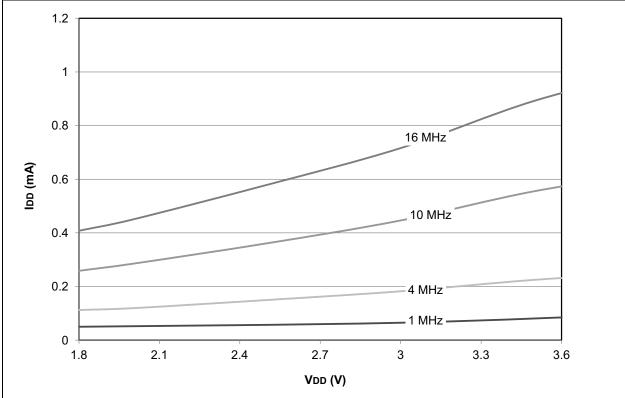

FIGURE 28-60: PIC18LF2X/4XK22 TYPICAL IDD: PRI\_IDLE EC MEDIUM POWER

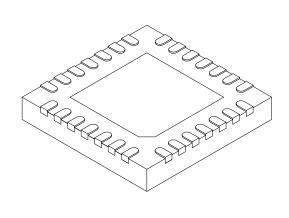

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | М    | ILLIMETERS | 6    |  |

|-------------------------|--------|------|------------|------|--|

| Dimension               | Limits | MIN  | NOM        | MAX  |  |

| Number of Pins          | Z      |      | 28         |      |  |

| Pitch                   | е      |      | 0.65 BSC   |      |  |

| Overall Height          | A      | 0.80 | 0.90       | 1.00 |  |

| Standoff                | A1     | 0.00 | 0.02       | 0.05 |  |

| Terminal Thickness      | A3     |      | 0.20 REF   |      |  |

| Overall Width           | Ш      |      | 6.00 BSC   |      |  |

| Exposed Pad Width       | E2     | 3.65 | 3.70       | 4.20 |  |

| Overall Length          | D      |      | 6.00 BSC   |      |  |

| Exposed Pad Length      | D2     | 3.65 | 3.70       | 4.20 |  |

| Terminal Width          | b      | 0.23 | 0.30       | 0.35 |  |

| Terminal Length         | L      | 0.50 | 0.55       | 0.70 |  |

| Terminal-to-Exposed Pad | K      | 0.20 | -          | -    |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2

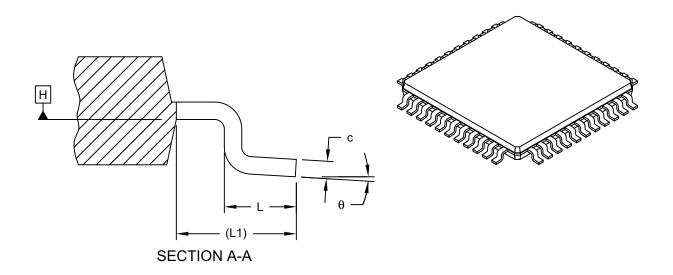

# 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units MILLIMETERS |          |           |      |  |  |

|--------------------------|-------------------|----------|-----------|------|--|--|

| Dimension                | Limits            | MIN      | NOM       | MAX  |  |  |

| Number of Leads          | N                 |          | 44        |      |  |  |

| Lead Pitch               | е                 |          | 0.80 BSC  |      |  |  |

| Overall Height           | A                 | -        | -         | 1.20 |  |  |

| Standoff                 | A1                | 0.05     | -         | 0.15 |  |  |

| Molded Package Thickness | A2                | 0.95     | 1.00      | 1.05 |  |  |

| Overall Width            | E                 |          | 12.00 BSC |      |  |  |

| Molded Package Width     | E1                |          | 10.00 BSC |      |  |  |

| Overall Length           | D                 |          | 12.00 BSC |      |  |  |

| Molded Package Length    | D1                |          | 10.00 BSC |      |  |  |

| Lead Width               | b                 | 0.30     | 0.37      | 0.45 |  |  |

| Lead Thickness           | С                 | 0.09     | -         | 0.20 |  |  |

| Lead Length              | L                 | 0.45     | 0.60      | 0.75 |  |  |

| Footprint                | L1                | 1.00 REF |           |      |  |  |

| Foot Angle               | θ                 | 0°       | 3.5°      | 7°   |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Exact shape of each corner is optional.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2