Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

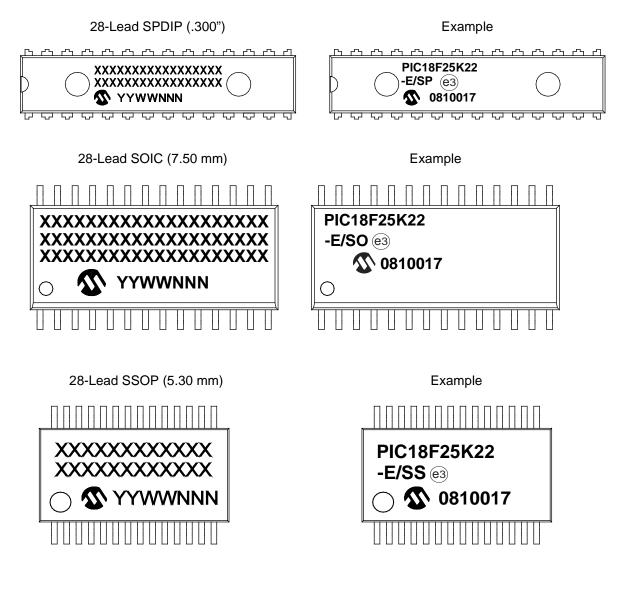

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 19x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k22-e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 2: | PIC18(L)F2XK22 PIN SUMMARY |

|----------|----------------------------|

|----------|----------------------------|

| IAD                       |              |     |        | FZANZZ     | 1 114 50 |          |                 |                                                  |         |              |                                               |            |         |              |

|---------------------------|--------------|-----|--------|------------|----------|----------|-----------------|--------------------------------------------------|---------|--------------|-----------------------------------------------|------------|---------|--------------|

| 28-SSOP, SOIC<br>28-SPDIP | 28-QFN, UQFN | 0/1 | Analog | Comparator | СТМИ     | SR Latch | Reference       | (E)CCP                                           | EUSART  | MSSP         | Timers                                        | Interrupts | dn-lluq | Basic        |

| 2                         | 27           | RA0 | AN0    | C12IN0-    |          |          |                 |                                                  |         |              |                                               |            |         |              |

| 3                         | 28           | RA1 | AN1    | C12IN1-    |          |          |                 |                                                  |         |              |                                               |            |         |              |

| 4                         | 1            | RA2 | AN2    | C2IN+      |          |          | VREF-<br>DACOUT |                                                  |         |              |                                               |            |         |              |

| 5                         | 2            | RA3 | AN3    | C1IN+      |          |          | VREF+           |                                                  |         |              |                                               |            |         |              |

| 6                         | 3            | RA4 |        | C1OUT      |          | SRQ      |                 | CCP5                                             |         |              | TOCKI                                         |            |         |              |

| 7                         | 4            | RA5 | AN4    | C2OUT      |          | SRNQ     | HLVDIN          |                                                  |         | SS1          |                                               |            |         |              |

| 10                        | 7            | RA6 |        |            |          |          |                 |                                                  |         |              |                                               |            |         | OSC2<br>CLKO |

| 9                         | 6            | RA7 |        |            |          |          |                 |                                                  |         |              |                                               |            |         | OSC1<br>CLKI |

| 21                        | 18           | RB0 | AN12   |            |          | SRI      |                 | CCP4<br>FLT0                                     |         | SS2          |                                               | INT0       | Y       |              |

| 22                        | 19           | RB1 | AN10   | C12IN3-    |          |          |                 | P1C                                              |         | SCK2<br>SCL2 |                                               | INT1       | Y       |              |

| 23                        | 20           | RB2 | AN8    |            | CTED1    |          |                 | P1B                                              |         | SDI2<br>SDA2 |                                               | INT2       | Y       |              |

| 24                        | 21           | RB3 | AN9    | C12IN2-    | CTED2    |          |                 | CCP2<br>P2A <sup>(1)</sup>                       |         | SDO2         |                                               |            | Y       |              |

| 25                        | 22           | RB4 | AN11   |            |          |          |                 | P1D                                              |         |              | T5G                                           | IOC        | Υ       |              |

| 26                        | 23           | RB5 | AN13   |            |          |          |                 | CCP3<br>P3A <sup>(4)</sup><br>P2B <sup>(3)</sup> |         |              | T1G<br>T3CKI <sup>(2)</sup>                   | IOC        | Y       |              |

| 27                        | 24           | RB6 |        |            |          |          |                 |                                                  | TX2/CK2 |              |                                               | IOC        | Y       | PGC          |

| 28                        | 25           | RB7 |        |            |          |          |                 |                                                  | RX2/DT2 |              |                                               | IOC        | Y       | PGD          |

| 11                        | 8            | RC0 |        |            |          |          |                 | P2B <sup>(3)</sup>                               |         |              | SOSCO<br>T1CKI<br>T3CKI <sup>(2)</sup><br>T3G |            |         |              |

| 12                        | 9            | RC1 |        |            |          |          |                 | CCP2<br>P2A <sup>(1)</sup>                       |         |              | SOSCI                                         |            |         |              |

| 13                        | 10           | RC2 | AN14   |            | CTPLS    |          |                 | CCP1<br>P1A                                      |         |              | T5CKI                                         |            |         |              |

| 14                        | 11           | RC3 | AN15   |            |          |          |                 |                                                  |         | SCK1<br>SCL1 |                                               |            |         |              |

| 15                        | 12           | RC4 | AN16   |            |          |          |                 |                                                  |         | SDI1<br>SDA1 |                                               |            |         |              |

| 16                        | 13           | RC5 | AN17   |            |          |          |                 |                                                  |         | SDO1         |                                               |            |         |              |

| 17                        | 14           | RC6 | AN18   |            |          |          |                 | CCP3<br>P3A <sup>(4)</sup>                       | TX1/CK1 |              |                                               |            |         |              |

| 18                        | 15           | RC7 | AN19   |            |          |          |                 | P3B                                              | RX1/DT1 |              |                                               |            |         |              |

| 1                         | 26           | RE3 |        |            |          |          |                 |                                                  |         |              |                                               |            |         | MCLR<br>VPP  |

| 8, 19<br>19               | 5, 16<br>16  | Vss |        |            |          |          |                 |                                                  |         |              |                                               |            |         | Vss          |

| 20                        | 17           | Vdd |        |            |          |          |                 |                                                  |         |              |                                               |            |         | Vdd          |

|                           |              |     |        |            |          |          |                 |                                                  |         |              |                                               |            |         |              |

CCP2/P2A multiplexed in fuses.

T3CKI multiplexed in fuses.

P2B multiplexed in fuses.

CCP3/P3A multiplexed in fuses. Note 1:

| Pin Nu        | ımber        |                              | <b>D</b> '  | Buffer      |                                                                                                                 |  |  |

|---------------|--------------|------------------------------|-------------|-------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| PDIP,<br>SOIC | QFN,<br>UQFN | Pin Name                     | Pin<br>Type | Description |                                                                                                                 |  |  |

| 2             | 27           | RA0/C12IN0-/AN0              |             |             |                                                                                                                 |  |  |

|               |              | RA0                          | I/O         | TTL         | Digital I/O.                                                                                                    |  |  |

|               |              | C12IN0-                      | Т           | Analog      | Comparators C1 and C2 inverting input.                                                                          |  |  |

|               |              | ANO                          | I           | Analog      | Analog input 0.                                                                                                 |  |  |

| 3             | 28           | RA1/C12IN1-/AN1              |             |             |                                                                                                                 |  |  |

|               |              | RA1                          | I/O         | TTL         | Digital I/O.                                                                                                    |  |  |

|               |              | C12IN1-                      | I           | Analog      | Comparators C1 and C2 inverting input.                                                                          |  |  |

|               |              | AN1                          | Ι           | Analog      | Analog input 1.                                                                                                 |  |  |

| 4             | 1            | RA2/C2IN+/AN2/DACOUT/VREF-   |             |             |                                                                                                                 |  |  |

|               |              | RA2                          | I/O         | TTL         | Digital I/O.                                                                                                    |  |  |

|               |              | C2IN+                        | I           | Analog      | Comparator C2 non-inverting input.                                                                              |  |  |

|               |              | AN2                          | I           | Analog      | Analog input 2.                                                                                                 |  |  |

|               |              | DACOUT                       | 0           | Analog      | DAC Reference output.                                                                                           |  |  |

|               |              | VREF-                        | Ι           | Analog      | A/D reference voltage (low) input.                                                                              |  |  |

| 5             | 2            | RA3/C1IN+/AN3/VREF+          |             |             |                                                                                                                 |  |  |

|               |              | RA3                          | I/O         | TTL         | Digital I/O.                                                                                                    |  |  |

|               |              | C1IN+                        | I           | Analog      | Comparator C1 non-inverting input.                                                                              |  |  |

|               |              | AN3                          | I           | Analog      | Analog input 3.                                                                                                 |  |  |

|               |              | VREF+                        | Ι           | Analog      | A/D reference voltage (high) input.                                                                             |  |  |

| 6             | 3            | RA4/CCP5/C1OUT/SRQ/T0CKI     |             |             |                                                                                                                 |  |  |

|               |              | RA4                          | I/O         | ST          | Digital I/O.                                                                                                    |  |  |

|               |              | CCP5                         | I/O         | ST          | Capture 5 input/Compare 5 output/PWM 5 output.                                                                  |  |  |

|               |              | C1OUT                        | 0           | CMOS        | Comparator C1 output.                                                                                           |  |  |

|               |              | SRQ                          | 0           | TTL         | SR latch Q output.                                                                                              |  |  |

|               |              | ТОСКІ                        | Ι           | ST          | Timer0 external clock input.                                                                                    |  |  |

| 7             | 4            | RA5/C2OUT/SRNQ/SS1/HLVDIN/AN | 14          |             |                                                                                                                 |  |  |

|               |              | RA5                          | I/O         | TTL         | Digital I/O.                                                                                                    |  |  |

|               |              | C2OUT                        | 0           | CMOS        | Comparator C2 output.                                                                                           |  |  |

|               |              | SRNQ                         | 0           | TTL         | SR latch $\overline{Q}$ output.                                                                                 |  |  |

|               |              | SS1                          | Т           | TTL         | SPI slave select input (MSSP).                                                                                  |  |  |

|               |              | HLVDIN                       | I           | Analog      | High/Low-Voltage Detect input.                                                                                  |  |  |

|               |              | AN4                          | Ι           | Analog      | Analog input 4.                                                                                                 |  |  |

| 10            | 7            | RA6/CLKO/OSC2                |             |             |                                                                                                                 |  |  |

|               |              | RA6                          | I/O         | TTL         | Digital I/O.                                                                                                    |  |  |

|               |              | CLKO                         | 0           |             | In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate. |  |  |

|               |              | OSC2                         | 0           |             | Oscillator crystal output. Connects to crystal or resonato<br>in Crystal Oscillator mode.                       |  |  |

| TABLE 1-2: |                                        |

|------------|----------------------------------------|

| IABLE 1-2: | PIC18(L)F2XK22 PINOUT I/O DESCRIPTIONS |

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

| Address | Name     | Bit 7                                                                                                    | Bit 6                                                                                                                                                                                                         | Bit 5           | Bit 4           | Bit 3           | Bit 2           | Bit 1           | Bit 0       | <u>Value c</u><br>POR, BO |     |

|---------|----------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------|---------------------------|-----|

| FFFh    | TOSU     | —                                                                                                        | —                                                                                                                                                                                                             | —               |                 | Top-of-Stack,   | Upper Byte (T   | OS<20:16>)      |             | 0 00                      | 000 |

| FFEh    | TOSH     |                                                                                                          |                                                                                                                                                                                                               | Тор             | -of-Stack, High | Byte (TOS<15    | 5:8>)           |                 |             | 0000 00                   | 000 |

| FFDh    | TOSL     |                                                                                                          |                                                                                                                                                                                                               | Тор             | o-of-Stack, Lov | v Byte (TOS<7   | :0>)            |                 |             | 0000 00                   | 000 |

| FFCh    | STKPTR   | STKFUL                                                                                                   | STKUNF                                                                                                                                                                                                        | _               |                 | ç               | STKPTR<4:0>     |                 |             | 00-00                     | 000 |

| FFBh    | PCLATU   | _                                                                                                        | _                                                                                                                                                                                                             | _               |                 | Holding F       | Register for PC | <20:16>         |             | 0 00                      | 000 |

| FFAh    | PCLATH   |                                                                                                          | •                                                                                                                                                                                                             | ŀ               | Holding Regist  | er for PC<15:8  | >               |                 |             | 0000 00                   | 000 |

| FF9h    | PCL      |                                                                                                          |                                                                                                                                                                                                               |                 | Holding Regis   | ter for PC<7:0> | •               |                 |             | 0000 00                   | 000 |

| FF8h    | TBLPTRU  | _                                                                                                        | _                                                                                                                                                                                                             | Pi              | rogram Memor    | y Table Pointer | Upper Byte(T    | BLPTR<21:16     | 6>)         | 00 00                     | 000 |

| FF7h    | TBLPTRH  |                                                                                                          | F                                                                                                                                                                                                             | Program Memo    | ory Table Point | ter High Byte(T | BLPTR<15:8>     | )               |             | 0000 00                   | 000 |

| FF6h    | TBLPTRL  |                                                                                                          | Р                                                                                                                                                                                                             | rogram Memo     | ory Table Point | er Low Byte(TE  | 3LPTR<7:0>)     |                 |             | 0000 00                   | 000 |

| FF5h    | TABLAT   |                                                                                                          |                                                                                                                                                                                                               |                 | Program Men     | ory Table Latc  | h               |                 |             | 0000 00                   | 000 |

| FF4h    | PRODH    |                                                                                                          |                                                                                                                                                                                                               |                 | Product Regis   | ter, High Byte  |                 |                 |             | XXXX XX                   | xxx |

| FF3h    | PRODL    |                                                                                                          |                                                                                                                                                                                                               |                 | Product Regis   | ster, Low Byte  |                 |                 |             | XXXX XX                   | xxx |

| FF2h    | INTCON   | GIE/GIEH                                                                                                 | PEIE/GIEL                                                                                                                                                                                                     | TMR0IE          | INTOIE          | RBIE            | TMR0IF          | INT0IF          | RBIF        | 0000 00                   | 00x |

| FF1h    | INTCON2  | RBPU                                                                                                     | INTEDG0                                                                                                                                                                                                       | INTEDG1         | INTEDG2         | _               | TMR0IP          | _               | RBIP        | 1111 -1                   | 1-1 |

| FF0h    | INTCON3  | INT2IP                                                                                                   | INT1IP                                                                                                                                                                                                        | _               | INT2IE          | INT1IE          | _               | INT2IF          | INT1IF      | 11-0 0-                   | -00 |

| FEFh    | INDF0    | Uses cont                                                                                                | ents of FSR0                                                                                                                                                                                                  | to address da   | ta memorv – v   | alue of FSR0 r  | ot changed (no  | ot a physical r | egister)    |                           |     |

| FEEh    | POSTINCO |                                                                                                          |                                                                                                                                                                                                               |                 |                 |                 | <b>.</b> .      |                 | • ,         |                           |     |

| FEDh    | POSTDEC0 |                                                                                                          |                                                                                                                                                                                                               |                 |                 |                 |                 |                 |             |                           |     |

| FECh    | PREINC0  |                                                                                                          |                                                                                                                                                                                                               |                 |                 |                 |                 |                 |             |                           |     |

| FEBh    | PLUSW0   |                                                                                                          | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register) – value of FSR0 offset by W                                                                            |                 |                 |                 |                 |                 |             |                           |     |

| FEAh    | FSR0H    |                                                                                                          |                                                                                                                                                                                                               |                 |                 |                 |                 | 00              | 000         |                           |     |

| FE9h    | FSR0L    |                                                                                                          |                                                                                                                                                                                                               |                 |                 |                 |                 | XXXX XX         | xxx         |                           |     |

| FE8h    | WREG     |                                                                                                          |                                                                                                                                                                                                               |                 |                 |                 |                 |                 | XXXX XX     | xxx                       |     |

| FE7h    | INDF1    | Uses cor                                                                                                 | Uses contents of FSR1 to address data memory – value of FSR1 not changed (not a physical register)                                                                                                            |                 |                 |                 |                 |                 |             |                           |     |

| FE6h    | POSTINC1 |                                                                                                          | Uses contents of FSR1 to address data memory – value of FSR1 not changed (not a physical register)<br>Uses contents of FSR1 to address data memory – value of FSR1 post-incremented (not a physical register) |                 |                 |                 |                 |                 |             |                           |     |

| FE5h    | POSTDEC1 |                                                                                                          |                                                                                                                                                                                                               |                 |                 | value of FSR1   |                 |                 |             |                           |     |

| FE4h    | PREINC1  |                                                                                                          |                                                                                                                                                                                                               |                 |                 | value of FSR1   |                 |                 |             |                           |     |

| FE3h    | PLUSW1   |                                                                                                          |                                                                                                                                                                                                               |                 | memory – val    | ue of FSR1 pre  |                 |                 |             |                           |     |

| FE2h    | FSR1H    | _                                                                                                        | — — — Indirect Data Memory Address Pointer 1, High Byte                                                                                                                                                       |                 |                 |                 |                 | 00              | 000         |                           |     |

| FE1h    | FSR1L    |                                                                                                          | •                                                                                                                                                                                                             | Indirect Data I | Memory Addre    | ss Pointer 1, L | ow Byte         |                 |             | XXXX XX                   | xxx |

| FE0h    | BSR      | —                                                                                                        | —                                                                                                                                                                                                             | —               | —               |                 | Bank Selec      | t Register      |             | 00                        | 000 |

| FDFh    | INDF2    | Uses co                                                                                                  |                                                                                                                                                                                                               |                 |                 |                 |                 |                 |             |                           |     |

| FDEh    | POSTINC2 |                                                                                                          |                                                                                                                                                                                                               |                 |                 |                 |                 |                 |             |                           |     |

| FDDh    | POSTDEC2 |                                                                                                          |                                                                                                                                                                                                               |                 |                 |                 |                 | )               |             |                           |     |

| FDCh    | PREINC2  | Uses contents of FSR2 to address data memory – value of FSR2 pre-incremented (not a physical register) – |                                                                                                                                                                                                               |                 |                 |                 |                 |                 |             |                           |     |

| FDBh    | PLUSW2   |                                                                                                          |                                                                                                                                                                                                               |                 |                 |                 |                 |                 |             |                           |     |

| FDAh    | FSR2H    | _                                                                                                        | _                                                                                                                                                                                                             | _               | _               | Indirect Dat    | a Memory Add    | ress Pointer 2  | , High Byte | 00                        | 000 |

| FD9h    | FSR2L    |                                                                                                          |                                                                                                                                                                                                               | ndirect Data N  | lemory Addres   | s Pointer 2, Lo | w Byte          |                 |             | XXXX XX                   | xxx |

| FD8h    | STATUS   | _                                                                                                        | _                                                                                                                                                                                                             | _               | N               | OV              | Z               | DC              | С           | x xx                      |     |

| FD7h    | TMR0H    |                                                                                                          | 1                                                                                                                                                                                                             | 1               | Timer0 Regist   |                 |                 | -               | -           | 0000 00                   |     |

| FD6h    | TMR0L    |                                                                                                          |                                                                                                                                                                                                               |                 | Timer0 Regist   |                 |                 |                 |             | xxxx xx                   |     |

| FD5h    | TOCON    | TMR0ON                                                                                                   | T08BIT                                                                                                                                                                                                        | TOCS            | TOSE            | PSA             |                 | T0PS<2:0>       |             | 1111 11                   |     |

| FD3h    | OSCCON   | IDLEN                                                                                                    | 100011                                                                                                                                                                                                        | IRCF<2:0>       | 1002            | OSTS            | HFIOFS          |                 | <1:0>       | 0011 q                    |     |

| FD2h    | OSCCON2  | PLLRDY                                                                                                   | SOSCRUN                                                                                                                                                                                                       |                 | MFIOSEL         | SOSCGO          | PRISD           | MFIOFS          | LFIOFS      | 00-0 01                   |     |

| Legend: |          |                                                                                                          |                                                                                                                                                                                                               |                 |                 | nds on conditio |                 |                 |             | 00.000                    | -70 |

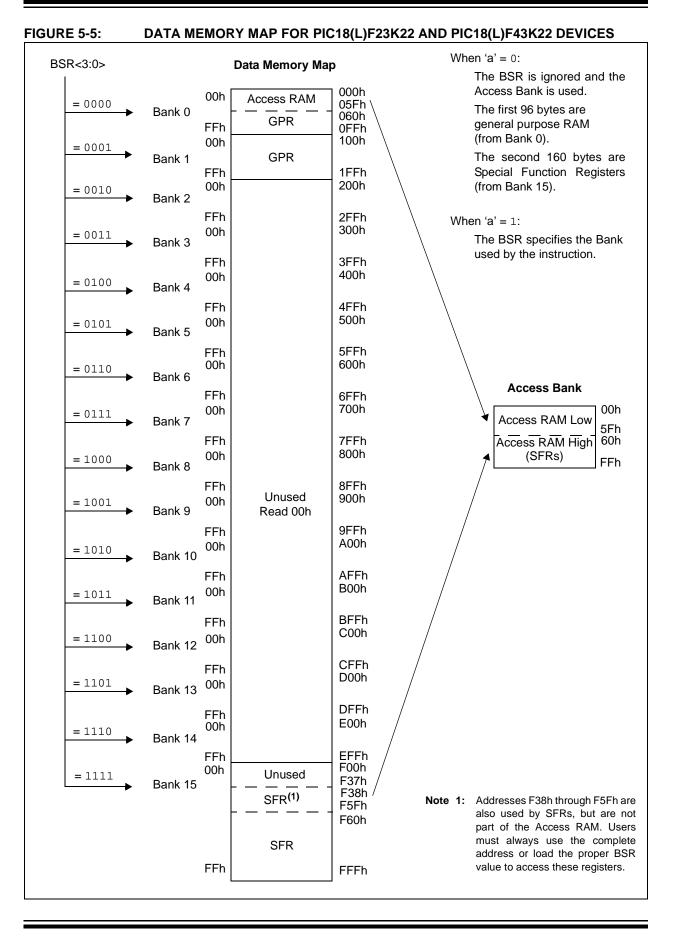

TABLE 5-2: REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES

Note 1: PIC18(L)F4XK22 devices only.

2: PIC18(L)F2XK22 devices only.

3: PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

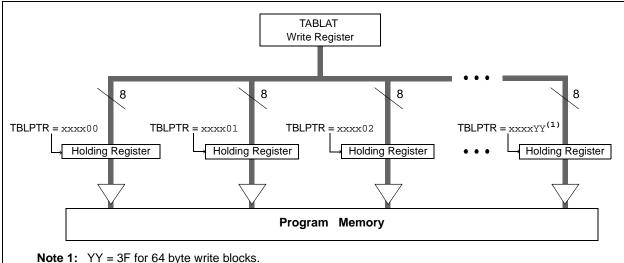

## 6.6 Writing to Flash Program Memory

The programming block size is 64 bytes. Word or byte programming is not supported.

Table writes are used internally to load the holding registers needed to program the Flash memory. There are only as many holding registers as there are bytes in a write block (64 bytes).

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction needs to be executed 64 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. After all the holding registers have been written, the programming operation of that block of memory is started by configuring the EECON1 register for a program memory write and performing the long write sequence. The long write is necessary for programming the internal Flash. Instruction execution is halted during a long write cycle. The long write will be terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

Note: The default value of the holding registers on device Resets and after write operations is FFh. A write of FFh to a holding register does not modify that byte. This means that individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all holding registers before executing a long write operation.

## FIGURE 6-5: TABLE WRITES TO FLASH PROGRAM MEMORY

### 6.6.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the block erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- 6. Write the 64-byte block into the holding registers with auto-increment.

- 7. Set the EECON1 register for the write operation:

- set EEPGD bit to point to program memory;

- · clear the CFGS bit to access program memory;

- set WREN to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Verify the memory (table read).

This procedure will require about 6 ms to update each write block of memory. An example of the required code is given in Example 6-3.

**Note:** Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the bytes in the holding registers.

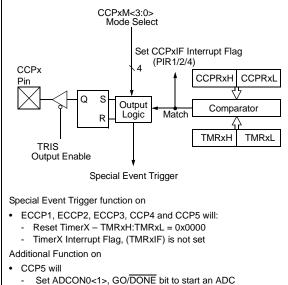

## 14.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains three Enhanced Capture/Compare/PWM modules (ECCP1, ECCP2, and ECCP3) and two standard Capture/Compare/PWM modules (CCP4 and CCP5).

The Capture and Compare functions are identical for all CCP/ECCP modules. The difference between CCP and ECCP modules are in the Pulse-Width Modulation (PWM) function. In CCP modules, the standard PWM function is identical. In ECCP modules, the Enhanced PWM function has either full-bridge or half-bridge PWM output. Full-bridge ECCP modules have four available I/O pins while half-bridge ECCP modules and can be configured as standard PWM modules. See Table 14-1 to determine the CCP/ECCP functionality available on each device in this family.

|  | TABLE 14-1: | PWM RESOURCES |

|--|-------------|---------------|

|--|-------------|---------------|

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to ECCP1, ECCP2, ECCP3, CCP4 and CCP5. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

| Device Name                                                                            | ECCP1                       | ECCP2                       | ECCP3                       | CCP4         | CCP5                                    |

|----------------------------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|--------------|-----------------------------------------|

| PIC18(L)F23K22<br>PIC18(L)F24K22<br>PIC18(L)F25K22<br>PIC18(L)F25K22<br>PIC18(L)F26K22 | Enhanced PWM<br>Full-Bridge | Enhanced PWM<br>Half-Bridge | Enhanced PWM<br>Half-Bridge | Standard PWM | Standard PWM<br>(Special Event Trigger) |

| PIC18(L)F43K22<br>PIC18(L)F44K22<br>PIC18(L)F45K22<br>PIC18(L)F45K22<br>PIC18(L)F46K22 | Enhanced PWM<br>Full-Bridge | Enhanced PWM<br>Full-Bridge | Enhanced PWM<br>Half-Bridge | Standard PWM | Standard PWM<br>(Special Event Trigger) |

## 14.2 Compare Mode

The Compare mode function described in this section is identical for all CCP and ECCP modules available on this device family.

Compare mode makes use of the 16-bit TimerX resources, Timer1, Timer3 and Timer5. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMRxH:TMRxL register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output

- · Set the CCPx output

- Clear the CCPx output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 14-2 shows a simplified diagram of the Compare operation.

### FIGURE 14-2: COMPARE MODE OPERATION BLOCK DIAGRAM

Conversion if ADCON<0>, ADON = 1.

## 14.2.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Some CCPx outputs are multiplexed on a couple of pins. Table 14-2 shows the CCP output pin Multiplexing. Selection of the output pin is determined by the CCPxMX bits in Configuration register 3H (CONFIG3H). Refer to Register 24-4 for more details.

Note: Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

## 14.2.2 TimerX MODE RESOURCE

In Compare mode, 16-bit TimerX resource must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 12.0 "Timer1/3/5 Module with Gate Control" for more information on configuring the 16-bit TimerX resources.

Note: Clocking TimerX from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TimerX must be clocked from the instruction clock (Fosc/4) or from an external clock source.

## 14.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

# 18.9 Register Definitions: Comparator Control

### **REGISTER 18-1: CMxCON0: COMPARATOR x CONTROL REGISTER**

| R/W-0         | R-0                                                                                                | R/W-0                                                                                                                      | R/W-0                                                                       | R/W-1            | R/W-0           | R/W-0           | R/W-0  |

|---------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------|-----------------|-----------------|--------|

| CxON          | CxOUT                                                                                              | CxOE                                                                                                                       | CxPOL                                                                       | CxSP             | CxR             | CxCH            | l<1:0> |

| bit 7         |                                                                                                    |                                                                                                                            |                                                                             |                  |                 |                 | bit    |

| Legend:       |                                                                                                    |                                                                                                                            |                                                                             |                  |                 |                 |        |

| R = Readable  | e bit                                                                                              | W = Writable                                                                                                               | bit                                                                         | U = Unimplei     | mented bit, rea | ad as '0'       |        |

| -n = Value at | POR                                                                                                | '1' = Bit is set                                                                                                           |                                                                             | '0' = Bit is cle |                 | x = Bit is unkr | nown   |

| bit 7         | 1 = Compar                                                                                         | nparator Cx Enal<br>ator Cx is enabl<br>ator Cx is disabl                                                                  | ed                                                                          |                  |                 |                 |        |

| bit 6         | <b>CxOUT:</b> Con<br><u>If CxPOL =</u><br>CxOUT = 0<br>CxOUT = 1<br><u>If CxPOL =</u><br>CxOUT = 1 | mparator Cx Ou<br>1 (inverted polar<br>when CxVIN+ ><br>when CxVIN+ <<br>0 (non-inverted<br>when CxVIN+ ><br>when CxVIN+ < | tput bit<br><u>ity):</u><br>CxVin-<br>CxVin-<br><u>polarity):</u><br>CxVin- |                  |                 |                 |        |

| bit 5         | 1 = CxOUT                                                                                          | parator Cx Outp<br>is present on the<br>is internal only                                                                   |                                                                             | 1)               |                 |                 |        |

| bit 4         | 1 = CxOUT                                                                                          | mparator Cx Ou<br>logic is inverted<br>logic is not inver                                                                  |                                                                             | Select bit       |                 |                 |        |

| bit 3         | <b>CxSP:</b> Com<br>1 = Cx oper                                                                    | parator Cx Spee<br>ates in Normal-F<br>ates in Low-Pow                                                                     | ed/Power Sele<br>Power, Higher                                              | Speed mode       |                 |                 |        |

| bit 2         | <b>CxR:</b> Comp<br>1 = CxVIN+                                                                     | arator Cx Reference<br>connects to CxV<br>connects to C12                                                                  | ence Select bi<br>/REF output                                               |                  | input)          |                 |        |

| bit 1-0       | CxCH<1:0><br>00 = C12IN<br>01 = C12IN<br>10 = C12IN                                                | : Comparator C<br>D- pin of Cx coni<br>1- pin of Cx coni<br>2- pin of Cx coni<br>3- pin of Cx coni                         | x Channel Sel<br>nects to CxVIN<br>nects to CxVIN<br>nects to CxVIN         | 1-<br>1-<br>1-   |                 |                 |        |

**Note 1:** Comparator output requires the following three conditions: CxOE = 1, CxON = 1 and corresponding port TRIS bit = 0.

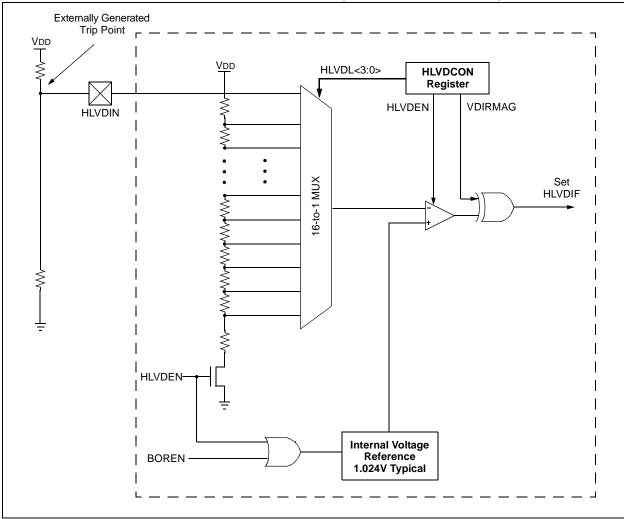

The module is enabled by setting the HLVDEN bit (HLVDCON<4>). Each time the HLVD module is enabled, the circuitry requires some time to stabilize. The IRVST bit (HLVDCON<5>) is a read-only bit used to indicate when the circuit is stable. The module can only generate an interrupt after the circuit is stable and IRVST is set.

The VDIRMAG bit (HLVDCON<7>) determines the overall operation of the module. When VDIRMAG is cleared, the module monitors for drops in VDD below a predetermined set point. When the bit is set, the module monitors for rises in VDD above the set point.

## 23.2 Operation

When the HLVD module is enabled, a comparator uses an internally generated reference voltage as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module.

When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the HLVDIF bit.

The trip point voltage is software programmable to any of 16 values. The trip point is selected by programming the HLVDL<3:0> bits (HLVDCON<3:0>).

The HLVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits, HLVDL<3:0>, are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, HLVDIN. This gives users the flexibility of configuring the High/Low-Voltage Detect interrupt to occur at any voltage in the valid operating range.

FIGURE 23-1: HLVD MODULE BLOCK DIAGRAM (WITH EXTERNAL INPUT)

#### 25.1.1 STANDARD INSTRUCTION SET

| ADDLW             | ADD literal to W             |                 | ADDWF            | ADD W to f                     |                         |                                                               |                                     |  |

|-------------------|------------------------------|-----------------|------------------|--------------------------------|-------------------------|---------------------------------------------------------------|-------------------------------------|--|

| Syntax:           | ADDLW                        | ADDLW k         |                  | Syntax:                        | ADDWF                   | ADDWF f {,d {,a}}                                             |                                     |  |

| Operands:         | $0 \le k \le 255$            |                 |                  | Operands:                      | $0 \leq f \leq 255$     |                                                               |                                     |  |

| Operation:        | ion: $(W) + k \rightarrow W$ |                 |                  | d ∈ [0,1]                      |                         |                                                               |                                     |  |

| Status Affected:  | N, OV, C, E                  | DC, Z           |                  | Oneration                      | $a \in [0,1]$           | doot                                                          |                                     |  |

| Encoding:         | 0000                         | 1111 kk         | kk kkkk          | Operation:<br>Status Affected: | $(W) + (f) \rightarrow$ |                                                               |                                     |  |

| Description:      | The conten                   | ts of W are ad  | lded to the      |                                | N, OV, C, E             |                                                               |                                     |  |

|                   |                              | 'k' and the res | ult is placed in | Encoding:                      | 0010                    | 01da ff                                                       |                                     |  |

|                   | W.                           |                 |                  | Description:                   |                         | egister 'f'. If 'd'<br>ared in W. If 'd'                      |                                     |  |

| Words:            | 1                            |                 |                  |                                | result is sto           | red back in re                                                |                                     |  |

| Cycles:           | 1                            |                 |                  |                                | (default).              |                                                               |                                     |  |

| Q Cycle Activity: | 00                           | 00              | 0.4              |                                | ,                       |                                                               | nk is selected.<br>ed to select the |  |

| Q1                | Q2                           | Q3              | Q4               |                                | GPR bank.               |                                                               |                                     |  |

| Decode            | Read<br>literal 'k'          | Process<br>Data | Write to W       |                                |                         |                                                               | ed instruction ction operates       |  |

| Example:          | ADDLW 1                      | 15h             |                  |                                | in Indexed<br>mode wher | Literal Offset /<br>never f ≤ 95 (5<br>. <b>2.3 "Byte-O</b> r | Addressing<br>Fh). See              |  |

| Before Instruc    | ction                        |                 |                  |                                |                         |                                                               | is in Indexed                       |  |

| W =               | 10h                          |                 |                  |                                |                         | set Mode" for                                                 | details.                            |  |

| After Instruction |                              |                 |                  | Words:                         | 1                       |                                                               |                                     |  |

| W =               | 25h                          |                 |                  | Cycles:                        | 1                       |                                                               |                                     |  |

|                   |                              |                 |                  | Q Cycle Activity:              |                         |                                                               |                                     |  |

|                   |                              |                 |                  | Q1                             | Q2                      | Q3                                                            | Q4                                  |  |

|                   |                              |                 |                  | Decode                         | Read                    | Process                                                       | Write to                            |  |

|                   |                              |                 |                  |                                | register 'f'            | Data                                                          | destination                         |  |

|                   |                              |                 |                  | Example:                       | ADDWF                   | REG, 0, 0                                                     | I                                   |  |

|                   |                              |                 | Before Instruc   | ction                          |                         |                                                               |                                     |  |

|                   |                              |                 |                  | W                              | = 17h                   |                                                               |                                     |  |

|                   |                              |                 |                  | REG<br>After Instruction       | = 0C2h                  |                                                               |                                     |  |

Note: All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

W

REG

0D9h

0C2h

=

=

| TBL               | RD          | Table Rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | d       |     |               |   |                                                                                                      |

|-------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|---------------|---|------------------------------------------------------------------------------------------------------|

| Synta             | ax:         | TBLRD ( *; *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | *+; *-; | +*) |               |   |                                                                                                      |

| Oper              | ands:       | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |     |               |   |                                                                                                      |

| Oper              | ation:      | if TBLRD *,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>TBLPTR – No Change;<br>if TBLRD *+,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>if TBLRD *-,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>(TBLPTR) – 1 $\rightarrow$ TBLPTR;<br>if TBLRD +*,<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;                                                                                                                                                                        |         |     |               |   |                                                                                                      |

| Statu             | s Affected: | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |     |               |   |                                                                                                      |

| Enco              | ding:       | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 000     | 00  | 0000          | ) | 10nn<br>nn=0 *<br>=1 *+<br>=2 *-<br>=3 +*                                                            |

| Desc              | ription:    | This instruction is used to read the contents<br>of Program Memory (P.M.). To address the<br>program memory, a pointer called Table<br>Pointer (TBLPTR) is used.<br>The TBLPTR (a 21-bit pointer) points to<br>each byte in the program memory. TBLPTR<br>has a 2-Mbyte address range.<br>TBLPTR[0] = 0: Least Significant Byte<br>of Program Memory<br>Word<br>TBLPTR[0] = 1: Most Significant Byte<br>of Program Memory<br>Word<br>The TBLRD instruction can modify the value<br>of TBLPTR as follows:<br>• no change<br>• post-increment<br>• post-decrement |         |     |               |   | dress the<br>I Table<br>bints to<br>r. TBLPTR<br>ificant Byte<br>n Memory<br>ficant Byte<br>n Memory |

| Word              | ls:         | pre-increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |     |               |   |                                                                                                      |

| Cycle             |             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |     |               |   |                                                                                                      |

| Q Cycle Activity: |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |     |               |   |                                                                                                      |

| 20                | Q1          | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |     | Q3            |   | Q4                                                                                                   |

|                   | Decode      | No<br>operatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | on      | оре | No<br>eration |   | No<br>operation                                                                                      |

|                   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |     |               |   |                                                                                                      |

No operation (Read Program

Memory)

No

operation

No operation

(Write TABLAT)

| TBLRD | Table Read | (Continued) |

|-------|------------|-------------|

|-------|------------|-------------|

| Example1:                                                                       | TBLRD *+  | + ;         |                       |

|---------------------------------------------------------------------------------|-----------|-------------|-----------------------|

| Before Instruction                                                              | n         |             |                       |

| TABLAT                                                                          |           | =           | 55h                   |

| TBLPTR<br>MEMORY                                                                | (00A356h) | =           | 00A356h<br>34h        |

| After Instruction                                                               | (,        |             | •                     |

| TABLAT                                                                          |           | =           | 34h                   |

| TBLPTR                                                                          |           | =           | 00A357h               |

| Example2:                                                                       | TBLRD +*  | * ;         |                       |