Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 19x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k22-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 3: PIC18(L)F4XK22 PIN SUMMARY (CONTINUED)

|           | •.      | -                |               | -,  |        |            |      | (        |           | ,      |        |             |        |            |         |             |

|-----------|---------|------------------|---------------|-----|--------|------------|------|----------|-----------|--------|--------|-------------|--------|------------|---------|-------------|

| 40-PDIP   | 40-UQFN | 44-TQFP          | 44-QFN        | 0/1 | Analog | Comparator | СТМИ | SR Latch | Reference | (E)CCP | EUSART | <b>JSSM</b> | Timers | Interrupts | Pull-up | Basic       |

| 9         | 24      | 26               | 26            | RE1 | AN6    |            |      |          |           | P3B    |        |             |        |            |         |             |

| 10        | 25      | 27               | 27            | RE2 | AN7    |            |      |          |           | CCP5   |        |             |        |            |         |             |

| 1         | 16      | 18               | 18            | RE3 |        |            |      |          |           |        |        |             |        |            | Y       | MCLR<br>VPP |

| 11,<br>32 | 7, 26   | 7,<br>28         | 7,8<br>28, 29 | Vdd |        |            |      |          |           |        |        |             |        |            |         | Vdd         |

| 12,<br>31 | 6, 27   | 6,<br>29         | 6,<br>30, 31  | Vss |        |            |      |          |           |        |        |             |        |            |         | Vss         |

| —         | —       | 12, 13<br>33, 34 | 13            | NC  |        |            |      |          |           |        |        |             |        |            |         |             |

CCP2 multiplexed in fuses. T3CKI multiplexed in fuses. Note 1:

2:

3: CCP3/P3A multiplexed in fuses.

4: P2B multiplexed in fuses.

|       | Pin N  | lumber  |                |                       | Pin             | Buffer | Description                                          |  |  |

|-------|--------|---------|----------------|-----------------------|-----------------|--------|------------------------------------------------------|--|--|

| PDIP  | TQFP   | QFN     | UQFN           | Pin Name              | Туре            | Туре   | Description                                          |  |  |

| 37    | 14     | 14      | 12             | RB4/IOC0/T5G/AN11     |                 |        | •                                                    |  |  |

|       |        |         |                | RB4                   | I/O             | TTL    | Digital I/O.                                         |  |  |

|       |        |         |                | IOC0                  | I               | TTL    | Interrupt-on-change pin.                             |  |  |

|       |        |         |                | T5G                   | I               | ST     | Timer5 external clock gate input.                    |  |  |

|       |        |         |                | AN11                  | I               | Analog | Analog input 11.                                     |  |  |

| 38    | 15     | 15      | 13             | RB5/IOC1/P3A/CCP3/T3C | KI/T1G/A        | N13    |                                                      |  |  |

|       |        |         |                | RB5                   | I/O             | TTL    | Digital I/O.                                         |  |  |

|       |        |         |                | IOC1                  | I               | TTL    | Interrupt-on-change pin.                             |  |  |

|       |        |         |                | P3A <sup>(1)</sup>    | 0               | CMOS   | Enhanced CCP3 PWM output.                            |  |  |

|       |        |         |                | CCP3 <sup>(1)</sup>   | I/O             | ST     | Capture 3 input/Compare 3 output/PWM 3 output        |  |  |

|       |        |         |                | Т3СКІ <sup>(2)</sup>  | I               | ST     | Timer3 clock input.                                  |  |  |

|       |        |         |                | T1G                   | I               | ST     | Timer1 external clock gate input.                    |  |  |

|       |        |         |                | AN13                  | I               | Analog | Analog input 13.                                     |  |  |

| 39    | 16     | 16      | 14             | RB6/IOC2/PGC          |                 |        |                                                      |  |  |

|       |        |         |                | RB6                   | I/O             | TTL    | Digital I/O.                                         |  |  |

|       |        |         |                | IOC2                  | I               | TTL    | Interrupt-on-change pin.                             |  |  |

|       |        |         |                | PGC                   | I/O             | ST     | In-Circuit Debugger and ICSP™ programming clock pin. |  |  |

| 40    | 17     | 17      | 15             | RB7/IOC3/PGD          |                 |        |                                                      |  |  |

|       |        |         |                | RB7                   | I/O             | TTL    | Digital I/O.                                         |  |  |

|       |        |         |                | IOC3                  | 1               | TTL    | Interrupt-on-change pin.                             |  |  |

|       |        |         |                | PGD                   | I/O             | ST     | In-Circuit Debugger and ICSP™ programming data pin.  |  |  |

| 15    | 32     | 34      | 30             | RC0/P2B/T3CKI/T3G/T1C | KI/SOSC         | 0      | , , , , , , , , , , , , , , , , , , ,                |  |  |

|       |        |         |                | RC0                   | I/O             | ST     | Digital I/O.                                         |  |  |

|       |        |         |                | P2B <sup>(2)</sup>    | 0               | смоз   | Enhanced CCP1 PWM output.                            |  |  |

|       |        |         |                | Т3СКІ <sup>(1)</sup>  | 1               | ST     | Timer3 clock input.                                  |  |  |

|       |        |         |                | T3G                   | I               | ST     | Timer3 external clock gate input.                    |  |  |

|       |        |         |                | T1CKI                 | 1               | ST     | Timer1 clock input.                                  |  |  |

|       |        |         |                | SOSCO                 | ο               | _      | Secondary oscillator output.                         |  |  |

| 16    | 35     | 35      | 31             | RC1/P2A/CCP2/SOSCI    |                 |        |                                                      |  |  |

|       |        |         |                | RC1                   | I/O             | ST     | Digital I/O.                                         |  |  |

|       |        |         |                | P2A <sup>(1)</sup>    | 0               | CMOS   | Enhanced CCP2 PWM output.                            |  |  |

|       |        |         |                | CCP2 <sup>(1)</sup>   | I/O             | ST     | Capture 2 input/Compare 2 output/PWM 2 output        |  |  |

|       |        |         |                | SOSCI                 | "°              | Analog | Secondary oscillator input.                          |  |  |

| 17    | 36     | 36      | 32             | RC2/CTPLS/P1A/CCP1/T  |                 | Ŭ      |                                                      |  |  |

|       |        |         |                | RC2                   | I/O             | ST     | Digital I/O.                                         |  |  |

|       |        |         |                | CTPLS                 | 0               | _      | CTMU pulse generator output.                         |  |  |

|       |        |         |                | P1A                   | 0               | CMOS   | Enhanced CCP1 PWM output.                            |  |  |

|       |        |         |                | CCP1                  | I/O             | ST     | Capture 1 input/Compare 1 output/PWM 1 output        |  |  |

|       |        |         |                | T5CKI                 | .,C             | ST     | Timer5 clock input.                                  |  |  |

|       |        |         |                | AN14                  |                 | Analog | Analog input 14.                                     |  |  |

| Legen | d- тті | _ TTL ~ | l<br>omnatible |                       | u<br>atiblo inn |        | put; ST = Schmitt Trigger input with CMOS levels;    |  |  |

Legend: IIL = IIL compatible input CMOS = CMOS compatible input or output; SI = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

#### 6.3 Register Definitions: Memory Control

#### REGISTER 6-1: EECON1: DATA EEPROM CONTROL 1 REGISTER

| R/W-x         | R/W-x                                                                                             | U-0                                      | R/W-0          | R/W-x                                 | R/W-0            | R/S-0           | R/S-0 |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------|------------------------------------------|----------------|---------------------------------------|------------------|-----------------|-------|--|--|--|--|--|

| EEPGD         | CFGS                                                                                              | —                                        | FREE           | WRERR                                 | WREN             | WR              | RD    |  |  |  |  |  |

| bit 7         |                                                                                                   |                                          |                |                                       |                  |                 | bit   |  |  |  |  |  |

| Legend:       |                                                                                                   |                                          |                |                                       |                  |                 |       |  |  |  |  |  |

| R = Readable  | e bit                                                                                             | W = Writable                             | bit            |                                       |                  |                 |       |  |  |  |  |  |

| S = Bit can b | e set by softwar                                                                                  | e. but not clea                          | red            | U = Unimpler                          | nented bit, read | d as '0'        |       |  |  |  |  |  |

| -n = Value at | POR                                                                                               | '1' = Bit is se                          | t              | '0' = Bit is cle                      | ared             | x = Bit is unkr | nown  |  |  |  |  |  |

|               |                                                                                                   |                                          |                |                                       |                  |                 |       |  |  |  |  |  |

| bit 7         | EEPGD: Flas                                                                                       | h Program or                             | Data EEPRON    | A Memory Selec                        | ct bit           |                 |       |  |  |  |  |  |

|               |                                                                                                   | -<br>lash program                        |                | -                                     |                  |                 |       |  |  |  |  |  |

|               |                                                                                                   | lata EEPROM                              | ,              |                                       |                  |                 |       |  |  |  |  |  |

| bit 6         | CFGS: Flash                                                                                       | Program/Data                             | EEPROM or      | Configuration S                       | elect bit        |                 |       |  |  |  |  |  |

|               |                                                                                                   | Configuration r                          | 0              |                                       |                  |                 |       |  |  |  |  |  |

| 6.4 C         |                                                                                                   |                                          | or data EEPR   | Ow memory                             |                  |                 |       |  |  |  |  |  |

| bit 5         | •                                                                                                 | ted: Read as                             |                | •.                                    |                  |                 |       |  |  |  |  |  |

| bit 4         |                                                                                                   | ( )                                      | rase Enable b  |                                       | DTD on the ne    |                 | ad    |  |  |  |  |  |

|               |                                                                                                   |                                          | of erase opera | dressed by TBL<br>ation)              | PIR on the ne    | Xt WR commar    | 10    |  |  |  |  |  |

|               | 0 = Perform                                                                                       |                                          |                |                                       |                  |                 |       |  |  |  |  |  |

| bit 3         | WRERR: Fla                                                                                        | sh Program/Da                            | ata EEPROM I   | Error Flag bit <sup>(1)</sup>         |                  |                 |       |  |  |  |  |  |

|               | 1 = A write operation is prematurely terminated (any Reset during self-timed programming in norma |                                          |                |                                       |                  |                 |       |  |  |  |  |  |

|               | •                                                                                                 | operation, or an improper write attempt) |                |                                       |                  |                 |       |  |  |  |  |  |

|               | 0 = 1 he write                                                                                    | e operation cor                          | npleted        |                                       |                  |                 |       |  |  |  |  |  |

| bit 2         | WREN: Flash                                                                                       | n Program/Dat                            | a EEPROM W     | rite Enable bit                       |                  |                 |       |  |  |  |  |  |

|               |                                                                                                   | •                                        |                |                                       |                  |                 |       |  |  |  |  |  |

| L:1 4         |                                                                                                   | •                                        | -lash program  | /data EEPROM                          |                  |                 |       |  |  |  |  |  |

| bit 1         | WR: Write Co                                                                                      |                                          | Maraaa/writa   |                                       |                  |                 |       |  |  |  |  |  |

|               |                                                                                                   |                                          |                | cycle or a progra<br>it is cleared by |                  |                 |       |  |  |  |  |  |

|               | · ·                                                                                               |                                          |                | ed) by software                       |                  |                 |       |  |  |  |  |  |

|               | 0 = Write cyc                                                                                     | cle to the EEPI                          | ROM is comple  | ete                                   |                  |                 |       |  |  |  |  |  |

| bit 0         | RD: Read Co                                                                                       |                                          |                |                                       |                  |                 |       |  |  |  |  |  |

|               |                                                                                                   |                                          |                | s one cycle. RD                       |                  |                 |       |  |  |  |  |  |

|               |                                                                                                   | ot cleared) by :<br>t initiate an EE     |                | it cannot be set                      | wnen EEPGD       | = 1  or CFGS =  | 1.)   |  |  |  |  |  |

|               | 0 = D0es 10                                                                                       |                                          | r itow leau    |                                       |                  |                 |       |  |  |  |  |  |

### **Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

#### 7.6 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to Section 24.0 "Special Features of the CPU" for additional information.

#### 7.7 Protection Against Spurious Write

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT). The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

#### 7.8 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM without exceeding the total number of write cycles to a single byte. Refer to the Data EEPROM Memory parameters in **Section 27.0** "**Electrical Specifications**" for write cycle limits. If this is the case, then an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 7-3.

Note: If data EEPROM is only used to store constants and/or data that changes rarely, an array refresh is likely not required. See specification.

| CLRF   | EEADR                                                                                                         | ; Start at address 0                                                                                                                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLRF   | EEADRH                                                                                                        | ; if > 256 bytes EEPROM                                                                                                                                                                                                   |

| BCF    | EECON1, CFGS                                                                                                  | ; Set for memory                                                                                                                                                                                                          |

| BCF    | EECON1, EEPGD                                                                                                 | ; Set for Data EEPROM                                                                                                                                                                                                     |

| BCF    | INTCON, GIE                                                                                                   | ; Disable interrupts                                                                                                                                                                                                      |

| BSF    | EECON1, WREN                                                                                                  | ; Enable writes                                                                                                                                                                                                           |

|        |                                                                                                               | ; Loop to refresh array                                                                                                                                                                                                   |

| BSF    | EECON1, RD                                                                                                    | ; Read current address                                                                                                                                                                                                    |

| MOVLW  | 55h                                                                                                           | ;                                                                                                                                                                                                                         |

| MOVWF  | EECON2                                                                                                        | ; Write 55h                                                                                                                                                                                                               |

| MOVLW  | 0AAh                                                                                                          | ;                                                                                                                                                                                                                         |

| MOVWF  | EECON2                                                                                                        | ; Write OAAh                                                                                                                                                                                                              |

| BSF    | EECON1, WR                                                                                                    | ; Set WR bit to begin write                                                                                                                                                                                               |

| BTFSC  | EECON1, WR                                                                                                    | ; Wait for write to complete                                                                                                                                                                                              |

| BRA    | \$-2                                                                                                          |                                                                                                                                                                                                                           |

| INCFSZ | EEADR, F                                                                                                      | ; Increment address                                                                                                                                                                                                       |

| BRA    | LOOP                                                                                                          | ; Not zero, do it again                                                                                                                                                                                                   |

| INCFSZ | EEADRH, F                                                                                                     | ; if > 256 bytes, Increment address                                                                                                                                                                                       |

| BRA    | LOOP                                                                                                          | ; if > 256 bytes, Not zero, do it again                                                                                                                                                                                   |

| DOF    | FECON1 MDEN                                                                                                   | ; Disable writes                                                                                                                                                                                                          |

|        | ,                                                                                                             |                                                                                                                                                                                                                           |

| BSF    | INTCON, GIE                                                                                                   | ; Enable interrupts                                                                                                                                                                                                       |

|        | CLRF<br>BCF<br>BCF<br>BSF<br>BSF<br>MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>BTFSC<br>BRA<br>INCFSZ<br>BRA<br>INCFSZ | CLRFEEADRHBCFEECON1, CFGSBCFEECON1, EEPGDBCFINTCON, GIEBSFEECON1, WRENBSFEECON1, RDMOVLW55hMOVWFEECON2MOVLW0AAhMOVWFEECON1, WRBSFEECON1, WRBSFEECON1, WRBRA\$-2INCFSZEEADR, FBRALOOPINCFSZEEADRH, FBRALOOPBCFEECON1, WREN |

#### EXAMPLE 7-3: DATA EEPROM REFRESH ROUTINE

| Name     | Bit 7   | Bit 6  | Bit 5       | Bit 4               | Bit 3               | Bit 2     | Bit 1   | Bit 0       | Register<br>on Page |  |

|----------|---------|--------|-------------|---------------------|---------------------|-----------|---------|-------------|---------------------|--|

| ANSELC   | ANSC7   | ANSC6  | ANSC5       | ANSC4               | ANSC3               | ANSC2     | —       |             | 150                 |  |

| ECCP1AS  | CCP1ASE |        | CCP1AS<2:0> |                     | PSS1A0              | C<1:0>    | PSS1B   | D<1:0>      | 202                 |  |

| CCP1CON  | P1M<    | 1:0>   | DC1B<       | 1:0>                |                     | CCP1M<3:0 | )>      |             | 198                 |  |

| ECCP2AS  | CCP2ASE |        | CCP2AS<2:0> |                     | PSS2A0              | C<1:0>    | PSS2B   | PSS2BD<1:0> |                     |  |

| CCP2CON  | P2M<    | 1:0>   | DC2B<       | 1:0>                |                     | CCP2M<3:0 | )>      | >           |                     |  |

| CTMUCONH | CTMUEN  |        | CTMUSIDL    | TGEN                | EDGEN               | EDGSEQEN  | IDISSEN | CTTRIG      | 323                 |  |

| LATC     | LATC7   | LATC6  | LATC5       | LATC4               | LATC3               | LATC2     | LATC1   | LATC0       | 152                 |  |

| PORTC    | RC7     | RC6    | RC5         | RC4                 | RC3                 | RC2       | RC1     | RC0         | 148                 |  |

| RCSTA1   | SPEN    | RX9    | SREN        | CREN                | ADDEN               | FERR      | OERR    | RX9D        | 270                 |  |

| SLRCON   | _       |        | _           | SLRE <sup>(1)</sup> | SLRD <sup>(1)</sup> | SLRC      | SLRB    | SLRA        | 153                 |  |

| SSP1CON1 | WCOL    | SSPOV  | SSPEN       | CKP                 |                     | SSPM<3:0  | >       |             | 253                 |  |

| T1CON    | TMR1CS  | 5<1:0> | T1CKPS      | <1:0>               | T1SOSCEN            | T1SYNC    | T1RD16  | TMR10N      | 166                 |  |

| T3CON    | TMR3CS  | 5<1:0> | T3CKPS-     | <1:0>               | T3SOSCEN            | T3SYNC    | T3RD16  | TMR3ON      | 166                 |  |

| T3GCON   | TMR3GE  | T3GPOL | T3GTM       | T3GSPM              | T3GGO/DONE          | T3GVAL    | T3GS    | S<1:0>      | 167                 |  |

| T5CON    | TMR5CS  | 5<1:0> | T5CKPS      | <1:0>               | T5SOSCEN            | T5SYNC    | T5RD16  | TMR5ON      | 166                 |  |

| TRISC    | TRISC7  | TRISC6 | TRISC5      | TRISC4              | TRISC3              | TRISC2    | TRISC1  | TRISC0      | 151                 |  |

| TXSTA1   | CSRC    | TX9    | TXEN        | SYNC                | SENDB               | BRGH      | TRMT    | TX9D        | 269                 |  |

#### TABLE 10-9: REGISTERS ASSOCIATED WITH PORTC

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for PORTC.

**Note 1:** Available on PIC18(L)F4XK22 devices.

#### TABLE 10-10: CONFIGURATION REGISTERS ASSOCIATED WITH PORTC

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| CONFIG3H | MCLRE | _     | P2BMX | T3CMX | HFOFST | CCP3MX | PBADEN | CCP2MX | 348                 |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTC.

#### TABLE 10-11: PORTD I/O SUMMARY

| Pin Name            | Function           | TRIS<br>Setting | ANSEL setting | Pin<br>Type | Buffer<br>Type   | Description                                              |

|---------------------|--------------------|-----------------|---------------|-------------|------------------|----------------------------------------------------------|

| RD0/SCK2/SCL2/AN20  | RD0                | 0               | 0             | 0           | DIG              | LATD<0> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<0> data input; disabled when analog input enabled. |

|                     | SCK2               | 0               | 0             | 0           | DIG              | MSSP2 SPI Clock output.                                  |

|                     |                    | 1               | 0             | I           | ST               | MSSP2 SPI Clock input.                                   |

|                     | SCL2               | 0               | 0             | 0           | DIG              | MSSP2 I <sup>2</sup> C Clock output.                     |

|                     |                    | 1               | 0             | I           | l <sup>2</sup> C | MSSP2 I <sup>2</sup> C Clock input.                      |

|                     | AN20               | 1               | 1             | Ι           | AN               | Analog input 20.                                         |

| RD1/CCP4/SDI2/SDA2/ | RD1                | 0               | 0             | 0           | DIG              | LATD<1> data output; not affected by analog input.       |

| AN21                |                    | 1               | 0             | I           | ST               | PORTD<1> data input; disabled when analog input enabled. |

|                     | CCP4               | 0               | 0             | 0           | DIG              | Compare 4 output/PWM 4 output.                           |

|                     |                    | 1               | 0             | I           | ST               | Capture 4 input.                                         |

|                     | SDI2               | 1               | 0             | I           | ST               | MSSP2 SPI data input.                                    |

|                     | SDA2               | 0               | 0             | 0           | DIG              | MSSP2 I <sup>2</sup> C data output.                      |

|                     |                    | 1               | 0             | I           | l <sup>2</sup> C | MSSP2 I <sup>2</sup> C data input.                       |

|                     | AN21               | 1               | 1             | I           | AN               | Analog input 21.                                         |

| RD2/P2B/AN22        | RD2                | 0               | 0             | 0           | DIG              | LATD<2> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<2> data input; disabled when analog input enabled. |

|                     | P2B <sup>(1)</sup> | 0               | 0             | 0           | DIG              | Enhanced CCP2 PWM output 2.                              |

|                     | AN22               | 1               | 1             | I           | AN               | Analog input 22.                                         |

| RD3/P2C/SS2/AN23    | RD3                | 0               | 0             | 0           | DIG              | LATD<3> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<3> data input; disabled when analog input enabled. |

|                     | P2C                | 0               | 0             | 0           | DIG              | Enhanced CCP2 PWM output 4.                              |

|                     | SS2                | 1               | 0             | I           | TTL              | MSSP2 SPI slave select input.                            |

|                     | AN23               | 1               | 1             | I           | AN               | Analog input 23.                                         |

| RD4/P2D/SDO2/AN24   | RD4                | 0               | 0             | 0           | DIG              | LATD<4> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<4> data input; disabled when analog input enabled. |

|                     | P2D                | 0               | 0             | 0           | DIG              | Enhanced CCP2 PWM output 3.                              |

|                     | SDO2               | 0               | 0             | 0           | DIG              | MSSP2 SPI data output.                                   |

|                     | AN24               | 1               | 1             | I           | AN               | Analog input 24.                                         |

| RD5/P1B/AN25        | RD5                | 0               | 0             | 0           | DIG              | LATD<5> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<5> data input; disabled when analog input enabled. |

|                     | P1B                | 0               | 0             | 0           | DIG              | Enhanced CCP1 PWM output 2.                              |

|                     | AN25               | 1               | 1             | I           | AN               | Analog input 25.                                         |

**Legend:** AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;  $I^2C$  = Schmitt Trigger input with  $I^2C$ .

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

| FIGURE 12-7:           | TIMER1/3/5 GATE SING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LE-PULSE AND TOGGLE COMBINED MODE                   |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| TMRxGE                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGPOL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGSPM                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGTM                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGG <u>O/</u><br>DONE | <ul> <li>Set by software</li> <li>Counting enabled of the set of the</li></ul> | Cleared by hardware on falling edge of TxGVAL       |

| TxG_IN                 | rising edge of TxG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

| ТхСКІ                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGVAL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TIMER1/3/5             | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>N + 1</u> <u>N + 2</u> <u>N + 3</u> <u>N + 4</u> |

| TMRxGIF                | Cleared by software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Set by hardware on<br>falling edge of TxGVAL        |

#### 12.12 Peripheral Module Disable

When a peripheral module is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bits for Timer1 (TMR1MD), Timer3 (TMR3MD) and Timer5 (TMR5MD) are in the PMD0 Register. See Section 3.0 "Power-Managed Modes" for more information.

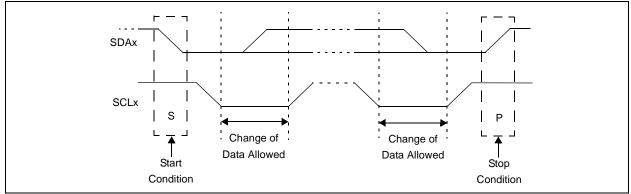

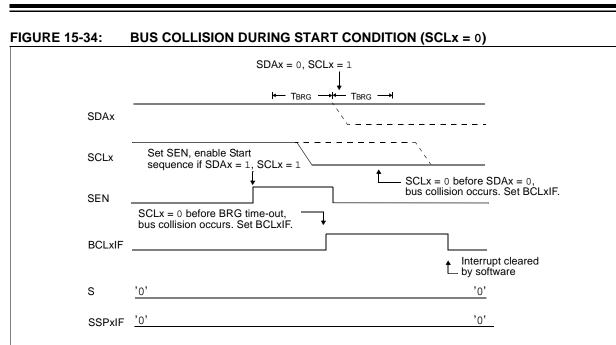

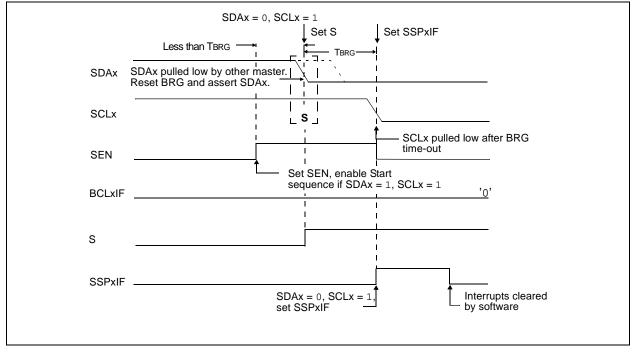

#### 15.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDAx from a high-to -low state while SCLx line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an active state. Figure 15-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDAx line low before asserting it low. This does not conform to the  $I^2C$  specification that states no bus collision can occur on a Start.

#### 15.4.6 STOP CONDITION

A Stop condition is a transition of the SDAx line from a low-to-high state while the SCLx line is high.

**Note:** At least one SCLx low time must appear before a Stop is valid, therefore, if the SDAx line goes low then high again while the SCLx line stays high, only the Start condition is detected.

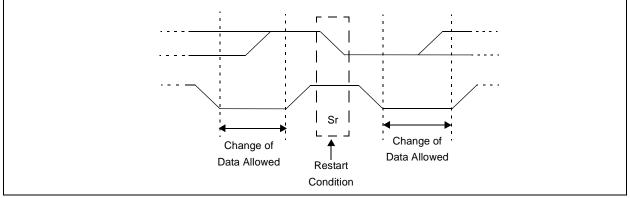

#### 15.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 15-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the R/W bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained. Until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

#### 15.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPxCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

#### FIGURE 15-12: I<sup>2</sup>C START AND STOP CONDITIONS

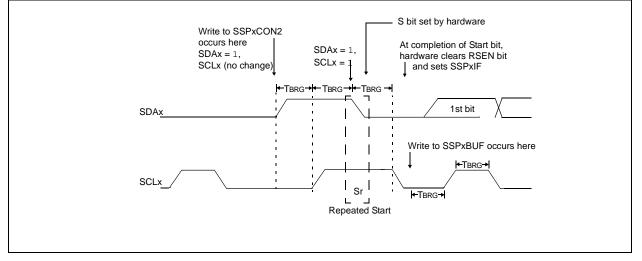

#### 15.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 15-27) occurs when the RSEN bit of the SSPxCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. SCLx is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

#### FIGURE 15-27: REPEAT START CONDITION WAVEFORM

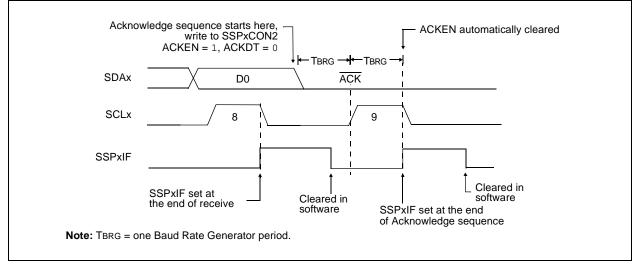

#### 15.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN, of the SSPxCON2 register. When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSPx module then goes into Idle mode (Figure 15-30).

#### 15.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write does not occur).

#### 15.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN, of the SSPxCON2 register. At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 15-31).

#### 15.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### FIGURE 15-30: ACKNOWLEDGE SEQUENCE WAVEFORM

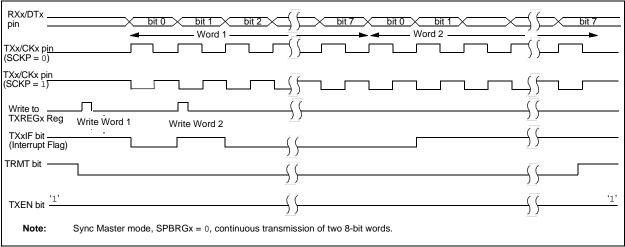

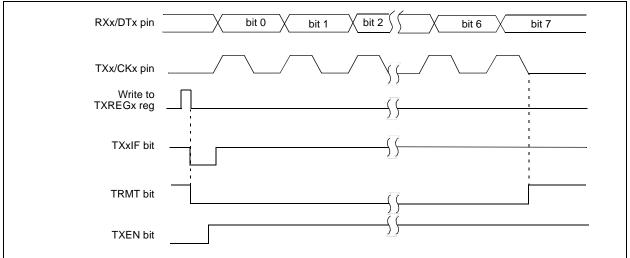

- 16.5.1.5 Synchronous Master Transmission Setup:

- Initialize the SPBRGHx, SPBRGx register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 16.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC. Set the TRIS bits corresponding to the RXx/DTx and TXx/CKx I/O pins.

- 4. Disable Receive mode by clearing bits SREN and CREN.

- 5. Enable Transmit mode by setting the TXEN bit.

- 6. If 9-bit transmission is desired, set the TX9 bit.

- 7. If interrupts are desired, set the TXxIE, GIE/ GIEH and PEIE/GIEL interrupt enable bits.

- 8. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 9. Start transmission by loading data to the TXREGx register.

### FIGURE 16-10: SYNCHRONOUS TRANSMISSION

#### FIGURE 16-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### 17.2 ADC Operation

#### 17.2.1 STARTING A CONVERSION

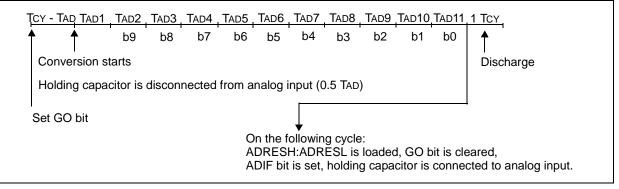

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will, depending on the ACQT bits of the ADCON2 register, either immediately start the Analog-to-Digital conversion or start an acquisition delay followed by the Analog-to-Digital conversion. Figure 17-3 shows the operation of the A/D converter after the GO bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into SLEEP mode before the conversion begins.

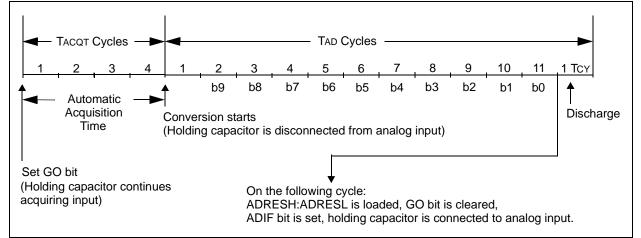

Figure 17-4 shows the operation of the A/D converter after the GO bit has been set and the ACQT<2:0> bits are set to '010' which selects a 4 TAD acquisition time before the conversion starts.

| Note: | The GO/DONE bit should not be set in the |                                         |                 |      |  |  |  |  |  |  |

|-------|------------------------------------------|-----------------------------------------|-----------------|------|--|--|--|--|--|--|

|       | same ir                                  | same instruction that turns on the ADC. |                 |      |  |  |  |  |  |  |

|       | Refer                                    | to                                      | Section 17.2.10 | "A/D |  |  |  |  |  |  |

|       | Conver                                   | sion F                                  | Procedure".     |      |  |  |  |  |  |  |

#### FIGURE 17-3: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

#### FIGURE 17-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

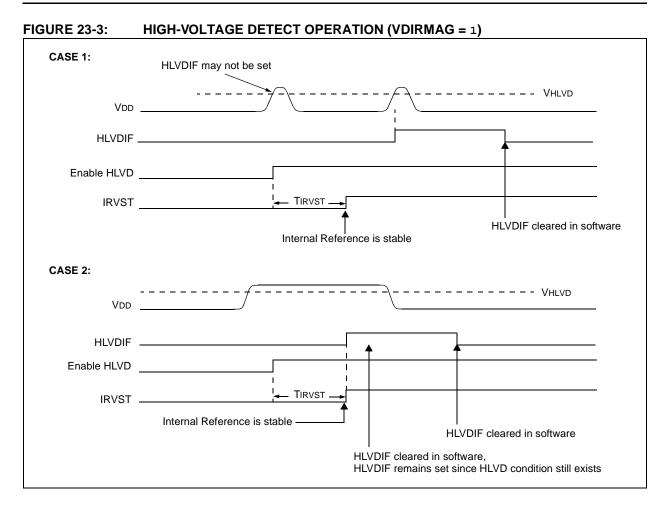

#### 23.6 Applications

In many applications, it is desirable to detect a drop below, or rise above, a particular voltage threshold. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

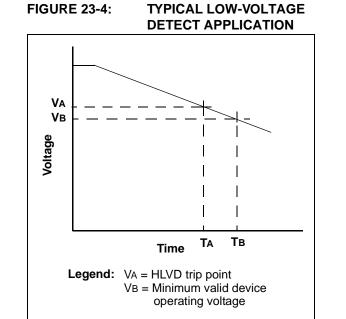

For general battery applications, Figure 23-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and a controlled shutdown before the device voltage exits the valid operating range at TB. This would give the application a time window, represented by the difference between TA and TB, to safely exit.

| Mnemo     | onic,   | Description                    | Cycles     | 16-  | Bit Instr | uction W | /ord | Status            | Netes |

|-----------|---------|--------------------------------|------------|------|-----------|----------|------|-------------------|-------|

| Opera     | nds     | Description                    | Cycles     | MSb  |           |          | LSb  | Affected          | Notes |

| BIT-ORIEN | ITED OP | ERATIONS                       |            |      |           |          |      |                   |       |

| BCF       | f, b, a | Bit Clear f                    | 1          | 1001 | bbba      | ffff     | ffff | None              | 1, 2  |

| BSF       | f, b, a | Bit Set f                      | 1          | 1000 | bbba      | ffff     | ffff | None              | 1, 2  |

| BTFSC     | f, b, a | Bit Test f, Skip if Clear      | 1 (2 or 3) | 1011 | bbba      | ffff     | ffff | None              | 3, 4  |

| BTFSS     | f, b, a | Bit Test f, Skip if Set        | 1 (2 or 3) | 1010 | bbba      | ffff     | ffff | None              | 3, 4  |

| BTG       | f, b, a | Bit Toggle f                   | 1          | 0111 | bbba      | ffff     | ffff | None              | 1, 2  |

| CONTROL   | OPERA   | TIONS                          |            |      |           |          |      | •                 |       |

| BC        | n       | Branch if Carry                | 1 (2)      | 1110 | 0010      | nnnn     | nnnn | None              |       |

| BN        | n       | Branch if Negative             | 1 (2)      | 1110 | 0110      | nnnn     | nnnn | None              |       |

| BNC       | n       | Branch if Not Carry            | 1 (2)      | 1110 | 0011      | nnnn     | nnnn | None              |       |

| BNN       | n       | Branch if Not Negative         | 1 (2)      | 1110 | 0111      | nnnn     | nnnn | None              |       |

| BNOV      | n       | Branch if Not Overflow         | 1 (2)      | 1110 | 0101      | nnnn     | nnnn | None              |       |

| BNZ       | n       | Branch if Not Zero             | 1 (2)      | 1110 | 0001      | nnnn     | nnnn | None              |       |

| BOV       | n       | Branch if Overflow             | 1 (2)      | 1110 | 0100      | nnnn     | nnnn | None              |       |

| BRA       | n       | Branch Unconditionally         | 2          | 1101 | 0nnn      | nnnn     | nnnn | None              |       |