#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (8K x 16)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 768 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-UQFN (4x4)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k22t-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

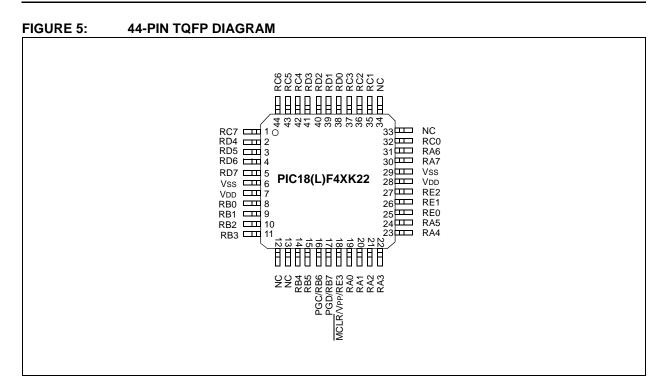

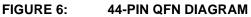

This document contains device specific information for the following devices:

- PIC18F23K22 PIC18LF23K22

- PIC18F24K22 PIC18LF24K22

- PIC18F25K22 PIC18LF25K22

- PIC18F26K22 PIC18LF26K22

- PIC18F43K22 PIC18LF43K22

- PIC18F44K22 PIC18LF44K22

- PIC18F45K22 PIC18LF45K22

- PIC18F46K22 PIC18LF46K22

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Flash program memory. On top of these features, the PIC18(L)F2X/4XK22 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

#### 1.1 New Core Features

#### 1.1.1 XLP TECHNOLOGY

All of the devices in the PIC18(L)F2X/4XK22 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- **On-the-fly Mode Switching:** The powermanaged modes are invoked by user code during operation, allowing the user to incorporate powersaving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 27.0 "Electrical Specifications" for values.

#### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18(L)F2X/4XK22 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O)

- Two External RC Oscillator modes with the same pin options as the External Clock modes

- An internal oscillator block which contains a 16 MHz HFINTOSC oscillator and a 31 kHz LFINTOSC oscillator, which together provide eight user selectable clock frequencies, from 31 kHz to 16 MHz. This option frees the two oscillator pins for use as additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both external and internal oscillator modes, which allows clock speeds of up to 64 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 64 MHz – all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the LFINTOSC. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or Wake-up from Sleep mode, until the primary clock source is available.

| R-0/0            | R-0/q                        | U-0            | R/W-0/0            | R/W-0/u               | R/W-1/1        | R-x/u          | R-0/0     |

|------------------|------------------------------|----------------|--------------------|-----------------------|----------------|----------------|-----------|

| PLLRDY           | SOSCRUN                      | _              | MFIOSEL            | SOSCGO <sup>(1)</sup> | PRISD          | MFIOFS         | LFIOFS    |

| bit 7            |                              |                | ·                  |                       |                |                | bit       |

| Legend:          |                              |                |                    |                       |                |                |           |

| R = Readable     | bit W = W                    | /ritable bit   | U = Unimple        | emented bit, rea      | ad as '0' d    | q = depends on | condition |

| '1' = Bit is set | '0' = B                      | it is cleared  | x = Bit is un      | known                 |                |                |           |

| -n/n = Value at  | POR and BOR                  | Value at all c | ther Resets        |                       |                |                |           |

|                  |                              |                |                    |                       |                |                |           |

| bit 7            | PLLRDY: PLL                  | Run Status b   | it                 |                       |                |                |           |

|                  | 1 = System clo               |                |                    |                       |                |                |           |

|                  | •                            |                |                    | , other than 4xF      | PLL .          |                |           |

| bit 6            | SOSCRUN: SO                  |                |                    |                       |                |                |           |

|                  |                              |                | om secondary S     |                       | 80             |                |           |

|                  | -                            |                |                    | , other than SO       | 30             |                |           |

| bit 5            | Unimplemente                 |                |                    |                       |                |                |           |

| bit 4            | MFIOSEL: MF                  |                |                    |                       |                |                |           |

|                  | 1 = MFINTOS0 = MFINTOS       |                |                    | DSC frequencie        | S OT 500 KHZ,  | 250 KHZ and 3  | 1.25 KHZ  |

| bit 3            |                              |                | cillator Start Co  | ntrol bit             |                |                |           |

|                  | 1 = Secondary                |                |                    |                       |                |                |           |

|                  | 0 = Secondary                | oscillator is  | shut off if no oth | ner sources are       | requesting it. |                |           |

| bit 2            | PRISD: Primar                | y Oscillator E | Prive Circuit Shu  | utdown bit            |                |                |           |

|                  | 1 = Oscillator               |                |                    |                       |                |                |           |

|                  | 0 = Oscillator of            |                |                    |                       |                |                |           |

| bit 1            |                              |                | ency Stable bit    |                       |                |                |           |

|                  | 1 = MFINTOS                  |                | _                  |                       |                |                |           |

|                  | 0 = MFINTOS                  |                |                    |                       |                |                |           |

| bit 0            | LFIOFS: LFINT                | •              | ency Stable bit    |                       |                |                |           |

|                  | 1 = LFINTOSC<br>0 = LFINTOSC |                | 2                  |                       |                |                |           |

|                  |                              |                |                    |                       |                |                |           |

#### REGISTER 2-2: OSCCON2: OSCILLATOR CONTROL REGISTER 2

#### 2.8 PLL Frequency Multiplier

A Phase-Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency oscillator circuit or to clock the device up to its highest rated frequency from the crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals or users who require higher clock speeds from an internal oscillator.

#### 2.8.1 PLL IN EXTERNAL OSCILLATOR MODES

The PLL can be enabled for any of the external oscillator modes using the OSC1/OSC2 pins by either setting the PLLCFG bit (CONFIG1H<4>), or setting the PLLEN bit (OSCTUNE<6>). The PLL is designed for input frequencies of 4 MHz up to 16 MHz. The PLL then multiplies the oscillator output frequency by four to produce an internal clock frequency up to 64 MHz. Oscillator frequencies below 4 MHz should not be used with the PLL.

#### 2.8.2 PLL IN HFINTOSC MODES

The 4x frequency multiplier can be used with the internal oscillator block to produce faster device clock speeds than are normally possible with the internal oscillator. When enabled, the PLL multiplies the HFINTOSC by four to produce clock rates up to 64 MHz.

Unlike external clock modes, when internal clock modes are enabled, the PLL can only be controlled through software. The PLLEN control bit of the OSCTUNE register is used to enable or disable the PLL operation when the HFINTOSC is used.

The PLL is designed for input frequencies of 4 MHz up to 16 MHz.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR      |

|-----------------|-------------------------|

|                 | ;SAVED IN FAST REGISTER |

|                 | ; STACK                 |

| •               |                         |

| •               |                         |

|                 |                         |

| SUB1 •          |                         |

| •               |                         |

| RETURN, FAST    |                         |

|                 | ;IN FAST REGISTER STACK |

#### 5.2.2 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 5.2.2.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of two (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 5-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, | W |

|-------|-------|---------|---|

|       | CALL  | TABLE   |   |

| ORG   | nn00h |         |   |

| TABLE | ADDWF | PCL     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | •     |         |   |

|       | •     |         |   |

|       | •     |         |   |

|       |       |         |   |

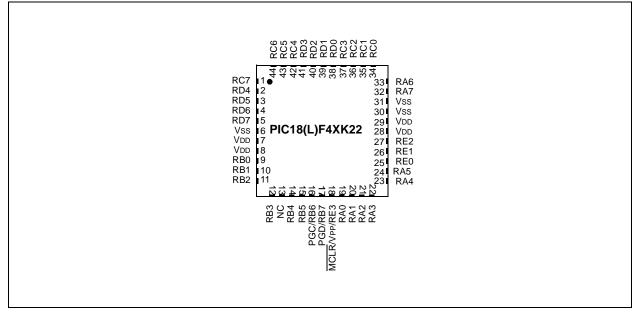

#### 5.2.2.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 6.1 "Table Reads and Table Writes".

#### 6.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

#### 6.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 6-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When EEPGD is clear, any subsequent operations will operate on the data EEPROM memory. When EEPGD is set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When CFGS is set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 24.0 "Special Features of the CPU"**). When CFGS is clear, memory selection access is determined by EEPGD. The FREE bit allows the program memory erase operation. When FREE is set, an erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. The WREN bit is clear on power-up.

The WRERR bit is set by hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

Note: During normal operation, the WRERR is read as '1'. This can indicate that a write operation was prematurely terminated by a Reset, or a write operation was attempted improperly.

The WR control bit initiates write operations. The WR bit cannot be cleared, only set, by firmware. Then WR bit is cleared by hardware at the completion of the write operation.

Note: The EEIF interrupt flag bit of the PIR2 register is set when the write is complete. The EEIF flag stays set until cleared by firmware.

#### 6.3.1 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 6.3.2 TBLPTR – TABLE POINTER REGISTER

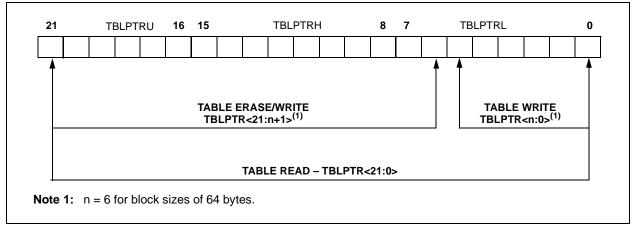

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the device ID, the user ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations on the TBLPTR affect only the low-order 21 bits.

#### 6.3.3 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory directly into the TABLAT register.

When a TBLWT is executed the byte in the TABLAT register is written, not to Flash memory but, to a holding register in preparation for a program memory write. The holding registers constitute a write block which varies depending on the device (see Table 6-1). The 3, 4, or 5 LSbs of the TBLPTRL register determine which specific address within the holding register block is written to. The MSBs of the Table Pointer have no effect during TBLWT operations.

When a program memory write is executed the entire holding register block is written to the Flash memory at the address determined by the MSbs of the TBLPTR. The 3, 4, or 5 LSBs are ignored during Flash memory writes. For more detail, see **Section 6.6** "**Writing to Flash Program Memory**".

When an erase of program memory is executed, the 16 MSbs of the Table Pointer register (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 6-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

#### TABLE 6-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

#### FIGURE 6-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

### 8.0 8 x 8 HARDWARE MULTIPLIER

#### 8.1 Introduction

All PIC18 devices include an 8 x 8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 8-1.

#### 8.2 Operation

Example 8-1 shows the instruction sequence for an 8 x 8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 8-2 shows the sequence to do an 8 x 8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 8-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MULWF ARG2 ; ARG1 * ARG2 -><br>; PRODH:PRODL | MOVF  | ARG1, | W | ; |       |     |       |    |  |

|----------------------------------------------|-------|-------|---|---|-------|-----|-------|----|--|

| ; PRODH:PRODL                                | MULWF | ARG2  |   | ; | ARG1  | *   | ARG2  | -> |  |

|                                              |       |       |   | ; | PRODE | I:1 | PRODL |    |  |

#### EXAMPLE 8-2: 8 x 8 SIGNED MULTIPLY

| MOVF  | ARG1, W  |   |                |

|-------|----------|---|----------------|

| MULWF | ARG2     | ; | ARG1 * ARG2 -> |

|       |          | ; | PRODH:PRODL    |

| BTFSC | ARG2, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG1         |

| MOVF  | ARG2, W  |   |                |

| BTFSC | ARG1, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG2         |

|       |          |   |                |

|                  |                           | Program           | Cycles |          | Tir      | ne       |         |

|------------------|---------------------------|-------------------|--------|----------|----------|----------|---------|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 64 MHz | @ 40 MHz | @ 10 MHz | @ 4 MHz |

| Q v Q unoignod   | Without hardware multiply | 13                | 69     | 4.3 μs   | 6.9 μs   | 27.6 μs  | 69 μs   |

| 8 x 8 unsigned   | Hardware multiply         | 1                 | 1      | 62.5 ns  | 100 ns   | 400 ns   | 1 μs    |

| Q v Q aignad     | Without hardware multiply | 33                | 91     | 5.7 μs   | 9.1 μs   | 36.4 μs  | 91 μs   |

| 8 x 8 signed     | Hardware multiply         | 6                 | 6      | 375 ns   | 600 ns   | 2.4 μs   | 6 μs    |

| 16 x 16 uppigpod | Without hardware multiply | 21                | 242    | 15.1 μs  | 24.2 μs  | 96.8 μs  | 242 μs  |

| 16 x 16 unsigned | Hardware multiply         | 28                | 28     | 1.8 μs   | 2.8 μs   | 11.2 μs  | 28 μs   |

| 16 x 16 signed   | Without hardware multiply | 52                | 254    | 15.9 μs  | 25.4 μs  | 102.6 μs | 254 μs  |

| 16 x 16 signed   | Hardware multiply         | 35                | 40     | 2.5 μs   | 4.0 μs   | 16.0 μs  | 40 µs   |

#### TABLE 8-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

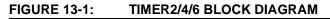

### 13.0 TIMER2/4/6 MODULE

There are three identical 8-bit Timer2-type modules available. To maintain pre-existing naming conventions, the Timers are called Timer2, Timer4 and Timer6 (also Timer2/4/6).

| Note: | The 'x' variable used in this section is used to designate Timer2, Timer4, or Timer6. For example, TxCON references |

|-------|---------------------------------------------------------------------------------------------------------------------|

|       | T2CON, T4CON, or T6CON. PRx references PR2, PR4, or PR6.                                                            |

The Timer2/4/6 module incorporates the following features:

- 8-bit Timer and Period registers (TMRx and PRx, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMRx match with PRx, respectively

- Optional use as the shift clock for the MSSPx modules (Timer2 only)

See Figure 13-1 for a block diagram of Timer2/4/6.

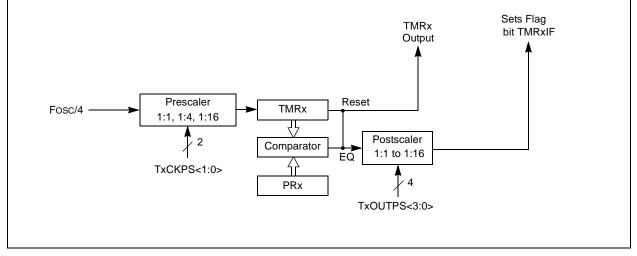

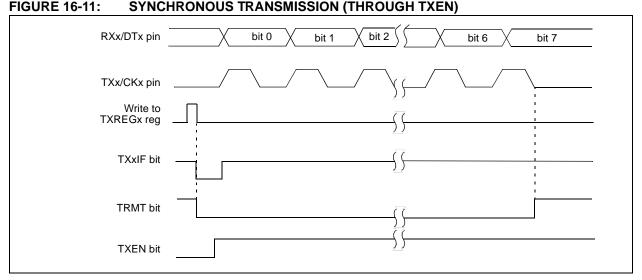

- 16.5.1.5 Synchronous Master Transmission Setup:

- 1. Initialize the SPBRGHx, SPBRGx register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 16.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- Enable the synchronous master serial port by 3. setting bits SYNC, SPEN and CSRC. Set the TRIS bits corresponding to the RXx/DTx and TXx/CKx I/O pins.

FIGURE 16-10:

- 4. Disable Receive mode by clearing bits SREN and CREN.

- Enable Transmit mode by setting the TXEN bit. 5.

- 6. If 9-bit transmission is desired, set the TX9 bit.

- 7. If interrupts are desired, set the TXxIE, GIE/ GIEH and PEIE/GIEL interrupt enable bits.

- If 9-bit transmission is selected, the ninth bit 8. should be loaded in the TX9D bit.

- Start transmission by loading data to the 9. TXREGx register.

### **FIGURE 16-11:**

SYNCHRONOUS TRANSMISSION

#### 16.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTAx register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTAx register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTAx register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTAx register enables the EUSART. If the RXx/DTx or TXx/CKx pins are shared with an analog peripheral the analog I/O functions must be disabled by clearing the corresponding ANSEL bits.

RXx/DTx and TXx/CKx pin output drivers must be disabled by setting the corresponding TRIS bits.

#### 16.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see Section 16.5.1.3 "Synchronous Master Transmission"), except in the case of the Sleep mode.

If two words are written to the TXREGx and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREGx register.

- 3. The TXxIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREGx register will transfer the second character to the TSR and the TXxIF bit will now be set.

- 5. If the PEIE/GIEL and TXxIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE/GIEH bit is also set, the program will call the Interrupt Service Routine.

- 16.5.2.2 Synchronous Slave Transmission Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- 3. Clear the CREN and SREN bits.

- 4. If using interrupts, ensure that the GIE/GIEH and PEIE/GIEL bits of the INTCON register are set and set the TXxIE bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREGx register.

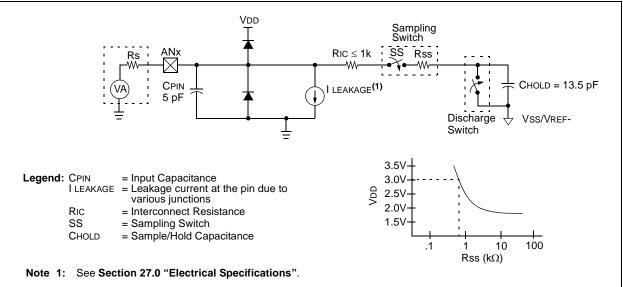

#### 17.4 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 17-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 17-5. The maximum recommended impedance for analog sources is  $3 \ k\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D

acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 17-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 17-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature = 50°C and external impedance of 10k

$$\Omega$$

3.0V VDD

$$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

= 5µs + TC + [(Temperature - 25°C)(0.05µs/°C)]

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{2047}\right) = V_{CHOLD} \qquad :[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{-\frac{TC}{RC}}\right) = V_{CHOLD} \qquad :[2] V_{CHOLD} charge response to V_{APPLIED}$$

$$V_{APPLIED}\left(1 - e^{-\frac{TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{2047}\right) \qquad :combining [1] and [2]$$

Solving for Tc:

$$T_{C} = -C_{HOLD}(RIC + RSS + RS) \ln(1/2047)$$

$$= -13.5pF(1k\Omega + 700\Omega + 10k\Omega) \ln(0.0004885)$$

$$= 1.20\mu s$$$$

$$TACQ = 5\mu s + 1.20\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 7.45\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

© 2010-2016 Microchip Technology Inc.

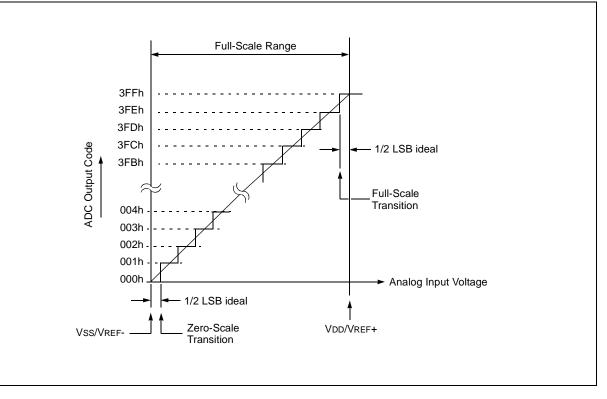

FIGURE 17-6: ADC TRANSFER FUNCTION

| ΒZ           |                                                                                     | Branch if                                                                 | Zero                                                                                                                     |                                                          |

|--------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Synta        | ax:                                                                                 | BZ n                                                                      |                                                                                                                          |                                                          |

| Oper         | ands:                                                                               | -128 ≤ n ≤ ′                                                              | 27                                                                                                                       |                                                          |

| Oper         | ation:                                                                              | if ZERO bit<br>(PC) + 2 + 2                                               |                                                                                                                          |                                                          |

| Statu        | is Affected:                                                                        | None                                                                      |                                                                                                                          |                                                          |

| Enco         | oding:                                                                              | 1110                                                                      | 0000 nnr                                                                                                                 | nn nnnn                                                  |

| Desc         | ription:                                                                            | will branch.<br>The 2's con<br>added to th<br>have incren<br>instruction, | ) bit is '1', ther<br>nplement num<br>e PC. Since th<br>nented to fetch<br>the new addre<br>n. This instruct<br>ruction. | ber '2n' is<br>he PC will<br>he the next<br>hess will be |

| Word         | ds:                                                                                 | 1                                                                         |                                                                                                                          |                                                          |

| Cycle        | es:                                                                                 | 1(2)                                                                      |                                                                                                                          |                                                          |

| Q C<br>If Ju | ycle Activity:                                                                      |                                                                           |                                                                                                                          |                                                          |

|              | Q1                                                                                  | Q2                                                                        | Q3                                                                                                                       | Q4                                                       |

|              | Decode                                                                              | Read literal<br>'n'                                                       | Process<br>Data                                                                                                          | Write to PC                                              |

|              | No<br>operation                                                                     | No<br>operation                                                           | No<br>operation                                                                                                          | No<br>operation                                          |

| lf No        | o Jump:                                                                             |                                                                           |                                                                                                                          |                                                          |

|              | Q1                                                                                  | Q2                                                                        | Q3                                                                                                                       | Q4                                                       |

|              | Decode                                                                              | Read literal<br>'n'                                                       | Process<br>Data                                                                                                          | No<br>operation                                          |

| <u>Exan</u>  | nple:<br>Before Instruc<br>PC<br>After Instructic<br>If ZERO<br>PC<br>If ZERO<br>PC | = ad<br>= 1;<br>= ad<br>= 0;                                              | BZ Jump<br>dress (HERE<br>dress (Jump<br>dress (HERE                                                                     | )                                                        |

|                                                     | Subrouti                                                                                                                                                              |                                                                                                                                 |                                                                                              |                                                                                                                                           |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                             | CALL k {,:                                                                                                                                                            | -                                                                                                                               |                                                                                              |                                                                                                                                           |

| Operands:                                           | 0 ≤ k ≤ 104<br>s ∈ [0,1]                                                                                                                                              | 8575                                                                                                                            |                                                                                              |                                                                                                                                           |

| Operation:                                          | $\begin{array}{l} (PC) + 4 \rightarrow \\ k \rightarrow PC < 20 \\ \text{if } s = 1 \\ (W) \rightarrow WS \\ (Status) \rightarrow \\ (BSR) \rightarrow B \end{array}$ | ):1>,<br>,<br>STATUS                                                                                                            | S,                                                                                           |                                                                                                                                           |

| Status Affected:                                    | None                                                                                                                                                                  |                                                                                                                                 |                                                                                              |                                                                                                                                           |

| Encoding:<br>1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110<br>1111                                                                                                                                                          | 110s<br>k <sub>19</sub> kkk                                                                                                     | k <sub>7</sub> kkl<br>kkkk                                                                   |                                                                                                                                           |

|                                                     |                                                                                                                                                                       |                                                                                                                                 |                                                                                              | n address                                                                                                                                 |

|                                                     | (PC + 4) is<br>stack. If 's'<br>BSR register<br>respective<br>STATUSS i<br>update occ<br>20-bit value<br>CALL is a                                                    | pushed of<br>= 1, the <sup>1</sup><br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                            | onto the<br>W, STA<br>so push<br>registers<br>S. If 's'<br>ult). The<br>ded into             | e return<br>TUS and<br>hed into th<br>s, WS,<br>= $0$ , no<br>hen, the<br>o PC<20:                                                        |

| Words:                                              | (PC + 4) is<br>stack. If 's'<br>BSR registe<br>respective<br>STATUSS<br>update occ<br>20-bit value                                                                    | pushed of<br>= 1, the <sup>1</sup><br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                            | onto the<br>W, STA<br>so push<br>registers<br>S. If 's'<br>ult). The<br>ded into             | e return<br>TUS and<br>hed into th<br>s, WS,<br>= $0$ , no<br>hen, the<br>o PC<20:                                                        |

| Words:<br>Cycles:                                   | (PC + 4) is<br>stack. If 's'<br>BSR register<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a                                                    | pushed of<br>= 1, the <sup>1</sup><br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                            | onto the<br>W, STA<br>so push<br>registers<br>S. If 's'<br>ult). The<br>ded into             | e return<br>TUS and<br>hed into th<br>s, WS,<br>= $0$ , no<br>hen, the<br>o PC<20:                                                        |

|                                                     | (PC + 4) is<br>stack. If 's'<br>BSR registr<br>respective<br>STATUSS i<br>update occ<br>20-bit value<br>CALL is a                                                     | pushed of<br>= 1, the <sup>1</sup><br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                            | onto the<br>W, STA<br>so push<br>registers<br>S. If 's'<br>ult). The<br>ded into             | e return<br>TUS and<br>hed into th<br>s, WS,<br>= $0$ , no<br>hen, the<br>o PC<20:                                                        |

| Cycles:                                             | (PC + 4) is<br>stack. If 's'<br>BSR registr<br>respective<br>STATUSS i<br>update occ<br>20-bit value<br>CALL is a                                                     | pushed of<br>= 1, the <sup>1</sup><br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                            | onto the<br>W, STA<br>so push<br>registers<br>S. If 's'<br>ult). Th<br>ded into<br>nstructio | e return<br>TUS and<br>hed into th<br>s, WS,<br>= $0$ , no<br>hen, the<br>o PC<20:                                                        |

| Cycles:<br>Q Cycle Activity:                        | (PC + 4) is<br>stack. If 's'<br>BSR registr<br>respective<br>STATUSS i<br>update occ<br>20-bit value<br>CALL is a<br>2<br>2                                           | pushed (<br>= 1, the <sup>1</sup> )<br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>9 'k' is loa<br>2-cycle ir             | onto the<br>W, STA<br>so push<br>registers<br>S. If 's'<br>ult). Th<br>ded into<br>astructio | e return<br>TUS and<br>hed into th<br>s, WS,<br>= 0, no<br>en, the<br>o PC<20:<br>on.                                                     |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>No  | (PC + 4) is<br>stack. If 's'<br>BSR registr<br>respective<br>STATUSS i<br>update occ<br>20-bit value<br>CALL is a<br>2<br>2<br>Q2<br>Read literal<br>'k'<7:0>,<br>No  | pushed (<br>= 1, the V<br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa<br>2-cycle ir<br>Q3<br>PUSH F<br>stac  | onto the<br>W, STA<br>so push<br>registers<br>S. If 's'<br>ult). Th<br>ded into<br>astructio | e return<br>TUS and<br>hed into th<br>s, WS,<br>= 0, no<br>en, the<br>o PC<20:<br>on.<br>Q4<br>Read lite<br>'k'<19:8:<br>Write to F<br>No |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode        | (PC + 4) is<br>stack. If 's'<br>BSR registr<br>respective<br>STATUSS<br>update occ<br>20-bit value<br>CALL is a<br>2<br>2<br>2<br>Read literal<br>'k'<7:0>,           | pushed of<br>= 1, the V<br>ers are al<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa<br>2-cycle ir<br>Q3<br>PUSH F<br>stac | onto the<br>W, STA<br>so push<br>registers<br>S. If 's'<br>ult). Th<br>ded into<br>astructio | e return<br>TUS and<br>hed into th<br>s, WS,<br>= 0, no<br>en, the<br>o PC<20:<br>on.<br>Q4<br>Read lite<br>'k'<19:8:<br>Write to F       |

After Instruction

PC = TOS = WS = BSRS = STATUSS = address (THERE) address (HERE + 4) W BSR Status

#### 27.10 Analog Characteristics

| TABLE 27-1: | COMPARATOR SPECIFICATIONS |

|-------------|---------------------------|

|             |                           |

| <b>Operating Conditions:</b> 1.8V < VDD < 5.5V, -40°C < TA < +125°C (unless otherwise stated) |        |                                           |     |     |      |       |                                 |

|-----------------------------------------------------------------------------------------------|--------|-------------------------------------------|-----|-----|------|-------|---------------------------------|

| Param<br>No.                                                                                  | Sym    | Characteristics                           | Min | Тур | Мах  | Units | Comments                        |

| CM01                                                                                          | VIOFF  | Input Offset Voltage                      |     | 3   | 40   | mV    | High-Power mode<br>VREF = VDD/2 |

|                                                                                               |        |                                           | —   | 4   | 60   | mV    | Low-Power mode<br>VREF = VDD/2  |

| CM02                                                                                          | VICM   | Input Common-mode Voltage                 | Vss | _   | Vdd  | V     |                                 |

| CM04*                                                                                         | TRESP  | Response Time <sup>(1)</sup>              | —   | 200 | 400  | ns    | High-Power mode                 |

|                                                                                               |        |                                           | —   | 600 | 3500 | ns    | Low-Power mode                  |

| CM05*                                                                                         | TMC20V | Comparator Mode Change to<br>Output Valid | —   | —   | 10   | μs    |                                 |

These parameters are characterized but not tested. \*

Note 1: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.

#### **TABLE 27-2: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS**

| Param<br>No. | Sym           | Characteristics                        | Min     | Тур    | Max      | Units | Comments                        |

|--------------|---------------|----------------------------------------|---------|--------|----------|-------|---------------------------------|

| CV01*        | CLSB          | Step Size <sup>(2)</sup>               | _       | VDD/32 |          | V     |                                 |

| CV02*        | CACC          | Absolute Accuracy                      | _       | _      | ± 1/2    | LSb   | $\Delta V \text{SRC} \ge 2.0 V$ |

| CV03*        | CR            | Unit Resistor Value (R)                | _       | 5k     | _        | Ω     |                                 |

| CV04*        | Сѕт           | Settling Time <sup>(1)</sup>           | _       |        | 10       | μS    |                                 |

| CV05*        | VSRC+         | DAC Positive Reference                 | VSRC-+2 | _      | Vdd      | V     |                                 |

| CV06*        | VSRC-         | DAC Negative Reference                 | Vss     | —      | VSRC+ -2 | V     |                                 |

| CV07*        | $\Delta VSRC$ | DAC Reference Range<br>(VSRC+ - VSRC-) | 2       | —      | Vdd      | V     |                                 |

These parameters are characterized but not tested.

Note 1: Settling time measured while CVRR = 1 and CVR3:CVR0 transitions from '0000' to '1111'.

2: See Section 22.0 "Digital-to-Analog Converter (DAC) Module" for more information.

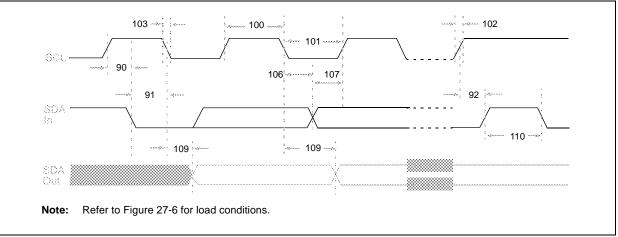

| Param.<br>No. | Symbol  | Characte        | eristic      | Min  | Max | Units | Conditions                   |  |

|---------------|---------|-----------------|--------------|------|-----|-------|------------------------------|--|

| 90            | TSU:STA | Start Condition | 100 kHz mode | 4700 | _   | ns    | Only relevant for Repeated   |  |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       | Start condition              |  |

| 91            | THD:STA | Start Condition | 100 kHz mode | 4000 | _   | ns    | After this period, the first |  |

|               |         | Hold Time       | 400 kHz mode | 600  | _   |       | clock pulse is generated     |  |

| 92            | Tsu:sto | Stop Condition  | 100 kHz mode | 4700 | _   | ns    |                              |  |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       |                              |  |

| 93            | THD:STO | Stop Condition  | 100 kHz mode | 4000 | _   | ns    |                              |  |

|               |         | Hold Time       | 400 kHz mode | 600  |     | 1     |                              |  |

### TABLE 27-15: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

### FIGURE 27-18: I<sup>2</sup>C BUS DATA TIMING

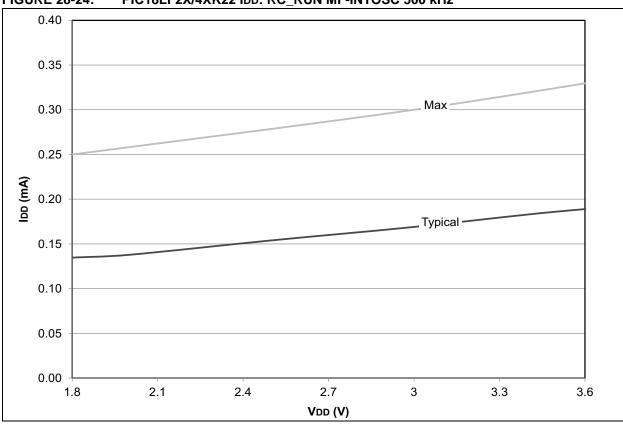

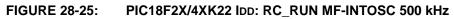

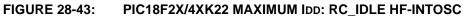

#### FIGURE 28-24: PIC18LF2X/4XK22 IDD: RC\_RUN MF-INTOSC 500 kHz

© 2010-2016 Microchip Technology Inc.

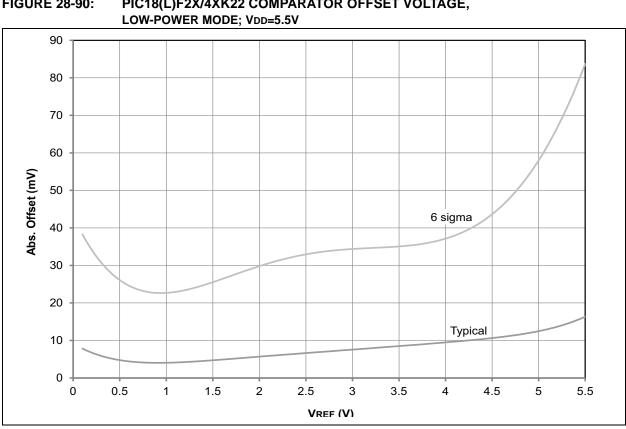

FIGURE 28-91: PIC18(L)F2X/4XK22 COMPARATOR OFFSET VOLTAGE, LOW-POWER MODE; VDD=3.0V

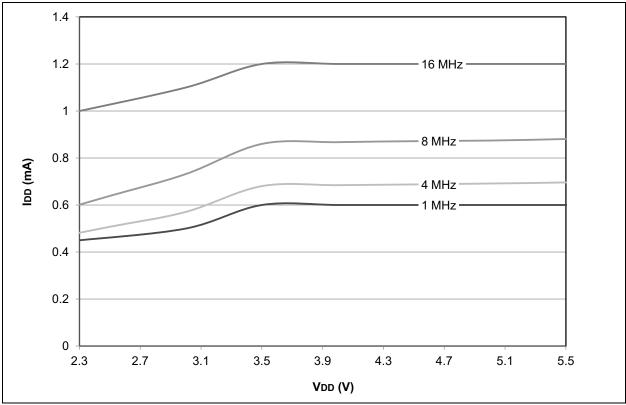

FIGURE 28-90: PIC18(L)F2X/4XK22 COMPARATOR OFFSET VOLTAGE,

#### 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | MILLIMETERS    |          |      |  |  |

|-------------------------|--------|----------------|----------|------|--|--|

| Dimension               | Limits | MIN            | NOM      | MAX  |  |  |

| Number of Pins          | Z      | 28             |          |      |  |  |

| Pitch                   | е      |                | 0.65 BSC |      |  |  |

| Overall Height          | A      | 0.80 0.90 1.00 |          |      |  |  |

| Standoff                | A1     | 0.00           | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3     | 0.20 REF       |          |      |  |  |

| Overall Width           | Ш      | 6.00 BSC       |          |      |  |  |

| Exposed Pad Width       | E2     | 3.65 3.70 4.20 |          |      |  |  |

| Overall Length          | D      | 6.00 BSC       |          |      |  |  |

| Exposed Pad Length      | D2     | 3.65           | 3.70     | 4.20 |  |  |

| Terminal Width          | b      | 0.23           | 0.30     | 0.35 |  |  |

| Terminal Length         | L      | 0.50           | 0.55     | 0.70 |  |  |

| Terminal-to-Exposed Pad | K      | 0.20           | -        | -    |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2