Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (8K x 16)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 768 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k22t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

| OSC Mode               | OSC1 Pin                                              | OSC2 Pin                                              |  |  |

|------------------------|-------------------------------------------------------|-------------------------------------------------------|--|--|

| RC, INTOSC with CLKOUT | Floating, external resistor should pull high          | At logic low (clock/4 output)                         |  |  |

| RC with IO             | Floating, external resistor should pull high          | Configured as PORTA, bit 6                            |  |  |

| INTOSC with IO         | Configured as PORTA, bit 7                            | Configured as PORTA, bit 6                            |  |  |

| EC with IO             | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |  |  |

| EC with CLKOUT         | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |  |  |

| LP, XT, HS             | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |  |  |

TABLE 2-3:OSC1 AND OSC2 PIN STATES IN SLEEP MODE

Note: See Table 4-2 in Section 4.0 "Reset" for time-outs due to Sleep and MCLR Reset.

## 2.11 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS<1:0>) bits of the OSCCON register.

PIC18(L)F2X/4XK22 devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 3.1.2 "Entering Power-Managed Modes"**.

#### 2.11.1 SYSTEM CLOCK SELECT (SCS<1:0>) BITS

The System Clock Select (SCS<1:0>) bits of the OSCCON register select the system clock source that is used for the CPU and peripherals.

- When SCS<1:0> = 00, the system clock source is determined by configuration of the FOSC<3:0> bits in the CONFIG1H Configuration register.

- When SCS<1:0> = 10, the system clock source is chosen by the internal oscillator frequency selected by the INTSRC bit of the OSCTUNE register, the MFIOSEL bit of the OSCCON2 register and the IRCF<2:0> bits of the OSCCON register.

- When SCS<1:0> = 01, the system clock source is the 32.768 kHz secondary oscillator shared with Timer1, Timer3 and Timer5.

After a Reset, the SCS<1:0> bits of the OSCCON register are always cleared.

Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS<1:0> bits of the OSCCON register. The user can monitor the SOSCRUN, MFIOFS and LFIOFS bits of the OSCCON2 register, and the HFIOFS and OSTS bits of the OSCCON register to determine the current system clock source.

#### 2.11.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCCON register indicates whether the system clock is running from the external clock source, as defined by the FOSC<3:0> bits in the CONFIG1H Configuration register, or from the internal clock source. In particular, when the primary oscillator is the source of the primary clock, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes.

## 2.11.3 CLOCK SWITCH TIMING

When switching between one oscillator and another, the new oscillator may not be operating which saves power (see Figure 2-9). If this is the case, there is a delay after the SCS<1:0> bits of the OSCCON register are modified before the frequency change takes place. The OSTS and IOFS bits of the OSCCON register will reflect the current active status of the external and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- 1. SCS<1:0> bits of the OSCCON register are modified.

- 2. The old clock continues to operate until the new clock is ready.

- 3. Clock switch circuitry waits for two consecutive rising edges of the old clock after the new clock ready signal goes true.

- 4. The system clock is held low starting at the next falling edge of the old clock.

- 5. Clock switch circuitry waits for an additional two rising edges of the new clock.

- 6. On the next falling edge of the new clock the low hold on the system clock is released and new clock is switched in as the system clock.

- 7. Clock switch is complete.

See Figure 2-1 for more details.

If the HFINTOSC is the source of both the old and new frequency, there is no start-up delay before the new frequency is active. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in **Section 27.0 "Electrical Specifications**", under AC Specifications (Oscillator Module).

## 2.12 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device.

This mode allows the application to wake-up from Sleep, perform a few instructions using the HFINTOSC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

Note: Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCCON register to remain clear.

When the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) is enabled (see **Section 2.5.1 "Oscillator Start-up Timer (OST)**"). The OST will suspend program execution until 1024 oscillations are counted. Two-Speed Start-up mode minimizes the delay in code execution by operating from the internal oscillator as the OST is counting. When the OST count reaches 1024 and the OSTS bit of the OSCCON register is set, program execution switches to the external oscillator.

#### 2.12.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is enabled when all of the following settings are configured as noted:

- Two-Speed Start-up mode is enabled when the IESO of the CONFIG1H Configuration register is set.

- SCS<1:0> (of the OSCCON register) = 00.

- FOSC<2:0> bits of the CONFIG1H Configuration register are configured for LP, XT or HS mode.

Two-Speed Start-up mode becomes active after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

| R/W-0           | R/W-0         | U-0              | R/W-0          | R/W-0            | R/W-0                               | R/W-0           | R/W-0  |

|-----------------|---------------|------------------|----------------|------------------|-------------------------------------|-----------------|--------|

| MSSP2MD         | MSSP1MD       | —                | CCP5MD         | CCP4MD           | CCP3MD                              | CCP2MD          | CCP1MD |

| bit 7           |               |                  |                |                  |                                     |                 | bit (  |

| Legend:         |               |                  |                |                  |                                     |                 |        |

| R = Readable    | bit           | W = Writable     | bit            | U = Unimpler     | mented bit, read                    | d as '0'        |        |

| -n = Value at F | POR           | '1' = Bit is set |                | '0' = Bit is cle | ared                                | x = Bit is unkr | nown   |

| bit 7           | MSSP2MD: N    | ISSP2 Periphe    | eral Module Di | sable Control I  | bit                                 |                 |        |

|                 | 1 = Module is | s disabled, Clo  | ck Source is d | lisconnected, r  | nodule does no<br>lule draws digita | 0 1             | ower   |

| bit 6           | MSSP1MD: N    | ISSP1 Periphe    | eral Module Di | sable Control I  | bit                                 |                 |        |

|                 |               |                  |                |                  | nodule does no<br>lule draws digita | • •             | ower   |

| bit 5           | Unimplemen    | ted: Read as '   | 0'             |                  |                                     |                 |        |

| bit 4           | CCP5MD: CC    | P5 Peripheral    | Module Disab   | ole Control bit  |                                     |                 |        |

|                 |               |                  |                |                  | nodule does no<br>lule draws digita | 0 1             | ower   |

| bit 3           | CCP4MD: CC    | P4 Peripheral    | Module Disab   | ole Control bit  |                                     |                 |        |

|                 |               |                  |                |                  | nodule does no<br>lule draws digita |                 | ower   |

| bit 2           | CCP3MD: CC    | P3 Peripheral    | Module Disab   | le Control bit   |                                     |                 |        |

|                 |               |                  |                | ,                | nodule does no<br>lule draws digita | 0 1             | ower   |

| bit 1           | CCP2MD: CC    | P2 Peripheral    | Module Disab   | le Control bit   |                                     |                 |        |

|                 |               |                  |                |                  | nodule does no<br>lule draws digita | • .             | ower   |

| bit 0           | CCP1MD: CC    | P1 Peripheral    | Module Disab   | ole Control bit  |                                     |                 |        |

|                 |               |                  |                |                  | nodule does no<br>lule draws digita | 0 1             | ower   |

|                 |               |                  |                |                  |                                     |                 |        |

| <b>D</b> . (1)( |       | Port Fun               | ction Priority by P    | ort Pin              |                      |

|-----------------|-------|------------------------|------------------------|----------------------|----------------------|

| Port bit        | PORTA | PORTB                  | PORTC                  | PORTD <sup>(2)</sup> | PORTE <sup>(2)</sup> |

| 5               | SRNQ  | CCP3 <sup>(3)</sup>    | SDO1                   | P1B                  |                      |

|                 | C2OUT | P3A <sup>(3)</sup>     | RC5                    | RD5                  |                      |

|                 | RA5   | P2B <sup>(1)(4)</sup>  |                        |                      |                      |

|                 |       | RB5                    |                        |                      |                      |

| 6               | OSC2  | PGC                    | TX1/CK1                | TX2/CK2              |                      |

|                 | CLKO  | TX2/CK2 <sup>(1)</sup> | CCP3 <sup>(1)(7)</sup> | P1C                  |                      |

|                 | RA6   | RB6                    | P3A <sup>(1)(7)</sup>  | RD6                  |                      |

|                 |       | ICDCK                  | RC6                    |                      |                      |

| 7               | RA7   |                        |                        |                      |                      |

|                 | OSC1  | PGD                    | RX1/DT1                | RX2/DT2              |                      |

|                 | RA7   | RX2/DT2 <sup>(1)</sup> | P3B <sup>(1)</sup>     | P1D                  |                      |

|                 |       | RB7                    | RC7                    | RD7                  |                      |

|                 |       | ICDDT                  |                        |                      |                      |

#### TABLE 10-4: PORT PIN FUNCTION PRIORITY (CONTINUED)

Note 1: PIC18(L)F2XK22 devices.

2: PIC18(L)F4XK22 devices.

3: Function default pin.

4: Function default pin (28-pin devices).

5: Function default pin (40/44-pin devices).

6: Function alternate pin.

7: Function alternate pin (28-pin devices).

8: Function alternate pin (40/44-pin devices)

|       |       |             |                   | •••••           |                           |       |

|-------|-------|-------------|-------------------|-----------------|---------------------------|-------|

| R/W-1 | R/W-1 | R/W-1       | U-0               | U-0             | U-0                       | U-0   |

| IOCB6 | IOCB5 | IOCB4       | —                 | —               | —                         | —     |

|       |       |             |                   |                 |                           | bit 0 |

|       |       |             |                   |                 |                           |       |

|       | R/W-1 | R/W-1 R/W-1 | R/W-1 R/W-1 R/W-1 | R/W-1 R/W-1 U-0 | R/W-1 R/W-1 R/W-1 U-0 U-0 |       |

#### REGISTER 10-13: IOCB: INTERRUPT-ON-CHANGE PORTB CONTROL REGISTER

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-4 **IOCB<7:4>:** Interrupt-on-Change PORTB control bits

1 = Interrupt-on-change enabled<sup>(1)</sup>

0 = Interrupt-on-change disabled

**Note 1:** Interrupt-on-change requires that the RBIE bit (INTCON<3>) is set.

## REGISTER 10-14: SLRCON: SLEW RATE CONTROL REGISTER

| U-0   | U-0 | U-0 | R/W-1               | R/W-1               | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|---------------------|---------------------|-------|-------|-------|

| —     | —   | _   | SLRE <sup>(1)</sup> | SLRD <sup>(1)</sup> | SLRC  | SLRB  | SLRA  |

| bit 7 |     |     |                     |                     |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                    |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 4   | SLRE: PORTE Slew Rate Control bit <sup>(1)</sup>                                                                                              |  |

|         | <ul><li>1 = All outputs on PORTE slew at a limited rate</li><li>0 = All outputs on PORTE slew at the standard rate</li></ul>                  |  |

| bit 3   | SLRD: PORTD Slew Rate Control bit <sup>(1)</sup>                                                                                              |  |

|         | <ul><li>1 = All outputs on PORTD slew at a limited rate</li><li>0 = All outputs on PORTD slew at the standard rate</li></ul>                  |  |

| bit 2   | SLRC: PORTC Slew Rate Control bit                                                                                                             |  |

|         | <ul><li>1 = All outputs on PORTC slew at a limited rate</li><li>0 = All outputs on PORTC slew at the standard rate</li></ul>                  |  |

| bit 1   | SLRB: PORTB Slew Rate Control bit                                                                                                             |  |

|         | <ul><li>1 = All outputs on PORTB slew at a limited rate</li><li>0 = All outputs on PORTB slew at the standard rate</li></ul>                  |  |

| bit 0   | SLRA: PORTA Slew Rate Control bit                                                                                                             |  |

|         | <ul> <li>1 = All outputs on PORTA slew at a limited rate<sup>(2)</sup></li> <li>0 = All outputs on PORTA slew at the standard rate</li> </ul> |  |

| Note 1. | These bits are available on PIC18(I )F4XK22 devices                                                                                           |  |

**Note 1:** These bits are available on PIC18(L)F4XK22 devices.

2: The slew rate of RA6 defaults to standard rate when the pin is used as CLKOUT.

### 12.8 Timer1/3/5 Interrupt

The Timer1/3/5 register pair (TMRxH:TMRxL) increments to FFFFh and rolls over to 0000h. When Timer1/3/5 rolls over, the Timer1/3/5 interrupt flag bit of the PIR1/2/5 register is set. To enable the interrupt on rollover, you must set these bits:

- TMRxON bit of the TxCON register

- TMRxIE bits of the PIE1, PIE2 or PIE5 registers

- PEIE/GIEL bit of the INTCON register

- GIE/GIEH bit of the INTCON register

The interrupt is cleared by clearing the TMRxIF bit in the Interrupt Service Routine.

For more information on selecting high or low priority status for the Timer1/3/5 Overflow Interrupt, see **Section 9.0 "Interrupts"**.

| Note: | The TMRxH:TMRxL register pair and the |

|-------|---------------------------------------|

|       | TMRxIF bit should be cleared before   |

|       | enabling interrupts.                  |

## 12.9 Timer1/3/5 Operation During Sleep

Timer1/3/5 can only operate during Sleep when set up in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMRxON bit of the TxCON register must be set

- TMRxIE bit of the PIE1/2/5 register must be set

- PEIE/GIEL bit of the INTCON register must be set

- TxSYNC bit of the TxCON register must be set

- TMRxCS bits of the TxCON register must be configured

- TxSOSCEN bit of the TxCON register must be configured

The device will wake-up on an overflow and execute the next instruction. If the GIE/GIEH bit of the INTCON register is set, the device will call the Interrupt Service Routine.

The secondary oscillator will continue to operate in Sleep regardless of the  $\overline{\text{TxSYNC}}$  bit setting.

### 12.10 ECCP/CCP Capture/Compare Time Base

The CCP modules use the TMRxH:TMRxL register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMRxH:TMRxL register pair is copied into the CCPRxH:CCPRxL register pair on a configured event.

In Compare mode, an event is triggered when the value CCPRxH:CCPRxL register pair matches the value in the TMRxH:TMRxL register pair. This event can be a Special Event Trigger.

For more information, see Section 14.0 "Capture/Compare/PWM Modules".

## 12.11 ECCP/CCP Special Event Trigger

When any of the CCP's are configured to trigger a special event, the trigger will clear the TMRxH:TMRxL register pair. This special event does not cause a Timer1/3/5 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPRxH:CCPRxL register pair becomes the period register for Timer1/3/5.

Timer1/3/5 should be synchronized and FOSC/4 should be selected as the clock source in order to utilize the Special Event Trigger. Asynchronous operation of Timer1/3/5 can cause a Special Event Trigger to be missed.

In the event that a write to TMRxH or TMRxL coincides with a Special Event Trigger from the CCP, the write will take precedence.

For more information, see **Section 17.2.8** "**Special Event Trigger**".

| Name                 | Bit 7   | Bit 6   |                 | Bit 4           |                               | Bit 2                 |                       | Bit 0                 | Register |

|----------------------|---------|---------|-----------------|-----------------|-------------------------------|-----------------------|-----------------------|-----------------------|----------|

| Name                 | Bit /   | BIT 6   | Bit 5           | Bit 4           | Bit 3                         | Bit 2                 | Bit 1                 | Bit U                 | on Page  |

| PIE2                 | OSCFIE  | C1IE    | C2IE            | EEIE            | BCL1IE                        | HLVDIE                | TMR3IE                | CCP2IE                | 118      |

| PIE4                 | _       | —       | _               | —               | —                             | CCP5IE                | CCP4IE                | CCP3IE                | 120      |

| PIR1                 | _       | ADIF    | RC1IF           | TX1IF           | SSP1IF                        | CCP1IF                | TMR2IF                | TMR1IF                | 112      |

| PIR2                 | OSCFIF  | C1IF    | C2IF            | EEIF            | BCL1IF                        | HLVDIF                | TMR3IF                | CCP2IF                | 113      |

| PIR4                 | —       | —       | _               | —               | —                             | CCP5IF                | CCP4IF                | CCP3IF                | 115      |

| PMD0                 | UART2MD | UART1MD | TMR6MD          | TMR5MD          | TMR4MD                        | TMR3MD                | TMR2MD                | TMR1MD                | 52       |

| PMD1                 | MSSP2MD | MSSP1MD | _               | CCP5MD          | CCP4MD                        | CCP3MD                | CCP2MD                | CCP1MD                | 53       |

| T1CON                | TMR1C   | S<1:0>  | T1CKP           | S<1:0>          | T1SOSCEN                      | T1SYNC                | T1RD16                | TMR10N                | 166      |

| T1GCON               | TMR1GE  | T1GPOL  | T1GTM           | T1GSPM          | T1GGO/DONE                    | T1GVAL                | T1GSS<1:0>            |                       | 167      |

| T3CON                | TMR3C   | S<1:0>  | T3CKP           | S<1:0>          | T3SOSCEN                      | T3SYNC                | T3RD16 TMR3ON         |                       | 166      |

| T3GCON               | TMR3GE  | T3GPOL  | T3GTM           | T3GSPM          | T3GGO/DONE                    | T3GVAL                | T3GSS<1:0>            |                       | 167      |

| T5CON                | TMR5C   | S<1:0>  | T5CKP           | S<1:0>          | T5SOSCEN T5SYNC T5RD16 TMR5ON |                       |                       | TMR5ON                | 166      |

| T5GCON               | TMR5GE  | T5GPOL  | T5GTM           | T5GSPM          | T5GGO/DONE                    | T5GVAL                | T5GSS                 | <1:0>                 | 167      |

| TMR1H                |         | Holding | Register for th | e Most Signifi  | cant Byte of the 10           | 6-bit TMR1 Re         | egister               |                       | _        |

| TMR1L                |         |         | Least Sign      | ificant Byte of | the 16-bit TMR1 I             | Register              |                       |                       | _        |

| TMR3H                |         | Holding | Register for th | e Most Signifi  | cant Byte of the 10           | 6-bit TMR3 Re         | egister               |                       | —        |

| TMR3L                |         |         | Least Sign      | ificant Byte of | the 16-bit TMR3 I             | Register              |                       |                       | —        |

| TMR5H                |         | Holding | Register for th | e Most Signifi  | cant Byte of the 10           | 6-bit TMR5 Re         | egister               |                       | —        |

| TMR5L                |         |         | Least Sign      | ificant Byte of | the 16-bit TMR5 I             | Register              |                       |                       | —        |

| TRISA                | TRISA7  | TRISA6  | TRISA5          | TRISA4          | TRISA3                        | TRISA2                | TRISA1                | TRISA0                | 151      |

| TRISB                | TRISB7  | TRISB6  | TRISB5          | TRISB4          | TRISB3                        | TRISB2                | TRISB1                | TRISB0                | 151      |

| TRISC                | TRISC7  | TRISC6  | TRISC5          | TRISC4          | TRISC3                        | TRISC2                | TRISC1                | TRISC0                | 151      |

| TRISD <sup>(1)</sup> | TRISD7  | TRISD6  | TRISD5          | TRISD4          | TRISD3                        | TRISD2                | TRISD1                | TRISD0                | 151      |

| TRISE                | WPUE3   | —       | —               | —               | —                             | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 151      |

#### TABLE 14-3: REGISTERS ASSOCIATED WITH CAPTURE (CONTINUED)

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Capture mode.

**Note 1:** These registers/bits are available on PIC18(L)F4XK22 devices.

### TABLE 14-4: CONFIGURATION REGISTERS ASSOCIATED WITH CAPTURE

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| CONFIG3H | MCLRE | —     | P2BMX | T3CMX | HFOFST | CCP3MX | PBADEN | CCP2MX | 348                 |

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Capture mode.

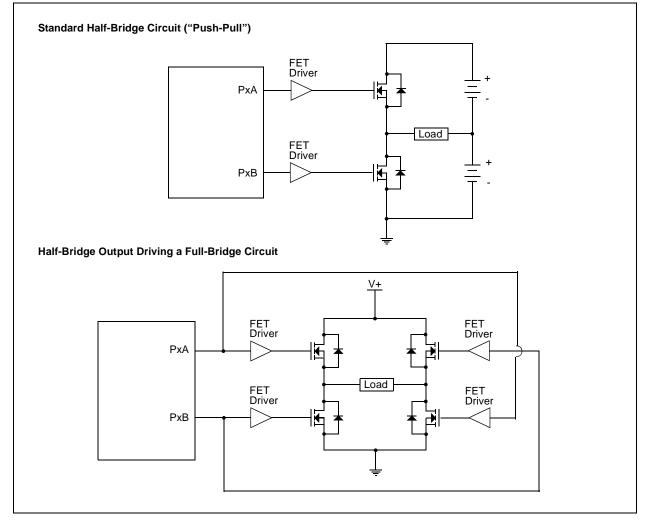

### 14.4.1 HALF-BRIDGE MODE

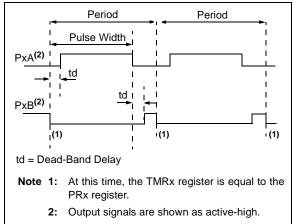

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCPx/PxA pin, while the complementary PWM output signal is output on the PxB pin (see Figure 14-9). This mode can be used for half-bridge applications, as shown in Figure 14-9, or for full-bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in halfbridge power devices. The value of the PDC<6:0> bits of the PWMxCON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 14.4.5 "Programmable Dead-Band Delay Mode"** for more details of the dead-band delay operations. Since the PxA and PxB outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure PxA and PxB as outputs.

#### FIGURE 14-8: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

### FIGURE 14-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

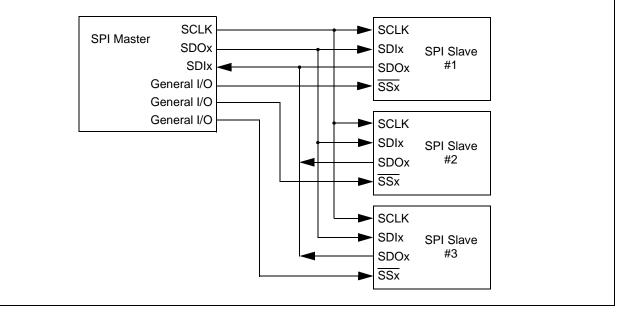

### FIGURE 15-4: SPI MASTER AND MULTIPLE SLAVE CONNECTION

#### 15.2.1 SPI MODE REGISTERS

The MSSPx module has five registers for SPI mode operation. These are:

- MSSPx STATUS register (SSPxSTAT)

- MSSPx Control register 1 (SSPxCON1)

- MSSPx Control register 3 (SSPxCON3)

- MSSPx Data Buffer register (SSPxBUF)

- MSSPx Address register (SSPxADD)

- MSSPx Shift register (SSPxSR) (Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and STATUS registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower 6 bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In one SPI Master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 15.7 "Baud Rate Generator"**.

SSPxSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPxSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPxSR and SSPxBUF together create a buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

### 15.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCKx is the clock output)

- Slave mode (SCKx is the clock input)

- Clock Polarity (Idle state of SCKx)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCKx)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

To enable the serial port, SSPx Enable bit, SSPxEN of the SSPxCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPxEN bit, re-initialize the SSPxCONx registers and then set the SSP<u>xEN</u> bit. This configures the SDIx, SDOx, SCKx and SSx pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- SDIx must have corresponding TRIS bit set

- SDOx must have corresponding TRIS bit cleared

- SCKx (Master mode) must have corresponding TRIS bit cleared

- SCKx (Slave mode) must have corresponding TRIS bit set

- SSx must have corresponding TRIS bit set

## 16.4.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCONx register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGHx:SPBRGx register pair. After the ABDOVF has been set, the counter continues to count until the fifth rising edge is detected on the RXx/DTx pin. Upon detecting the fifth RXx/DTx edge, the hardware will set the RCxIF interrupt flag and clear the ABDEN bit of the BAUDCONx register. The RCxIF flag can be subsequently cleared by reading the RCREGx. The ABDOVF flag can be cleared by software directly.

To terminate the auto-baud process before the RCxIF flag is set, clear the ABDEN bit then clear the ABDOVF bit. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

#### 16.4.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RXx/DTx line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCONx register. Once set, the normal receive sequence on RXx/DTx is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RXx/DTx line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCxIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 16-7), and asynchronously if the device is in Sleep mode (Figure 16-8). The interrupt condition is cleared by reading the RCREGx register.

The WUE bit is automatically cleared by the low-to-high transition on the RXx line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 16.4.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be 10 or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCxIF bit. The WUE bit is cleared by hardware by a rising edge on RXx/DTx. The interrupt condition is then cleared by software by reading the RCREGx register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

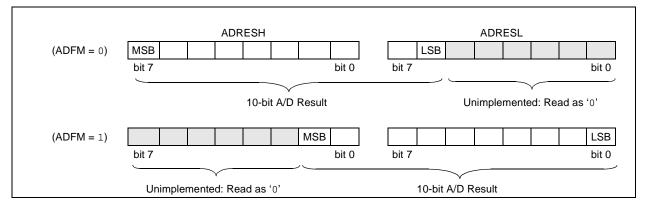

### 17.1.7 RESULT FORMATTING

The 10-bit A/D conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON2 register controls the output format.

Figure 17-2 shows the two output formats.

## FIGURE 17-2: 10-BIT A/D CONVERSION RESULT FORMAT

## 17.3 Register Definitions: ADC Control

Note: Analog pin control is determined by the ANSELx registers (see Register 10-2)

#### REGISTER 17-1: ADCON0: A/D CONTROL REGISTER 0

| U-0   | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0   | R/W-0 |

|-------|-------|-------|----------|-------|-------|---------|-------|

| —     |       |       | CHS<4:0> |       |       | GO/DONE | ADON  |

| bit 7 |       |       |          |       |       |         | bit 0 |

| Legend:       |                    |                                  |                                      |                    |

|---------------|--------------------|----------------------------------|--------------------------------------|--------------------|

| R = Readable  | e bit              | W = Writable bit                 | U = Unimplemented bit, re            | ead as '0'         |

| -n = Value at | POR                | '1' = Bit is set                 | '0' = Bit is cleared                 | x = Bit is unknown |

|               |                    |                                  |                                      |                    |

| bit 7         | Unimple            | mented: Read as '0'              |                                      |                    |

| bit 6-2       | CHS<4:0            | )>: Analog Channel Select bits   | ;                                    |                    |

|               | 00000 =            |                                  |                                      |                    |

|               | 00001 =            |                                  |                                      |                    |

|               | 00010 =            |                                  |                                      |                    |

|               | 00011 =            |                                  |                                      |                    |

|               | 00100 =            |                                  |                                      |                    |

|               | 00101 =            |                                  |                                      |                    |

|               | 00110 =            |                                  |                                      |                    |

|               | 00111 =            |                                  |                                      |                    |

|               | 01000 =            |                                  |                                      |                    |

|               | 01001 =<br>01010 = |                                  |                                      |                    |

|               | 01010 = 01011 =    |                                  |                                      |                    |

|               | 01011 =            |                                  |                                      |                    |

|               | 01100 =            |                                  |                                      |                    |

|               | 01101 =            |                                  |                                      |                    |

|               | 01111 =            |                                  |                                      |                    |

|               | 10000 =            |                                  |                                      |                    |

|               | 10001 =            |                                  |                                      |                    |

|               | 10010 =            |                                  |                                      |                    |

|               | 10011 =            | AN19                             |                                      |                    |

|               | 10100 =            | AN20 <sup>(1)</sup>              |                                      |                    |

|               | 10101 =            |                                  |                                      |                    |

|               | 10110 =            | AN22 <sup>(1)</sup>              |                                      |                    |

|               | 10111 =            |                                  |                                      |                    |

|               | 11000 =            |                                  |                                      |                    |

|               | 11001 =            |                                  |                                      |                    |

|               | 11010 =            |                                  |                                      |                    |

|               | 11011 =            |                                  |                                      |                    |

|               |                    | Reserved                         |                                      |                    |

|               | 11101 =            |                                  |                                      |                    |

|               | 11110 =            |                                  |                                      | (2)                |

|               |                    | _                                | 96V Volt Fixed Voltage Reference     | )·-/               |

| bit 1         |                    | IE: A/D Conversion Status bit    |                                      |                    |

|               |                    | , , ,                            | tting this bit starts an A/D convers |                    |

|               |                    | , j                              | ardware when the A/D conversion      | has completed.     |

|               | 0 = A/D            | conversion completed/not in prog | gress                                |                    |

| bit 0         | ADON: A            | ADC Enable bit                   |                                      |                    |

|               | 1 = ADC            | is enabled                       |                                      |                    |

|               | 0 = ADC            | is disabled and consumes no or   | perating current                     |                    |

2: Allow greater than 15  $\mu s$  acquisition time when measuring the Fixed Voltage Reference.

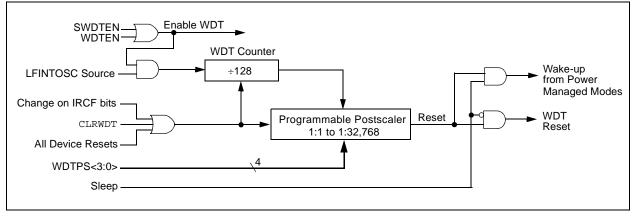

## 24.3 Watchdog Timer (WDT)

For PIC18(L)F2X/4XK22 devices, the WDT is driven by the LFINTOSC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the LFINTOSC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration Register 2H. Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: a SLEEP or CLRWDT instruction is executed, the IRCF bits of the OSCCON register are changed or a clock failure has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: Changing the setting of the IRCF bits of the OSCCON register clears the WDT and postscaler counts.

- **3:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

#### FIGURE 24-1: WDT BLOCK DIAGRAM

| POP                                  | Pop Top of Return Stack                                                                                                                                                                                                                                                                    | PUSH                                      | Push Top of Return Stack                                                                                                                                                                                                                    |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                              | POP                                                                                                                                                                                                                                                                                        | Syntax:                                   | PUSH                                                                                                                                                                                                                                        |

| Operands:                            | None                                                                                                                                                                                                                                                                                       | Operands:                                 | None                                                                                                                                                                                                                                        |

| Operation:                           | $(TOS) \rightarrow bit bucket$                                                                                                                                                                                                                                                             | Operation:                                | $(PC + 2) \rightarrow TOS$                                                                                                                                                                                                                  |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                       | Status Affected:                          | None                                                                                                                                                                                                                                        |

| Encoding:                            | 0000 0000 0000 0110                                                                                                                                                                                                                                                                        | Encoding:                                 | 0000 0000 0000 0101                                                                                                                                                                                                                         |

| Description:                         | The TOS value is pulled off the return<br>stack and is discarded. The TOS value<br>then becomes the previous value that<br>was pushed onto the return stack.<br>This instruction is provided to enable<br>the user to properly manage the return<br>stack to incorporate a software stack. | Description:<br>Words:                    | The PC + 2 is pushed onto the top of<br>the return stack. The previous TOS<br>value is pushed down on the stack.<br>This instruction allows implementing a<br>software stack by modifying TOS and<br>then pushing it onto the return stack. |

| Words:                               | 1                                                                                                                                                                                                                                                                                          | Cycles:                                   | 1                                                                                                                                                                                                                                           |

| Cycles:                              | 1                                                                                                                                                                                                                                                                                          | Q Cycle Activity:                         |                                                                                                                                                                                                                                             |

| Q Cycle Activity:                    |                                                                                                                                                                                                                                                                                            | Q1                                        | Q2 Q3 Q4                                                                                                                                                                                                                                    |

| Q1<br>Decode                         | Q2Q3Q4NoPOP TOSNooperationvalueoperation                                                                                                                                                                                                                                                   | Decode                                    | PUSH         No         No           PC + 2 onto         operation         operation           return stack                                                                                                                                 |

| Example:                             | POP<br>Goto new                                                                                                                                                                                                                                                                            | Example:<br>Before Instruc                | PUSH                                                                                                                                                                                                                                        |

| Before Instruct<br>TOS<br>Stack (1 I | ion<br>= 0031A2h<br>evel down) = 014332h                                                                                                                                                                                                                                                   | TOS<br>PC                                 | = 345Ah<br>= 0124h                                                                                                                                                                                                                          |

| After Instructio<br>TOS<br>PC        | n<br>= 014332h<br>= NEW                                                                                                                                                                                                                                                                    | After Instructio<br>PC<br>TOS<br>Stack (1 | on<br>= 0126h<br>= 0126h<br>level down) = 345Ah                                                                                                                                                                                             |

| RET   | FIE                                                     | Return fr                                                                                                                                      | om Inte                                                                                               | rrupt                                                                                                               |                                                                                        |

|-------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Synta | ax:                                                     | RETFIE {                                                                                                                                       | s}                                                                                                    |                                                                                                                     |                                                                                        |

| Oper  | ands:                                                   | $s \in [0,1]$                                                                                                                                  |                                                                                                       |                                                                                                                     |                                                                                        |

| Oper  | ration:                                                 | $(TOS) \rightarrow P$<br>$1 \rightarrow GIE/G$<br>if s = 1<br>$(WS) \rightarrow W$<br>(STATUSS)<br>$(BSRS) \rightarrow$<br>PCLATU, F           | iIEH or Pf<br>,<br>) → Statu<br>BSR,                                                                  | S,                                                                                                                  | nged.                                                                                  |

| Statu | is Affected:                                            | GIE/GIEH,                                                                                                                                      | PEIE/GI                                                                                               | EL.                                                                                                                 |                                                                                        |

| Enco  | oding:                                                  | 0000                                                                                                                                           | 0000                                                                                                  | 0001                                                                                                                | 000s                                                                                   |

| Desc  | ription:                                                | Return fror<br>and Top-of<br>the PC. Int<br>setting eith<br>global inter<br>contents of<br>STATUSS<br>their corres<br>STATUS ar<br>of these re | -Stack (TC<br>errupts ar<br>er the hig<br>rupt enab<br>t the shad<br>and BSR<br>sponding<br>nd BSR. I | DS) is loa<br>re enabled<br>h or low p<br>ble bit. If 's<br>low registe<br>S, are loa<br>registers,<br>f 's' = 0, r | ded into<br>d by<br>priority<br>s' = 1, the<br>ers, WS,<br>ded into<br>W,<br>no update |

| Word  | ds:                                                     | 1                                                                                                                                              |                                                                                                       |                                                                                                                     |                                                                                        |

| Cycle | es:                                                     | 2                                                                                                                                              |                                                                                                       |                                                                                                                     |                                                                                        |

| QC    | ycle Activity:                                          |                                                                                                                                                |                                                                                                       |                                                                                                                     |                                                                                        |

|       | Q1                                                      | Q2                                                                                                                                             | Q3                                                                                                    |                                                                                                                     | Q4                                                                                     |

|       | Decode                                                  | No<br>operation                                                                                                                                | No<br>operat                                                                                          | tion fro                                                                                                            | OP PC<br>om stack<br>t GIEH or<br>GIEL                                                 |

|       | No                                                      | No                                                                                                                                             | No                                                                                                    |                                                                                                                     | No                                                                                     |

|       | operation                                               | operation                                                                                                                                      | operat                                                                                                | ion o                                                                                                               | peration                                                                               |

| Exan  | nple:                                                   | RETFIE                                                                                                                                         | 1                                                                                                     |                                                                                                                     |                                                                                        |

|       | After Interrupt<br>PC<br>W<br>BSR<br>Status<br>GIE/GIEF | I, PEIE/GIEL                                                                                                                                   | = V<br>= B                                                                                            | OS<br>VS<br>SRS<br>TATUSS                                                                                           |                                                                                        |

| ds:<br>on:<br>Affected:<br>ng:<br>tion:<br>le Activity:<br>Q1<br>Decode | RETLW k<br>$0 \le k \le 255$<br>$k \rightarrow W$ ,<br>(TOS) $\rightarrow$ PC<br>PCLATU, P<br>None<br>0000<br>W is loaded<br>program co<br>of the stack<br>high addres<br>unchanged.<br>1<br>2<br>Q2<br>Read<br>literal 'k' | 1100<br>with the 8<br>unter is loa<br>(the return<br>is latch (PC                                                     | kkkk<br>3-bit liter<br>aded fro<br>n addres<br>CLATH)<br>s F                                                                              | kkkk<br>al 'k'. Th<br>m the to<br>ss). The<br>remains<br>Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| on:<br>Affected:<br>ng:<br>ition:<br>le Activity:<br>Q1                 | $k \rightarrow W$ ,<br>(TOS) $\rightarrow$ PC<br>PCLATU, P<br>None<br>W is loaded<br>program co<br>of the stack<br>high addres<br>unchanged.<br>1<br>2<br>Q2<br>Read                                                        | CLATH and<br>1100<br>I with the 8<br>unter is loa<br>(the return<br>is latch (PC)<br>Q3<br>Proces                     | kkkk<br>3-bit liter<br>aded fro<br>n addres<br>CLATH)<br>s F                                                                              | kkkk<br>al 'k'. Th<br>m the to<br>ss). The<br>remains<br>Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Affected:<br>ng:<br>ntion:<br>le Activity:<br>Q1                        | (TOS) → P0<br>PCLATU, P<br>None<br>W is loaded<br>program co<br>of the stack<br>high addres<br>unchanged.<br>1<br>2<br>Q2<br>Read                                                                                           | CLATH and<br>1100<br>I with the 8<br>unter is loa<br>(the return<br>is latch (PC)<br>Q3<br>Proces                     | kkkk<br>3-bit liter<br>aded fro<br>n addres<br>CLATH)<br>s F                                                                              | kkkk<br>al 'k'. Th<br>m the to<br>ss). The<br>remains<br>Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ng:<br>htion:<br>le Activity:<br>Q1                                     | 0000<br>W is loaded<br>program co<br>of the stack<br>high addres<br>unchanged.<br>1<br>2<br>Q2<br>Read                                                                                                                      | l with the 8<br>unter is loa<br>(the return<br>is latch (PC)<br>Q3<br>Proces                                          | 3-bit liter<br>aded fro<br>n addres<br>CLATH)<br>s F                                                                                      | al 'k'. The to the total set. The term and the total set. The term and the total set. The total set to the total set total set. The total set tota |

| le Activity:                                                            | W is loaded<br>program co<br>of the stack<br>high addres<br>unchanged.<br>1<br>2<br>Q2<br>Read                                                                                                                              | l with the 8<br>unter is loa<br>(the return<br>is latch (PC)<br>Q3<br>Proces                                          | 3-bit liter<br>aded fro<br>n addres<br>CLATH)<br>s F                                                                                      | al 'k'. The to the total set. The term and the total set. The term and the total set. The total set to the total set total set. The total set tota |