Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

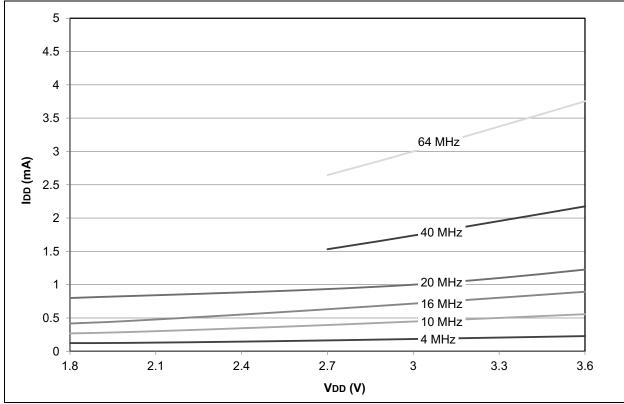

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (8K x 16)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 768 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k22t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 5-2:       REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES (CONTINUED) |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | <u>Value on</u><br>POR, BOR |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------------|

| F3Ah    | ANSELC | ANSC7 | ANSC6 | ANSC5 | ANSC4 | ANSC3 | ANSC2 | _     |       | 1111 11                     |

| F39h    | ANSELB | _     | _     | ANSB5 | ANSB4 | ANSB3 | ANSB2 | ANSB1 | ANSB0 | 11 1111                     |

| F38h    | ANSELA |       | -     | ANSA5 |       | ANSA3 | ANSA2 | ANSA1 | ANSA0 | 1- 1111                     |

**Legend:** x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: PIC18(L)F4XK22 devices only.

2: PIC18(L)F2XK22 devices only.

3: PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

The PLUSW register can be used to implement a form of indexed addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

#### 5.6.3.3 Operations by FSRs on FSRs

Indirect addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to either the INDF2 or POSTDEC2 register will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by indirect addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

## 5.7 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the introduction of a new addressing mode for the data memory space.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect addressing with FSR0 and FSR1 also remain unchanged.

### 5.7.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of indirect addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of indexed addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0) and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

#### 5.7.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use direct addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 5-11.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 25.2.1** "Extended Instruction Syntax".

<sup>© 2010-2016</sup> Microchip Technology Inc.

#### 6.4 Reading the Flash Program Memory

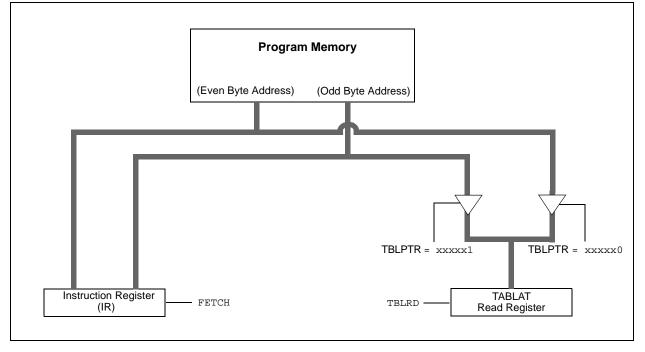

The TBLRD instruction retrieves data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation. The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU |   | Load TBLPTR with the base<br>address of the word |

|-----------|----------------|----------------------------|---|--------------------------------------------------|

|           | MOVLW          | CODE_ADDR_HIGH             | ' | address of the word                              |

|           | MOVWF          | TBLPTRH                    |   |                                                  |

|           |                |                            |   |                                                  |

|           | MOVLW          | CODE_ADDR_LOW              |   |                                                  |

|           | MOVWF          | TBLPTRL                    |   |                                                  |

| READ_WORD |                |                            |   |                                                  |

|           | TBLRD*+        |                            | ; | read into TABLAT and increment                   |

|           | MOVF           | TABLAT, W                  | ; | get data                                         |

|           | MOVWF          | WORD_EVEN                  |   |                                                  |

|           | TBLRD*+        |                            | ; | read into TABLAT and increment                   |

|           | MOVFW          | TABLAT, W                  | ; | get data                                         |

|           | MOVF           | WORD_ODD                   |   |                                                  |

|           |                |                            |   |                                                  |

| U-0                                                                  | U-0                                                                        | U-0                                          | U-0             | U-0             | R/W-0    | R/W-0  | R/W-0  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|-----------------|-----------------|----------|--------|--------|--|--|--|--|--|--|--|

| _                                                                    | —                                                                          | —                                            | —               | —               | TMR6IF   | TMR5IF | TMR4IF |  |  |  |  |  |  |  |

| bit 7 bit 0                                                          |                                                                            |                                              |                 |                 |          |        |        |  |  |  |  |  |  |  |

| Levend                                                               |                                                                            |                                              |                 |                 |          |        |        |  |  |  |  |  |  |  |

| Legend:                                                              |                                                                            |                                              |                 |                 |          |        |        |  |  |  |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                            |                                              |                 |                 |          |        |        |  |  |  |  |  |  |  |

| -n = Value at F                                                      | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                              |                 |                 |          |        |        |  |  |  |  |  |  |  |

|                                                                      |                                                                            |                                              |                 |                 |          |        |        |  |  |  |  |  |  |  |

| bit 7-3                                                              | Unimplemen                                                                 | ted: Read as '                               | 0'              |                 |          |        |        |  |  |  |  |  |  |  |

| bit 2                                                                | TMR6IF: TMF                                                                | R6 to PR6 Mate                               | ch Interrupt Fl | ag bit          |          |        |        |  |  |  |  |  |  |  |

|                                                                      | 1 = TMR6 to                                                                | PR6 match oc                                 | curred (must    | be cleared in s | oftware) |        |        |  |  |  |  |  |  |  |

|                                                                      | 0 = No TMR6                                                                | to PR6 match                                 | occurred        |                 |          |        |        |  |  |  |  |  |  |  |

| bit 1                                                                | TMR5IF: TMF                                                                | R5 Overflow Int                              | errupt Flag bi  | it              |          |        |        |  |  |  |  |  |  |  |

|                                                                      | 1 = TMR5 register overflowed (must be cleared in software)                 |                                              |                 |                 |          |        |        |  |  |  |  |  |  |  |

|                                                                      | 0 = TMR5 reg                                                               | 0 = TMR5 register did not overflow           |                 |                 |          |        |        |  |  |  |  |  |  |  |

| bit 0                                                                | TMR4IF: TMF                                                                | TMR4IF: TMR4 to PR4 Match Interrupt Flag bit |                 |                 |          |        |        |  |  |  |  |  |  |  |

|                                                                      |                                                                            |                                              |                 | be cleared in s | oftware) |        |        |  |  |  |  |  |  |  |

|                                                                      | 0 = NO IMR4                                                                | to PR4 match                                 | occurred        |                 |          |        |        |  |  |  |  |  |  |  |

### REGISTER 9-8: PIR5: PERIPHERAL INTERRUPT (FLAG) REGISTER 5

| ECCP Mode            | PxM<1:0> | CCPx/PxA           | PxB                | PxC                | PxD                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

#### TABLE 14-12: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

**Note 1:** PWM Steering enables outputs in Single mode.

#### **FIGURE 14-6: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH** STATE)

| PxM<1:0>               | Signal        | 0 ◀ Pulse Width          | PRX+1                |

|------------------------|---------------|--------------------------|----------------------|

|                        |               | -                        | — Period →           |

| 00 (Single Output)     | PxA Modulated | <br>Delay <sup>(1)</sup> | Delaý <sup>(1)</sup> |

|                        | PxA Modulated |                          |                      |

| 10 (Half-Bridge)       | PxB Modulated | _ '<br>_ <u>'</u>        |                      |

|                        | PxA Active    |                          |                      |

| (Full-Bridge,          | PxB Inactive  |                          |                      |

| <sup>01</sup> Forward) | PxC Inactive  |                          |                      |

|                        | PxD Modulated |                          |                      |

|                        | PxA Inactive  |                          |                      |

| 11 (Full-Bridge,       | PxB Modulated |                          |                      |

| Reverse)               | PxC Active    |                          |                      |

|                        | PxD Inactive  |                          |                      |

Period = 4 \* Tosc \* (PRx + 1) \* (TMRx Prescale Value)

Pulse Width = Tosc \* (CCPRxL<7:0>:CCPxCON<5:4>) \* (TMRx Prescale Value)

Delay = 4 \* Tosc \* (PWMxCON<6:0>)

Note 1: Dead-band delay is programmed using the PWMxCON register (Section 14.4.5 "Programmable Dead-Band Delay Mode").

| Name                 | Bit 7    | Bit 6     | Bit 5       | Bit 4        | Bit 3       | Bit 2                  | Bit 1                 | Bit 0                 | Register on<br>Page |

|----------------------|----------|-----------|-------------|--------------|-------------|------------------------|-----------------------|-----------------------|---------------------|

| ECCP1AS              | CCP1ASE  |           | CCP1AS<2:0> |              | PSS1A       | SS1AC<1:0> PSS1BD<1:0> |                       |                       | 202                 |

| CCP1CON              | P1M-     | <1:0>     | DC1B        | <1:0>        |             | CCP1M                  | 1<3:0>                |                       | 198                 |

| ECCP2AS              | CCP2ASE  |           | CCP2AS<2:0> |              | PSS2A       | C<1:0>                 | PSS2B                 | D<1:0>                | 202                 |

| CCP2CON              | P2M-     | <1:0>     | DC2B        | <1:0>        |             | CCP2M                  | 1<3:0>                |                       | 198                 |

| ECCP3AS              | CCP3ASE  |           | CCP3AS<2:0> |              | PSS3A       | C<1:0>                 | PSS3B                 | D<1:0>                | 202                 |

| CCP3CON              | P3M-     | <1:0>     | DC3B        | <1:0>        |             | CCP3N                  | 1<3:0>                |                       | 198                 |

| CCPTMRS0             | C3TSE    | L<1:0>    | —           | C2TSE        | L<1:0>      | —                      | C1TSE                 | L<1:0>                | 201                 |

| INTCON               | GIE/GIEH | PEIE/GIEL | TMR0IE      | INTOIE       | RBIE        | TMR0IF                 | INT0IF                | RBIF                  | 109                 |

| IPR1                 | _        | ADIP      | RC1IP       | TX1IP        | SSP1IP      | CCP1IP                 | TMR2IP                | TMR1IP                | 121                 |

| IPR2                 | OSCFIP   | C1IP      | C2IP        | EEIP         | BCL1IP      | HLVDIP                 | TMR3IP                | CCP2IP                | 122                 |

| IPR4                 | _        | —         | —           | —            | _           | CCP5IP                 | CCP4IP                | CCP3IP                | 124                 |

| PIE1                 | —        | ADIE      | RC1IE       | TX1IE        | SSP1IE      | CCP1IE                 | TMR2IE                | TMR1IE                | 117                 |

| PIE2                 | OSCFIE   | C1IE      | C2IE        | EEIE         | BCL1IE      | HLVDIE                 | TMR3IE                | CCP2IE                | 118                 |

| PIE4                 | _        | —         | —           | —            | _           | CCP5IE                 | CCP4IE                | CCP3IE                | 120                 |

| PIR1                 | _        | ADIF      | RC1IF       | TX1IF        | SSP1IF      | CCP1IF                 | TMR2IF                | TMR1IF                | 112                 |

| PIR2                 | OSCFIF   | C1IF      | C2IF        | EEIF         | BCL1IF      | HLVDIF                 | TMR3IF                | CCP2IF                | 113                 |

| PIR4                 | _        | —         | —           | —            | _           | CCP5IF                 | CCP4IF                | CCP3IF                | 115                 |

| PMD0                 | UART2MD  | UART1MD   | TMR6MD      | TMR5MD       | TMR4MD      | TMR3MD                 | TMR2MD                | TMR1MD                | 52                  |

| PMD1                 | MSSP2MD  | MSSP1MD   | —           | CCP5MD       | CCP4MD      | CCP3MD                 | CCP2MD                | CCP1MD                | 53                  |

| PR2                  |          | •         |             | Timer2 Peric | od Register |                        |                       | •                     | —                   |

| PR4                  |          |           |             | Timer4 Peric | od Register |                        |                       |                       | —                   |

| PR6                  |          |           |             | Timer6 Peric | od Register |                        |                       |                       | —                   |

| PSTR1CON             | _        | _         | —           | STR1SYNC     | STR1D       | STR1C                  | STR1B                 | STR1A                 | 203                 |

| PSTR2CON             | _        | _         | —           | STR2SYNC     | STR2D       | STR2C                  | STR2B                 | STR2A                 | 203                 |

| PSTR3CON             | _        | _         | —           | STR3SYNC     | STR3D       | STR3C                  | STR3B                 | STR3A                 | 203                 |

| PWM1CON              | P1RSEN   |           |             |              | P1DC<6:0>   |                        |                       |                       | 203                 |

| PWM2CON              | P2RSEN   |           |             |              | P2DC<6:0>   |                        |                       |                       | 203                 |

| PWM3CON              | P3RSEN   |           |             |              | P3DC<6:0>   |                        |                       |                       | 203                 |

| T2CON                | _        |           | T2OUT       | PS<3:0>      |             | TMR2ON                 | T2CKP                 | S<1:0>                | 166                 |

| T4CON                | _        |           | T4OUTI      | PS<3:0>      |             | TMR4ON                 | T4CKP                 | S<1:0>                | 166                 |

| T6CON                | _        |           | T6OUTI      | PS<3:0>      |             | TMR6ON                 | T6CKP                 | S<1:0>                | 166                 |

| TMR2                 |          | •         |             | Timer2 R     | legister    |                        |                       |                       | _                   |

| TMR4                 |          |           |             | Timer4 R     | legister    |                        |                       |                       | —                   |

| TMR6                 |          |           |             | Timer6 R     | legister    |                        |                       |                       | —                   |

| TRISA                | TRISA7   | TRISA6    | TRISA5      | TRISA4       | TRISA3      | TRISA2                 | TRISA1                | TRISA0                | 151                 |

| TRISB                | TRISB7   | TRISB6    | TRISB5      | TRISB4       | TRISB3      | TRISB2                 | TRISB1                | TRISB0                | 151                 |

| TRISC                | TRISC7   | TRISC6    | TRISC5      | TRISC4       | TRISC3      | TRISC2                 | TRISC1                | TRISC0                | 151                 |

| TRISD <sup>(1)</sup> | TRISD7   | TRISD6    | TRISD5      | TRISD4       | TRISD3      | TRISD2                 | TRISD1                | TRISD0                | 151                 |

| TRISE                | WPUE3    | —         |             | —            | _           | TRISE2 <sup>(1)</sup>  | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 151                 |

#### TABLE 14-13: REGISTERS ASSOCIATED WITH ENHANCED PWM

Legend:

— = Unimplemented location, read as '0'. Shaded bits are not used by Enhanced PWM mode.

Note

1:

These registers/bits are available on PIC18(L)F4XK22 devices.

#### TABLE 14-14: CONFIGURATION REGISTERS ASSOCIATED WITH ENHANCED PWM

|   | Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---|---------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| С | ONFIG3H | MCLRE |       | P2BMX | T3CMX | HFOFST | ССРЗМХ | PBADEN | CCP2MX | 348                 |

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Enhanced PWM mode.

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

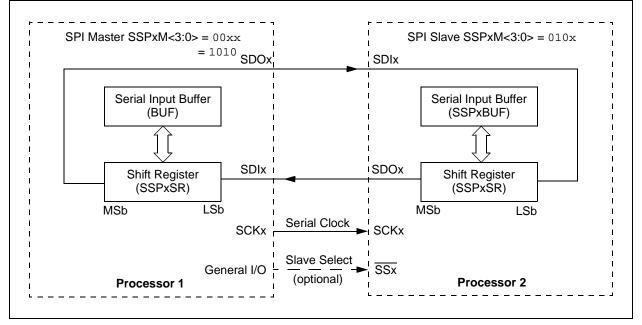

The MSSPx consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF of the SSPxSTAT register, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL of the SSPxCON1 register, will be

set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSPx interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

### 15.3 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit Bus (I<sup>2</sup>C) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCLx)

- Serial Data (SDAx)

Figure 15-2 shows the block diagram of the MSSPx module when operating in  $I^2C$  mode.

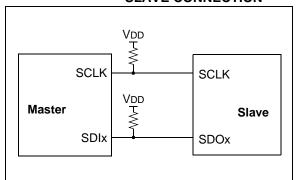

Both the SCLx and SDAx connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 15-11 shows a typical connection between two processors configured as master and slave devices.

The I<sup>2</sup>C bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode

(master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDAx line while the SCLx line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

### FIGURE 15-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDAx line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of data bits is always performed while the SCLx line is held low. Transitions that occur while the SCLx line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an ACK bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDAx line while the SCLx line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

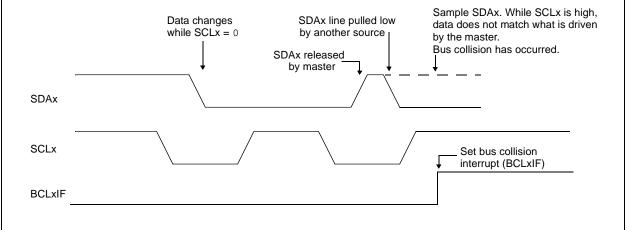

#### 15.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF, and reset the I<sup>2</sup>C port to its Idle state (Figure 15-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $l^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

#### 16.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode would typically be used in RS-232 systems. The receiver block diagram is shown in Figure 16-2. The data is received on the RXx/DTx pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREGx register.

#### 16.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTAx register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTAx register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTAx register enables the EUSART. The RXx/DTx I/O pin must be configured as an input by setting the corresponding TRIS control bit. If the RXx/DTx pin is shared with an analog peripheral the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

#### 16.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 16.1.2.5 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCxIF interrupt flag bit of the PIR1/PIR3 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREGx register.

| Note: | If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See <b>Section 16.1.2.6</b> |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|       | "Receive Overrun Error" for more information on overrun errors.                                                                               |

#### 16.1.2.3 Receive Data Polarity

The polarity of the receive data can be controlled with the DTRXP bit of the BAUDCONx register. The default state of this bit is '0' which selects high true receive idle and data bits. Setting the DTRXP bit to '1' will invert the receive data resulting in low true idle and data bits. The DTRXP bit controls receive data polarity only in Asynchronous mode. In Synchronous mode the DTRXP bit has a different function.

| FIGURE 16-12:                                     | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                              |

|---------------------------------------------------|------------------------------------------------------------------------|

| RXx/DTx<br>pin<br>TXx/CKx pin<br>(SCKP = 0)       |                                                                        |

| TXx/CKx pin<br>(SCKP = 1)<br>Write to<br>bit SREN |                                                                        |

| SREN bit                                          |                                                                        |

| CREN bit <u>'0'</u><br>RCxIF bit<br>(Interrupt)   | .0,<br>.0,                                                             |

| Read<br>RCREGx                                    | gram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0. |

|                                                   |                                                                        |

#### TABLE 16-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name     | Bit 7                                                    | Bit 6                                          | Bit 5  | Bit 4       | Bit 3        | Bit 2     | Bit 1   | Bit 0   | Register<br>on Page |  |  |  |

|----------|----------------------------------------------------------|------------------------------------------------|--------|-------------|--------------|-----------|---------|---------|---------------------|--|--|--|

| BAUDCON1 | ABDOVF RCIDL DTRXP CKTXP BRG16 — WUE ABDEN               |                                                |        |             |              |           |         |         | 271                 |  |  |  |

| BAUDCON2 | ABDOVF RCIDL DTRXP CKTXP BRG16 — WUE ABDEN               |                                                |        |             |              |           |         |         |                     |  |  |  |

| INTCON   | GIE/GIEH PEIE/GIEL TMR0IE INT0IE RBIE TMR0IF INT0IF RBIF |                                                |        |             |              |           |         |         |                     |  |  |  |

| IPR1     | _                                                        | - ADIP RC1IP TX1IP SSP1IP CCP1IP TMR2IP TMR1IP |        |             |              |           |         |         |                     |  |  |  |

| IPR3     | SSP2IP                                                   | BCL2IP                                         | RC2IP  | TX2IP       | CTMUIP       | TMR5GIP   | TMR3GIP | TMR1GIP | 123                 |  |  |  |

| PIE1     | _                                                        | ADIE                                           | RC1IE  | TX1IE       | SSP1IE       | CCP1IE    | TMR2IE  | TMR1IE  | 117                 |  |  |  |

| PIE3     | SSP2IE BCL2IE RC2IE TX2IE CTMUIE TMR5GIE TMR3GIE TMR1GIE |                                                |        |             |              |           |         |         |                     |  |  |  |

| PIR1     | - ADIF RC1IF TX1IF SSP1IF CCP1IF TMR2IF TMR1IF           |                                                |        |             |              |           |         |         |                     |  |  |  |

| PIR3     | SSP2IF BCL2IF RC2IF TX2IF CTMUIF TMR5GIF TMR3GIF TMR1GIF |                                                |        |             |              |           |         |         |                     |  |  |  |

| PMD0     | UART2MD                                                  | UART1MD                                        | TMR6MD | TMR5MD      | TMR4MD       | TMR3MD    | TMR2MD  | TMR1MD  | 52                  |  |  |  |

| RCREG1   |                                                          |                                                | E      | USART1 Re   | ceive Regis  | ter       |         |         | —                   |  |  |  |

| RCSTA1   | SPEN                                                     | RX9                                            | SREN   | CREN        | ADDEN        | FERR      | OERR    | RX9D    | 270                 |  |  |  |

| RCREG2   |                                                          |                                                | E      | USART2 Re   | ceive Regis  | ter       |         |         | —                   |  |  |  |

| RCSTA2   | SPEN                                                     | RX9                                            | SREN   | CREN        | ADDEN        | FERR      | OERR    | RX9D    | 270                 |  |  |  |

| SPBRG1   |                                                          |                                                | EUSART | 1 Baud Rate | e Generator, | Low Byte  |         |         | —                   |  |  |  |

| SPBRGH1  |                                                          |                                                | EUSART | 1 Baud Rate | Generator,   | High Byte |         |         | —                   |  |  |  |

| SPBRG2   |                                                          |                                                | EUSART | 2 Baud Rate | e Generator, | Low Byte  |         |         | —                   |  |  |  |

| SPBRGH2  |                                                          |                                                | EUSART | 2 Baud Rate | Generator,   | High Byte |         |         | —                   |  |  |  |

| TXSTA1   | CSRC                                                     | TX9                                            | TXEN   | SYNC        | SENDB        | BRGH      | TRMT    | TX9D    | 269                 |  |  |  |

| TXSTA2   | CSRC                                                     | TX9                                            | TXEN   | SYNC        | SENDB        | BRGH      | TRMT    | TX9D    | 269                 |  |  |  |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for synchronous master reception.

### 24.2 Register Definitions: Configuration Word

REGISTER 24-1: CONFIG1H: CONFIGURATION REGISTER 1 HIGH

| REGISTE    | R 24-1: CONF<br>R/P-0                                                                                                                                                                             | R/P-1                                                                                                                                                                                  | R/P-0                                                                                                                                                                                              |                                                                                                                                               | 1 HIGH<br>R/P-1                                           | R/P-0           |       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------|-------|

| IESO       | FCMEN                                                                                                                                                                                             | R/P-1<br>PRICLKEN                                                                                                                                                                      | R/P-0<br>PLLCFG                                                                                                                                                                                    | R/P-0                                                                                                                                         |                                                           | R/P-0<br><3:0>  | R/P-1 |

| bit 7      | FOWEIN                                                                                                                                                                                            | FRICEREIN                                                                                                                                                                              | FLLCFG                                                                                                                                                                                             |                                                                                                                                               | FUSC                                                      | <0.0>           | bit C |

|            |                                                                                                                                                                                                   |                                                                                                                                                                                        |                                                                                                                                                                                                    |                                                                                                                                               |                                                           |                 |       |

| Legend:    |                                                                                                                                                                                                   |                                                                                                                                                                                        |                                                                                                                                                                                                    |                                                                                                                                               |                                                           |                 |       |

| R = Reada  | able bit                                                                                                                                                                                          | P = Programr                                                                                                                                                                           | nable bit                                                                                                                                                                                          | U = Unimple                                                                                                                                   | mented bit, read                                          | d as '0'        |       |

| -n = Value | when device is un                                                                                                                                                                                 | programmed                                                                                                                                                                             |                                                                                                                                                                                                    | x = Bit is unk                                                                                                                                | nown                                                      |                 |       |

| bit 7      | 1 = Oscillator                                                                                                                                                                                    | rnal/External O<br>Switchover mo                                                                                                                                                       | ode enabled                                                                                                                                                                                        | nover bit                                                                                                                                     |                                                           |                 |       |

| bit 6      | FCMEN <sup>(1)</sup> : F<br>1 = Fail-Safe                                                                                                                                                         | ail-Safe Clock I<br>Clock Monitor<br>Clock Monitor                                                                                                                                     | Monitor Enable<br>enabled                                                                                                                                                                          | e bit                                                                                                                                         |                                                           |                 |       |

| bit 5      | 1 = Primary (                                                                                                                                                                                     | Primary Clock I<br>Clock is always<br>Clock can be di                                                                                                                                  | enabled                                                                                                                                                                                            | ware                                                                                                                                          |                                                           |                 |       |

| bit 4      | 1 = 4 x PLL a                                                                                                                                                                                     | PLL Enable bi<br>Navays enabled<br>s under softwar                                                                                                                                     | , Oscillator mu                                                                                                                                                                                    |                                                                                                                                               | E<6>)                                                     |                 |       |

| bit 3-0    | 1111 = Exte<br>1110 = Exte<br>1101 = EC c<br>1100 = EC c<br>1011 = EC c<br>1010 = EC c<br>1010 = Inter<br>1000 = Inter<br>0111 = Exte<br>0110 = Exte<br>0101 = EC c<br>0100 = EC c<br>0100 = EC c | oscillator (medi<br>oscillator, CLKC<br>nal oscillator bl<br>nal oscillator bl<br>rnal RC oscillator<br>rnal RC oscillator<br>oscillator (high<br>oscillator (medi<br>oscillator (high | tor, CLKOUT f<br>tor, CLKOUT f<br>power, ≤500 k<br>OUT function o<br>um power, 50<br>OUT function o<br>ock, CLKOUT<br>ock<br>tor<br>tor, CLKOUT f<br>power, >16 M<br>OUT function o<br>um power, 4 | unction on RA<br>Hz)<br>n OSC2 (low j<br>0 kHz-16 MHz<br>n OSC2 (med<br>function on OS<br>unction on OS<br>Hz)<br>n OSC2 (high<br>MHz-16 MHz) | 6<br>power, <b>≤500 kH</b><br>:)<br>ium power, 500<br>SC2 | ) kHz-16 MHz)   |       |

| Note 1:    | 0000 = LP o                                                                                                                                                                                       |                                                                                                                                                                                        |                                                                                                                                                                                                    |                                                                                                                                               |                                                           | a aat than that |       |

| Note 1:    | When FOSC<3:0>                                                                                                                                                                                    |                                                                                                                                                                                        |                                                                                                                                                                                                    |                                                                                                                                               | nd FCMEN bit i                                            |                 |       |

## should also be set to prevent a false failed clock indication and to enable automatic clock switch over from the internal oscillator block to the external oscillator when the OST times out.

| BNC                                                                             | ;                                                               | Branch if                                                                                | Not Carry                                                                                                                                                                                                                                                                             | /    |                |  |  |  |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|--|--|--|

| Synta                                                                           | ax:                                                             | BNC n                                                                                    | BNC n                                                                                                                                                                                                                                                                                 |      |                |  |  |  |

| Oper                                                                            | ands:                                                           | -128 ≤ n ≤ ′                                                                             | 127                                                                                                                                                                                                                                                                                   |      |                |  |  |  |

| Oper                                                                            | ation:                                                          | if CARRY b<br>(PC) + 2 + 2                                                               |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

| Statu                                                                           | s Affected:                                                     | None                                                                                     |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

| Enco                                                                            | ding:                                                           | 1110                                                                                     | 0011 :                                                                                                                                                                                                                                                                                | nnnn | nnnn           |  |  |  |

| Desc                                                                            | ription:                                                        | will branch.<br>The 2's con<br>added to the<br>incremente<br>instruction,<br>PC + 2 + 2r | If the CARRY bit is '0', then the program<br>will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction. |      |                |  |  |  |

| Word                                                                            | ls:                                                             | 1                                                                                        |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

| Cycle                                                                           | es:                                                             | 1(2)                                                                                     |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

| Q C<br>If Ju                                                                    | ycle Activity:<br>mp:                                           |                                                                                          |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

|                                                                                 | Q1                                                              | Q2                                                                                       | Q3                                                                                                                                                                                                                                                                                    |      | Q4             |  |  |  |

|                                                                                 | Decode                                                          | Read literal<br>'n'                                                                      | Process<br>Data                                                                                                                                                                                                                                                                       | s Wr | ite to PC      |  |  |  |

|                                                                                 | No<br>operation                                                 | No<br>operation                                                                          | No<br>operation                                                                                                                                                                                                                                                                       | n op | No<br>peration |  |  |  |

| lf No                                                                           | o Jump:                                                         |                                                                                          |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

|                                                                                 | Q1                                                              | Q2                                                                                       | Q3                                                                                                                                                                                                                                                                                    |      | Q4             |  |  |  |

|                                                                                 | Decode                                                          | Read literal<br>'n'                                                                      | Process<br>Data                                                                                                                                                                                                                                                                       |      | No<br>peration |  |  |  |

| Example: HERE BNC Jump                                                          |                                                                 |                                                                                          |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

| Before Instruction<br>PC = address (HERE)<br>After Instruction<br>If CARRY = 0; |                                                                 |                                                                                          |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

|                                                                                 | PC = address (Jump)<br>If CARRY = 1;<br>PC = address (HERE + 2) |                                                                                          |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

| BNN                                                                                                                                                      | Branch if                                                                            | Not Nega                                                                                                                                                                                                                                                                                 | tive |                |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|--|--|--|--|

| Syntax:                                                                                                                                                  | BNN n                                                                                | BNN n                                                                                                                                                                                                                                                                                    |      |                |  |  |  |  |

| Operands:                                                                                                                                                | -128 ≤ n ≤ 1                                                                         | $-128 \le n \le 127$                                                                                                                                                                                                                                                                     |      |                |  |  |  |  |

| Operation:                                                                                                                                               |                                                                                      | if NEGATIVE bit is '0' (PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                    |      |                |  |  |  |  |

| Status Affected:                                                                                                                                         | None                                                                                 |                                                                                                                                                                                                                                                                                          |      |                |  |  |  |  |

| Encoding:                                                                                                                                                | 1110                                                                                 | 0111 1                                                                                                                                                                                                                                                                                   | nnnn | nnnn           |  |  |  |  |

| Description:                                                                                                                                             | program wi<br>The 2's cor<br>added to th<br>incremente<br>instruction,<br>PC + 2 + 2 | If the NEGATIVE bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction. |      |                |  |  |  |  |

| Words:                                                                                                                                                   | 1                                                                                    | 1                                                                                                                                                                                                                                                                                        |      |                |  |  |  |  |

| Cycles:                                                                                                                                                  | 1(2)                                                                                 | 1(2)                                                                                                                                                                                                                                                                                     |      |                |  |  |  |  |

| Q Cycle Activity:<br>If Jump:                                                                                                                            | 00                                                                                   | 00                                                                                                                                                                                                                                                                                       |      | 04             |  |  |  |  |

| Q1                                                                                                                                                       | Q2                                                                                   | Q3                                                                                                                                                                                                                                                                                       | 10/- | Q4             |  |  |  |  |

| Decode                                                                                                                                                   | Read literal<br>'n'                                                                  | Process<br>Data                                                                                                                                                                                                                                                                          | VVF  | ite to PC      |  |  |  |  |

| No                                                                                                                                                       | No                                                                                   | No                                                                                                                                                                                                                                                                                       |      | No             |  |  |  |  |

| operation                                                                                                                                                | operation                                                                            | operatior                                                                                                                                                                                                                                                                                | n op | peration       |  |  |  |  |