Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 19x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25k22-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                                           | 11   |

|-------|---------------------------------------------------------------------------|------|

| 2.0   | Oscillator Module (With Fail-Safe Clock Monitor))                         | . 25 |

| 3.0   | Power-Managed Modes                                                       | . 44 |

| 4.0   | Reset                                                                     | . 55 |

| 5.0   | Memory Organization                                                       | . 64 |

| 6.0   | Flash Program Memory                                                      | . 90 |

| 7.0   | Data EEPROM Memory                                                        | . 99 |

| 8.0   | 8 x 8 Hardware Multiplier                                                 | 104  |

| 9.0   | Interrupts                                                                | 106  |

| 10.0  | I/O Ports                                                                 | 127  |

| 11.0  | Timer0 Module                                                             | 154  |

| 12.0  | Timer1/3/5 Module with Gate Control                                       | 157  |

| 13.0  | Timer2/4/6 Module                                                         | 169  |

| 14.0  | Capture/Compare/PWM Modules                                               |      |

| 15.0  | Master Synchronous Serial Port (MSSP1 and MSSP2) Module                   | 204  |

| 16.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |      |

| 17.0  | Analog-to-Digital Converter (ADC) Module                                  |      |

| 18.0  | Comparator Module                                                         | 302  |

| 19.0  | Charge Time Measurement Unit (CTMU)                                       | 311  |

| 20.0  | SR LATCH                                                                  |      |

| 21.0  | Fixed Voltage Reference (FVR)                                             | 331  |

| 22.0  | Digital-to-Analog Converter (DAC) Module                                  |      |

| 23.0  | High/Low-Voltage Detect (HLVD)                                            |      |

| 24.0  | Special Features of the CPU                                               | 343  |

| 25.0  | Instruction Set Summary                                                   | 360  |

| 26.0  | Development Support                                                       | 410  |

| 27.0  | Electrical Specifications                                                 | 414  |

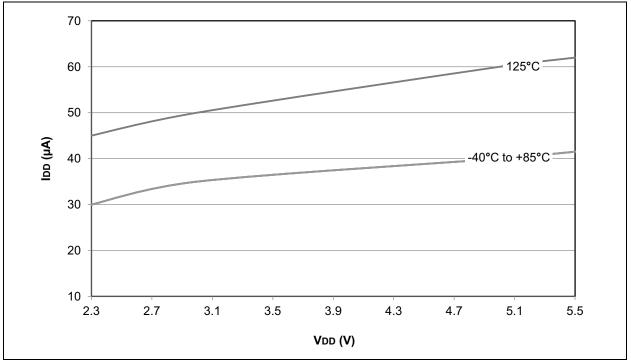

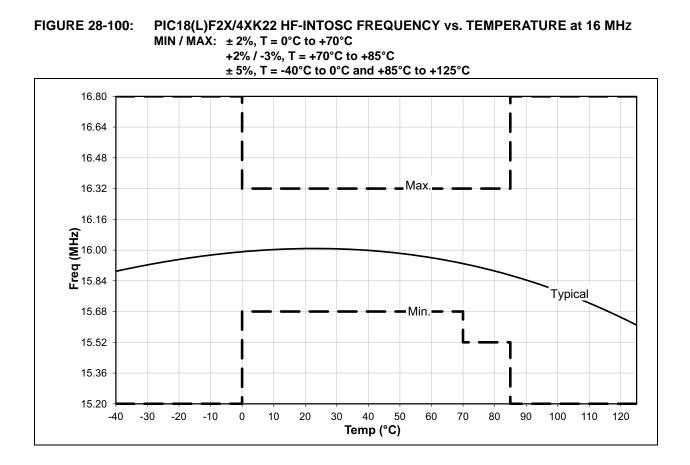

| 28.0  | DC and AC Characteristics Graphs and Tables                               | 453  |

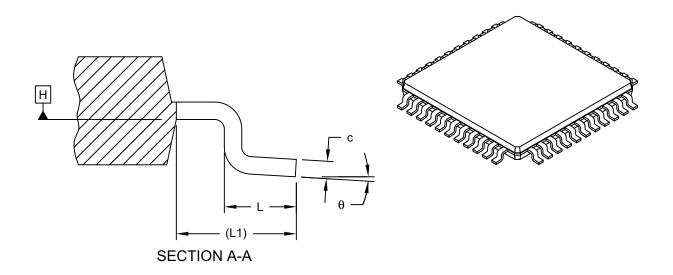

| 29.0  | Packaging Information                                                     | 509  |

| Appe  | ndix A: Revision History                                                  | 534  |

| Appe  | ndix B: Device Differences                                                | 535  |

| The M | Aicrochip Web Site                                                        | 536  |

| Custo | omer Change Notification Service                                          | 536  |

| Custo | omer Support                                                              | 536  |

| Produ | uct Identification System                                                 | 537  |

|       |                                                                           |      |

## 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F23K22 PIC18LF23K22

- PIC18F24K22 PIC18LF24K22

- PIC18F25K22 PIC18LF25K22

- PIC18F26K22 PIC18LF26K22

- PIC18F43K22 PIC18LF43K22

- PIC18F44K22 PIC18LF44K22

- PIC18F45K22 PIC18LF45K22

- PIC18F46K22 PIC18LF46K22

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Flash program memory. On top of these features, the PIC18(L)F2X/4XK22 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

#### 1.1 New Core Features

#### 1.1.1 XLP TECHNOLOGY

All of the devices in the PIC18(L)F2X/4XK22 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- **On-the-fly Mode Switching:** The powermanaged modes are invoked by user code during operation, allowing the user to incorporate powersaving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 27.0 "Electrical Specifications" for values.

## 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18(L)F2X/4XK22 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O)

- Two External RC Oscillator modes with the same pin options as the External Clock modes

- An internal oscillator block which contains a 16 MHz HFINTOSC oscillator and a 31 kHz LFINTOSC oscillator, which together provide eight user selectable clock frequencies, from 31 kHz to 16 MHz. This option frees the two oscillator pins for use as additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both external and internal oscillator modes, which allows clock speeds of up to 64 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 64 MHz – all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the LFINTOSC. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or Wake-up from Sleep mode, until the primary clock source is available.

## 9.4 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable, priority and flag bits.

## 9.5 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are five Peripheral Interrupt Request Flag registers (PIR1, PIR2, PIR3, PIR4 and PIR5).

## 9.6 **PIE Registers**

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are five Peripheral Interrupt Enable registers (PIE1, PIE2, PIE3, PIE4 and PIE5). When IPEN = 0, the PEIE/GIEL bit must be set to enable any of these peripheral interrupts.

## 9.7 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are five Peripheral Interrupt Priority registers (IPR1, IPR2, IPR3, IPR4 and IPR5). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

|                         |                                                                                                                                              |                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                             | 020,                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function                | TRIS<br>Setting                                                                                                                              | ANSEL<br>Setting                                                                                                                                                                                                                   | Pin<br>Type                                                                                                                                                                                                                                                                   | Buffer<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RB6                     | 0                                                                                                                                            | —                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                             | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LATB<6> data output; not affected by analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                         | 1                                                                                                                                            | _                                                                                                                                                                                                                                  | I                                                                                                                                                                                                                                                                             | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PORTB<6> data input; disabled when analog input<br>enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| IOC2                    | 1                                                                                                                                            | —                                                                                                                                                                                                                                  | I                                                                                                                                                                                                                                                                             | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Interrupt-on-change pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TX2 <sup>(3)</sup>      | 1                                                                                                                                            | —                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                             | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EUSART asynchronous transmit data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CK2 <sup>(3)</sup>      | 1                                                                                                                                            | —                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                             | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EUSART synchronous serial clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                         | 1                                                                                                                                            | _                                                                                                                                                                                                                                  | Ι                                                                                                                                                                                                                                                                             | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EUSART synchronous serial clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PGC                     | x                                                                                                                                            | _                                                                                                                                                                                                                                  | I                                                                                                                                                                                                                                                                             | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                      | In-Circuit Debugger and ICSP <sup>™</sup> programming clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RB7                     | 0                                                                                                                                            | —                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                             | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LATB<7> data output; not affected by analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                         | 1                                                                                                                                            | _                                                                                                                                                                                                                                  | Ι                                                                                                                                                                                                                                                                             | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PORTB<7> data input; disabled when analog input<br>enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| IOC3                    | 1                                                                                                                                            | —                                                                                                                                                                                                                                  | I                                                                                                                                                                                                                                                                             | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Interrupt-on-change pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RX2 <sup>(2), (3)</sup> | 1                                                                                                                                            | —                                                                                                                                                                                                                                  | I                                                                                                                                                                                                                                                                             | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EUSART asynchronous receive data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DT2 <sup>(2), (3)</sup> | 1                                                                                                                                            | —                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                             | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EUSART synchronous serial data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                         | 1                                                                                                                                            | —                                                                                                                                                                                                                                  | I                                                                                                                                                                                                                                                                             | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EUSART synchronous serial data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PGD                     | x                                                                                                                                            | —                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                             | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                     | In-Circuit Debugger and ICSP <sup>™</sup> programming data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                         | x                                                                                                                                            | —                                                                                                                                                                                                                                  | I                                                                                                                                                                                                                                                                             | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                      | In-Circuit Debugger and ICSP <sup>™</sup> programming data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         | Function     RB6     IOC2     TX2 <sup>(3)</sup> CK2 <sup>(3)</sup> PGC     RB7     IOC3     RX2 <sup>(2), (3)</sup> DT2 <sup>(2), (3)</sup> | Function   TRIS<br>Setting     RB6   0     1   1     IOC2   1     TX2 <sup>(3)</sup> 1     CK2 <sup>(3)</sup> 1     PGC   x     RB7   0     IOC3   1     RX2 <sup>(2)</sup> , (3)   1     DT2 <sup>(2)</sup> , (3)   1     PGD   x | Function   TRIS<br>Setting   ANSEL<br>Setting     RB6   0      1    1     IOC2   1      TX2 <sup>(3)</sup> 1      CK2 <sup>(3)</sup> 1      PGC   x      RB7   0      IOC3   1      IOC3   1      IOC3   1      PGC   1      PGC   X      IOC3   1      IOC3   1      PGD   X | Function   TRIS<br>Setting   ANSEL<br>Setting   Pin<br>Type     RB6   0   —   0     1   —   0   1     IOC2   1   —   1     IOC2   1   —   1     TX2 <sup>(3)</sup> 1   —   0     CK2 <sup>(3)</sup> 1   —   0     PGC   x   —   1     RB7   0   —   0     1   —   1   —     RB7   0   —   0     1   —   1   —     RB7   0   —   0     1   —   1   —     IOC3   1   —   1     DT2 <sup>(2)</sup> , (3)   1   —   0     1   —   0   1     PGD   x   —   0 | $\begin{array}{ c c c c c c } \hline Function & Setting & Setting & Type & Type \\ \hline RB6 & 0 & & 0 & DIG \\ \hline 1 & & 0 & DIG \\ \hline 1 & & 1 & TTL \\ \hline 10C2 & 1 & & 1 & TTL \\ \hline TX2^{(3)} & 1 & & 0 & DIG \\ \hline CK2^{(3)} & 1 & & 0 & DIG \\ \hline 1 & & I & ST \\ \hline PGC & x & & I & ST \\ \hline PGC & x & & I & ST \\ \hline RB7 & 0 & & 0 & DIG \\ \hline 1 & & I & TTL \\ \hline RX2^{(2), (3)} & 1 & & I & ST \\ \hline DT2^{(2), (3)} & 1 & & I & ST \\ \hline PGD & x & & 0 & DIG \\ \hline \end{array}$ |

TABLE 10-5: PORTB I/O SUMMARY (CONTINUED)

**Legend:** AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;  $I^2C$  = Schmitt Trigger input with  $I^2C$ .

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

3: Function on PORTD and PORTE for PIC18(L)F4XK22 devices.

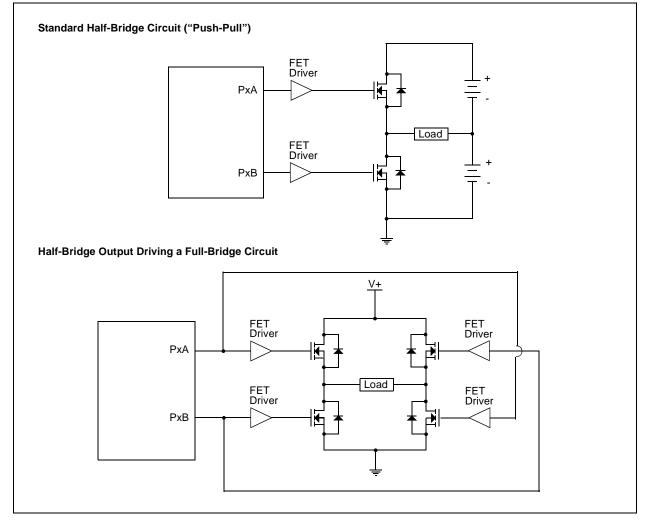

## 14.4.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCPx/PxA pin, while the complementary PWM output signal is output on the PxB pin (see Figure 14-9). This mode can be used for half-bridge applications, as shown in Figure 14-9, or for full-bridge applications, where four power switches are being modulated with two PWM signals.

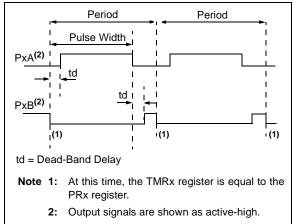

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in halfbridge power devices. The value of the PDC<6:0> bits of the PWMxCON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 14.4.5 "Programmable Dead-Band Delay Mode"** for more details of the dead-band delay operations. Since the PxA and PxB outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure PxA and PxB as outputs.

#### FIGURE 14-8: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

## FIGURE 14-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

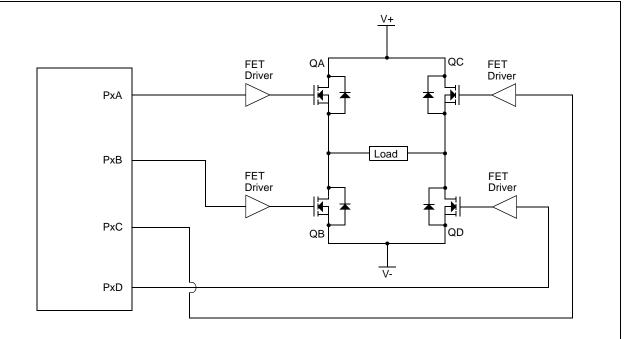

### 14.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of full-bridge application is shown in Figure 14-10.

In the Forward mode, pin CCPx/PxA is driven to its active state, pin PxD is modulated, while PxB and PxC will be driven to their inactive state as shown in Figure 14-11.

In the Reverse mode, PxC is driven to its active state, pin PxB is modulated, while PxA and PxD will be driven to their inactive state as shown Figure 14-11.

PxA, PxB, PxC and PxD outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the PxA, PxB, PxC and PxD pins as outputs.

#### FIGURE 14-10: EXAMPLE OF FULL-BRIDGE APPLICATION

## 15.4 I<sup>2</sup>C Mode Operation

All MSSPx I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and 2 interrupt flags interface the module with the PIC microcontroller and user software. Two pins, SDAx and SCLx, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 15.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the 8th falling edge of the SCLx line, the device outputting data on the SDAx changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCLx, is provided by the master. Data is valid to change while the SCLx signal is low, and sampled on the rising edge of the clock. Changes on the SDAx line while the SCLx line is high define special conditions on the bus, explained below.

## 15.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Phillips  $I^2C$  specification.

## 15.4.3 SDAx AND SCLx PINS

Selection of any I<sup>2</sup>C mode with the SSPxEN bit set, forces the SCLx and SDAx pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

**Note:** Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

## 15.4.4 SDAx HOLD TIME

The hold time of the SDAx pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDAx is held valid after the falling edge of SCLx. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

## TABLE 15-1: I<sup>2</sup>C BUS TERMS

| TABLE 15-1:         | TABLE 15-1: I <sup>2</sup> C BUS TERMS                                                                                                                                                                          |  |  |  |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| TERM                | Description                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                                  |  |  |  |  |  |  |  |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                                                   |  |  |  |  |  |  |  |

| Master              | The device that initiates a transfer, generates clock signals and termi-<br>nates a transfer.                                                                                                                   |  |  |  |  |  |  |  |

| Slave               | The device addressed by the mas-<br>ter.                                                                                                                                                                        |  |  |  |  |  |  |  |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                               |  |  |  |  |  |  |  |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                                             |  |  |  |  |  |  |  |

| Synchronization     | Procedure to synchronize the<br>clocks of two or more devices on<br>the bus.                                                                                                                                    |  |  |  |  |  |  |  |

| Idle                | No master is controlling the bus,<br>and both SDAx and SCLx lines are<br>high.                                                                                                                                  |  |  |  |  |  |  |  |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                                    |  |  |  |  |  |  |  |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                                    |  |  |  |  |  |  |  |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                                             |  |  |  |  |  |  |  |

| Write Request       | Slave receives a matching<br>address with R/W bit clear, and is<br>ready to clock in data.                                                                                                                      |  |  |  |  |  |  |  |

| Read Request        | Master sends an address byte with<br>the $R/\overline{W}$ bit set, indicating that it<br>wishes to clock data out of the<br>Slave. This data is the next and all<br>following bytes until a Restart or<br>Stop. |  |  |  |  |  |  |  |

| Clock Stretching    | When a device on the bus holds SCLx low to stall communication.                                                                                                                                                 |  |  |  |  |  |  |  |

| Bus Collision       | Any time the SDAx line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                                                     |  |  |  |  |  |  |  |

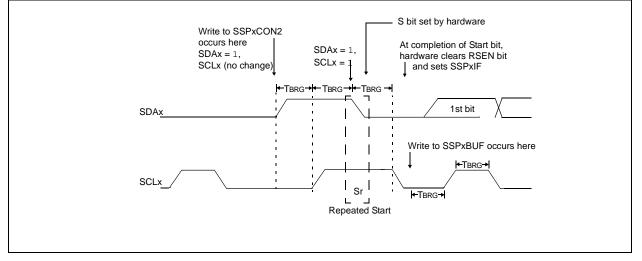

## 15.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 15-27) occurs when the RSEN bit of the SSPxCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. SCLx is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

## FIGURE 15-27: REPEAT START CONDITION WAVEFORM

#### REGISTER 15-3: SSPxCON1: SSPx CONTROL REGISTER 1 (CONTINUED)

- bit 3-0

- SSPxM<3:0>: Synchronous Serial Port Mode Select bits

- 0000 = SPI Master mode, clock = Fosc/4

- 0001 = SPI Master mode, clock = Fosc/16 0010 = SPI Master mode, clock = Fosc/64

- 0011 = SPI Master mode, clock = TMR2 output/2

- 0100 =SPI Slave mode, clock = SCKx pin, SSx pin control enabled

- 0101 = SPI Slave mode, clock = SCKx pin, SSx pin control disabled, SSx can be used as I/O pin

- $0110 = I^2C$  Slave mode, 7-bit address

- $0111 = I^2C$  Slave mode, 10-bit address

- $1000 = I^2C$  Master mode, clock = Fosc / (4 \* (SSPxADD+1))<sup>(4)</sup>

- 1001 = Reserved

- 1010 = SPI Master mode, clock = Fosc/(4 \* (SSPxADD+1))

- $1011 = I^2C$  firmware controlled Master mode (slave idle)

- 1100 = Reserved

- 1101 = Reserved

- 1110 =  $I^2C$  Slave mode, 7-bit address with Start and Stop bit interrupts enabled

- 1111 =  $I^2C$  Slave mode, 10-bit address with Start and Stop bit interrupts enabled

- Note 1: In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPxBUF register.

- 2: When enabled, these pins must be properly configured as input or output.

- 3: When enabled, the SDAx and SCLx pins must be configured as inputs.

- 4: SSPxADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

## 17.1.7 RESULT FORMATTING

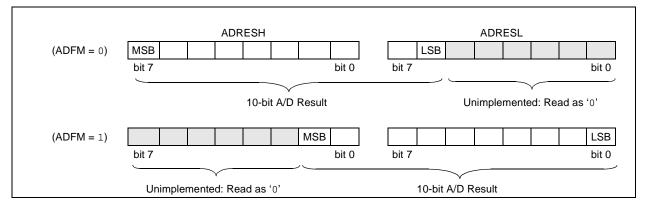

The 10-bit A/D conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON2 register controls the output format.

Figure 17-2 shows the two output formats.

## FIGURE 17-2: 10-BIT A/D CONVERSION RESULT FORMAT

## 18.5 Operation During Sleep

The comparator, if enabled before entering Sleep mode, remains active during Sleep. The additional current consumed by the comparator is shown separately in **Section 27.0** "**Electrical Specifications**". If the comparator is not used to wake the device, power consumption can be minimized while in Sleep mode by turning off the comparator. Each comparator is turned off by clearing the CxON bit of the CMxCON0 register.

A change to the comparator output can wake-up the device from Sleep. To enable the comparator to wake the device from Sleep, the CxIE bit of the PIE2 register and the PEIE/GIEL bit of the INTCON register must be set. The instruction following the SLEEP instruction always executes following a wake from Sleep. If the GIE/GIEH bit of the INTCON register is also set, the device will then execute the Interrupt Service Routine.

## 18.6 Effects of a Reset

A device Reset forces the CMxCON0 and CM2CON1 registers to their Reset states. This forces both comparators and the voltage references to their Off states.Comparator Control Registers.

## 18.7 Analog Input Connection Considerations

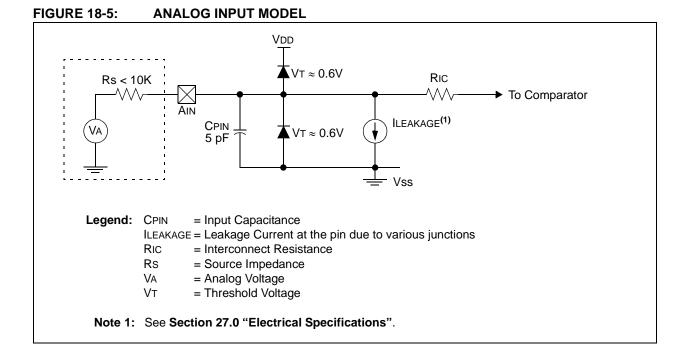

A simplified circuit for an analog input is shown in Figure 18-5. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

## 23.6 Applications

In many applications, it is desirable to detect a drop below, or rise above, a particular voltage threshold. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

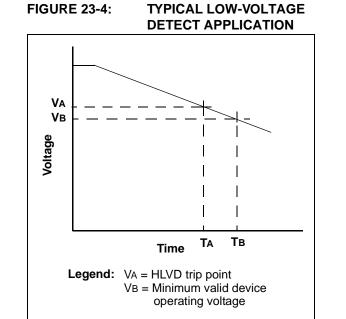

For general battery applications, Figure 23-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and a controlled shutdown before the device voltage exits the valid operating range at TB. This would give the application a time window, represented by the difference between TA and TB, to safely exit.

|                         | Complem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ent f                                    |            |                              |  |  |  |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------|------------------------------|--|--|--|--|--|--|

| Syntax:                 | COMF f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | {,d {,a}}                                |            |                              |  |  |  |  |  |  |

| Operands:               | $0 \le f \le 255$<br>d $\in [0,1]$<br>a $\in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |            |                              |  |  |  |  |  |  |

| Operation:              | $(\overline{f}) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $(\overline{f}) \rightarrow \text{dest}$ |            |                              |  |  |  |  |  |  |

| Status Affected:        | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | N, Z                                     |            |                              |  |  |  |  |  |  |

| Encoding:               | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11da                                     | ffff       | ffff                         |  |  |  |  |  |  |

| Description:            | The contents of register 'f' are<br>complemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f' (default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed |                                          |            |                              |  |  |  |  |  |  |

|                         | Literal Offs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | set Mode                                 | " for deta | uls.                         |  |  |  |  |  |  |

| Words:                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                          |            |                              |  |  |  |  |  |  |

| Cycles:                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                          |            |                              |  |  |  |  |  |  |

| -                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                          |            |                              |  |  |  |  |  |  |

| Q Cycle Activity:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                          |            |                              |  |  |  |  |  |  |

| Q Cycle Activity:<br>Q1 | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Q3                                       |            | Q4                           |  |  |  |  |  |  |

| Q Cycle Activity:       | Q2<br>Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Q3<br>Proce<br>Data                      |            | Q4<br>Write to<br>estination |  |  |  |  |  |  |

| Q Cycle Activity:<br>Q1 | Read<br>register 'f'<br>COMF<br>tion<br>= 13h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Proce<br>Data                            |            | Write to                     |  |  |  |  |  |  |

| 005050                           | CPFSEQ Compare f with W, skip if f = W |                                      |                 |  |  |  |  |  |  |

|----------------------------------|----------------------------------------|--------------------------------------|-----------------|--|--|--|--|--|--|

| CPFSEQ                           | -                                      |                                      | ID IT T = W     |  |  |  |  |  |  |

| Syntax:                          | CPFSEQ                                 | f {,a}                               |                 |  |  |  |  |  |  |

| Operands:                        | 0 ≤ f ≤ 255<br>a ∈ [0,1]               |                                      |                 |  |  |  |  |  |  |

| Operation:                       | (f) – (W),                             |                                      |                 |  |  |  |  |  |  |

|                                  | skip if $(f) = ($                      |                                      |                 |  |  |  |  |  |  |

| Statua Affaatad                  | None                                   | comparison)                          |                 |  |  |  |  |  |  |

| Status Affected:                 |                                        | 001a fff                             | f ffff          |  |  |  |  |  |  |

| Encoding:<br>Description:        | 0110                                   | 001a fff                             |                 |  |  |  |  |  |  |

| Description.                     |                                        | o the contents                       |                 |  |  |  |  |  |  |

|                                  | performing                             | an unsigned s                        | ubtraction.     |  |  |  |  |  |  |

|                                  | ,                                      | en the fetched<br>and a NOP is ex    |                 |  |  |  |  |  |  |

|                                  |                                        | king this a 2-c                      |                 |  |  |  |  |  |  |

|                                  | instruction.                           | 5                                    |                 |  |  |  |  |  |  |

|                                  |                                        | he Access Bar                        |                 |  |  |  |  |  |  |

|                                  | GPR bank.                              | he BSR is use                        | d to select the |  |  |  |  |  |  |

|                                  |                                        | nd the extende                       | ed instruction  |  |  |  |  |  |  |

|                                  |                                        | ed, this instruc                     |                 |  |  |  |  |  |  |

|                                  |                                        | Literal Offset A<br>iever f ≤ 95 (5F | 0               |  |  |  |  |  |  |

|                                  |                                        | .2.3 "Byte-Ori                       | ,               |  |  |  |  |  |  |

|                                  |                                        | d Instruction                        |                 |  |  |  |  |  |  |

|                                  |                                        | set Mode" for                        | details.        |  |  |  |  |  |  |

| Words:                           | 1                                      |                                      |                 |  |  |  |  |  |  |

| Cycles:                          | 1(2)<br>Note: 3 cv                     | ycles if skip an                     | d followed      |  |  |  |  |  |  |

|                                  |                                        | a 2-word instru                      |                 |  |  |  |  |  |  |

| Q Cycle Activity:                |                                        |                                      |                 |  |  |  |  |  |  |

| Q1                               | Q2                                     | Q3                                   | Q4              |  |  |  |  |  |  |

| Decode                           | Read                                   | Process                              | No              |  |  |  |  |  |  |

| lf skip:                         | register 'f'                           | Data                                 | operation       |  |  |  |  |  |  |

| Q1                               | Q2                                     | Q3                                   | Q4              |  |  |  |  |  |  |

| No                               | No                                     | No                                   | No              |  |  |  |  |  |  |

| operation<br>If skip and followe | operation                              | operation                            | operation       |  |  |  |  |  |  |

| Q1                               | Q2                                     | Q3                                   | Q4              |  |  |  |  |  |  |

| No                               | No                                     | No                                   | No              |  |  |  |  |  |  |

| operation                        | operation                              | operation                            | operation       |  |  |  |  |  |  |

| No<br>operation                  | No<br>operation                        | No<br>operation                      | No<br>operation |  |  |  |  |  |  |

|                                  |                                        |                                      |                 |  |  |  |  |  |  |

| Example:                         | HERE<br>NEOUAL                         | CPFSEQ REG                           | , 0             |  |  |  |  |  |  |

|                                  | EQUAL                                  | :                                    |                 |  |  |  |  |  |  |

| Before Instruc                   | ction                                  |                                      |                 |  |  |  |  |  |  |

| PC Addr                          |                                        | RE                                   |                 |  |  |  |  |  |  |

| W                                | = ?                                    |                                      |                 |  |  |  |  |  |  |

| REG<br>After Instructi           | = ?                                    |                                      |                 |  |  |  |  |  |  |

| If REG                           | = W;                                   |                                      |                 |  |  |  |  |  |  |

| PC                               | ,                                      |                                      |                 |  |  |  |  |  |  |

| If REG                           |                                        | ≠ W;                                 |                 |  |  |  |  |  |  |

| PC = Address (NEQUAL)            |                                        |                                      |                 |  |  |  |  |  |  |

## 25.2 Extended Instruction Set

In addition to the standard 75 instructions of the PIC18 instruction set, PIC18(L)F2X/4XK22 devices also provide an optional extension to the core CPU functionality. The added features include eight additional instructions that augment indirect and indexed addressing operations and the implementation of Indexed Literal Offset Addressing mode for many of the standard PIC18 instructions.

The additional features of the extended instruction set are disabled by default. To enable them, users must set the XINST Configuration bit.

The instructions in the extended set can all be classified as literal operations, which either manipulate the File Select Registers, or use them for indexed addressing. Two of the instructions, ADDFSR and SUBFSR, each have an additional special instantiation for using FSR2. These versions (ADDULNK and SUBULNK) allow for automatic return after execution.

The extended instructions are specifically implemented to optimize re-entrant program code (that is, code that is recursive or that uses a software stack) written in high-level languages, particularly C. Among other things, they allow users working in high-level languages to perform certain operations on data structures more efficiently. These include:

- dynamic allocation and deallocation of software stack space when entering and leaving subroutines

- function pointer invocation

- software Stack Pointer manipulation

- manipulation of variables located in a software stack

A summary of the instructions in the extended instruction set is provided in Table 25-3. Detailed descriptions are provided in **Section 25.2.2 "Extended Instruction Set**". The opcode field descriptions in Table 25-1 apply to both the standard and extended PIC18 instruction sets.

Note: The instruction set extension and the Indexed Literal Offset Addressing mode were designed for optimizing applications written in C; the user may likely never use these instructions directly in assembler. The syntax for these commands is provided as a reference for users who may be reviewing code that has been generated by a compiler.

## 25.2.1 EXTENDED INSTRUCTION SYNTAX

Most of the extended instructions use indexed arguments, using one of the File Select Registers and some offset to specify a source or destination register. When an argument for an instruction serves as part of indexed addressing, it is enclosed in square brackets ("[]"). This is done to indicate that the argument is used as an index or offset. MPASM<sup>™</sup> Assembler will flag an error if it determines that an index or offset value is not bracketed.