Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

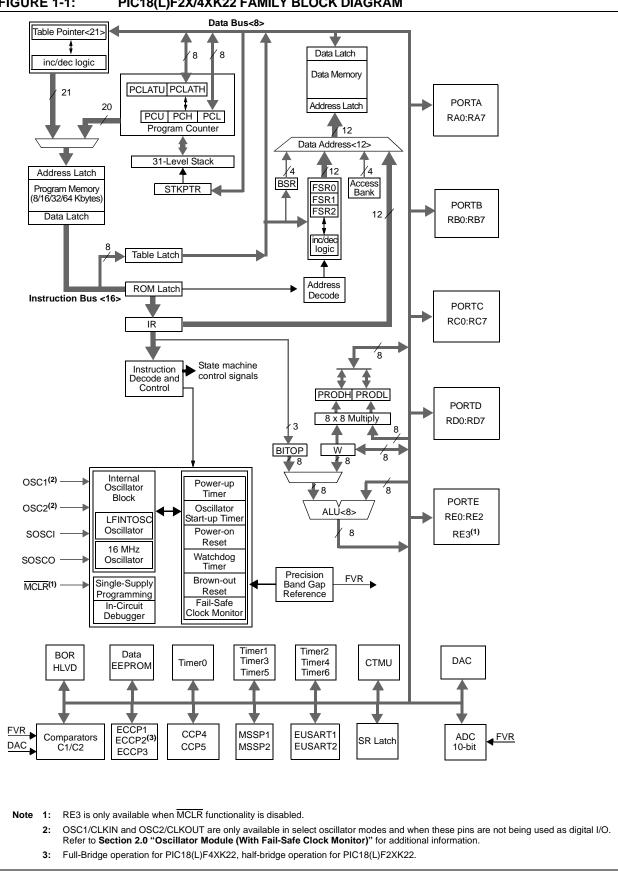

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1.5K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25k22t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                           | 11   |

|-------|---------------------------------------------------------------------------|------|

| 2.0   | Oscillator Module (With Fail-Safe Clock Monitor))                         | . 25 |

| 3.0   | Power-Managed Modes                                                       | . 44 |

| 4.0   | Reset                                                                     | . 55 |

| 5.0   | Memory Organization                                                       | . 64 |

| 6.0   | Flash Program Memory                                                      | . 90 |

| 7.0   | Data EEPROM Memory                                                        | . 99 |

| 8.0   | 8 x 8 Hardware Multiplier                                                 | 104  |

| 9.0   | Interrupts                                                                | 106  |

| 10.0  | I/O Ports                                                                 | 127  |

| 11.0  | Timer0 Module                                                             | 154  |

| 12.0  | Timer1/3/5 Module with Gate Control                                       | 157  |

| 13.0  | Timer2/4/6 Module                                                         | 169  |

| 14.0  | Capture/Compare/PWM Modules                                               |      |

| 15.0  | Master Synchronous Serial Port (MSSP1 and MSSP2) Module                   | 204  |

| 16.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |      |

| 17.0  | Analog-to-Digital Converter (ADC) Module                                  |      |

| 18.0  | Comparator Module                                                         | 302  |

| 19.0  | Charge Time Measurement Unit (CTMU)                                       | 311  |

| 20.0  | SR LATCH                                                                  |      |

| 21.0  | Fixed Voltage Reference (FVR)                                             | 331  |

| 22.0  | Digital-to-Analog Converter (DAC) Module                                  | 333  |

| 23.0  | High/Low-Voltage Detect (HLVD)                                            | 337  |

| 24.0  | Special Features of the CPU                                               | 343  |

| 25.0  | Instruction Set Summary                                                   | 360  |

| 26.0  | Development Support                                                       | 410  |

| 27.0  | Electrical Specifications                                                 | 414  |

| 28.0  | DC and AC Characteristics Graphs and Tables                               | 453  |

| 29.0  | Packaging Information                                                     | 509  |

| Appe  | ndix A: Revision History                                                  | 534  |

| Appe  | ndix B: Device Differences                                                | 535  |

| The M | Aicrochip Web Site                                                        | 536  |

| Custo | omer Change Notification Service                                          | 536  |

| Custo | omer Support                                                              | 536  |

| Produ | uct Identification System                                                 | 537  |

|       |                                                                           |      |

# 2.4 Clock Source Modes

Clock Source modes can be classified as external or internal.

- External Clock modes rely on external circuitry for the clock source. Examples are: Clock modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC mode) circuits.

- Internal clock sources are contained internally within the Oscillator block. The Oscillator block has three internal oscillators: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz Medium-Frequency Internal Oscillator (MFINTOSC) and the 31.25 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS<1:0>) bits of the OSCCON register. See **Section 2.11 "Clock Switching"** for additional information.

# 2.5 External Clock Modes

### 2.5.1 OSCILLATOR START-UP TIMER (OST)

When the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module. When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 2-2.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see **Section 2.12 "Two-Speed Clock Start-up Mode"**).

| TABLE 2-2. OSCILLATOR DELAT EXAMPLES |                                  |                                                          |                                      |  |  |  |  |  |  |

|--------------------------------------|----------------------------------|----------------------------------------------------------|--------------------------------------|--|--|--|--|--|--|

| Switch From                          | Switch To                        | Frequency                                                | Oscillator Delay                     |  |  |  |  |  |  |

| Sleep/POR/BOR                        | LFINTOSC<br>MFINTOSC<br>HFINTOSC | 31.25 kHz<br>31.25 kHz to 500 kHz<br>31.25 kHz to 16 MHz | Oscillator Start-up Delay (Tiosc_st) |  |  |  |  |  |  |

| Sleep/POR/BOR                        | EC, RC                           | DC – 64 MHz                                              | 2 instruction cycles                 |  |  |  |  |  |  |

| LFINTOSC (31.25 kHz)                 | EC, RC                           | DC – 64 MHz                                              | 1 cycle of each                      |  |  |  |  |  |  |

| Sleep/POR/BOR                        | LP, XT, HS                       | 32 kHz to 40 MHz                                         | 1024 Clock Cycles (OST)              |  |  |  |  |  |  |

| Sleep/POR/BOR                        | 4xPLL                            | 32 MHz to 64 MHz                                         | 1024 Clock Cycles (OST) + 2 ms       |  |  |  |  |  |  |

| LFINTOSC (31.25 kHz)                 | LFINTOSC<br>HFINTOSC             | 31.25 kHz to 16 MHz                                      | 1 μs (approx.)                       |  |  |  |  |  |  |

# TABLE 2-2: OSCILLATOR DELAY EXAMPLES

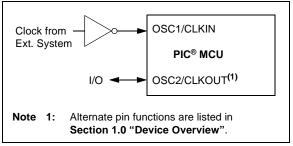

## 2.5.2 EC MODE

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 2-5 shows the pin connections for EC mode.

The External Clock (EC) offers different power modes, Low Power (ECLP), Medium Power (ECMP) and High Power (ECHP), selectable by the FOSC<3:0> bits. Each mode is best suited for a certain range of frequencies. The ranges are:

- ECLP below 500 kHz

- ECMP between 500 kHz and 16 MHz

- ECHP above 16 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep.

Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

|          | 00111 |       |       |       |        |        |        |        |                     |  |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|--|

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |

| CONFIG2L |       |       |       | BORV  | <1:0>  | BOREI  | N<1:0> | PWRTEN | 346                 |  |

| CONFIG2H | _     | _     |       | WDPS  | 6<3:0> |        | WDTE   | N<1:0> | 347                 |  |

| CONFIG3H | MCLRE | —     | P2BMX | T3CMX | HFOFST | CCP3MX | PBADEN | CCP2MX | 348                 |  |

| CONFIG4L | DEBUG | XINST |       |       |        | LVP    |        | STRVEN | 349                 |  |

TABLE 4-5: CONFIGURATION REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for Resets.

| Name                  | Bit 7    | Bit 6     | Bit 5     | Bit 4        | Bit 3        | Bit 2         | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|----------|-----------|-----------|--------------|--------------|---------------|--------|--------|---------------------|

| INTCON                | GIE/GIEH | PEIE/GIEL | TMR0IE    | INT0IE       | RBIE         | TMR0IF        | INT0IF | RBIF   | 109                 |

| EEADR                 | EEADR7   | EEADR6    | EEADR5    | EEADR4       | EEADR3       | EEADR2        | EEADR1 | EEADR0 | —                   |

| EEADRH <sup>(1)</sup> |          | —         | —         | _            | —            | —             | EEADR9 | EEADR8 | —                   |

| EEDATA                |          |           | EE        | PROM Dat     | a Register   |               |        |        | —                   |

| EECON2                |          | EEPR      | OM Contro | I Register 2 | 2 (not a phy | sical registe | er)    |        | —                   |

| EECON1                | EEPGD    | CFGS      | —         | FREE         | WRERR        | WREN          | WR     | RD     | 100                 |

| IPR2                  | OSCFIP   | C1IP      | C2IP      | EEIP         | BCL1IP       | HLVDIP        | TMR3IP | CCP2IP | 122                 |

| PIR2                  | OSCFIF   | C1IF      | C2IF      | EEIF         | BCL1IF       | HLVDIF        | TMR3IF | CCP2IF | 113                 |

| PIE2                  | OSCFIE   | C1IE      | C2IE      | EEIE         | BCL1IE       | HLVDIE        | TMR3IE | CCP2IE | 118                 |

# TABLE 7-1: REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

Legend: — = unimplemented, read as '0'. Shaded bits are not used during EEPROM access.

Note 1: PIC18(L)F26K22 and PIC18(L)F46K22 only.

# **10.7 Port Analog Control**

Most port pins are multiplexed with analog functions such as the Analog-to-Digital Converter and comparators. When these I/O pins are to be used as analog inputs it is necessary to disable the digital input buffer to avoid excessive current caused by improper biasing of the digital input. Individual control of the digital input buffers on pins which share analog functions is provided by the ANSELA, ANSELB, ANSELC, ANSELD and ANSELE registers. Setting an ANSx bit high will disable the associated digital input buffer and cause all reads of that pin to return '0' while allowing analog functions of that pin to operate correctly.

The state of the ANSx bits has no affect on digital output functions. A pin with the associated TRISx bit clear and ANSx bit set will still operate as a digital output but the input mode will be analog. This can cause unexpected behavior when performing readmodify-write operations on the affected port.

All ANSEL register bits default to '1' upon POR and BOR, disabling digital inputs for their associated port pins. All TRIS register bits default to '1' upon POR or BOR, disabling digital outputs for their associated port pins. As a result, all port pins that have an ANSEL register will default to analog inputs upon POR or BOR.

## 10.8 Port Slew Rate Control

The output slew rate of each port is programmable to select either the standard transition rate or a reduced transition rate of approximately 0.1 times the standard to minimize EMI. The reduced transition time is the default slew rate for all ports.

| 10.9 | Register | <b>Definitions</b> – | Port Control |

|------|----------|----------------------|--------------|

|------|----------|----------------------|--------------|

# REGISTER 10-1: PORTX<sup>(1)</sup>: PORTX REGISTER

| R/W-u/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

| Rx7     | Rx6     | Rx5     | Rx4     | Rx3     | Rx2     | Rx1     | Rx0     |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Logona.                    |                             |                                    |

|----------------------------|-----------------------------|------------------------------------|

| R = Readable bit           | W = Writable bit            | U = Unimplemented bit, read as '0' |

| '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown                 |

| -n/n = Value at POR and BO | R/Value at all other Resets |                                    |

bit 7-0 Rx<7:0>: PORTx I/O bit values<sup>(2)</sup>

**Note 1:** Register Description for PORTA, PORTB, PORTC and PORTD.

2: Writes to PORTx are written to corresponding LATx register. Reads from PORTx register is return of I/O pin values.

### 14.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PRx is 255. The resolution is a function of the PRx register value as shown by Equation 14-4.

### EQUATION 14-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PRx+1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

# TABLE 14-7: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 32 MHz)

| PWM Frequency             | 1.95 kHz | 7.81 kHz | 31.25 kHz | 125 kHz | 250 kHz | 333.3 kHz |

|---------------------------|----------|----------|-----------|---------|---------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1       | 1       | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F    | 0x1F    | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8       | 7       | 6.6       |

### TABLE 14-8: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

### TABLE 14-9: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PRx Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

## 14.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMRx register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMRx will continue from its previous state.

#### 14.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 2.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

## 14.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

| R/W-0                                   | R/W-0      | R/W-0                                 | R/W-0        | R/W-0                                                 | R/W-0             | R/W-0          | R/W-0          |  |  |  |

|-----------------------------------------|------------|---------------------------------------|--------------|-------------------------------------------------------|-------------------|----------------|----------------|--|--|--|

| PxRSEN                                  |            |                                       |              | PxDC<6:0>                                             |                   |                |                |  |  |  |

| bit 7                                   |            |                                       |              |                                                       |                   |                | bit 0          |  |  |  |

|                                         |            |                                       |              |                                                       |                   |                |                |  |  |  |

| Legend:                                 |            |                                       |              |                                                       |                   |                |                |  |  |  |

| R = Readable bit W = Writable bit       |            |                                       | bit          | U = Unimpler                                          | nented bit, read  | d as '0'       |                |  |  |  |

| u = Bit is unchanged x = Bit is unknown |            |                                       | nown         | -n/n = Value at POR and BOR/Value at all other Resets |                   |                |                |  |  |  |

| '1' = Bit is set                        | t          | '0' = Bit is clea                     | ared         |                                                       |                   |                |                |  |  |  |

|                                         |            |                                       |              |                                                       |                   |                |                |  |  |  |

| bit 7                                   | PxRSEN: P  | WM Restart Ena                        | able bit     |                                                       |                   |                |                |  |  |  |

|                                         | •          | uto-shutdown, th<br>'M restarts auton |              | bit clears automa                                     | atically once the | e shutdown eve | ent goes away; |  |  |  |

|                                         | 0 = Upon a | uto-shutdown, C                       | CPxASE mus   | st be cleared in s                                    | software to rest  | tart the PWM   |                |  |  |  |

| bit 6-0                                 | PxDC<6:0>  | : PWM Delay Co                        | ount bits    |                                                       |                   |                |                |  |  |  |

|                                         | PxDCx = N  | umber of Fosc/                        | 4 (4 * Tosc) | cycles between                                        | the scheduled     | d time when a  | a PWM signal   |  |  |  |

#### REGISTER 14-6: PWMxCON: ENHANCED PWM CONTROL REGISTER

### REGISTER 14-7: PSTRxCON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-1 |

|-------|-----|-----|----------|-------|-------|-------|-------|

| —     | —   | —   | STRxSYNC | STRxD | STRxC | STRxB | STRxA |

| bit 7 |     |     |          |       |       |       | bit 0 |

should transition active and the actual time it transitions active

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                         |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <b>STRxSYNC:</b> Steering Sync bit<br>1 = Output steering update occurs on next PWM period<br>0 = Output steering update occurs at the beginning of the instruction cycle boundary |

| bit 3   | <b>STRxD:</b> Steering Enable bit D<br>1 = PxD pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxD pin is assigned to port pin                               |

| bit 2   | <b>STRxC:</b> Steering Enable bit C<br>1 = PxC pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxC pin is assigned to port pin                               |

| bit 1   | <b>STRxB:</b> Steering Enable bit B<br>1 = PxB pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxB pin is assigned to port pin                               |

| bit 0   | <b>STRxA:</b> Steering Enable bit A<br>1 = PxA pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxA pin is assigned to port pin                               |

| Note 1. | The DWM Steering mode is evoluble only when the CCDyCON register hits CCDyM (20) 11.0                                                                                              |

**Note 1:** The PWM Steering mode is available only when the CCPxCON register bits CCPxM<3:2> = 11 and PxM<1:0> = 00.

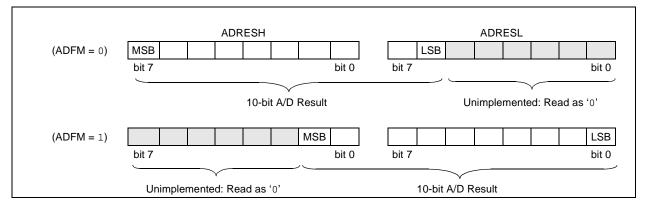

# 17.1.7 RESULT FORMATTING

The 10-bit A/D conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON2 register controls the output format.

Figure 17-2 shows the two output formats.

# FIGURE 17-2: 10-BIT A/D CONVERSION RESULT FORMAT

### EXAMPLE 19-3: CAPACITANCE CALIBRATION ROUTINE

```

#include "p18cxxx.h"

#define COUNT 25

//@ 8MHz INTFRC = 62.5 us.

#define ETIME COUNT*2.5

//time in uS

#define DELAY for(i=0;i<COUNT;i++)</pre>

#define ADSCALE 1023

//for unsigned conversion 10 sig

bits

#define ADREF 3.3

//Vdd connected to A/D Vr+

#define RCAL .027

//R value is 4200000 (4.2M)

//scaled so that result is in

//1/100th of uA

int main(void)

{

int i;

int j = 0;

//index for loop

unsigned int Vread = 0;

float CTMUISrc, CTMUCap, Vavg, VTot, Vcal;

//assume CTMU and A/D have been set up correctly

//see Example 25-1 for CTMU & A/D setup

setup();

CTMUCONHbits.CTMUEN = 1;

//Enable the CTMU

CTMUCONLbits.EDG1STAT = 0;

// Set Edge status bits to zero

CTMUCONLbits.EDG2STAT = 0;

for(j=0;j<10;j++)</pre>

{

CTMUCONHbits.IDISSEN = 1;

//drain charge on the circuit

//wait 125us

DELAY;

CTMUCONHbits.IDISSEN = 0;

//end drain of circuit

CTMUCONLbits.EDG1STAT = 1;

//Begin charging the circuit

//using CTMU current source

//wait for 125us

DELAY;

CTMUCONLbits.EDG1STAT = 0;

//Stop charging circuit

PIR1bits.ADIF = 0;

//make sure A/D Int not set

ADCON0bits.GO=1;

//and begin A/D conv.

while(!PIR1bits.ADIF);

//Wait for A/D convert complete

Vread = ADRES;

//Get the value from the A/D

PIR1bits.ADIF = 0;

//Clear A/D Interrupt Flag

VTot += Vread;

//Add the reading to the total

}

Vavg = (float)(VTot/10.000);

//Average of 10 readings

Vcal = (float)(Vavg/ADSCALE*ADREF);

//CTMUISrc is in 1/100ths of uA

CTMUISrc = Vcal/RCAL;

CTMUCap = (CTMUISrc*ETIME/Vcal)/100;

```

#### 25.1.1 STANDARD INSTRUCTION SET

| ADDLW             | ADD liter               | al to W         |                  | ADDWF                          | ADD W to                | o f                                                |                                     |

|-------------------|-------------------------|-----------------|------------------|--------------------------------|-------------------------|----------------------------------------------------|-------------------------------------|

| Syntax:           | ADDLW                   | k               |                  | Syntax:                        | ADDWF                   | f {,d {,a}}                                        |                                     |

| Operands:         | $0 \le k \le 255$       |                 |                  | Operands:                      | $0 \leq f \leq 255$     | $0 \le f \le 255$                                  |                                     |

| Operation:        | $(W) + k \rightarrow V$ | W               |                  |                                | d ∈ [0,1]               |                                                    |                                     |

| Status Affected:  | N, OV, C, E             | DC, Z           |                  | Oneration                      | $a \in [0,1]$           | deet                                               |                                     |

| Encoding:         | 0000                    | 1111 kk         | kk kkkk          | Operation:<br>Status Affected: | $(W) + (f) \rightarrow$ |                                                    |                                     |

| Description:      | The conten              | ts of W are ac  | lded to the      |                                | N, OV, C, E             |                                                    |                                     |

|                   |                         | 'k' and the res | ult is placed in | Encoding:                      | 0010                    |                                                    | ff ffff                             |

|                   | W.                      |                 |                  | Description:                   |                         | egister 'f'. If 'd<br>pred in W. If 'd             |                                     |

| Words:            | 1                       |                 |                  |                                | result is sto           | ored back in re                                    |                                     |

| Cycles:           | 1                       |                 |                  |                                | (default).              |                                                    |                                     |

| Q Cycle Activity: | 00                      | 00              | 0.4              |                                | ,                       |                                                    | nk is selected.<br>ed to select the |

| Q1                | Q2                      | Q3              | Q4               |                                | GPR bank.               |                                                    |                                     |

| Decode            | Read<br>literal 'k'     | Process<br>Data | Write to W       |                                |                         |                                                    | ed instruction ction operates       |

| Example:          | ADDLW 1                 | 15h             |                  |                                | in Indexed<br>mode wher | Literal Offset<br>never f ≤ 95 (5<br>.2.3 "Byte-Or | Addressing<br>Fh). See              |

| Before Instru     | ction                   |                 |                  |                                |                         | •                                                  | is in Indexed                       |

| W =               | 10h                     |                 |                  |                                | Literal Offe            | set Mode" for                                      | details.                            |

| After Instructi   | on                      |                 |                  | Words:                         | 1                       |                                                    |                                     |

| W =               | 25h                     |                 |                  | Cycles:                        | 1                       |                                                    |                                     |

|                   |                         |                 |                  |                                |                         |                                                    |                                     |

|                   |                         |                 |                  | Q Cycle Activity:              |                         |                                                    |                                     |

|                   |                         |                 |                  | Q1                             | Q2                      | Q3                                                 | Q4                                  |

|                   |                         |                 |                  | Decode                         | Read                    | Process                                            | Write to                            |

|                   |                         |                 |                  |                                | register 'f'            | Data                                               | destination                         |

|                   |                         |                 |                  | Example:                       | ADDWF                   | REG, 0, 0                                          | )                                   |

|                   |                         |                 |                  | Before Instruc                 | ction                   |                                                    |                                     |

|                   |                         |                 |                  | W                              | = 17h                   |                                                    |                                     |

|                   |                         |                 |                  | REG<br>After Instruction       | = 0C2h<br>on            |                                                    |                                     |

Note: All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

W

REG

0D9h

0C2h

=

=

**Branch if Not Zero**

0001

incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

2-cycle instruction.

If the ZERO bit is '0', then the program

The 2's complement number '2n' is added to the PC. Since the PC will have

Q3

Process

Data

No

operation

Q3

Process

Data

BNZ Jump

address (HERE)

address (Jump)

1; address (HERE + 2)

nnnn

nnnn

Q4

Write to PC

No

operation

Q4

No

operation

BNZ n  $\textbf{-128} \leq n \leq 127$ if ZERO bit is '0'  $(PC) + 2 + 2n \rightarrow PC$

| BNC         | <b>DV</b>                                             | Branch if                                                                 | Not Overflo                                                                          | w                                                      | BNZ   | 2                                                   | Brand                                                                             | ch if                                                 |

|-------------|-------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------|-------|-----------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------|

| Synta       | ax:                                                   | BNOV n                                                                    |                                                                                      |                                                        | Synt  | ax:                                                 | BNZ                                                                               | n                                                     |

| Oper        | ands:                                                 | -128 ≤ n ≤ 1                                                              | 127                                                                                  |                                                        | Ope   | rands:                                              | <b>-</b> 128 ≤                                                                    | n ≤ 1                                                 |

| Oper        | ation:                                                | if OVERFL0<br>(PC) + 2 + 2                                                |                                                                                      |                                                        | Ope   | ration:                                             | if ZER<br>(PC) +                                                                  |                                                       |

| Statu       | is Affected:                                          | None                                                                      |                                                                                      |                                                        | Statu | is Affected:                                        | None                                                                              |                                                       |

| Enco        | oding:                                                | 1110                                                                      | 0101 nn                                                                              | nn nnnn                                                | Enco  | oding:                                              | 111                                                                               | 0                                                     |

| Desc        | ription:                                              | program wil<br>The 2's con<br>added to the<br>incrementer<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the<br>the new addro<br>n. This instruc | iber '2n' is<br>he PC will have<br>next<br>ess will be |       | sription:                                           | If the 2<br>will bra<br>The 2'<br>added<br>increm<br>instruc<br>PC + 2<br>2-cycle | anch.<br>s com<br>to the<br>nentee<br>tion,<br>2 + 2r |

| Word        | ds:                                                   | 1                                                                         |                                                                                      |                                                        | Word  | ds:                                                 | 1                                                                                 |                                                       |

| Cycle       | es:                                                   | 1(2)                                                                      |                                                                                      |                                                        | Cycl  | es:                                                 | 1(2)                                                                              |                                                       |

|             | ycle Activity:<br>Imp:                                |                                                                           |                                                                                      |                                                        |       | ycle Activity:<br>Imp:                              |                                                                                   |                                                       |

|             | Q1                                                    | Q2                                                                        | Q3                                                                                   | Q4                                                     | _     | Q1                                                  | Q2                                                                                |                                                       |

|             | Decode                                                | Read literal<br>'n'                                                       | Process<br>Data                                                                      | Write to PC                                            |       | Decode                                              | Read lit<br>'n'                                                                   | eral                                                  |

|             | No<br>operation                                       | No<br>operation                                                           | No<br>operation                                                                      | No<br>operation                                        |       | No<br>operation                                     | No<br>operati                                                                     | ion                                                   |

| If No       | o Jump:                                               |                                                                           |                                                                                      | •                                                      | If N  | o Jump:                                             |                                                                                   |                                                       |

|             | Q1                                                    | Q2                                                                        | Q3                                                                                   | Q4                                                     | _     | Q1                                                  | Q2                                                                                |                                                       |

|             | Decode                                                | Read literal<br>'n'                                                       | Process<br>Data                                                                      | No<br>operation                                        |       | Decode                                              | Read lit<br>'n'                                                                   | eral                                                  |

| <u>Exar</u> | nple:                                                 | HERE                                                                      | BNOV Jump                                                                            | )                                                      | Exar  | nple:                                               | HERE                                                                              |                                                       |

|             | Before Instruc<br>PC                                  | = ad                                                                      | dress (HERE                                                                          | )                                                      |       | Before Instruc<br>PC                                | =                                                                                 | ade                                                   |

|             | After Instruction<br>If OVERI<br>PC<br>If OVERI<br>PC | FLOW = 0;<br>= ad<br>FLOW = 1;                                            | dress (Jump<br>dress (HERE                                                           |                                                        |       | After Instruction<br>If ZERO<br>PC<br>If ZERO<br>PC | on<br>=<br>=<br>=<br>=                                                            | 0;<br>ado<br>1;<br>ado                                |

| TSTFS                                                                           | z                                                  | Test f, ski                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | p if 0             |                 |  |

|---------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|--|

| Syntax:                                                                         |                                                    | TSTFSZ f {                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | a}                 |                 |  |

| Operand                                                                         | ls:                                                | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |                 |  |

| Operatio                                                                        | on:                                                | skip if f = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |                 |  |

| Status A                                                                        | ffected:                                           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |                 |  |

| Encodin                                                                         | g:                                                 | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 011a fff           | f ffff          |  |

| Descript                                                                        | ion:                                               | If 'f' = 0, the next instruction fetched<br>during the current instruction execution<br>is discarded and a NOP is executed,<br>making this a 2-cycle instruction.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                    |                 |  |

| Words:                                                                          |                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |                 |  |

| Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction. |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |                 |  |

| Q Cycle                                                                         | e Activity:                                        | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |                 |  |

|                                                                                 | Q1                                                 | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q3                 | Q4              |  |

|                                                                                 | Decode                                             | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Process<br>Data    | No<br>operation |  |

| If skip:                                                                        |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |                 |  |

|                                                                                 | Q1                                                 | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q3                 | Q4              |  |

|                                                                                 | No                                                 | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                 | No              |  |

|                                                                                 | peration                                           | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | operation          | operation       |  |

| п экір а                                                                        | Q1                                                 | d by 2-word in:<br>Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q3                 | Q4              |  |

|                                                                                 | No                                                 | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                 | No              |  |

| c                                                                               | peration                                           | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | operation          | operation       |  |

|                                                                                 | No                                                 | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                 | No              |  |

|                                                                                 | peration                                           | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | operation          | operation       |  |

| <u>Example</u>                                                                  | <u>2</u> :                                         | HERE T<br>NZERO S<br>ZERO S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    | , 1             |  |

|                                                                                 | ore Instruc<br>PC<br>er Instructic<br>If CNT<br>PC | = Ad<br>on<br>= 00<br>= Ad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | dress (ZERO)       |                 |  |

|                                                                                 | If CNT<br>PC                                       | ≠ 00<br>= Ad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | h,<br>dress (NZERO | )               |  |

| XORLW                                                                             | Exclusiv                   | Exclusive OR literal with W |     |       |      |  |

|-----------------------------------------------------------------------------------|----------------------------|-----------------------------|-----|-------|------|--|

| Syntax:                                                                           | XORLW                      | k                           |     |       |      |  |

| Operands:                                                                         | perands: $0 \le k \le 255$ |                             |     |       |      |  |

| Operation:                                                                        | (W) .XOR                   | $. k \rightarrow W$         |     |       |      |  |

| Status Affected:                                                                  | N, Z                       |                             |     |       |      |  |

| Encoding:                                                                         | 0000                       | 1010                        | kkk | k k   | kkk  |  |

| Description: The contents of W are XO<br>the 8-bit literal 'k'. The resu<br>in W. |                            |                             |     |       |      |  |

| Words:                                                                            | 1                          |                             |     |       |      |  |

| Cycles:                                                                           | 1                          |                             |     |       |      |  |

| Q Cycle Activity:                                                                 |                            |                             |     |       |      |  |

| Q1                                                                                | Q2                         | Q3                          |     | Q     | 4    |  |

| Decode                                                                            | Read<br>literal 'k'        | Proce<br>Data               |     | Write | to W |  |

| Example:                                                                          | XORLW                      | 0AFh                        |     |       |      |  |

| Before Instruc                                                                    | tion                       |                             |     |       |      |  |

| W                                                                                 | = B5h                      |                             |     |       |      |  |

| After Instruction                                                                 | on                         |                             |     |       |      |  |

| W | = | 1Ah |

|---|---|-----|

# 26.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 26.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

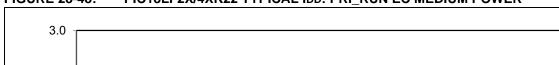

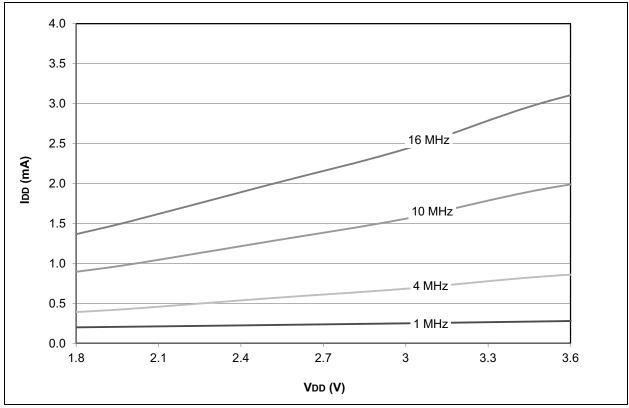

FIGURE 28-49: PIC18LF2X/4XK22 MAXIMUM IDD: PRI\_RUN EC MEDIUM POWER

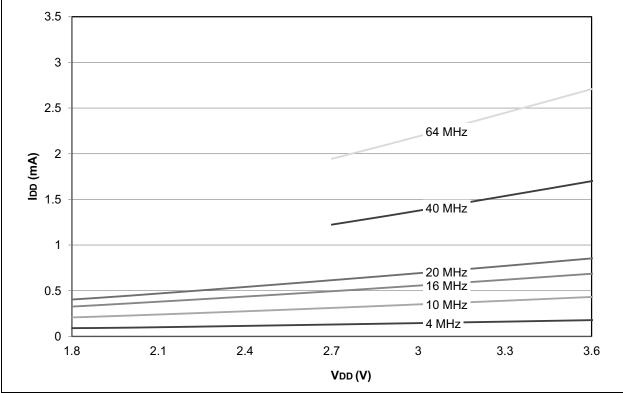

FIGURE 28-65: PIC18LF2X/4XK22 MAXIMUM IDD: PRI\_IDLE EC HIGH POWER

DS40001412G-page 486

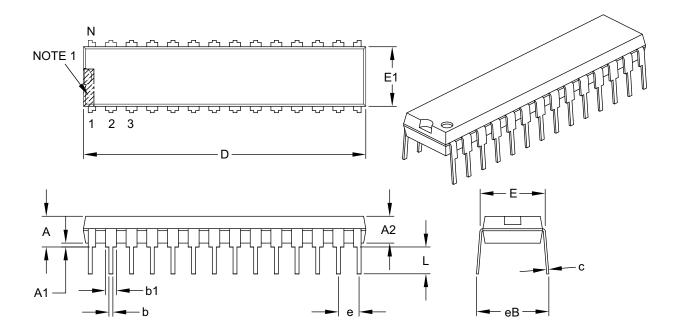

# 29.2 Package Details

The following sections give the technical details of the packages.

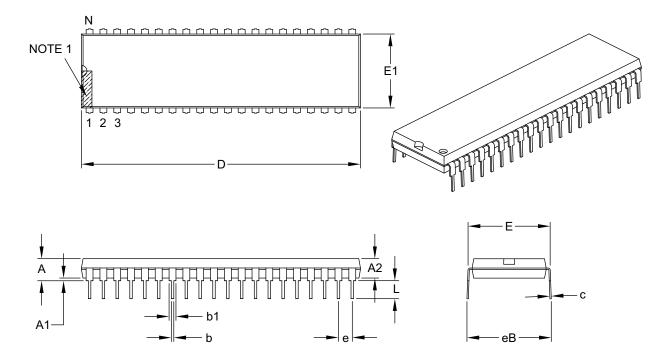

# 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |  |

|----------------------------|------------------|-------|----------|-------|--|

|                            | Dimension Limits | MIN   | NOM      | MAX   |  |

| Number of Pins             | N                |       | 28       |       |  |

| Pitch                      | e                |       | .100 BSC |       |  |

| Top to Seating Plane       | A                | _     | -        | .200  |  |

| Molded Package Thickness   | A2               | .120  | .135     | .150  |  |

| Base to Seating Plane      | A1               | .015  | -        | _     |  |

| Shoulder to Shoulder Width | E                | .290  | .310     | .335  |  |

| Molded Package Width       | E1               | .240  | .285     | .295  |  |

| Overall Length             | D                | 1.345 | 1.365    | 1.400 |  |

| Tip to Seating Plane       | L                | .110  | .130     | .150  |  |

| Lead Thickness             | С                | .008  | .010     | .015  |  |

| Upper Lead Width           | b1               | .040  | .050     | .070  |  |

| Lower Lead Width           | b                | .014  | .018     | .022  |  |

| Overall Row Spacing §      | eB               | _     | -        | .430  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

# 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |

|----------------------------|------------------|-------|----------|-------|

|                            | Dimension Limits | MIN   | NOM      | MAX   |

| Number of Pins             | N                |       | 40       |       |

| Pitch                      | e                |       | .100 BSC |       |

| Top to Seating Plane       | A                | -     | -        | .250  |

| Molded Package Thickness   | A2               | .125  | -        | .195  |

| Base to Seating Plane      | A1               | .015  | -        | _     |

| Shoulder to Shoulder Width | E                | .590  | -        | .625  |

| Molded Package Width       | E1               | .485  | -        | .580  |

| Overall Length             | D                | 1.980 | -        | 2.095 |

| Tip to Seating Plane       | L                | .115  | -        | .200  |

| Lead Thickness             | С                | .008  | -        | .015  |

| Upper Lead Width           | b1               | .030  | -        | .070  |

| Lower Lead Width           | b                | .014  | -        | .023  |

| Overall Row Spacing §      | eB               | _     | -        | .700  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B

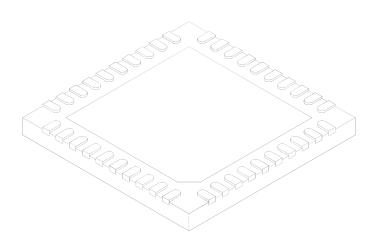

40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |          |           | S    |

|------------------------|------------------|----------|-----------|------|

| Dimensi                | Dimension Limits |          |           | MAX  |

| Number of Pins         | Ν                |          | 40        |      |

| Pitch                  | е                |          | 0.40 BSC  |      |

| Overall Height         | Α                | 0.45     | 0.50      | 0.55 |

| Standoff               | A1               | 0.00     | 0.02      | 0.05 |

| Contact Thickness      | A3               |          | 0.127 REF |      |

| Overall Width          | E                | 5.00 BSC |           |      |

| Exposed Pad Width      | E2               | 3.60     | 3.70      | 3.80 |

| Overall Length         | D                |          | 5.00 BSC  |      |

| Exposed Pad Length     | D2               | 3.60     | 3.70      | 3.80 |

| Contact Width          | b                | 0.15     | 0.20      | 0.25 |

| Contact Length         | L                | 0.30     | 0.40      | 0.50 |

| Contact-to-Exposed Pad | К                | 0.20     | -         | -    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-156A Sheet 2 of 2