Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 19x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k22-e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F23K22 PIC18LF23K22

- PIC18F24K22 PIC18LF24K22

- PIC18F25K22

PIC18LF25K22

- PIC18F26K22 PIC18LF26K22

- PIC18F43K22 PIC18LF43K22

- PIC18F44K22 PIC18LF44K22

- PIC18F45K22 PIC18LF45K22

- PIC18F46K22 PIC18LF46K22

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Flash program memory. On top of these features, the PIC18(L)F2X/4XK22 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

#### 1.1 New Core Features

#### 1.1.1 XLP TECHNOLOGY

All of the devices in the PIC18(L)F2X/4XK22 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- **On-the-fly Mode Switching:** The powermanaged modes are invoked by user code during operation, allowing the user to incorporate powersaving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 27.0 "Electrical Specifications" for values.

#### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18(L)F2X/4XK22 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O)

- Two External RC Oscillator modes with the same pin options as the External Clock modes

- An internal oscillator block which contains a 16 MHz HFINTOSC oscillator and a 31 kHz LFINTOSC oscillator, which together provide eight user selectable clock frequencies, from 31 kHz to 16 MHz. This option frees the two oscillator pins for use as additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both external and internal oscillator modes, which allows clock speeds of up to 64 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 64 MHz – all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the LFINTOSC. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or Wake-up from Sleep mode, until the primary clock source is available.

|          | 00111 |       |       |             |        |        |        |        |                     |  |  |  |  |  |

|----------|-------|-------|-------|-------------|--------|--------|--------|--------|---------------------|--|--|--|--|--|

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |  |  |  |  |

| CONFIG2L |       |       |       | BORV        | <1:0>  | BOREI  | N<1:0> | PWRTEN | 346                 |  |  |  |  |  |

| CONFIG2H | _     | -     |       | WDPS        | 6<3:0> |        | WDTE   | 347    |                     |  |  |  |  |  |

| CONFIG3H | MCLRE | —     | P2BMX | P2BMX T3CMX |        | CCP3MX | PBADEN | CCP2MX | 348                 |  |  |  |  |  |

| CONFIG4L | DEBUG | XINST |       |             |        | LVP    |        | STRVEN | 349                 |  |  |  |  |  |

TABLE 4-5: CONFIGURATION REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for Resets.

## PIC18(L)F2X/4XK22

## 6.3 Register Definitions: Memory Control

#### REGISTER 6-1: EECON1: DATA EEPROM CONTROL 1 REGISTER

| R/W-x         | R/W-x            | U-0                                  | R/W-0           | R/W-x                                 | R/W-0            | R/S-0           | R/S-0         |

|---------------|------------------|--------------------------------------|-----------------|---------------------------------------|------------------|-----------------|---------------|

| EEPGD         | CFGS             | —                                    | FREE            | WRERR                                 | WREN             | WR              | RD            |

| bit 7         |                  |                                      |                 |                                       |                  |                 | bit           |

| Legend:       |                  |                                      |                 |                                       |                  |                 |               |

| R = Readable  | e bit            | W = Writable                         | bit             |                                       |                  |                 |               |

| S = Bit can b | e set by softwar | e. but not clea                      | red             | U = Unimpler                          | nented bit, read | d as '0'        |               |

| -n = Value at | POR              | '1' = Bit is se                      | t               | '0' = Bit is cle                      | ared             | x = Bit is unkr | nown          |

|               |                  |                                      |                 |                                       |                  |                 |               |

| bit 7         | EEPGD: Flas      | h Program or                         | Data EEPRON     | A Memory Selec                        | ct bit           |                 |               |

|               |                  | -<br>lash program                    |                 | -                                     |                  |                 |               |

|               |                  | lata EEPROM                          | ,               |                                       |                  |                 |               |

| bit 6         | CFGS: Flash      | Program/Data                         | EEPROM or       | Configuration S                       | elect bit        |                 |               |

|               |                  | Configuration r                      | 0               |                                       |                  |                 |               |

| 6.4 C         |                  |                                      | or data EEPR    | Ow memory                             |                  |                 |               |

| bit 5         | •                | ted: Read as                         |                 | •.                                    |                  |                 |               |

| bit 4         |                  | ( )                                  | rase Enable b   |                                       | DTD on the ne    |                 | ad            |

|               |                  |                                      | of erase opera  | dressed by TBL<br>ation)              | PIR on the ne    | Xt WR commar    | 10            |

|               | 0 = Perform      |                                      |                 |                                       |                  |                 |               |

| bit 3         | WRERR: Fla       | sh Program/Da                        | ata EEPROM I    | Error Flag bit <sup>(1)</sup>         |                  |                 |               |

|               | 1 = A write o    | peration is pre                      | maturely termi  | nated (any Res                        | et during self-t | imed programn   | ning in norma |

|               | •                |                                      | per write attem | pt)                                   |                  |                 |               |

|               | 0 = 1 he write   | e operation cor                      | npleted         |                                       |                  |                 |               |

| bit 2         | WREN: Flash      | n Program/Dat                        | a EEPROM W      | rite Enable bit                       |                  |                 |               |

|               |                  | •                                    |                 |                                       |                  |                 |               |

| L:1 4         |                  | •                                    | -lash program   | /data EEPROM                          |                  |                 |               |

| bit 1         | WR: Write Co     |                                      | Maraaa/writa    |                                       |                  |                 |               |

|               |                  |                                      |                 | cycle or a progra<br>it is cleared by |                  |                 |               |

|               | · ·              |                                      |                 | ed) by software                       |                  |                 |               |

|               | 0 = Write cyc    | cle to the EEPI                      | ROM is comple   | ete                                   |                  |                 |               |

| bit 0         | RD: Read Co      |                                      |                 |                                       |                  |                 |               |

|               |                  |                                      |                 | s one cycle. RD                       |                  |                 |               |

|               |                  | ot cleared) by :<br>t initiate an EE |                 | it cannot be set                      | wnen EEPGD       | = 1  or CFGS =  | 1.)           |

|               | 0 = D0es 10      |                                      | r itow leau     |                                       |                  |                 |               |

## **Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

#### TABLE 10-1: PORTA I/O SUMMARY

| Pin Name                       | Function | TRIS<br>Setting | ANSEL<br>Setting | Pin<br>Type | Buffer<br>Type | Description                                                                                                          |

|--------------------------------|----------|-----------------|------------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------|

| RA0/C12IN0-/AN0                | RA0      | 0               | 0                | 0           | DIG            | LATA<0> data output; not affected by analog input.                                                                   |

|                                |          | 1               | 0                | Ι           | TTL            | PORTA<0> data input; disabled when analog input enabled.                                                             |

|                                | C12IN0-  | 1               | 1                | Ι           | AN             | Comparators C1 and C2 inverting input.                                                                               |

|                                | AN0      | 1               | 1                | I           | AN             | Analog input 0.                                                                                                      |

| RA1/C12IN1-/AN1                | RA1      | 0               | 0                | 0           | DIG            | LATA<1> data output; not affected by analog input.                                                                   |

|                                |          | 1               | 0                | I           | TTL            | PORTA<1> data input; disabled when analog input enabled.                                                             |

|                                | C12IN1-  | 1               | 1                | I           | AN             | Comparators C1 and C2 inverting input.                                                                               |

|                                | AN1      | 1               | 1                | I           | AN             | Analog input 1.                                                                                                      |

| RA2/C2IN+/AN2/<br>DACOUT/VREF- | RA2      | 0               | 0                | 0           | DIG            | LATA<2> data output; not affected by analog input; disabled when DACOUT enabled.                                     |

|                                |          | 1               | 0                | Ι           | TTL            | PORTA<2> data input; disabled when analog input enabled;<br>disabled when DACOUT enabled.                            |

|                                | C2IN+    | 1               | 1                | Ι           | AN             | Comparator C2 non-inverting input.                                                                                   |

|                                | AN2      | 1               | 1                | Ι           | AN             | Analog output 2.                                                                                                     |

|                                | DACOUT   | x               | 1                | 0           | AN             | DAC Reference output.                                                                                                |

|                                | VREF-    | 1               | 1                | Ι           | AN             | A/D reference voltage (low) input.                                                                                   |

| RA3/C1IN+/AN3/                 | RA3      | 0               |                  | 0           | DIG            | LATA<3> data output; not affected by analog input.                                                                   |

| VREF+                          |          | 1               | 0                | I           | TTL            | PORTA<3> data input; disabled when analog input enabled.                                                             |

|                                | C1IN+    | 1               | 1                | I           | AN             | Comparator C1 non-inverting input.                                                                                   |

|                                | AN3      | 1               | 1                | I           | AN             | Analog input 3.                                                                                                      |

|                                | VREF+    | 1               | 1                | I           | AN             | A/D reference voltage (high) input.                                                                                  |

| RA4/CCP5/C1OUT/                | RA4      | 0               | —                | 0           | DIG            | LATA<4> data output.                                                                                                 |

| SRQ/T0CKI                      |          | 1               | _                | I           | ST             | PORTA<4> data input; default configuration on POR.                                                                   |

|                                | CCP5     | 0               | _                | 0           | DIG            | CCP5 Compare output/PWM output, takes priority over RA4 output                                                       |

|                                |          | 1               | —                | Ι           | ST             | Capture 5 input/Compare 5 output/ PWM 5 output.                                                                      |

|                                | C1OUT    | 0               | _                | 0           | DIG            | Comparator C1 output.                                                                                                |

|                                | SRQ      | 0               | _                | 0           | DIG            | SR latch Q output; take priority over CCP 5 output.                                                                  |

|                                | TOCKI    | 1               | _                | I           | ST             | Timer0 external clock input.                                                                                         |

| RA5/C2OUT/SRNQ/                | RA5      | 0               | 0                | 0           | DIG            | LATA<5> data output; not affected by analog input.                                                                   |

| SS1/<br>HLVDIN/AN4             |          | 1               | 0                | I           | TTL            | PORTA<5> data input; disabled when analog input enabled.                                                             |

| HLVDIN/AN4                     | C2OUT    | 0               | 0                | 0           | DIG            | Comparator C2 output.                                                                                                |

|                                | SRNQ     | 0               | 0                | 0           | DIG            | SR latch $\overline{Q}$ output.                                                                                      |

|                                | SS1      | 1               | 0                | I           | TTL            | SPI slave select input (MSSP1).                                                                                      |

|                                | HLVDIN   | 1               | 1                | I           | AN             | High/Low-Voltage Detect input.                                                                                       |

|                                | AN4      | 1               | 1                | 1           | AN             | A/D input 4.                                                                                                         |

| RA6/CLKO/OSC2                  | RA6      | 0               | _                | 0           | DIG            | LATA<6> data output; enabled in INTOSC modes when CLKO is no<br>enabled.                                             |

|                                |          | 1               | —                | Ι           | TTL            | PORTA<6> data input; enabled in INTOSC modes when CLKO is not enabled.                                               |

|                                | CLKO     | x               | —                | 0           | DIG            | In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the fre-<br>quency of OSC1 and denotes the instruction cycle rate. |

|                                | OSC2     | x               | _                | 0           | XTAL           | Oscillator crystal output; connects to crystal or resonator in Crystal Oscillator mode.                              |

| RA7/CLKI/OSC1                  | RA7      | 0               | _                | 0           | DIG            | LATA<7> data output; disabled in external oscillator modes.                                                          |

|                                |          | 1               | —                | Ι           | TTL            | PORTA<7> data input; disabled in external oscillator modes.                                                          |

|                                | CLKI     | x               | —                | I           | AN             | External clock source input; always associated with pin function OSC1.                                               |

|                                | OSC1     | x               |                  | Ι           | XTAL           | Oscillator crystal input or external clock source input ST buffer wher<br>configured in RC mode; CMOS otherwise.     |

Legend: AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C.

#### 10.5 PORTD Registers

| Note: | PORTD is only available on 40-pin and |

|-------|---------------------------------------|

|       | 44-pin devices.                       |

PORTD is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., disable the output driver). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

All of the PORTD pins are multiplexed with analog and digital peripheral modules. See Table 10-11.

**Note:** On a Power-on Reset, these pins are configured as analog inputs.

EXAMPLE 10-4: INITIALIZING PORTD

| MOVLB<br>CLRF | 0xF<br>PORTD | ; Set BSR for banked SFRs<br>; Initialize PORTD by<br>; clearing output |

|---------------|--------------|-------------------------------------------------------------------------|

|               |              | ; data latches                                                          |

| CLRF          | LATD         | ; Alternate method                                                      |

|               |              | ; to clear output                                                       |

|               |              | ; data latches                                                          |

| MOVLW         | OCFh         | ; Value used to                                                         |

|               |              | ; initialize data                                                       |

|               |              | ; direction                                                             |

| MOVWF         | TRISD        | ; Set RD<3:0> as inputs                                                 |

|               |              | ; RD<5:4> as outputs                                                    |

|               |              | ; RD<7:6> as inputs                                                     |

| MOVLW         | 30h          | ; Value used to                                                         |

|               |              | ; enable digital inputs                                                 |

| MOVWF         | ANSELD       | ; RD<3:0> dig input enable                                              |

|               |              | ; RC<7:6> dig input enable                                              |

|               |              |                                                                         |

#### 10.5.1 PORTD OUTPUT PRIORITY

Each PORTD pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the higher priority. Table 10-4 lists the PORTD pin functions from the highest to the lowest priority.

Analog input functions, such as ADC, comparator and SR latch inputs, are not shown in the priority lists.

These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below.

# PIC18(L)F2X/4XK22

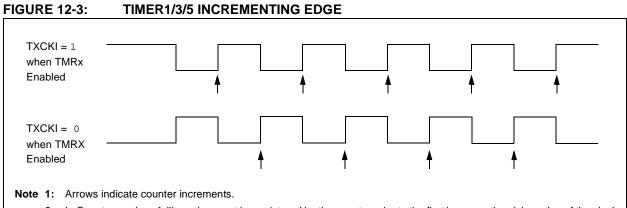

2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

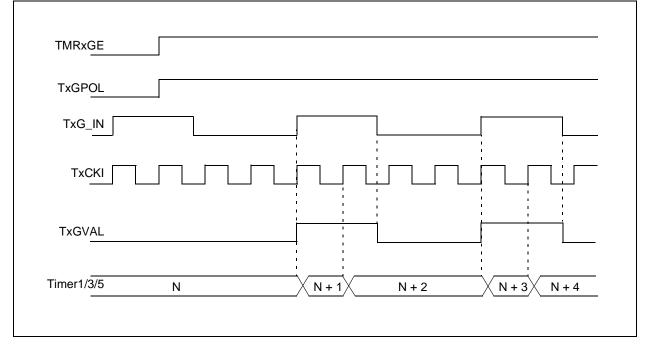

### FIGURE 12-4: TIMER1/3/5 GATE ENABLE MODE

| ECCP Mode            | PxM<1:0> | CCPx/PxA           | PxB                | PxC                | PxD                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

#### TABLE 14-12: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

**Note 1:** PWM Steering enables outputs in Single mode.

#### **FIGURE 14-6: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH** STATE)

| PxM<1:0>               | Signal        | 0 ◀ Pulse Width          | PRX+1                |

|------------------------|---------------|--------------------------|----------------------|

|                        |               | -                        | ── Period ───►       |

| 00 (Single Output)     | PxA Modulated | <br>Delay <sup>(1)</sup> | Delaý <sup>(1)</sup> |

|                        | PxA Modulated |                          |                      |

| 10 (Half-Bridge)       | PxB Modulated | _ '<br>_ <u>'</u>        |                      |

|                        | PxA Active    |                          |                      |

| (Full-Bridge,          | PxB Inactive  |                          |                      |

| <sup>01</sup> Forward) | PxC Inactive  |                          |                      |

|                        | PxD Modulated |                          |                      |

|                        | PxA Inactive  |                          |                      |

| 11 (Full-Bridge,       | PxB Modulated |                          |                      |

| Reverse)               | PxC Active    |                          |                      |

|                        | PxD Inactive  |                          |                      |

Period = 4 \* Tosc \* (PRx + 1) \* (TMRx Prescale Value)

Pulse Width = Tosc \* (CCPRxL<7:0>:CCPxCON<5:4>) \* (TMRx Prescale Value)

Delay = 4 \* Tosc \* (PWMxCON<6:0>)

Note 1: Dead-band delay is programmed using the PWMxCON register (Section 14.4.5 "Programmable Dead-Band Delay Mode").

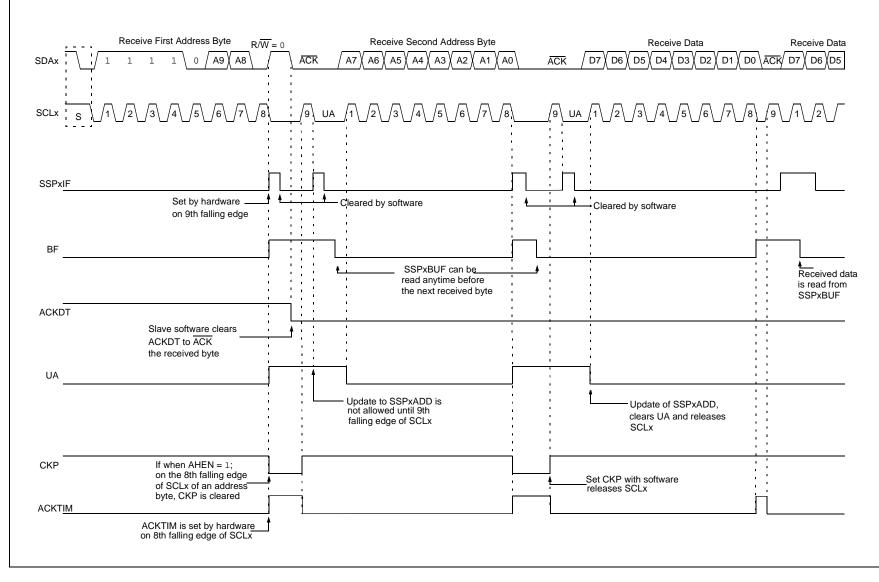

## FIGURE 15-21: I<sup>2</sup>C SLAVE, 10-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 1, DHEN = 0)

PIC18(L)F2X/4XK22

| R/W-0         | R/W-0                                                                                                                                                                                                                                  | R/W-0                                                     | R/W-0             | R/W-0           | R-0              | R-0             | R-0  |  |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------|-----------------|------------------|-----------------|------|--|--|--|--|--|--|

| SPEN          | RX9                                                                                                                                                                                                                                    | SREN                                                      | CREN              | ADDEN           | FERR             | OERR            | RX9D |  |  |  |  |  |  |

| bit 7         |                                                                                                                                                                                                                                        |                                                           |                   |                 |                  |                 | bit  |  |  |  |  |  |  |

| Legend:       |                                                                                                                                                                                                                                        |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                  | W = Writable                                              | bit               | U = Unimple     | emented bit, rea | d as '0'        |      |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                                                                                                    | '1' = Bit is se                                           | t                 | '0' = Bit is cl | eared            | x = Bit is unkr | nown |  |  |  |  |  |  |

| bit 7         | <b>SPEN:</b> Serial Port Enable bit<br>1 = Serial port enabled (configures RXx/DTx and TXx/CKx pins as serial port pins)                                                                                                               |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               |                                                                                                                                                                                                                                        | port enabled (co<br>port disabled (he                     |                   | DTx and TXx/0   | CKx pins as ser  | ial port pins)  |      |  |  |  |  |  |  |

| bit 6         | RX9: 9-bit F                                                                                                                                                                                                                           | Receive Enable                                            | bit               |                 |                  |                 |      |  |  |  |  |  |  |

|               |                                                                                                                                                                                                                                        | <ul><li>9-bit reception</li><li>8-bit reception</li></ul> |                   |                 |                  |                 |      |  |  |  |  |  |  |

| bit 5         | SREN: Sing                                                                                                                                                                                                                             | gle Receive Ena                                           | ble bit           |                 |                  |                 |      |  |  |  |  |  |  |

|               | Asynchrono                                                                                                                                                                                                                             | ous mode:                                                 |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               | Don't care                                                                                                                                                                                                                             |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               |                                                                                                                                                                                                                                        | <u>us mode – Maste</u>                                    |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               |                                                                                                                                                                                                                                        | s single receive<br>es single receive                     |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               |                                                                                                                                                                                                                                        | leared after rece                                         |                   | ete.            |                  |                 |      |  |  |  |  |  |  |

|               | <u>Synchronou</u>                                                                                                                                                                                                                      | <u>us mode – Slave</u>                                    | <u>)</u>          |                 |                  |                 |      |  |  |  |  |  |  |

|               | Don't care                                                                                                                                                                                                                             |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

| bit 4         | CREN: Continuous Receive Enable bit                                                                                                                                                                                                    |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               | Asynchronous mode:                                                                                                                                                                                                                     |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               | 1 = Enables receiver                                                                                                                                                                                                                   |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               | 0 = Disables receiver<br>Synchronous mode:                                                                                                                                                                                             |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               | <u>Synchronous mode</u> :<br>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)                                                                                                                     |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               | <ul> <li>0 = Disables continuous receive until enable bit CREM is cleared (CREM overhoes SREM)</li> </ul>                                                                                                                              |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

| bit 3         | ADDEN: Ad                                                                                                                                                                                                                              | dress Detect E                                            | nable bit         |                 |                  |                 |      |  |  |  |  |  |  |

|               | Asynchronc                                                                                                                                                                                                                             | ous mode 9-bit (                                          | <u>RX9 = 1)</u> : |                 |                  |                 |      |  |  |  |  |  |  |

|               | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set<br>0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit<br>Asynchronous mode 8-bit (RX9 = 0): |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               | Don't care                                                                                                                                                                                                                             |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

| bit 2         | FERR: Frar                                                                                                                                                                                                                             | ning Error bit                                            |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               | <ul> <li>1 = Framing error (can be updated by reading RCREGx register and receive next valid byte)</li> <li>0 = No framing error</li> </ul>                                                                                            |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

| bit 1         | OERR: Ove                                                                                                                                                                                                                              | errun Error bit                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

|               | 1 = Overru<br>0 = No ove                                                                                                                                                                                                               | n error (can be o<br>errun error                          | cleared by clea   | aring bit CREN  | 1)               |                 |      |  |  |  |  |  |  |

| <b>h</b> :+ 0 | <b>DYOD</b> . Nint                                                                                                                                                                                                                     |                                                           |                   |                 |                  |                 |      |  |  |  |  |  |  |

| bit 0         | TAJD. INITI                                                                                                                                                                                                                            | h bit of Receive                                          | d Data            |                 |                  |                 |      |  |  |  |  |  |  |

## REGISTER 16-2: RCSTAX: RECEIVE STATUS AND CONTROL REGISTER

|        |                  | SYNC = 0, BRGH = 0, BRG16 = 1 |                                 |                  |            |                                 |                   |            |                                 |                  |            |                                 |  |  |  |

|--------|------------------|-------------------------------|---------------------------------|------------------|------------|---------------------------------|-------------------|------------|---------------------------------|------------------|------------|---------------------------------|--|--|--|

| BAUD   | Fosc = 8.000 MHz |                               |                                 | Fosc = 4.000 MHz |            |                                 | Fosc = 3.6864 MHz |            |                                 | Fosc = 1.000 MHz |            |                                 |  |  |  |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRGHx:<br>SPBRGx<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRGHx:<br>SPBRGx<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRGHx<br>:SPBRGx<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRGHx:<br>SPBRGx<br>(decimal) |  |  |  |

| 300    | 299.9            | -0.02                         | 1666                            | 300.1            | 0.04       | 832                             | 300.0             | 0.00       | 767                             | 300.5            | 0.16       | 207                             |  |  |  |

| 1200   | 1199             | -0.08                         | 416                             | 1202             | 0.16       | 207                             | 1200              | 0.00       | 191                             | 1202             | 0.16       | 51                              |  |  |  |

| 2400   | 2404             | 0.16                          | 207                             | 2404             | 0.16       | 103                             | 2400              | 0.00       | 95                              | 2404             | 0.16       | 25                              |  |  |  |

| 9600   | 9615             | 0.16                          | 51                              | 9615             | 0.16       | 25                              | 9600              | 0.00       | 23                              | _                | _          | _                               |  |  |  |

| 10417  | 10417            | 0.00                          | 47                              | 10417            | 0.00       | 23                              | 10473             | 0.53       | 21                              | 10417            | 0.00       | 5                               |  |  |  |

| 19.2k  | 19.23k           | 0.16                          | 25                              | 19.23k           | 0.16       | 12                              | 19.20k            | 0.00       | 11                              | _                | _          | _                               |  |  |  |

| 57.6k  | 55556            | -3.55                         | 8                               | —                | _          | _                               | 57.60k            | 0.00       | 3                               | _                | _          | _                               |  |  |  |

| 115.2k | _                | _                             | _                               | _                | _          | _                               | 115.2k            | 0.00       | 1                               | _                | _          | _                               |  |  |  |

## TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                     |            |                                 | SYNC           | <b>C</b> = 0, BR | GH = 1, BRG1                    | 6 = 1 or S     | 'NC = 1, E | 3RG16 = 1                       |                    |            |                                 |

|--------|---------------------|------------|---------------------------------|----------------|------------------|---------------------------------|----------------|------------|---------------------------------|--------------------|------------|---------------------------------|

| BAUD   | D Fosc = 64.000 MHz |            | Fosc = 18.432 MHz               |                |                  | Fosc = 16.000 MHz               |                |            | Fos                             | Fosc = 11.0592 MHz |            |                                 |

| RATE   | Actual<br>Rate      | %<br>Error | SPBRGHx:<br>SPBRGx<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRGHx:<br>SPBRGx<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRGHx<br>:SPBRGx<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRGHx:<br>SPBRGx<br>(decimal) |

| 300    | 300                 | 0.00       | 53332                           | 300.0          | 0.00             | 15359                           | 300.0          | 0.00       | 13332                           | 300.0              | 0.00       | 9215                            |

| 1200   | 1200                | 0.00       | 13332                           | 1200           | 0.00             | 3839                            | 1200.1         | 0.01       | 3332                            | 1200               | 0.00       | 2303                            |

| 2400   | 2400                | 0.00       | 6666                            | 2400           | 0.00             | 1919                            | 2399.5         | -0.02      | 1666                            | 2400               | 0.00       | 1151                            |

| 9600   | 9598.1              | -0.02      | 1666                            | 9600           | 0.00             | 479                             | 9592           | -0.08      | 416                             | 9600               | 0.00       | 287                             |

| 10417  | 10417               | 0.00       | 1535                            | 10425          | 0.08             | 441                             | 10417          | 0.00       | 383                             | 10433              | 0.16       | 264                             |

| 19.2k  | 19.21k              | 0.04       | 832                             | 19.20k         | 0.00             | 239                             | 19.23k         | 0.16       | 207                             | 19.20k             | 0.00       | 143                             |

| 57.6k  | 57.55k              | -0.08      | 277                             | 57.60k         | 0.00             | 79                              | 57.97k         | 0.64       | 68                              | 57.60k             | 0.00       | 47                              |

| 115.2k | 115.11k             | -0.08      | 138                             | 115.2k         | 0.00             | 39                              | 114.29k        | -0.79      | 34                              | 115.2k             | 0.00       | 23                              |

|        |                  |            |                                 | SYNC           | <b>C</b> = 0, BR | GH = 1, BRG1                    | 6 = 1 or S     | /NC = 1, I | BRG16 = 1                       |                |            |                                 |

|--------|------------------|------------|---------------------------------|----------------|------------------|---------------------------------|----------------|------------|---------------------------------|----------------|------------|---------------------------------|

| BAUD   | Fosc = 8.000 MHz |            | Fos                             | sc = 4.00      | 0 MHz            | Fosc = 3.6864 MHz               |                |            | Fosc = 1.000 MHz                |                |            |                                 |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRGHx:<br>SPBRGx<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRGHx:<br>SPBRGx<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRGHx<br>:SPBRGx<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRGHx:<br>SPBRGx<br>(decimal) |

| 300    | 300.0            | 0.00       | 6666                            | 300.0          | 0.01             | 3332                            | 300.0          | 0.00       | 3071                            | 300.1          | 0.04       | 832                             |

| 1200   | 1200             | -0.02      | 1666                            | 1200           | 0.04             | 832                             | 1200           | 0.00       | 767                             | 1202           | 0.16       | 207                             |

| 2400   | 2401             | 0.04       | 832                             | 2398           | 0.08             | 416                             | 2400           | 0.00       | 383                             | 2404           | 0.16       | 103                             |

| 9600   | 9615             | 0.16       | 207                             | 9615           | 0.16             | 103                             | 9600           | 0.00       | 95                              | 9615           | 0.16       | 25                              |

| 10417  | 10417            | 0.00       | 191                             | 10417          | 0.00             | 95                              | 10473          | 0.53       | 87                              | 10417          | 0.00       | 23                              |

| 19.2k  | 19.23k           | 0.16       | 103                             | 19.23k         | 0.16             | 51                              | 19.20k         | 0.00       | 47                              | 19.23k         | 0.16       | 12                              |

| 57.6k  | 57.14k           | -0.79      | 34                              | 58.82k         | 2.12             | 16                              | 57.60k         | 0.00       | 15                              | _              | _          | —                               |

| 115.2k | 117.6k           | 2.12       | 16                              | 111.1k         | -3.55            | 8                               | 115.2k         | 0.00       | 7                               |                | _          | —                               |

## 18.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of the program execution. The analog comparator module includes the following features:

- Independent comparator control

- Programmable input selection

- Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- Wake-up from Sleep

- Programmable Speed/Power optimization

- PWM shutdown

- · Programmable and fixed voltage reference

- Selectable Hysteresis

#### 18.1 Comparator Overview

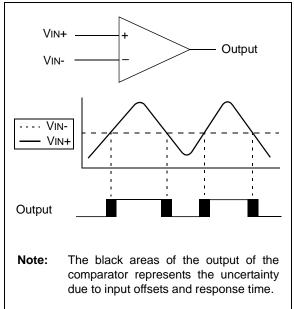

A single comparator is shown in Figure 18-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

#### FIGURE 18-1: SINGLE COMPARATOR

| U-0           | U-0                    | R/P-1            | R/P-1             | R/P-1             | R/P-1               | R/P-1           | R/P-1 |

|---------------|------------------------|------------------|-------------------|-------------------|---------------------|-----------------|-------|

| _             | —                      |                  | WDTI              | PS<3:0>           |                     | WDTEN<1:0>      |       |

| bit 7         |                        |                  |                   |                   |                     |                 | bit   |

|               |                        |                  |                   |                   |                     |                 |       |

| Legend:       |                        |                  |                   |                   |                     |                 |       |

| R = Readable  | e bit                  | P = Programma    | ble bit           | U = Unimpleme     | nted bit, read as ' | 0'              |       |

| -n = Value wh | nen device is unprogra | ammed            |                   | x = Bit is unknow | wn                  |                 |       |

|               |                        |                  |                   |                   |                     |                 |       |

| bit 7-6       | Unimplemented          | I: Read as '0'   |                   |                   |                     |                 |       |

| bit 5-2       | WDTPS<3:0>: V          | Vatchdog Timer   | Postscale Selec   | t bits            |                     |                 |       |

|               | 1111 = 1:32,768        | •                |                   |                   |                     |                 |       |

|               | 1110 = 1:16,384        | Ļ                |                   |                   |                     |                 |       |

|               | 1101 = 1:8,192         |                  |                   |                   |                     |                 |       |

|               | 1100 = 1:4,096         |                  |                   |                   |                     |                 |       |

|               | 1011 = 1:2,048         |                  |                   |                   |                     |                 |       |

|               | 1010 = 1:1,024         |                  |                   |                   |                     |                 |       |

|               | 1001 = <b>1:512</b>    |                  |                   |                   |                     |                 |       |

|               | 1000 <b>= 1:256</b>    |                  |                   |                   |                     |                 |       |

|               | 0111 = <b>1:128</b>    |                  |                   |                   |                     |                 |       |

|               | 0110 = 1:64            |                  |                   |                   |                     |                 |       |

|               | 0101 = 1:32            |                  |                   |                   |                     |                 |       |

|               | 0100 = 1:16            |                  |                   |                   |                     |                 |       |

|               | 0011 = 1:8             |                  |                   |                   |                     |                 |       |

|               | 0010 = 1:4             |                  |                   |                   |                     |                 |       |

|               | 0001 = 1:2             |                  |                   |                   |                     |                 |       |

|               | 0000 = 1:1             |                  |                   |                   |                     |                 |       |

| bit 1-0       | WDTEN<1:0>: \          | Vatchdog Timer   | Enable bits       |                   |                     |                 |       |

|               | 11 = WDT enabl         | led in hardware; | SWDTEN bit dis    | abled             |                     |                 |       |

|               | 10 = WDT control       |                  |                   |                   |                     |                 |       |

|               | 01 = WDT enab          | led when device  | is active, disabl | ed when device is | in Sleep; SWDTE     | EN bit disabled |       |

|               |                        | led in hardware; |                   |                   | 1,7 -               |                 |       |

#### REGISTER 24-3: CONFIG2H: CONFIGURATION REGISTER 2 HIGH

## 27.0 ELECTRICAL SPECIFICATIONS

## Absolute Maximum Ratings (†)

| Ambient temperature under bias                                | 40°C to +125°C       |

|---------------------------------------------------------------|----------------------|

| Storage temperature                                           | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD, and MCLR) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to VSS                            |                      |

| PIC18LF24K22                                                  | -0.3V to +4.5V       |

| PIC18(L)F26K22                                                | -0.3V to +6.5V       |

| Voltage on MCLR with respect to Vss (Note 2)                  | 0V to +11.0V         |

| Total power dissipation (Note 1)                              | 1.0W                 |

| Maximum current out of Vss pin (-40°C to +85°C)               | 300 mA               |

| Maximum current out of Vss pin (+85°C to +125°C)              | 125 mA               |

| Maximum current into VDD pin (-40°C to +85°C)                 | 200 mA               |

| Maximum current into VDD pin (+85°C to +125°C)                | 85 mA                |

| Input clamp current, Iικ (Vi < 0 or Vi > VDD)                 | ±20 mA               |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                | ±20 mA               |

| Maximum output current sunk by any I/O pin                    | 25 mA                |

| Maximum output current sourced by any I/O pin                 | 25 mA                |

| Maximum current sunk by all ports (-40°C to +85°C)            | 200 mA               |

| Maximum current sunk by all ports (+85°C to +125°C)           | 110 mA               |

| Maximum current sourced by all ports (-40°C to +85°C)         | 185 mA               |

| Maximum current sourced by all ports (+85°C to +125°C)        | 70 mA                |

- **Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD  $-\sum$  IOH} +  $\sum$  {(VDD - VOH) x IOH} +  $\sum$ (VOL x IOL)

- 2: Voltage spikes below Vss at the MCLR/VPP/RE3 pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP/ RE3 pin, rather than pulling this pin directly to Vss.

**† NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### 27.4 DC Characteristics: RC Idle Supply Current, PIC18(L)F2X/4XK22

| PIC18LF2X/4XK22 |                                         | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |       |                 |            |                                                             |  |  |  |

|-----------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------|------|-------|-----------------|------------|-------------------------------------------------------------|--|--|--|

| PIC18F2X/4XK22  |                                         | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |       |                 |            |                                                             |  |  |  |

| Param<br>No.    | Device Characteristics                  | Тур                                                                                                                  | Max  | Units |                 | 5          |                                                             |  |  |  |

| D045            | Supply Current (IDD) <sup>(1),(2)</sup> | 0.5                                                                                                                  | 18   | μΑ    | -40°C           | VDD = 1.8V | Fosc = 31 kHz                                               |  |  |  |

|                 |                                         | 0.6                                                                                                                  | 18   | μΑ    | +25°C           |            | ( <b>RC_IDLE</b> mode,<br>LFINTOSC source)                  |  |  |  |

|                 |                                         | 0.7                                                                                                                  | —    | μΑ    | +60°C           |            |                                                             |  |  |  |

|                 |                                         | 0.75                                                                                                                 | 20   | μΑ    | +85°C           |            |                                                             |  |  |  |

|                 |                                         | 2.3                                                                                                                  | 22   | μΑ    | +125°C          |            |                                                             |  |  |  |

| D046            |                                         | 1.1                                                                                                                  | 20   | μΑ    | -40°C           | VDD = 3.0V |                                                             |  |  |  |

|                 |                                         | 1.2                                                                                                                  | 20   | μΑ    | +25°C           |            |                                                             |  |  |  |

|                 |                                         | 1.3                                                                                                                  | —    | μΑ    | +60°C           |            |                                                             |  |  |  |

|                 |                                         | 1.4                                                                                                                  | 22   | μΑ    | +85°C           |            |                                                             |  |  |  |

|                 |                                         | 3.2                                                                                                                  | 25   | μΑ    | +125°C          |            |                                                             |  |  |  |

| D047            |                                         | 17                                                                                                                   | 30   | μΑ    | -40°C           | VDD = 2.3V | Fosc = 31 kHz<br>( <b>RC_IDLE</b> mode,<br>LFINTOSC source) |  |  |  |

|                 |                                         | 13                                                                                                                   | 30   | μΑ    | +25°C           |            |                                                             |  |  |  |

|                 |                                         | 14                                                                                                                   | 30   | μΑ    | +85°C           |            |                                                             |  |  |  |

|                 |                                         | 15                                                                                                                   | 45   | μΑ    | +125°C          |            |                                                             |  |  |  |

| D048            |                                         | 19                                                                                                                   | 35   | μΑ    | -40°C           | VDD = 3.0V |                                                             |  |  |  |

|                 |                                         | 15                                                                                                                   | 35   | μΑ    | +25°C           |            |                                                             |  |  |  |

|                 |                                         | 16                                                                                                                   | 35   | μΑ    | +85°C           |            |                                                             |  |  |  |

|                 |                                         | 17                                                                                                                   | 50   | μΑ    | +125°C          |            |                                                             |  |  |  |

| D049            |                                         | 21                                                                                                                   | 40   | μΑ    | -40°C           | VDD = 5.0V |                                                             |  |  |  |

|                 |                                         | 15                                                                                                                   | 40   | μΑ    | +25°C           |            |                                                             |  |  |  |

|                 |                                         | 16                                                                                                                   | 40   | μΑ    | +85°C           |            |                                                             |  |  |  |

|                 |                                         | 18                                                                                                                   | 60   | μΑ    | +125°C          |            |                                                             |  |  |  |

| D050            |                                         | 0.11                                                                                                                 | 0.20 | mA    | -40°C to +125°C | VDD = 1.8V | Fosc = 500 kHz                                              |  |  |  |

| D051            |                                         | 0.12                                                                                                                 | 0.25 | mA    | -40°C to +125°C | VDD = 3.0V | ( <b>RC_IDLE</b> mode,<br>MFINTOSC source)                  |  |  |  |

| D052            |                                         | 0.14                                                                                                                 | 0.21 | mA    | -40°C to +125°C | VDD = 2.3V | Fosc = 500 kHz                                              |  |  |  |

| D053            |                                         | 0.15                                                                                                                 | 0.25 | mA    | -40°C to +125°C | VDD = 3.0V | ( <b>RC_IDLE</b> mode,<br>MFINTOSC source)                  |  |  |  |

| D054            |                                         | 0.20                                                                                                                 | 0.31 | mA    | -40°C to +125°C | VDD = 5.0V |                                                             |  |  |  |

**Note 1:** The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

Test condition: All Peripheral Module Control bits in PMD0, PMD1 and PMD2 set to '1'.

2: The test conditions for all IDD measurements in active operation mode are:

All I/O pins set as outputs driven to Vss;

$\overline{MCLR} = VDD;$

OSC1 = external square wave, from rail-to-rail (PRI\_RUN and PRI\_IDLE only).

| PIC18LF2X/4XK22 |                        | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |       |                 |            |                                                                      |  |  |  |

|-----------------|------------------------|----------------------------------------------------------------------------------------------------------------------|------|-------|-----------------|------------|----------------------------------------------------------------------|--|--|--|

| PIC18F2X/4XK22  |                        | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |       |                 |            |                                                                      |  |  |  |

| Param<br>No.    | Device Characteristics | Тур                                                                                                                  | Max  | Units | Conditions      |            |                                                                      |  |  |  |

| D055            |                        | 0.25                                                                                                                 | 0.40 | mA    | -40°C to +125°C | Vdd = 1.8V | Fosc = 1 MHz                                                         |  |  |  |

| D056            |                        | 0.35                                                                                                                 | 0.50 | mA    | -40°C to +125°C | VDD = 3.0V | ( <b>RC_IDLE</b> mode,<br>HFINTOSC source)                           |  |  |  |

| D057            |                        | 0.30                                                                                                                 | 0.45 | mA    | -40°C to +125°C | VDD = 2.3V | Fosc = 1 MHz                                                         |  |  |  |

| D058            |                        | 0.40                                                                                                                 | 0.50 | mA    | -40°C to +125°C | VDD = 3.0V | ( <b>RC_IDLE</b> mode,<br>HFINTOSC source)                           |  |  |  |

| D059            |                        | 0.45                                                                                                                 | 0.60 | mA    | -40°C to +125°C | VDD = 5.0V |                                                                      |  |  |  |

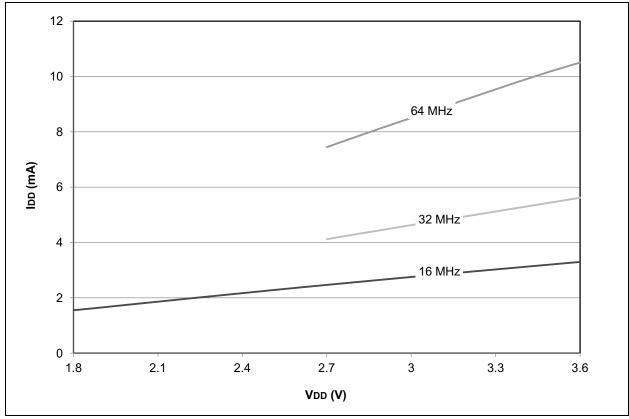

| D060            |                        | 0.50                                                                                                                 | 0.7  | mA    | -40°C to +125°C | VDD = 1.8V | Fosc = 16 MHz                                                        |  |  |  |