Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 19x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k22-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

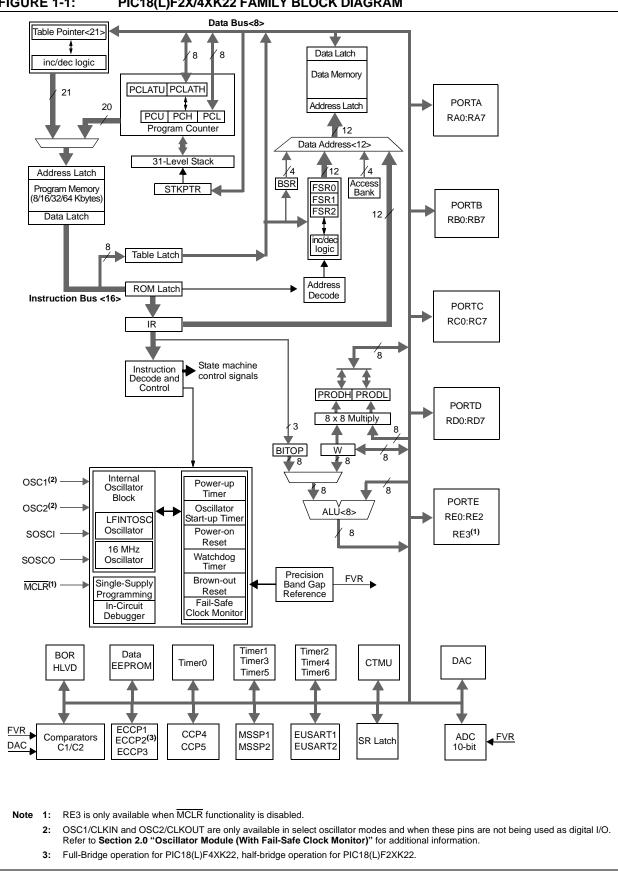

## 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F23K22 PIC18LF23K22

- PIC18F24K22 PIC18LF24K22

- PIC18F25K22

PIC18LF25K22

- PIC18F26K22 PIC18LF26K22

- PIC18F43K22 PIC18LF43K22

- PIC18F44K22 PIC18LF44K22

- PIC18F45K22 PIC18LF45K22

- PIC18F46K22 PIC18LF46K22

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Flash program memory. On top of these features, the PIC18(L)F2X/4XK22 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

#### 1.1 New Core Features

#### 1.1.1 XLP TECHNOLOGY

All of the devices in the PIC18(L)F2X/4XK22 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- **On-the-fly Mode Switching:** The powermanaged modes are invoked by user code during operation, allowing the user to incorporate powersaving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 27.0 "Electrical Specifications" for values.

#### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18(L)F2X/4XK22 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O)

- Two External RC Oscillator modes with the same pin options as the External Clock modes

- An internal oscillator block which contains a 16 MHz HFINTOSC oscillator and a 31 kHz LFINTOSC oscillator, which together provide eight user selectable clock frequencies, from 31 kHz to 16 MHz. This option frees the two oscillator pins for use as additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both external and internal oscillator modes, which allows clock speeds of up to 64 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 64 MHz – all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the LFINTOSC. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or Wake-up from Sleep mode, until the primary clock source is available.

# PIC18(L)F2X/4XK22

## 2.8 PLL Frequency Multiplier

A Phase-Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency oscillator circuit or to clock the device up to its highest rated frequency from the crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals or users who require higher clock speeds from an internal oscillator.

#### 2.8.1 PLL IN EXTERNAL OSCILLATOR MODES

The PLL can be enabled for any of the external oscillator modes using the OSC1/OSC2 pins by either setting the PLLCFG bit (CONFIG1H<4>), or setting the PLLEN bit (OSCTUNE<6>). The PLL is designed for input frequencies of 4 MHz up to 16 MHz. The PLL then multiplies the oscillator output frequency by four to produce an internal clock frequency up to 64 MHz. Oscillator frequencies below 4 MHz should not be used with the PLL.

#### 2.8.2 PLL IN HFINTOSC MODES

The 4x frequency multiplier can be used with the internal oscillator block to produce faster device clock speeds than are normally possible with the internal oscillator. When enabled, the PLL multiplies the HFINTOSC by four to produce clock rates up to 64 MHz.

Unlike external clock modes, when internal clock modes are enabled, the PLL can only be controlled through software. The PLLEN control bit of the OSCTUNE register is used to enable or disable the PLL operation when the HFINTOSC is used.

The PLL is designed for input frequencies of 4 MHz up to 16 MHz.

## 6.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed one byte at a time. A write to program memory is executed on blocks of 64 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation cannot be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

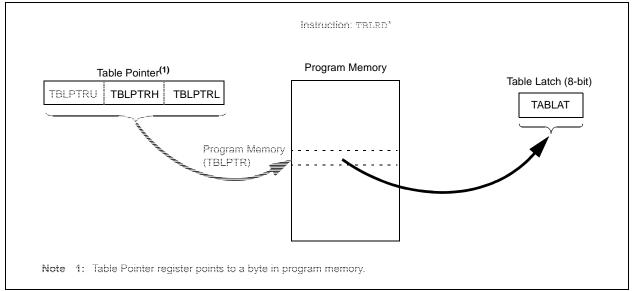

## 6.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

The table read operation retrieves one byte of data directly from program memory and places it into the TABLAT register. Figure 6-1 shows the operation of a table read.

The table write operation stores one byte of data from the TABLAT register into a write block holding register. The procedure to write the contents of the holding registers into program memory is detailed in **Section 6.6 "Writing to Flash Program Memory"**. Figure 6-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. Tables containing data, rather than program instructions, are not required to be word aligned. Therefore, a table can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

#### FIGURE 6-1: TABLE READ OPERATION

## 7.0 DATA EEPROM MEMORY

The data EEPROM is a nonvolatile memory array, separate from the data RAM and program memory, which is used for long-term storage of program data. It is not directly mapped in either the register file or program memory space but is indirectly addressed through the Special Function Registers (SFRs). The EEPROM is readable and writable during normal operation over the entire VDD range.

Four SFRs are used to read and write to the data EEPROM as well as the program memory. They are:

- EECON1

- EECON2

- EEDATA

- EEADR

- EEADRH

The data EEPROM allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and the EEADR:EEADRH register pair hold the address of the EEPROM location being accessed.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer; it will vary with voltage and temperature as well as from chip-to-chip. Please refer to the Data EEPROM Memory parameters in Section 27.0 "Electrical Specifica-tions" for limits.

## 7.1 EEADR and EEADRH Registers

The EEADR register is used to address the data EEPROM for read and write operations. The 8-bit range of the register can address a memory range of 256 bytes (00h to FFh). The EEADRH register expands the range to 1024 bytes by adding an additional two address bits.

## 7.2 EECON1 and EECON2 Registers

Access to the data EEPROM is controlled by two registers: EECON1 and EECON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The EECON1 register (Register 7-1) is the control register for data and program memory access. Control bit EEPGD determines if the access will be to program or data EEPROM memory. When the EEPGD bit is clear, operations will access the data EEPROM memory. When the EEPGD bit is set, program memory is accessed.

Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When the CFGS bit is set, subsequent operations access Configuration registers. When the CFGS bit is clear, the EEPGD bit selects either program Flash or data EEPROM memory.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear.

The WRERR bit is set by hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR         |

|-------|--------------------------------------------|

|       | may read as '1'. This can indicate that a  |

|       | write operation was prematurely termi-     |

|       | nated by a Reset, or a write operation was |

|       | attempted improperly.                      |

The WR control bit initiates write operations. The bit can be set but not cleared by software. It is cleared only by hardware at the completion of the write operation.

Note: The EEIF interrupt flag bit of the PIR2 register is set when the write is complete. It must be cleared by software.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 6.1 "Table Reads and Table Writes"** regarding table reads.

The EECON2 register is not a physical register. It is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

## 9.8 Register Definitions: Interrupt Control

| R/W-0        | R/W-0                                                                          | R/W-0                                                          | R/W-0                               | R/W-0                          | R/W-0              | R/W-0             | R/W-x |

|--------------|--------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------|--------------------------------|--------------------|-------------------|-------|

| GIE/GIE      | H PEIE/GIEL                                                                    | TMR0IE                                                         | INTOIE                              | RBIE                           | TMR0IF             | INT0IF            | RBIF  |

| bit 7        |                                                                                |                                                                |                                     |                                |                    |                   | bit ( |

|              |                                                                                |                                                                |                                     |                                |                    |                   |       |

| Legend:      |                                                                                |                                                                |                                     |                                |                    |                   |       |

| R = Readab   |                                                                                | W = Writable b                                                 | it                                  | •                              | ented bit, read as |                   |       |

| -n = Value a | it POR                                                                         | '1' = Bit is set                                               |                                     | '0' = Bit is clea              | ired               | x = Bit is unknow | vn    |

| bit 7        | When IPEN =<br>1 = Enables a<br>0 = Disables a<br>When IPEN =                  | II unmasked inter<br>III interrupts inclu-<br><u>1:</u>        | rupts<br>ding peripherals           | 5                              |                    |                   |       |

|              | 0 = Disables a                                                                 | II high priority inte<br>III interrupts inclue                 | ding low priority                   | ,                              |                    |                   |       |

| bit 6        | When IPEN =<br>1 = Enables a<br>0 = Disables a<br>When IPEN =<br>1 = Enables a | II unmasked perip<br>II peripheral inter                       | oheral interrupts<br>rupts<br>rupts | 5                              |                    |                   |       |

| bit 5        | 1 = Enables th                                                                 | 0 Overflow Interr<br>ne TMR0 overflow<br>he TMR0 overflow      | ,<br>v interrupt                    |                                |                    |                   |       |

| bit 4        | 1 = Enables th                                                                 | External Interrupt<br>ne INT0 external i<br>he INT0 external   | nterrupt                            |                                |                    |                   |       |

| bit 3        | 1 = Enables th                                                                 | nterrupt-On-Cha<br>ne IOCx port char<br>he IOCx port cha       | nge interrupt                       | rrupt Enable bit <sup>(2</sup> | 2)                 |                   |       |

| bit 2        | 1 = TMR0 reg                                                                   | 0 Overflow Interr<br>ister has overflow<br>ister did not overf | ved (must be cle                    | eared by softwar               | e)                 |                   |       |

| bit 1        | 1 = The INT0                                                                   | External Interrupt<br>external interrupt<br>external interrupt | occurred (must                      | t be cleared by s              | oftware)           |                   |       |

| bit 0        | <b>RBIF:</b> Port B I<br>1 = At least or                                       | nterrupt-On-Chai                                               | nge (IOCx) Inte<br>> (RB<7:4>) pi   | ns changed state               | e (must be cleare  | d by software)    |       |

| Note 1:      | A mismatch condition                                                           |                                                                |                                     | it. Reading POR                | TB will end the    |                   |       |

| 2:           | RB port change inte                                                            | rrupto olgo roqui                                              | o tha individual                    | nin IOCB anable                | 96                 |                   |       |

### REGISTER 9-1: INTCON: INTERRUPT CONTROL REGISTER

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

| R/W-1           | R/W-1         | R/W-1                             | R/W-1            | U-0              | R/W-1             | U-0            | R/W-1          |

|-----------------|---------------|-----------------------------------|------------------|------------------|-------------------|----------------|----------------|

| RBPU            | INTEDG0       | INTEDG1                           | INTEDG2          | —                | TMR0IP            | _              | RBIP           |

| bit 7           | •<br>•        |                                   |                  |                  |                   |                | bit            |

|                 |               |                                   |                  |                  |                   |                |                |

| Legend:         |               |                                   |                  |                  |                   |                |                |

| R = Readable    |               | W = Writable                      |                  | -                | mented bit, read  |                |                |

| -n = Value at F | POR           | '1' = Bit is set                  |                  | '0' = Bit is cle | eared             | x = Bit is unk | nown           |

|                 |               |                                   |                  |                  |                   |                |                |

| bit 7           |               | TB Pull-up Ena                    |                  |                  |                   |                |                |

|                 |               | FB pull-ups are                   |                  | that the nin i   | s an input and th | e correspondi  | na WPLIB bit i |

|                 | set.          |                                   |                  |                  | s an input and t  | ie concoponali |                |

| bit 6           | INTEDG0: E>   | kternal Interrup                  | t 0 Edge Sele    | ct bit           |                   |                |                |

|                 |               | on rising edge                    |                  |                  |                   |                |                |

|                 | -             | on falling edge                   |                  |                  |                   |                |                |

| bit 5           |               | kternal Interrup                  | t 1 Edge Sele    | ct bit           |                   |                |                |

|                 |               | on rising edge<br>on falling edge |                  |                  |                   |                |                |

| bit 4           | •             | kternal Interrup                  |                  | ot hit           |                   |                |                |

| DIL 4           |               | on rising edge                    | t z Euge Sele    |                  |                   |                |                |

|                 |               | on falling edge                   | )                |                  |                   |                |                |

| bit 3           | Unimplemen    | ted: Read as '                    | 0'               |                  |                   |                |                |

| bit 2           | TMROIP: TMI   | R0 Overflow In                    | terrupt Priority | / bit            |                   |                |                |

|                 | 1 = High prio | ority                             |                  |                  |                   |                |                |

|                 | 0 = Low prior | rity                              |                  |                  |                   |                |                |

| bit 1           | Unimplemen    | ted: Read as '                    | 0'               |                  |                   |                |                |

| bit 0           | RBIP: RB Po   | rt Change Inte                    | rrupt Priority b | it               |                   |                |                |

|                 | 1 = High prio | 2                                 |                  |                  |                   |                |                |

|                 | 0 = Low prior | P1+1/                             |                  |                  |                   |                |                |

#### REGISTER 9-2: INTCON2: INTERRUPT CONTROL 2 REGISTER

| Note: | Interrupt flag bits are set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs, regardless of the state of  |

|       | its corresponding enable bit or the global    |

|       | enable bit. User software should ensure       |

|       | the appropriate interrupt flag bits are clear |

|       | prior to enabling an interrupt. This feature  |

|       | allows for software polling.                  |

| R/W-0        | R/W-0                                             | R/W-0             | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|--------------|---------------------------------------------------|-------------------|----------------|------------------|-----------------|-----------------|--------|

| OSCFIE       | C1IE                                              | C2IE              | EEIE           | BCL1IE           | HLVDIE          | TMR3IE          | CCP2IE |

| bit 7        |                                                   |                   |                |                  |                 |                 | bit (  |

| Legend:      |                                                   |                   |                |                  |                 |                 |        |

| R = Readab   | le bit                                            | W = Writable      | bit            | U = Unimple      | mented bit, rea | d as '0'        |        |

| -n = Value a | t POR                                             | '1' = Bit is set  |                | '0' = Bit is cle | ared            | x = Bit is unki | nown   |

| bit 7        | <b>OSCFIE:</b> Osc<br>1 = Enabled<br>0 = Disabled | illator Fail Inte | rrupt Enable I | bit              |                 |                 |        |

| bit 6        | C1IE: Compa<br>1 = Enabled<br>0 = Disabled        | rator C1 Interro  | upt Enable bit | t                |                 |                 |        |

| bit 5        | <b>C2IE:</b> Compa<br>1 = Enabled<br>0 = Disabled | rator C2 Interro  | upt Enable bit | t                |                 |                 |        |

| bit 4        | EEIE: Data E<br>1 = Enabled<br>0 = Disabled       | EPROM/Flash       | Write Operat   | ion Interrupt Er | nable bit       |                 |        |

| bit 3        | BCL1IE: MSS<br>1 = Enabled<br>0 = Disabled        | SP1 Bus Collisi   | on Interrupt E | Enable bit       |                 |                 |        |

| bit 2        | HLVDIE: Low<br>1 = Enabled<br>0 = Disabled        | -Voltage Detec    | t Interrupt En | able bit         |                 |                 |        |

| bit 1        | <b>TMR3IE:</b> TMI<br>1 = Enabled<br>0 = Disabled | R3 Overflow In    | terrupt Enable | e bit            |                 |                 |        |

| bit 0        | <b>CCP2IE:</b> CCI<br>1 = Enabled<br>0 = Disabled | P2 Interrupt En   | able bit       |                  |                 |                 |        |

#### REGISTER 9-10: PIE2: PERIPHERAL INTERRUPT ENABLE (FLAG) REGISTER 2

| Name     | Bit 7   | Bit 6  | Bit 5    | Bit 4         | Bit 3     | Bit 2   | Bit 1    | Bit 0  | Register<br>on Page |

|----------|---------|--------|----------|---------------|-----------|---------|----------|--------|---------------------|

| ANSELA   | —       | _      | ANSA5    | _             | ANSA3     | ANSA2   | ANSA1    | ANSA0  | 149                 |

| CM1CON0  | C1ON    | C10UT  | C10E     | C1POL         | C1SP      | C1R     | C1CH     | l<1:0> | 308                 |

| CM2CON0  | C2ON    | C2OUT  | C2OE     | C2POL         | C2SP      | C2R     | C2CH     | l<1:0> | 308                 |

| LATA     | LATA7   | LATA6  | LATA5    | LATA4         | LATA3     | LATA2   | LATA1    | LATA0  | 152                 |

| VREFCON1 | DACEN   | DACLPS | DACOE    | —             | DACP      | SS<1:0> | —        | DACNSS | 335                 |

| VREFCON2 | —       | —      | _        |               | DACR<4:0> |         |          |        | 336                 |

| HLVDCON  | VDIRMAG | BGVST  | IRVST    | HLVDEN        |           | HLVDL   | <3:0>    |        | 337                 |

| PORTA    | RA7     | RA6    | RA5      | RA4           | RA3       | RA2     | RA1      | RA0    | 148                 |

| SLRCON   | —       | —      | _        | SLRE          | SLRD      | SLRC    | SLRB     | SLRA   | 153                 |

| SRCON0   | SRLEN   | S      | RCLK<2:0 | >             | SRQEN     | SRNQEN  | SRPS     | SRPR   | 329                 |

| SSP1CON1 | WCOL    | SSPOV  | SSPEN    | CKP SSPM<3:0> |           |         |          |        | 253                 |

| T0CON    | TMR0ON  | T08BIT | TOCS     | T0SE          | PSA       | Т       | 0PS<2:0> |        | 154                 |

| TRISA    | TRISA7  | TRISA6 | TRISA5   | TRISA4        | TRISA3    | TRISA2  | TRISA1   | TRISA0 | 151                 |

|          |         |        |          |               |           |         |          |        |                     |

TABLE 10-2: REGISTERS ASSOCIATED WITH PORTA

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTA.

#### TABLE 10-3: CONFIGURATION REGISTERS ASSOCIATED WITH PORTA

| Name                                          | Bit 7                                                                             | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|-----------------------------------------------|-----------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| CONFIG1H IESO FCMEN PRICLKEN PLLCFG FOSC<3:0> |                                                                                   |       |       |       |       | 345   |       |       |                     |

| Levend                                        | Levende unimplemented levetions, read or (o). Checked hits are not used for DODTA |       |       |       |       |       |       |       |                     |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTA.

#### 10.1.1 PORTA OUTPUT PRIORITY

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the higher priority. Table 10-4 lists the PORTA pin functions from the highest to the lowest priority.

Analog input functions, such as ADC and comparator, are not shown in the priority lists.

These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below.

| D I. M   |                     | Port Fun            | ction Priority by P | ort Pin              |                      |

|----------|---------------------|---------------------|---------------------|----------------------|----------------------|

| Port bit | PORTA               | PORTB               | PORTC               | PORTD <sup>(2)</sup> | PORTE <sup>(2)</sup> |

| 0        | RA0                 | CCP4 <sup>(1)</sup> | SOSCO               | SCL2                 | CCP3 <sup>(8)</sup>  |

|          |                     | RB0                 | P2B <sup>(6)</sup>  | SCK2                 | P3A <sup>(8)</sup>   |

|          |                     |                     | RC0                 | RD0                  | RE0                  |

| 1        | RA1                 | SCL2 <sup>(1)</sup> | SOSCI               | SDA2                 | P3B                  |

|          |                     | SCK2 <sup>(1)</sup> | CCP2 <sup>(3)</sup> | CCP4                 | RE1                  |

|          |                     | P1C <sup>(1)</sup>  | P2A <sup>(3)</sup>  | RD1                  |                      |

|          |                     | RB1                 | RC1                 |                      |                      |

| 2        | RA2                 | SDA2 <sup>(1)</sup> | CCP1                | P2B                  | CCP5                 |

|          |                     | P1B <sup>(1)</sup>  | P1A                 | RD2 <sup>(4)</sup>   | RE2                  |

|          |                     | RB2                 | CTPLS               |                      |                      |

|          |                     |                     | RC2                 |                      |                      |

| 3        | RA3                 | SDO2 <sup>(1)</sup> | SCL1                | P2C                  | MCLR                 |

|          |                     | CCP2 <sup>(6)</sup> | SCK1                | RD3                  | Vpp                  |

|          |                     | P2A <sup>(6)</sup>  | RC3                 |                      | RE3                  |

|          |                     | RB3                 |                     |                      |                      |

| 4        | SRQ                 | P1D <sup>(1)</sup>  | SDA1                | SDO2                 |                      |

|          | C1OUT               | RB4                 | RC4                 | P2D                  |                      |

|          | CCP5 <sup>(1)</sup> |                     |                     | RD4                  |                      |

|          | RA4                 |                     |                     |                      |                      |

#### TABLE 10-4: PORT PIN FUNCTION PRIORITY

Note 1: PIC18(L)F2XK22 devices.

2: PIC18(L)F4XK22 devices.

- **3:** Function default pin.

- **4:** Function default pin (28-pin devices).

- **5:** Function default pin (40/44-pin devices).

- **6:** Function alternate pin.

- 7: Function alternate pin (28-pin devices).

- 8: Function alternate pin (40/44-pin devices)

| <b>D</b> . (1)( | Port Function Priority by Port Pin |                        |                        |                      |                      |  |  |  |  |

|-----------------|------------------------------------|------------------------|------------------------|----------------------|----------------------|--|--|--|--|

| Port bit        | PORTA                              | PORTB                  | PORTC                  | PORTD <sup>(2)</sup> | PORTE <sup>(2)</sup> |  |  |  |  |

| 5               | SRNQ                               | CCP3 <sup>(3)</sup>    | SDO1                   | P1B                  |                      |  |  |  |  |

|                 | C2OUT                              | P3A <sup>(3)</sup>     | RC5                    | RD5                  |                      |  |  |  |  |

|                 | RA5                                | P2B <sup>(1)(4)</sup>  |                        |                      |                      |  |  |  |  |

|                 |                                    | RB5                    |                        |                      |                      |  |  |  |  |

| 6               | OSC2                               | PGC                    | TX1/CK1                | TX2/CK2              |                      |  |  |  |  |

|                 | CLKO                               | TX2/CK2 <sup>(1)</sup> | CCP3 <sup>(1)(7)</sup> | P1C                  |                      |  |  |  |  |

|                 | RA6                                | RB6                    | P3A <sup>(1)(7)</sup>  | RD6                  |                      |  |  |  |  |

|                 |                                    | ICDCK                  | RC6                    |                      |                      |  |  |  |  |

| 7               | RA7                                |                        |                        |                      |                      |  |  |  |  |

|                 | OSC1                               | PGD                    | RX1/DT1                | RX2/DT2              |                      |  |  |  |  |

|                 | RA7                                | RX2/DT2 <sup>(1)</sup> | P3B <sup>(1)</sup>     | P1D                  |                      |  |  |  |  |

|                 |                                    | RB7                    | RC7                    | RD7                  |                      |  |  |  |  |

|                 |                                    | ICDDT                  |                        |                      |                      |  |  |  |  |

#### TABLE 10-4: PORT PIN FUNCTION PRIORITY (CONTINUED)

Note 1: PIC18(L)F2XK22 devices.

2: PIC18(L)F4XK22 devices.

3: Function default pin.

4: Function default pin (28-pin devices).

5: Function default pin (40/44-pin devices).

6: Function alternate pin.

7: Function alternate pin (28-pin devices).

8: Function alternate pin (40/44-pin devices)

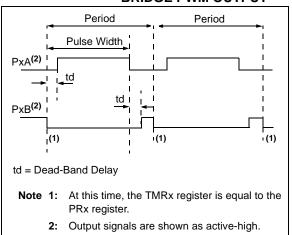

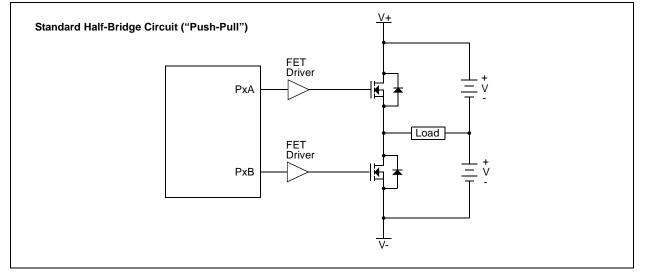

#### 14.4.5 PROGRAMMABLE DEAD-BAND DELAY MODE

In half-bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shootthrough current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable deadband delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 14-16 for illustration. The lower seven bits of the associated PWMxCON register (Register 14-6) sets the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

#### FIGURE 14-16: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

## FIGURE 14-17: EXAMPLE OF HALF-BRIDGE APPLICATIONS

PIC18(L)F2X/4XK22

# PIC18(L)F2X/4XK22

#### 16.4.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RXx signal, the RXx signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCONx register starts the auto-baud calibration sequence (Section 16.4.2 "Auto-baud Overflow"). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRGx begins counting up using the BRG counter clock as shown in Table 16-6. The fifth rising edge will occur on the RXx/ DTx pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGHx:SPBRGx register pair, the ABDEN bit is automatically cleared, and the RCxIF interrupt flag is set. A read operation on the RCREGx needs to be performed to clear the RCxIF interrupt. RCREGx content should be discarded. When calibrating for modes that do not use the SPBRGHx register the user can verify that the SPBRGx register did not overflow by checking for 00h in the SPBRGHx register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 16-6. During ABD, both the SPBRGHx and SPBRGx registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGHx and SPBRGx registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte <u>following</u> the Break character (see Section 16.4.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the autobaud counter starts counting at one. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract one from the SPBRGHx:SPBRGx register pair.

| TABLE 16-6: | BRG COUNTER CLOCK |

|-------------|-------------------|

|             | RATES             |

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

Note: During the ABD sequence, SPBRGx and SPBRGHx registers are both used as a 16-bit counter, independent of BRG16 setting.

| BRG Value   | XXXXh         | 0000h                  |                                                                                   | 001Ch                |

|-------------|---------------|------------------------|-----------------------------------------------------------------------------------|----------------------|

| RXx/DTx pin |               | Start                  | Edge #1 Edge #2 Edge #3 Edge #4     bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit | Edge #5     Stop bit |

| BRG Clock   |               |                        |                                                                                   | (                    |

|             | Set by User — | ı<br><del> </del>      |                                                                                   | Auto Cleared         |

| ABDEN bit   |               | ]                      | I                                                                                 |                      |

| RCIDL       |               | <u>.</u>               | 1                                                                                 |                      |

| RCxIF bit   |               | 1 <u> </u>             |                                                                                   |                      |

| (Interrupt) |               | 1                      |                                                                                   |                      |

| Read        |               | I<br>I                 | -                                                                                 |                      |

| RCREGx      |               | 1                      | 1                                                                                 |                      |

| SPBRGx      |               | 1<br>I                 | XXh                                                                               | X 1Ch                |

| SPBRGHx     |               | 1                      | XXh                                                                               | 00h                  |

|             |               | ence requires the EUS. | -<br>-                                                                            |                      |

## FIGURE 16-6: AUTOMATIC BAUD RATE CALIBRATION

### 17.1.5 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON2 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11 TAD periods as shown in Figure 17-3.

For correct conversion, the appropriate TAD specification must be met. See A/D conversion requirements in Table 27-22 for more information. Table 17-1 gives examples of appropriate ADC clock selections.

| Note: | Unless using the FRC, any changes in the |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|

|       | system clock frequency will change the   |  |  |  |  |  |  |  |  |

|       | ADC clock frequency, which may           |  |  |  |  |  |  |  |  |

|       | adversely affect the ADC result.         |  |  |  |  |  |  |  |  |

## 17.1.6 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital Conversion. The ADC interrupt enable is the ADIE bit in the PIE1 register and the interrupt priority is the ADIP bit in the IPR1 register. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADIF bit must be cleared by software.

**Note:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the Interrupt Service Routine.

| TABLE 17-1: | ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES |

|-------------|---------------------------------------------------------|

|-------------|---------------------------------------------------------|

| ADC Clock F                | Period (TAD) | Device Frequency (Fosc) |                         |                               |                               |  |  |

|----------------------------|--------------|-------------------------|-------------------------|-------------------------------|-------------------------------|--|--|

| ADC Clock Source ADCS<2:0> |              | 64 MHz 16 MHz           |                         | 4 MHz                         | 1 MHz                         |  |  |

| Fosc/2                     | 000          | 31.25 ns <sup>(2)</sup> | 125 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>         | 2.0 μs                        |  |  |

| Fosc/4                     | 100          | 62.5 ns <sup>(2)</sup>  | 250 ns <sup>(2)</sup>   | 1.0 μs                        | 4.0 μs <sup>(3)</sup>         |  |  |

| Fosc/8                     | 001          | 400 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 2.0 μs                        | 8.0 μs <b>(3)</b>             |  |  |

| Fosc/16                    | 101          | 250 ns <sup>(2)</sup>   | 1.0 μs                  | 4.0 μs <sup>(3)</sup>         | 16.0 μs <b><sup>(3)</sup></b> |  |  |

| Fosc/32                    | 010          | 500 ns <sup>(2)</sup>   | 2.0 μs                  | 8.0 μs <sup>(3)</sup>         | 32.0 μs <b><sup>(3)</sup></b> |  |  |

| Fosc/64                    | 110          | 1.0 μs                  | 4.0 μs <sup>(3)</sup>   | 16.0 μs <b><sup>(3)</sup></b> | 64.0 μs <b>(3)</b>            |  |  |

| FRC                        | x11          | 1-4 μs <sup>(1,4)</sup> | 1-4 μs <sup>(1,4)</sup> | 1-4 μs <sup>(1,4)</sup>       | 1-4 μs <sup>(1,4)</sup>       |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of  $1.7 \ \mu$ s.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock Fosc. However, the FRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

## 20.0 SR LATCH

The module consists of a single SR latch with multiple Set and Reset inputs as well as separate latch outputs. The SR latch module includes the following features:

- Programmable input selection

- SR latch output is available internally/externally

- Selectable Q and  $\overline{Q}$  output

- Firmware Set and Reset

The SR latch can be used in a variety of analog applications, including oscillator circuits, one-shot circuit, hysteretic controllers, and analog timing applications.

### 20.1 Latch Operation

The latch is a Set-Reset latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be set or reset by:

- Software control (SRPS and SRPR bits)

- Comparator C1 output (sync\_C1OUT)

- Comparator C2 output (sync\_C2OUT)

- SRI Pin

- Programmable clock (DIVSRCLK)

The SRPS and the SRPR bits of the SRCON0 register may be used to set or reset the SR latch, respectively. The latch is Reset-dominant. Therefore, if both Set and Reset inputs are high, the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

The output from Comparator C1 or C2 can be used as the Set or Reset inputs of the SR latch. The output of either Comparator can be synchronized to the Timer1 clock source. See Section 18.0 "Comparator Module" and Section 12.0 "Timer1/3/5 Module with Gate Control" for more information.

An external source on the SRI pin can be used as the Set or Reset inputs of the SR latch.

An internal clock source, DIVSRCLK, is available and it can periodically set or reset the SR latch. The SRCLK<2:0> bits in the SRCON0 register are used to select the clock source period. The SRSCKE and SRRCKE bits of the SRCON1 register enable the clock source to set or reset the SR latch, respectively.

## 20.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR latch outputs may be directly output to I/O pins at the same time. Control is determined by the state of bits SRQEN and SRNQEN in the SRCON0 register.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

## 20.3 DIVSRCLK Clock Generation

The DIVSRCLK clock signal is generated from the peripheral clock which is pre-scaled by a value determined by the SRCLK<2:0> bits. See Figure 20-2 and Table 20-1 for additional detail.

## 20.4 Effects of a Reset

Upon any device Reset, the SR latch is not initialized, and the SRQ and SRNQ outputs are unknown. The user's firmware is responsible to initialize the latch output before enabling it to the output pins.

## 24.5 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 Flash devices differs significantly from other PIC microcontroller devices.

The user program memory is divided into three or five blocks, depending on the device. One of these is a Boot Block of 0.5K or 2K bytes, depending on the device. The remainder of the memory is divided into individual blocks on binary boundaries.

Each of the blocks has three code protection bits associated with them. They are:

- Code-Protect bit (CPn)

- Write-Protect bit (WRTn)

- External Block Table Read bit (EBTRn)

Figure 24-2 shows the program memory organization for 8, 16 and 32-Kbyte devices and the specific code protection bit associated with each block. The actual locations of the bits are summarized in Table 24-5.

## FIGURE 24-2: CODE-PROTECTED PROGRAM MEMORY FOR PIC18(L)F2X/4XK22

|                                               | Block Code Protection                         |                                               |                                                |                                 |  |

|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|------------------------------------------------|---------------------------------|--|

| 8 Kbytes                                      | 16 Kbytes                                     | 32 Kbytes                                     | 64 Kbytes                                      | Controlled By:                  |  |

| (PIC18(L)FX3K22)                              | (PIC18(L)FX4K22)                              | (PIC18(L)FX5K22)                              | (PIC18(L)FX6K22)                               |                                 |  |

| Boot Block                                    | Boot Block                                    | Boot Block                                    | Boot Block                                     | CPB, WRTB, EBTRB                |  |

| (000h-1FFh)                                   | (000h-7FFh)                                   | (000h-7FFh)                                   | (000h-7FFh)                                    |                                 |  |

| Block 0                                       | Block 0                                       | Block 0                                       | Block 0                                        | CP0, WRT0, EBTR0                |  |

| (200h-FFFh)                                   | (800h-1FFFh)                                  | (800h-1FFFh)                                  | (800h-3FFFh)                                   |                                 |  |

| Block 1                                       | Block 1                                       | Block 1                                       | Block 1                                        | CP1, WRT1, EBTR1                |  |

| (1000h-1FFFh)                                 | (2000h-3FFFh)                                 | (2000h-3FFFh)                                 | (4000h-7FFFh)                                  |                                 |  |

|                                               |                                               | Block 2<br>(4000h-5FFFh)                      | Block 2<br>(8000h-BFFFh)                       | CP2, WRT2, EBTR2                |  |

|                                               |                                               | Block 3<br>(6000h-7FFFh)                      | Block 3<br>(C000h-FFFFh)                       | CP3, WRT3, EBTR3                |  |

| Unimplemented<br>Read '0's<br>(2000h-1FFFFFh) | Unimplemented<br>Read '0's<br>(4000h-1FFFFFh) | Unimplemented<br>Read '0's<br>(8000h-1FFFFFh) | Unimplemented<br>Read '0's<br>(10000h-1FFFFFh) | (Unimplemented<br>Memory Space) |  |

#### TABLE 24-5: CONFIGURATION REGISTERS ASSOCIATED WITH CODE PROTECTION

| File Name |          | Bit 7 | Bit 6 | Bit 5               | Bit 4 | Bit 3                | Bit 2                | Bit 1 | Bit 0 |

|-----------|----------|-------|-------|---------------------|-------|----------------------|----------------------|-------|-------|

| 300008h   | CONFIG5L |       | _     |                     | _     | CP3 <sup>(1)</sup>   | CP2 <sup>(1)</sup>   | CP1   | CP0   |

| 300009h   | CONFIG5H | CPD   | CPB   | _                   | _     | _                    | _                    |       | —     |

| 30000Ah   | CONFIG6L | _     | —     | —                   | _     | WRT3 <sup>(1)</sup>  | WRT2 <sup>(1)</sup>  | WRT1  | WRT0  |

| 30000Bh   | CONFIG6H | WRTD  | WRTB  | WRTC <sup>(2)</sup> | _     | _                    | —                    | _     | _     |

| 30000Ch   | CONFIG7L | —     | —     | _                   | —     | EBTR3 <sup>(1)</sup> | EBTR2 <sup>(1)</sup> | EBTR1 | EBTR0 |

| 30000Dh   | CONFIG7H |       | EBTRB | —                   | —     | —                    | —                    | _     | —     |

Legend: Shaded bits are unimplemented.

Note 1: Available on PIC18(L)FX5K22 and PIC18(L)FX6K22 devices only.

**2:** In user mode, this bit is read-only and cannot be self-programmed.

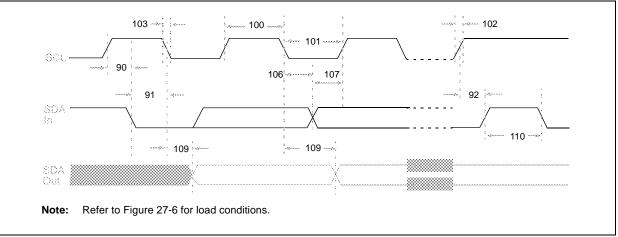

| Param.<br>No. | Symbol  | Characteristic  |              | Min  | Max | Units | Conditions                   |  |

|---------------|---------|-----------------|--------------|------|-----|-------|------------------------------|--|

| 90            | TSU:STA | Start Condition | 100 kHz mode | 4700 | _   | ns    | Only relevant for Repeated   |  |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       | Start condition              |  |

| 91 THD:ST     | THD:STA | Start Condition | 100 kHz mode | 4000 | _   | ns    | After this period, the first |  |

|               |         | Hold Time       | 400 kHz mode | 600  | _   |       | clock pulse is generated     |  |

| 92            | Tsu:sto | Stop Condition  | 100 kHz mode | 4700 | _   | ns    |                              |  |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       |                              |  |

| 93            | THD:STO | Stop Condition  | 100 kHz mode | 4000 | _   | ns    |                              |  |

|               |         | Hold Time       | 400 kHz mode | 600  |     | 1     |                              |  |

## TABLE 27-15: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

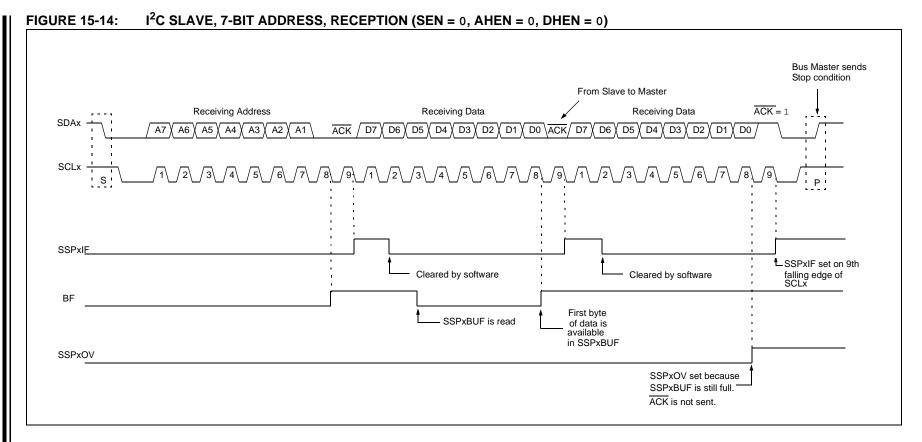

## FIGURE 27-18: I<sup>2</sup>C BUS DATA TIMING

## PIC18(L)F2X/4XK22

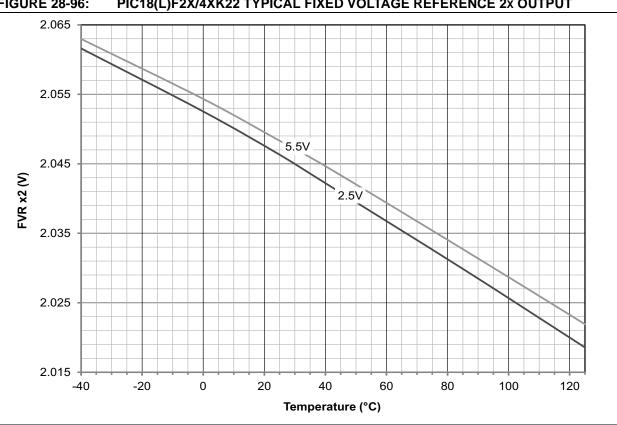

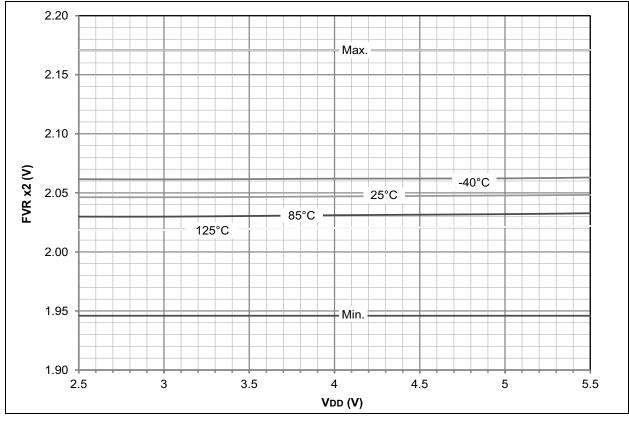

**FIGURE 28-97:** PIC18(L)F2X/4XK22 TYPICAL FIXED VOLTAGE REFERENCE 2x OUTPUT

FIGURE 28-96: PIC18(L)F2X/4XK22 TYPICAL FIXED VOLTAGE REFERENCE 2x OUTPUT

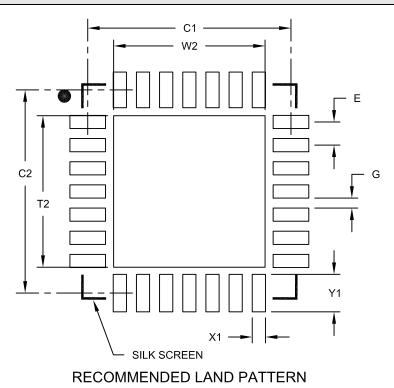

## 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| i                          | Units            |          |      |      |  |

|----------------------------|------------------|----------|------|------|--|

|                            | MILLIMETERS      |          |      |      |  |

| Dimension                  | Dimension Limits |          |      | MAX  |  |

| Contact Pitch              | E                | 0.65 BSC |      |      |  |

| Optional Center Pad Width  | W2               |          |      | 4.25 |  |

| Optional Center Pad Length | T2               |          |      | 4.25 |  |

| Contact Pad Spacing        | C1               |          | 5.70 |      |  |

| Contact Pad Spacing        | C2               |          | 5.70 |      |  |

| Contact Pad Width (X28)    | X1               |          |      | 0.37 |  |

| Contact Pad Length (X28)   | Y1               |          |      | 1.00 |  |

| Distance Between Pads      | G                | 0.20     |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A