Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 30x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8×8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf43k22-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

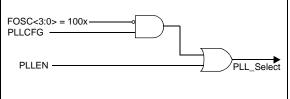

## FIGURE 2-3: PLL\_SELECT BLOCK DIAGRAM

### TABLE 2-1: PLL\_SELECT TRUTH TABLE

| Primary Clock MUX Source    | FOSC<3:0> | PLLCFG | PLLEN | PLL_Select |

|-----------------------------|-----------|--------|-------|------------|

| FOSC (any source)           | 0000-1111 | 0      | 0     | 0          |

| OSC1/OSC2 (external source) | 0000-0111 | 1      | х     | 1          |

|                             | 1010-1111 | 0      | 1     | 1          |

| INTOSC (internal source)    | 1000-1001 | x      | 0     | 0          |

|                             |           | x      | 1     | 1          |

#### 3.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by any one of the following:

- an interrupt

- a Reset

- a Watchdog Time-out

This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 3.2 "Run Modes", Section 3.3 "Sleep Mode" and Section 3.4 "Idle Modes").

#### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode or the Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

The instruction immediately following the SLEEP instruction is executed on all exits by interrupt from Idle or Sleep modes. Code execution then branches to the interrupt vector if the GIE/GIEH bit of the INTCON register is set, otherwise code execution continues without branching (see Section 9.0 "Interrupts").

A fixed delay of interval TCSD following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

#### 3.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see **Section 3.2 "Run Modes"** and **Section 3.3 "Sleep Mode**"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see **Section 24.3 "Watchdog Timer (WDT)**").

The WDT timer and postscaler are cleared by any one of the following:

- executing a **SLEEP** instruction

- executing a CLRWDT instruction

- the loss of the currently selected clock source when the Fail-Safe Clock Monitor is enabled

- modifying the IRCF bits in the OSCCON register when the internal oscillator block is the device clock source

#### 3.5.3 EXIT BY RESET

Exiting Sleep and Idle modes by Reset causes code execution to restart at address '0'. See **Section 4.0** "**Reset**" for more details.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator.

#### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC, INTOSC, and INTOSCIO modes). However, a fixed delay of interval TCsD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

### 4.2 Register Definitions: Reset Control

#### REGISTER 4-1: RCON: RESET CONTROL REGISTER

| R/W-0/0          | R/W-q/u               | U-0                                                  | R/W-1/q                  | R-1/q           | R-1/q                             | R/W-q/u                         | R/W-0/q       |

|------------------|-----------------------|------------------------------------------------------|--------------------------|-----------------|-----------------------------------|---------------------------------|---------------|

| IPEN             | SBOREN <sup>(1)</sup> | _                                                    | RI                       | TO              | PD                                | POR <sup>(2)</sup>              | BOR           |

| bit 7            | ·                     |                                                      |                          |                 | •                                 | ·                               | bit (         |

| Legend:          |                       |                                                      |                          |                 |                                   |                                 |               |

| R = Readable     | e bit                 | W = Writable                                         | bit                      | U = Unimplei    | mented bit, read                  | d as '0'                        |               |

| '1' = Bit is set |                       | '0' = Bit is cle                                     | eared                    | •               |                                   | R/Value at all c                | ther Resets   |

| x = Bit is unk   | nown                  | u = unchang                                          | jed                      | q = depends     | on condition                      |                                 |               |

| bit 7            | IPEN: Interru         | ot Priority Ena                                      | ble bit                  |                 |                                   |                                 |               |

|                  |                       | iority levels or                                     |                          |                 |                                   |                                 |               |

|                  |                       |                                                      |                          | IC16CXXX Co     | mpatibility mode                  | e)                              |               |

| bit 6            | SBOREN: BO            | OR Software E                                        | nable bit <sup>(1)</sup> |                 |                                   |                                 |               |

|                  | If BOREN<1:           |                                                      |                          |                 |                                   |                                 |               |

|                  | 1 = BOR is er         |                                                      |                          |                 |                                   |                                 |               |

|                  | 0 = BOR is di         |                                                      |                          |                 |                                   |                                 |               |

|                  |                       | <u>0&gt; = 00, 10                               </u> |                          |                 |                                   |                                 |               |

| bit 5            | Unimplemen            | ted: Read as                                         | '0'                      |                 |                                   |                                 |               |

| bit 4            | RI: RESET IN          | struction Flag                                       | bit                      |                 |                                   |                                 |               |

|                  | 0 = The RES           |                                                      | was executed             | · ·             | nware or Power<br>evice Reset (mu | -on Reset)<br>ust be set in fin | mware after a |

| bit 3            | TO: Watchdo           | g Time-out Fla                                       | ag bit                   |                 |                                   |                                 |               |

|                  |                       | ower-up, CLRW                                        |                          | or SLEEP instr  | ruction                           |                                 |               |

| bit 2            | PD: Power-de          | own Detection                                        | Flag bit                 |                 |                                   |                                 |               |

|                  |                       |                                                      | the CLRWDT in            |                 |                                   |                                 |               |

|                  |                       |                                                      | SLEEP instruc            | ction           |                                   |                                 |               |

| bit 1            |                       | on Reset Stat                                        |                          |                 |                                   |                                 |               |

|                  |                       | r-on Reset occ                                       |                          | cot in coffward | offer a Rower                     | on Reset occur                  | c)            |

| bit 0            | <b>BOR:</b> Brown-    |                                                      | -                        | Set in Soltware |                                   | on Reset occur                  | 5)            |

|                  |                       |                                                      |                          | (set by firmwa  | re only)                          |                                 |               |

|                  |                       |                                                      |                          |                 |                                   | or Brown-out R                  | eset occurs)  |

| Note 1: Wi       | nen CONFIG2L[         | 2:1] = 01, the                                       | n the SBOREN             | Reset state is  | s '1'; otherwise,                 | it is '0'.                      |               |

|                  | e actual Reset        |                                                      |                          | • • • •         | levice Reset. S                   |                                 | lowing this   |

register and Section 4.7 "Reset State of Registers" for additional information.

**3:** See Table 4-1.

**Note 1:** Brown-out Reset is indicated when BOR is '0' and POR is '1' (assuming that both POR and BOR were set to '1' by firmware immediately after POR).

2: It is recommended that the POR bit be set after a Power-on Reset has been detected so that subsequent Power-on Resets may be detected.

#### 5.4.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h-5Fh) in Bank 0 and the last 160 bytes of memory (60h-FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figures 5-5 through 5-7).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0', however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 5.7.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

#### 5.4.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM, which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

#### 5.4.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy the top portion of Bank 15 (F38h to FFFh). A list of these registers is given in Table 5-1 and Table 5-2.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of a peripheral feature are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

| TABLE   | 5-2: RI              | EGISTER  | FILE SUN                                                                                                             |        | OR PIC18      | (L)F2X/47     | (K22 DEV              | ICES (CO              | NIINUEL               | )                           |

|---------|----------------------|----------|----------------------------------------------------------------------------------------------------------------------|--------|---------------|---------------|-----------------------|-----------------------|-----------------------|-----------------------------|

| Address | Name                 | Bit 7    | Bit 6                                                                                                                | Bit 5  | Bit 4         | Bit 3         | Bit 2                 | Bit 1                 | Bit 0                 | <u>Value on</u><br>POR, BOR |

| FA2h    | IPR2                 | OSCFIP   | C1IP                                                                                                                 | C2IP   | EEIP          | BCL1IP        | HLVDIP                | TMR3IP                | CCP2IP                | 1111 1111                   |

| FA1h    | PIR2                 | OSCFIF   | C1IF                                                                                                                 | C2IF   | EEIF          | BCL1IF        | HLVDIF                | TMR3IF                | CCP2IF                | 0000 0000                   |

| FA0h    | PIE2                 | OSCFIE   | C1IE                                                                                                                 | C2IE   | EEIE          | BCL1IE        | HLVDIE                | TMR3IE                | CCP2IE                | 0000 0000                   |

| F9Fh    | IPR1                 | —        | ADIP                                                                                                                 | RC1IP  | TX1IP         | SSP1IP        | CCP1IP                | TMR2IP                | TMR1IP                | -111 1111                   |

| F9Eh    | PIR1                 | _        | ADIF                                                                                                                 | RC1IF  | TX1IF         | SSP1IF        | CCP1IF                | TMR2IF                | TMR1IF                | -000 0000                   |

| F9Dh    | PIE1                 | _        | ADIE                                                                                                                 | RC1IE  | TX1IE         | SSP1IE        | CCP1IE                | TMR2IE                | TMR1IE                | -000 0000                   |

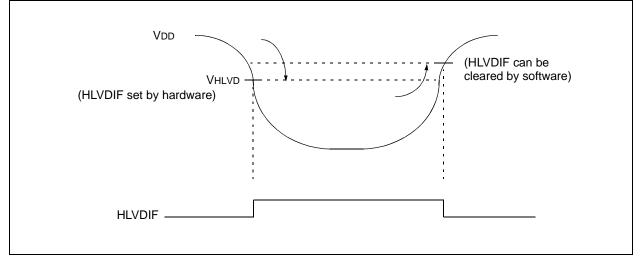

| F9Ch    | HLVDCON              | VDIRMAG  | BGVST                                                                                                                | IRVST  | HLVDEN        |               | HLVDL                 | <3:0>                 |                       | 0000 0000                   |

| F9Bh    | OSCTUNE              | INTSRC   | PLLEN                                                                                                                |        |               | TUN           | <5:0>                 |                       |                       | 00xx xxxx                   |

| F96h    | TRISE                | WPUE3    | _                                                                                                                    | _      | _             | _             | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 1111                        |

| F95h    | TRISD <sup>(1)</sup> | TRISD7   | TRISD6                                                                                                               | TRISD5 | TRISD4        | TRISD3        | TRISD2                | TRISD1                | TRISD0                | 1111 1111                   |

| F94h    | TRISC                | TRISC7   | TRISC6                                                                                                               | TRISC5 | TRISC4        | TRISC3        | TRISC2                | TRISC1                | TRISC0                | 1111 1111                   |

| F93h    | TRISB                | TRISB7   | TRISB6                                                                                                               | TRISB5 | TRISB4        | TRISB3        | TRISB2                | TRISB1                | TRISB0                | 1111 1111                   |

| F92h    | TRISA                | TRISA7   | TRISA6                                                                                                               | TRISA5 | TRISA4        | TRISA3        | TRISA2                | TRISA1                | TRISA0                | 1111 1111                   |

| F8Dh    | LATE <sup>(1)</sup>  | —        | —                                                                                                                    | _      | _             | —             | LATE2                 | LATE1                 | LATE0                 | xxx                         |

| F8Ch    | LATD <sup>(1)</sup>  | LATD7    | LATD6                                                                                                                | LATD5  | LATD4         | LATD3         | LATD2                 | LATD1                 | LATD0                 | xxxx xxxx                   |

| F8Bh    | LATC                 | LATC7    | LATC6                                                                                                                | LATC5  | LATC4         | LATC3         | LATC2                 | LATC1                 | LATC0                 | xxxx xxxx                   |

| F8Ah    | LATB                 | LATB7    | LATB6                                                                                                                | LATB5  | LATB4         | LATB3         | LATB2                 | LATB1                 | LATB0                 | xxxx xxxx                   |

| F89h    | LATA                 | LATA7    | LATA6                                                                                                                | LATA5  | LATA4         | LATA3         | LATA2                 | LATA1                 | LATA0                 | xxxx xxxx                   |

|         | PORTE <sup>(2)</sup> | _        | _                                                                                                                    | _      | _             | RE3           | _                     | _                     | _                     | x                           |

| F84h    | PORTE <sup>(1)</sup> | _        | _                                                                                                                    | _      | _             | RE3           | RE2                   | RE1                   | RE0                   | x000                        |

| F83h    | PORTD <sup>(1)</sup> | RD7      | RD6                                                                                                                  | RD5    | RD4           | RD3           | RD2                   | RD1                   | RD0                   | 0000 0000                   |

| F82h    | PORTC                | RC7      | RC6                                                                                                                  | RC5    | RC4           | RC3           | RC2                   | RC1                   | RC0                   | 0000 00xx                   |

| F81h    | PORTB                | RB7      | RB6                                                                                                                  | RB5    | RB4           | RB3           | RB2                   | RB1                   | RB0                   | xxx0 0000                   |

| F80h    | PORTA                | RA7      | RA6                                                                                                                  | RA5    | RA4           | RA3           | RA2                   | RA1                   | RA0                   | xx0x 0000                   |

| F7Fh    | IPR5                 | _        | _                                                                                                                    | _      | _             | _             | TMR6IP                | TMR5IP                | TMR4IP                | 111                         |

| F7Eh    | PIR5                 | _        | _                                                                                                                    | _      | _             | _             | TMR6IF                | TMR5IF                | TMR4IF                | 111                         |

| F7Dh    | PIE5                 | _        | _                                                                                                                    | _      | _             | _             | TMR6IE                | TMR5IE                | TMR4IE                | 000                         |

| F7Ch    | IPR4                 | _        | _                                                                                                                    | _      | _             | _             | CCP5IP                | CCP4IP                | CCP3IP                | 000                         |

| F7Bh    | PIR4                 | _        | _                                                                                                                    | _      | _             | _             | CCP5IF                | CCP4IF                | CCP3IF                | 000                         |

| F7Ah    | PIE4                 | _        | _                                                                                                                    | _      | _             | _             | CCP5IE                | CCP4IE                | CCP3IE                | 000                         |

| F79h    | CM1CON0              | C10N     | C1OUT                                                                                                                | C10E   | C1POL         | C1SP          | C1R                   | C1CH                  | 1<1:0>                | 0000 1000                   |

| F78h    | CM2CON0              | C2ON     | C2OUT                                                                                                                | C2OE   | C2POL         | C2SP          | C2R                   | C2CH                  | l<1:0>                | 0000 1000                   |

| F77h    | CM2CON1              | MC1OUT   | MC2OUT                                                                                                               | C1RSEL | C2RSEL        | C1HYS         | C2HYS                 | C1SYNC                | C2SYNC                | 0000 0000                   |

| F76h    | SPBRGH2              |          | 1                                                                                                                    | EUSAR  | T2 Baud Rate  | Generator, Hi |                       |                       |                       | 0000 0000                   |

| F75h    | SPBRG2               |          |                                                                                                                      |        | T2 Baud Rate  |               |                       |                       |                       | 0000 0000                   |

| F74h    | RCREG2               |          |                                                                                                                      |        | T2 Receive Re |               | ,                     |                       |                       | 0000 0000                   |

| F73h    | TXREG2               |          |                                                                                                                      |        | T2 Transmit R | 0             |                       |                       |                       | 0000 0000                   |

| F72h    | TXSTA2               | CSRC     | TX9                                                                                                                  | TXEN   | SYNC          | SENDB         | BRGH                  | TRMT                  | TX9D                  | 0000 0010                   |

| F71h    | RCSTA2               | SPEN     | RX9                                                                                                                  | SREN   | CREN          | ADDEN         | FERR                  | OERR                  | RX9D                  | 0000 000x                   |

| F70h    | BAUDCON2             | ABDOVF   | RCIDL                                                                                                                | DTRXP  | CKTXP         | BRG16         | _                     | WUE                   | ABDEN                 | 01x0 0-00                   |

| F6Fh    | SSP2BUF              |          | SSP2 Receive Buffer/Transmit Register                                                                                |        |               |               |                       |                       |                       |                             |

| F6Eh    | SSP2ADD              | SSP2 Add | SSP2 Address Register in I <sup>2</sup> C Slave Mode. SSP2 Baud Rate Reload Register in I <sup>2</sup> C Master Mode |        |               |               |                       |                       |                       |                             |

| F6Dh    | SSP2STAT             | SMP      | CKE                                                                                                                  | D/A    | P             | S             | R/W                   | UA                    | BF                    | 0000 0000                   |

| F6Ch    | SSP2CON1             | WCOL     | SSPOV                                                                                                                | SSPEN  | CKP           |               | SSPM                  |                       |                       | 0000 0000                   |

| F6Bh    | SSP2CON1             | GCEN     | ACKSTAT                                                                                                              | ACKDT  | ACKEN         | RCEN          | PEN                   | RSEN                  | SEN                   | 0000 0000                   |

| F6Ah    | SSP2CON2             | JULIN    | NONOTAI                                                                                                              | NONDT  | SSP1 MASK I   | -             |                       | NOLIN                 | ULIN                  | 1111 1111                   |

| F69h    | SSP2CON3             | ACKTIM   | PCIE                                                                                                                 | SCIE   | BOEN          | SDAHT         | SBCDE                 | AHEN                  | DHEN                  | 0000 0000                   |

| Legend: |                      |          |                                                                                                                      |        | = value deper |               |                       |                       | DILIN                 | 3000 0000                   |

| TABLE 5-2: | REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES (CONTINUED) |

|------------|-----------------------------------------------------------------|

|------------|-----------------------------------------------------------------|

$\label{eq:legend: Legend: Legend: a generative state of the state of$

Note 1: PIC18(L)F4XK22 devices only.

2: PIC18(L)F2XK22 devices only.

3: PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

| R/W-1           | R/W-1                                                                         | R/W-1                                        | R/W-1            | U-0              | R/W-1             | U-0            | R/W-1          |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------|----------------------------------------------|------------------|------------------|-------------------|----------------|----------------|--|--|--|--|

| RBPU            | INTEDG0                                                                       | INTEDG1                                      | INTEDG2          | —                | TMR0IP            | _              | RBIP           |  |  |  |  |

| bit 7           | •<br>•                                                                        |                                              |                  |                  |                   |                | bit            |  |  |  |  |

|                 |                                                                               |                                              |                  |                  |                   |                |                |  |  |  |  |

| Legend:         |                                                                               |                                              |                  |                  |                   |                |                |  |  |  |  |

| R = Readable    |                                                                               | W = Writable                                 |                  | -                | mented bit, read  |                |                |  |  |  |  |

| -n = Value at F | POR                                                                           | '1' = Bit is set                             |                  | '0' = Bit is cle | eared             | x = Bit is unk | nown           |  |  |  |  |

|                 |                                                                               |                                              |                  |                  |                   |                |                |  |  |  |  |

| bit 7           |                                                                               | TB Pull-up Ena                               |                  |                  |                   |                |                |  |  |  |  |

|                 |                                                                               | FB pull-ups are                              |                  | that the nin i   | s an input and th | e correspondi  | na WPLIB bit i |  |  |  |  |

|                 | set.                                                                          |                                              |                  |                  | s an input and t  | ie concoponali |                |  |  |  |  |

| bit 6           | INTEDG0: E>                                                                   | kternal Interrup                             | t 0 Edge Sele    | ct bit           |                   |                |                |  |  |  |  |

|                 |                                                                               | 1 = Interrupt on rising edge                 |                  |                  |                   |                |                |  |  |  |  |

|                 | -                                                                             | on falling edge                              |                  |                  |                   |                |                |  |  |  |  |

| bit 5           |                                                                               | NTEDG1: External Interrupt 1 Edge Select bit |                  |                  |                   |                |                |  |  |  |  |

|                 |                                                                               | on rising edge<br>on falling edge            |                  |                  |                   |                |                |  |  |  |  |

| bit 4           | •                                                                             | 0 0                                          |                  | ot hit           |                   |                |                |  |  |  |  |

| DIL 4           | INTEDG2: External Interrupt 2 Edge Select bit<br>1 = Interrupt on rising edge |                                              |                  |                  |                   |                |                |  |  |  |  |

|                 |                                                                               | on falling edge                              | )                |                  |                   |                |                |  |  |  |  |

| bit 3           | Unimplemen                                                                    | ted: Read as '                               | 0'               |                  |                   |                |                |  |  |  |  |

| bit 2           | TMROIP: TMI                                                                   | R0 Overflow In                               | terrupt Priority | / bit            |                   |                |                |  |  |  |  |

|                 | 1 = High priority                                                             |                                              |                  |                  |                   |                |                |  |  |  |  |

|                 | 0 = Low prior                                                                 | rity                                         |                  |                  |                   |                |                |  |  |  |  |

| bit 1           | Unimplemen                                                                    | ted: Read as '                               | 0'               |                  |                   |                |                |  |  |  |  |

| bit 0           | RBIP: RB Po                                                                   | rt Change Inte                               | rrupt Priority b | it               |                   |                |                |  |  |  |  |

|                 | 1 = High prio                                                                 | 2                                            |                  |                  |                   |                |                |  |  |  |  |

|                 | 0 = Low prior                                                                 | P1+1/                                        |                  |                  |                   |                |                |  |  |  |  |

#### REGISTER 9-2: INTCON2: INTERRUPT CONTROL 2 REGISTER

| Note: | Interrupt flag bits are set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs, regardless of the state of  |

|       | its corresponding enable bit or the global    |

|       | enable bit. User software should ensure       |

|       | the appropriate interrupt flag bits are clear |

|       | prior to enabling an interrupt. This feature  |

|       | allows for software polling.                  |

#### 10.2 PORTB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., disable the output driver). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

| EXAMPLE 10-2: | INITIALIZING PORTB |

|---------------|--------------------|

| EXAMPLE 10-2: | INITIALIZING PURIB |

| MOVLB | 0xF    | ; Set BSR for banked SFRs     |

|-------|--------|-------------------------------|

| CLRF  | PORTB  | ; Initialize PORTB by         |

|       |        | ; clearing output             |

|       |        | ; data latches                |

| CLRF  | LATB   | ; Alternate method            |

|       |        | ; to clear output             |

|       |        | ; data latches                |

| MOVLW | 0F0h   | ; Value for init              |

| MOVWF | ANSELB | ; Enable RB<3:0> for          |

|       |        | ; digital input pins          |

|       |        | ; (not required if config bit |

|       |        | ; PBADEN is clear)            |

| MOVLW | 0CFh   | ; Value used to               |

|       |        | ; initialize data             |

|       |        | ; direction                   |

| MOVWF | TRISB  | ; Set RB<3:0> as inputs       |

|       |        | ; RB<5:4> as outputs          |

|       |        | ; RB<7:6> as inputs           |

|       |        |                               |

#### 10.2.1 PORTB OUTPUT PRIORITY

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the higher priority. Table 10-4 lists the PORTB pin functions from the highest to the lowest priority.

Analog input functions, such as ADC, comparator and SR latch inputs, are not shown in the priority lists.

These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below.

### **10.3 Additional PORTB Pin Functions**

PORTB pins RB<7:4> have an interrupt-on-change option. All PORTB pins have a weak pull-up option.

#### 10.3.1 WEAK PULL-UPS

Each of the PORTB pins has an individually controlled weak internal pull-up. When set, each bit of the WPUB register enables the corresponding pin pull-up. When cleared, the RBPU bit of the INTCON2 register enables pull-ups on all pins which also have their corresponding WPUB bit set. When set, the RBPU bit disables all weak pull-ups. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

| Note: | On a Power-on Reset, RB<5:0> are configured as analog inputs by default and read as '0'; RB<7:6> are configured as digital inputs. |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | When the PBADEN Configuration bit is set to '1', RB<5:0> will alternatively be configured as digital inputs on POR.                |

|       |                                                                                                                                    |

#### 10.3.2 INTERRUPT-ON-CHANGE

Four of the PORTB pins (RB<7:4>) are individually configurable as interrupt-on-change pins. Control bits in the IOCB register enable (when set) or disable (when clear) the interrupt function for each pin.

When set, the RBIE bit of the INTCON register enables interrupts on all pins which also have their corresponding IOCB bit set. When clear, the RBIE bit disables all interrupt-on-changes.

Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt-on-change comparison).

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of PORTB. The 'mismatch' outputs of the last read are OR'd together to set the PORTB Change Interrupt flag bit (RBIF) in the INTCON register.

This interrupt can wake the device from the Sleep mode, or any of the Idle modes. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- Any read or write of PORTB to clear the mismatch condition (except when PORTB is the source or destination of a MOVFF instruction).

- b) Execute at least one instruction after reading or writing PORTB, then clear the flag bit, RBIF.

| Pin Name          | Function                 | TRIS<br>Setting | ANSEL setting | Pin<br>Type | Buffer<br>Type | Description                                              |

|-------------------|--------------------------|-----------------|---------------|-------------|----------------|----------------------------------------------------------|

| RC5/SDO1/AN17     | RC5                      | 0               | 0             | 0           | DIG            | LATC<5> data output; not affected by analog input.       |

|                   |                          | 1               | 0             | I           | ST             | PORTC<5> data input; disabled when analog input enabled. |

|                   | SDO1                     | 0               | 0             | 0           | DIG            | MSSP1 SPI data output.                                   |

|                   | AN17                     | 1               | 1             | I           | AN             | Analog input 17.                                         |

| RC6/P3A/CCP3/TX1/ | RC6                      | 0               | 0             | 0           | DIG            | LATC<6> data output; not affected by analog input.       |

| CK1/AN18          |                          | 1               | 0             | I           | ST             | PORTC<6> data input; disabled when analog input enabled. |

|                   | P3A <sup>(2), (3)</sup>  | 0               | 0             | 0           | CMOS           | Enhanced CCP3 PWM output 1.                              |

|                   | CCP3 <sup>(2), (3)</sup> | 0               | 0             | 0           | DIG            | Compare 3 output/PWM 3 output.                           |

|                   |                          | 1               | 0             | I           | ST             | Capture 3 input.                                         |

|                   | TX1                      | 1               | 0             | 0           | DIG            | EUSART asynchronous transmit data output.                |

|                   | CK1                      | 1               | 0             | 0           | DIG            | EUSART synchronous serial clock output.                  |

|                   |                          | 1               | 0             | Ι           | ST             | EUSART synchronous serial clock input.                   |

|                   | AN18                     | 1               | 1             | I           | AN             | Analog input 18.                                         |

| RC7/P3B/RX1/DT1/  | RC7                      | 0               | 0             | 0           | DIG            | LATC<7> data output; not affected by analog input.       |

| AN19              |                          | 1               | 0             | Ι           | ST             | PORTC<7> data input; disabled when analog input enabled. |

|                   | P3B                      | 0               | 0             | 0           | CMOS           | Enhanced CCP3 PWM output 2.                              |

|                   | RX1                      | 1               | 0             | I           | ST             | EUSART asynchronous receive data in.                     |

|                   | DT1                      | 1               | 0             | 0           | DIG            | EUSART synchronous serial data output.                   |

|                   |                          | 1               | 0             | I           | ST             | EUSART synchronous serial data input.                    |

|                   | AN19                     | 1               | 1             | I           | AN             | Analog input 19.                                         |

### TABLE 10-8: PORTC I/O SUMMARY (CONTINUED)

Legend:AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS =<br/>CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;  $I^2C$  = Schmitt Trigger input with  $I^2C$ .

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

3: Function on PORTD and PORTE for PIC18FXXK22 devices.

#### 15.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCLx pin is held low (see **Section 15.5.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then the SCLx pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCLx input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes Idle and waits for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCLx pin must be released by setting bit CKP.

An MSSPx interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 15.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDAx line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIRx register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

#### 15.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 15-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDAx and SCLx.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit set is received by the slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCLx, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

**Note 1:** If the master ACKs the clock will be stretched.

**2:** ACKSTAT is the only bit updated on the rising edge of SCLx (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

| Name     | Bit 7      | Bit 6          | Bit 5                    | Bit 4        | Bit 3       | Bit 2      | Bit 1                       | Bit 0                 | Register<br>on Page |

|----------|------------|----------------|--------------------------|--------------|-------------|------------|-----------------------------|-----------------------|---------------------|

| ANSELA   | _          | _              | ANSA5                    | —            | ANSA3       | ANSA2      | ANSA1                       | ANSA0                 | 149                 |

| ANSELB   |            | _              | ANSB5                    | ANSB4        | ANSB3       | ANSB2      | ANSB1 <sup>(1)</sup>        | ANSB0 <sup>(1)</sup>  | 150                 |

| ANSELC   | ANSC7      | ANSC6          | ANSC5                    | ANSC4        | ANSC3       | ANSC2      | _                           | _                     | 150                 |

| ANSELD   | ANSD7      | ANSD6          | ANSD5                    | ANSD4        | ANSD3       | ANSD2      | ANSD1 <sup>(2)</sup>        | ANSD0 <sup>(2)</sup>  | 150                 |

| INTCON   | GIE/GIEH   | PEIE/GIEL      | TMR0IE                   | INT0IE       | RBIE        | TMR0IF     | INT0IF                      | RBIF                  | 109                 |

| IPR1     | _          | ADIP           | RC1IP                    | TX1IP        | SSP1IP      | CCP1IP     | TMR2IP                      | TMR1IP                | 121                 |

| IPR2     | OSCFIP     | C1IP           | C2IP                     | EEIP         | BCL1IP      | HLVDIP     | TMR3IP                      | CCP2IP                | 122                 |

| IPR3     | SSP2IP     | BCL2IP         | RC2IP                    | TX2IP        | CTMUIP      | TMR5GIP    | TMR3GIP                     | TMR1GIP               | 123                 |

| PIE1     | _          | ADIE           | RC1IE                    | TX1IE        | SSP1IE      | CCP1IE     | TMR2IE                      | TMR1IE                | 117                 |

| PIE2     | OSCFIE     | C1IE           | C2IE                     | EEIE         | BCL1IE      | HLVDIE     | TMR3IE                      | CCP2IE                | 118                 |

| PIE3     | SSP2IE     | BCL2IE         | RC2IE                    | TX2IE        | CTMUIE      | TMR5GIE    | TMR3GIE                     | TMR1GIE               | 119                 |

| PIR1     | _          | ADIF           | RC1IF                    | TX1IF        | SSP1IF      | CCP1IF     | TMR2IF                      | TMR1IF                | 112                 |

| PIR2     | OSCFIF     | C1IF           | C2IF                     | EEIF         | BCL1IF      | HLVDIF     | TMR3IF                      | CCP2IF                | 113                 |

| PIR3     | SSP2IF     | BCL2IF         | RC2IF                    | TX2IF        | CTMUIF      | TMR5GIF    | TMR3GIF                     | TMR1GIF               | 114                 |

| PMD1     | MSSP2MD    | MSSP1MD        | _                        | CCP5MD       | CCP4MD      | CCP3MD     | CCP2MD                      | CCP1MD                | 53                  |

| SSP1ADD  | SSP1 Addre | ss Register in | I <sup>2</sup> C Slave n | node. SSP1   | Baud Rate   | Reload Reg | ister in I <sup>2</sup> C M | laster mode.          | 258                 |

| SSP1BUF  |            |                | SSP1 Re                  | eceive Buffe | er/Transmit | Register   |                             |                       | _                   |

| SSP1CON1 | WCOL       | SSPOV          | SSPEN                    | CKP          |             | SSPI       | M<3:0>                      |                       | 253                 |

| SSP1CON2 | GCEN       | ACKSTAT        | ACKDT                    | ACKEN        | RCEN        | PEN        | RSEN                        | SEN                   | 255                 |

| SSP1CON3 | ACKTIM     | PCIE           | SCIE                     | BOEN         | SDAHT       | SBCDE      | AHEN                        | DHEN                  | 256                 |

| SSP1MSK  |            |                | S                        | SP1 MASK     | Register bi | ts         |                             |                       | 257                 |

| SSP1STAT | SMP        | CKE            | D/A                      | Р            | S           | R/W        | UA                          | BF                    | 252                 |

| SSP2ADD  | SSP2 Addre | ss Register in | I <sup>2</sup> C Slave n | node. SSP2   | Baud Rate   | Reload Reg | ister in I <sup>2</sup> C M | laster mode.          | 258                 |

| SSP2BUF  |            |                | SSP2 Re                  | eceive Buffe | er/Transmit | Register   |                             |                       | _                   |

| SSP2CON1 | WCOL       | SSPOV          | SSPEN                    | CKP          |             | SSPI       | M<3:0>                      |                       | 253                 |

| SSP2CON2 | GCEN       | ACKSTAT        | ACKDT                    | ACKEN        | RCEN        | PEN        | RSEN                        | SEN                   | 255                 |

| SSP2CON3 | ACKTIM     | PCIE           | SCIE                     | BOEN         | SDAHT       | SBCDE      | AHEN                        | DHEN                  | 256                 |

| SSP2MSK  |            |                | S                        | SP1 MASK     | Register bi |            |                             |                       | 257                 |

| SSP2STAT | SMP        | CKE            | D/A                      | Р            | S           | R/W        | UA                          | BF                    | 252                 |

| TRISB    | TRISB7     | TRISB6         | TRISB5                   | TRISB4       | TRISB3      | TRISB2     | TRISB1 <sup>(1)</sup>       | TRISB0 <sup>(1)</sup> | 151                 |

| TRISC    | TRISC7     | TRISC6         | TRISC5                   | TRISC4       | TRISC3      | TRISC2     | TRISC1                      | TRISC0                | 151                 |

| TRISD    | TRISD7     | TRISD6         | TRISD5                   | TRISD4       | TRISD3      | TRISD2     | TRISD1 <sup>(2)</sup>       | TRISD0 <sup>(2)</sup> | 151                 |

### TABLE 15-2: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

**Legend:** Shaded bits are not used by the MSSPx in  $I^2C$  mode.

Note 1: PIC18(L)F2XK22 devices.

2: PIC18(L)F4XK22 devices.

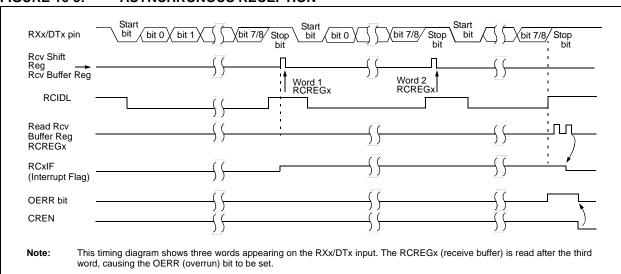

#### FIGURE 16-5: ASYNCHRONOUS RECEPTION

#### TABLE 16-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name                  | Bit 7    | Bit 6     | Bit 5   | Bit 4     | Bit 3       | Bit 2     | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------------|----------|-----------|---------|-----------|-------------|-----------|---------|---------|---------------------|

| BAUDCON1              | ABDOVF   | RCIDL     | DTRXP   | CKTXP     | BRG16       | _         | WUE     | ABDEN   | 271                 |

| BAUDCON2              | ABDOVF   | RCIDL     | DTRXP   | CKTXP     | BRG16       | _         | WUE     | ABDEN   | 271                 |

| INTCON                | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE    | RBIE        | TMR0IF    | INT0IF  | RBIF    | 109                 |

| IPR1                  | —        | ADIP      | RC1IP   | TX1IP     | SSP1IP      | CCP1IP    | TMR2IP  | TMR1IP  | 121                 |

| IPR3                  | SSP2IP   | BCL2IP    | RC2IP   | TX2IP     | CTMUIP      | TMR5GIP   | TMR3GIP | TMR1GIP | 123                 |

| PIE1                  | —        | ADIE      | RC1IE   | TX1IE     | SSP1IE      | CCP1IE    | TMR2IE  | TMR1IE  | 117                 |

| PIE3                  | SSP2IE   | BCL2IE    | RC2IE   | TX2IE     | CTMUIE      | TMR5GIE   | TMR3GIE | TMR1GIE | 119                 |

| PIR1                  | —        | ADIF      | RC1IF   | TX1IF     | SSP1IF      | CCP1IF    | TMR2IF  | TMR1IF  | 112                 |

| PIR3                  | SSP2IF   | BCL2IF    | RC2IF   | TX2IF     | CTMUIF      | TMR5GIF   | TMR3GIF | TMR1GIF | 114                 |

| PMD0                  | UART2MD  | UART1MD   | TMR6MD  | TMR5MD    | TMR4MD      | TMR3MD    | TMR2MD  | TMR1MD  | 52                  |

| RCREG1                |          |           | EU      | SART1 Re  | ceive Regis | ter       |         |         | —                   |

| RCSTA1                | SPEN     | RX9       | SREN    | CREN      | ADDEN       | FERR      | OERR    | RX9D    | 270                 |

| RCREG2                |          |           | EU      | SART2 Re  | ceive Regis | ter       |         |         | —                   |

| RCSTA2                | SPEN     | RX9       | SREN    | CREN      | ADDEN       | FERR      | OERR    | RX9D    | 270                 |

| SPBRG1                |          |           | EUSART1 | Baud Rate | Generator,  | Low Byte  |         |         | —                   |

| SPBRGH1               |          |           | EUSART1 | Baud Rate | Generator,  | High Byte |         |         | —                   |

| SPBRG2                |          |           | EUSART2 | Baud Rate | Generator,  | Low Byte  |         |         | —                   |

| SPBRGH2               |          |           | EUSART2 | Baud Rate | Generator,  | High Byte |         |         | —                   |

| TRISB <sup>(2)</sup>  | TRISB7   | TRISB6    | TRISB5  | TRISB4    | TRISB3      | TRISB2    | TRISB1  | TRISB0  | 151                 |

| TRISC                 | TRISC7   | TRISC6    | TRISC5  | TRISC4    | TRISC3      | TRISC2    | TRISC1  | TRISC0  | 151                 |

| TRISD <sup>(1)</sup>  | TRISD7   | TRISD6    | TRISD5  | TRISD4    | TRISD3      | TRISD2    | TRISD1  | TRISD0  | 151                 |

| ANSELC                | ANSC7    | ANSC6     | ANSC5   | ANSC4     | ANSC3       | ANSC2     | _       | —       | 150                 |

| ANSELD <sup>(1)</sup> | ANSD7    | ANSD6     | ANSD5   | ANSD4     | ANSD3       | ANSD2     | ANSD1   | ANSD0   | 150                 |

| TXSTA1                | CSRC     | TX9       | TXEN    | SYNC      | SENDB       | BRGH      | TRMT    | TX9D    | 269                 |

| TXSTA2                | CSRC     | TX9       | TXEN    | SYNC      | SENDB       | BRGH      | TRMT    | TX9D    | 269                 |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for asynchronous reception.

1: PIC18(L)F4XK22 devices.

2: PIC18(L)F2XK22 devices.

Note

| R/W-0         | R/W-0                     | R/W-0                                                     | R/W-0             | R/W-0           | R-0               | R-0                                | R-0     |

|---------------|---------------------------|-----------------------------------------------------------|-------------------|-----------------|-------------------|------------------------------------|---------|

| SPEN          | RX9                       | SREN                                                      | CREN              | ADDEN           | FERR              | OERR                               | RX9D    |

| bit 7         |                           |                                                           |                   |                 |                   |                                    | bit     |

| Legend:       |                           |                                                           |                   |                 |                   |                                    |         |

| R = Readable  | e bit                     | W = Writable                                              | e bit             | U = Unimple     | emented bit, rea  | d as '0'                           |         |

| -n = Value at | POR                       | '1' = Bit is se                                           | t                 | ʻ0' = Bit is cl | eared             | x = Bit is unkr                    | nown    |

| bit 7         |                           | al Port Enable b                                          |                   |                 |                   |                                    |         |

|               |                           | port enabled (co<br>port disabled (he                     |                   | DTx and TXx/    | CKx pins as ser   | ial port pins)                     |         |

| bit 6         | <b>RX9:</b> 9-bit F       | Receive Enable                                            | bit               |                 |                   |                                    |         |

|               |                           | <ul><li>9-bit reception</li><li>8-bit reception</li></ul> |                   |                 |                   |                                    |         |

| bit 5         | SREN: Sing                | gle Receive Ena                                           | ble bit           |                 |                   |                                    |         |

|               | Asynchrono                | ous mode:                                                 |                   |                 |                   |                                    |         |

|               | Don't care                |                                                           |                   |                 |                   |                                    |         |

|               |                           | <u>is mode – Maste</u>                                    |                   |                 |                   |                                    |         |

|               |                           | s single receive<br>es single receive                     |                   |                 |                   |                                    |         |

|               |                           | leared after rece                                         |                   | ete.            |                   |                                    |         |

|               | <u>Synchronou</u>         | <u>ıs mode – Slave</u>                                    | <u>.</u>          |                 |                   |                                    |         |

|               | Don't care                |                                                           |                   |                 |                   |                                    |         |

| bit 4         | CREN: Con                 | tinuous Receive                                           | e Enable bit      |                 |                   |                                    |         |

|               | <u>Asynchronc</u>         |                                                           |                   |                 |                   |                                    |         |

|               | 1 = Enable                |                                                           |                   |                 |                   |                                    |         |

|               | 0 = Disable<br>Synchronou |                                                           |                   |                 |                   |                                    |         |

|               |                           |                                                           | ceive until enal  | hle hit CREN    | is cleared (CRF   | N overrides SR                     | EN)     |

|               |                           | es continuous re                                          |                   |                 |                   |                                    |         |

| bit 3         | ADDEN: Ad                 | dress Detect E                                            | nable bit         |                 |                   |                                    |         |

|               | Asynchronc                | ous mode 9-bit (                                          | <u>RX9 = 1)</u> : |                 |                   |                                    |         |

|               | 0 = Disable               |                                                           | ction, all bytes  |                 |                   | ouffer when RSF<br>n be used as pa |         |

|               | Don't care                |                                                           |                   |                 |                   |                                    |         |

| bit 2         | FERR: Frar                | ning Error bit                                            |                   |                 |                   |                                    |         |

|               | 1 = Framin<br>0 = No fran |                                                           | updated by rea    | ading RCREG     | x register and re | eceive next valio                  | d byte) |

| bit 1         | OERR: Ove                 | errun Error bit                                           |                   |                 |                   |                                    |         |

|               | 1 = Overru<br>0 = No ove  | n error (can be o<br>rrun error                           | cleared by clea   | aring bit CREN  | 1)                |                                    |         |

| bit 0         | RX9D: Nint                | h bit of Receive                                          | d Data            |                 |                   |                                    |         |

|               |                           |                                                           | abata             |                 |                   |                                    |         |

### REGISTER 16-2: RCSTAX: RECEIVE STATUS AND CONTROL REGISTER

### 17.2 ADC Operation

#### 17.2.1 STARTING A CONVERSION

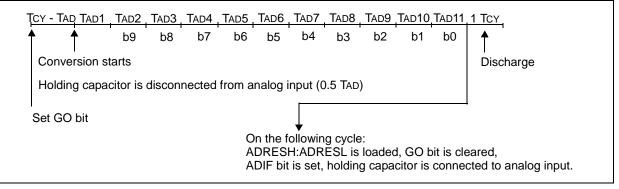

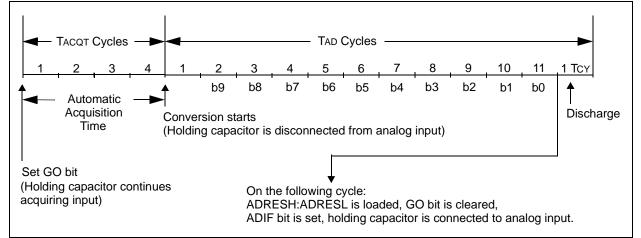

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will, depending on the ACQT bits of the ADCON2 register, either immediately start the Analog-to-Digital conversion or start an acquisition delay followed by the Analog-to-Digital conversion. Figure 17-3 shows the operation of the A/D converter after the GO bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into SLEEP mode before the conversion begins.

Figure 17-4 shows the operation of the A/D converter after the GO bit has been set and the ACQT<2:0> bits are set to '010' which selects a 4 TAD acquisition time before the conversion starts.

| Note: | The GO/DONE bit should not be set in the |    |                 |      |  |  |  |  |

|-------|------------------------------------------|----|-----------------|------|--|--|--|--|

|       | same instruction that turns on the ADC.  |    |                 |      |  |  |  |  |

|       | Refer                                    | to | Section 17.2.10 | "A/D |  |  |  |  |

|       | Conversion Procedure".                   |    |                 |      |  |  |  |  |

#### FIGURE 17-3: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

#### FIGURE 17-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

| U-0           | U-0                                                                                                                                                                                       | U-0                                                                                                                                                                                                                | R/P-1                                                                                                     | R/P-1                                   | R/P-1             | R/P-1            | R/P-1                 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------|------------------|-----------------------|

| _             | _                                                                                                                                                                                         | _                                                                                                                                                                                                                  | BORV                                                                                                      | ′<1:0> <sup>(1)</sup>                   | BOREN             | <1:0> <b>(2)</b> | PWRTEN <sup>(2)</sup> |

| bit 7         |                                                                                                                                                                                           |                                                                                                                                                                                                                    |                                                                                                           |                                         |                   |                  | bit                   |

|               |                                                                                                                                                                                           |                                                                                                                                                                                                                    |                                                                                                           |                                         |                   |                  |                       |