Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 30x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

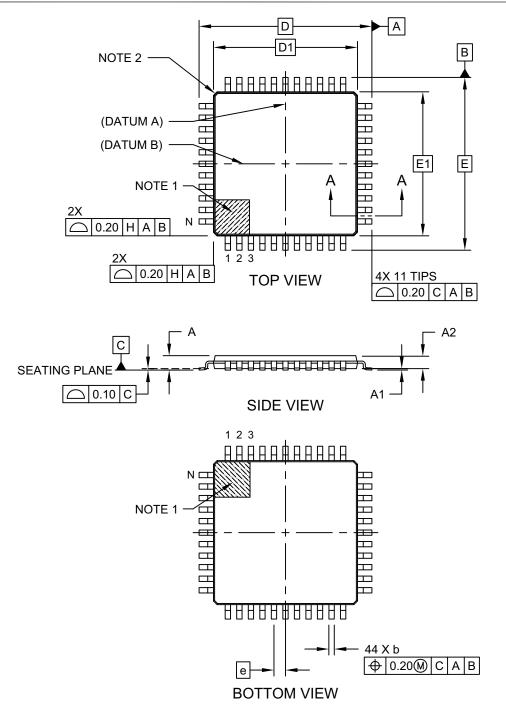

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf43k22-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2 Oscillator Control

The OSCCON, OSCCON2 and OSCTUNE registers (Register 2-1 to Register 2-3) control several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

- Main System Clock Selection (SCS)

- Primary Oscillator Circuit Shutdown (PRISD)

- Secondary Oscillator Enable (SOSCGO)

- Primary Clock Frequency 4x multiplier (PLLEN)

- Internal Frequency selection bits (IRCF, INTSRC)

- Clock Status bits (OSTS, HFIOFS, MFIOFS, LFIOFS. SOSCRUN, PLLRDY)

- Power management selection (IDLEN)

## 2.2.1 MAIN SYSTEM CLOCK SELECTION

The System Clock Select bits, SCS<1:0>, select the main clock source. The available clock sources are

- Primary clock defined by the FOSC<3:0> bits of CONFIG1H. The primary clock can be the primary oscillator, an external clock, or the internal oscillator block.

- Secondary clock (secondary oscillator)

- Internal oscillator block (HFINTOSC, MFINTOSC and LFINTOSC).

The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared to select the primary clock on all forms of Reset.

### 2.2.2 INTERNAL FREQUENCY SELECTION

The Internal Oscillator Frequency Select bits (IRCF<2:0>) select the frequency output of the internal oscillator block. The choices are the LFINTOSC source (31.25 kHz), the MFINTOSC source (31.25 kHz, 250 kHz or 500 kHz) and the HFINTOSC source (16 MHz) or one of the frequencies derived from the HFINTOSC postscaler (31.25 kHz to 8 MHz). If the internal oscillator block is supplying the main clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the output frequency of the internal oscillator is set to the default frequency of 1 MHz.

## 2.2.3 LOW FREQUENCY SELECTION

When a nominal output frequency of 31.25 kHz is selected (IRCF<2:0> = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit of the OSCTUNE register and MFIOSEL bit of the OSCCON2 register. See Figure 2-2 and Register 2-1 for specific 31.25 kHz selection. This option allows users to select a 31.25 kHz clock (MFINTOSC or HFINTOSC) that can be tuned using the TUN<5:0> bits in OSCTUNE register, while maintaining power savings with a very low clock speed. LFINTOSC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor, regardless of the setting of INTSRC and MFIOSEL bits

This option allows users to select the tunable and more precise HFINTOSC as a clock source, while maintaining power savings with a very low clock speed.

## 2.2.4 POWER MANAGEMENT

The IDLEN bit of the OSCCON register determines whether the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

## 2.11.3 CLOCK SWITCH TIMING

When switching between one oscillator and another, the new oscillator may not be operating which saves power (see Figure 2-9). If this is the case, there is a delay after the SCS<1:0> bits of the OSCCON register are modified before the frequency change takes place. The OSTS and IOFS bits of the OSCCON register will reflect the current active status of the external and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- 1. SCS<1:0> bits of the OSCCON register are modified.

- 2. The old clock continues to operate until the new clock is ready.

- 3. Clock switch circuitry waits for two consecutive rising edges of the old clock after the new clock ready signal goes true.

- 4. The system clock is held low starting at the next falling edge of the old clock.

- 5. Clock switch circuitry waits for an additional two rising edges of the new clock.

- 6. On the next falling edge of the new clock the low hold on the system clock is released and new clock is switched in as the system clock.

- 7. Clock switch is complete.

See Figure 2-1 for more details.

If the HFINTOSC is the source of both the old and new frequency, there is no start-up delay before the new frequency is active. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in **Section 27.0 "Electrical Specifications**", under AC Specifications (Oscillator Module).

## 2.12 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device.

This mode allows the application to wake-up from Sleep, perform a few instructions using the HFINTOSC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

Note: Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCCON register to remain clear.

When the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) is enabled (see **Section 2.5.1 "Oscillator Start-up Timer (OST)**"). The OST will suspend program execution until 1024 oscillations are counted. Two-Speed Start-up mode minimizes the delay in code execution by operating from the internal oscillator as the OST is counting. When the OST count reaches 1024 and the OSTS bit of the OSCCON register is set, program execution switches to the external oscillator.

### 2.12.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is enabled when all of the following settings are configured as noted:

- Two-Speed Start-up mode is enabled when the IESO of the CONFIG1H Configuration register is set.

- SCS<1:0> (of the OSCCON register) = 00.

- FOSC<2:0> bits of the CONFIG1H Configuration register are configured for LP, XT or HS mode.

Two-Speed Start-up mode becomes active after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

# PIC18(L)F2X/4XK22

| Address | Name                  | Bit 7                                     | Bit 6                                                                      | Bit 5        | Bit 4            | Bit 3                   | Bit 2      | Bit 1    | Bit 0     | <u>Value on</u><br>POR, BOR |

|---------|-----------------------|-------------------------------------------|----------------------------------------------------------------------------|--------------|------------------|-------------------------|------------|----------|-----------|-----------------------------|

| F68h    | CCPR2H                | Capture/Compare/PWM Register 2, High Byte |                                                                            |              |                  |                         |            |          |           |                             |

| F67h    | CCPR2L                |                                           |                                                                            | Capture/C    | ompare/PWM       | Register 2, Lo          | w Byte     |          |           | xxxx xxxx                   |

| F66h    | CCP2CON               | P2M<                                      | <1:0>                                                                      | DC2E         | 3<1:0>           |                         | CCP2N      | 1<3:0>   |           | 0000 0000                   |

| F65h    | PWM2CON               | P2RSEN                                    |                                                                            |              |                  | P2DC<6:0>               |            |          |           | 0000 0000                   |

| F64h    | ECCP2AS               | CCP2ASE                                   |                                                                            | CCP2AS<2:0   | >                | PSS2A                   | AC<1:0>    | PSS2B    | 0000 0000 |                             |

| F63h    | PSTR2CON              | I                                         | —                                                                          | —            | STR2SYNC         | STR2D                   | STR2C      | STR2B    | STR2A     | 0 0001                      |

| F62h    | IOCB                  | IOCB7                                     | IOCB6                                                                      | IOCB5        | IOCB4            | _                       | -          | —        | _         | 1111                        |

| F61h    | WPUB                  | WPUB7                                     | WPUB6                                                                      | WPUB5        | WPUB4            | WPUB3                   | WPUB2      | WPUB1    | WPUB0     | 1111 1111                   |

| Feah    | SLRCON <sup>(2)</sup> |                                           | _                                                                          | -            | _                | —                       | SLRC       | SLRB     | SLRA      | 111                         |

| F60h    | SLRCON <sup>(1)</sup> | I                                         | —                                                                          | —            | SLRE             | SLRD                    | SLRC       | SLRB     | SLRA      | 1 1111                      |

| F5Fh    | CCPR3H                |                                           |                                                                            | Capture/     | Compare/PWN      | /I Register 3, H        | ligh Byte  |          |           | xxxx xxxx                   |

| F5Eh    | CCPR3L                |                                           |                                                                            | Capture/     | Compare/PWN      | /I Register 3, L        | ow Byte    |          |           | xxxx xxxx                   |

| F5Dh    | CCP3CON               | P3M<                                      | <1:0>                                                                      | DC3E         | 3<1:0>           |                         | CCP3N      | <3:0>    |           | 0000 0000                   |

| F5Ch    | PWM3CON               | P3RSEN                                    |                                                                            |              |                  | P3DC<6:0>               |            |          |           | 0000 0000                   |

| F5Bh    | ECCP3AS               | <b>CCP3ASE</b>                            |                                                                            | CCP3AS<2:0   | >                | PSS3A                   | AC<1:0>    | PSS3B    | D<1:0>    | 0000 0000                   |

| F5Ah    | PSTR3CON              | _                                         | _                                                                          | _            | STR3SYNC         | STR3D                   | STR3C      | STR3B    | STR3A     | 0 0001                      |

| F59h    | CCPR4H                |                                           |                                                                            | Capture/     | Compare/PWI      | M Register 4, H         | ligh Byte  |          |           | xxxx xxxx                   |

| F58h    | CCPR4L                |                                           |                                                                            | Capture/     | Compare/PWI      | VI Register 4, L        | _ow Byte   |          |           | xxxx xxxx                   |

| F57h    | CCP4CON               |                                           | _                                                                          | DC4E         | 3<1:0>           |                         | CCP4N      | 1<3:0>   |           | 00 0000                     |

| F56h    | CCPR5H                |                                           | •                                                                          | Capture/     | Compare/PWI      | M Register 5, H         | ligh Byte  |          |           | xxxx xxxx                   |

| F55h    | CCPR5L                |                                           |                                                                            | Capture/     | Compare/PWI      | VI Register 5, L        | _ow Byte   |          |           | xxxx xxxx                   |

| F54h    | CCP5CON               |                                           | —                                                                          | DC5E         | 3<1:0>           |                         | CCP5N      | 1<3:0>   |           | 00 0000                     |

| F53h    | TMR4                  | Timer4 Register                           |                                                                            |              |                  |                         |            |          |           | 0000 0000                   |

| F52h    | PR4                   |                                           | Timer4 Period Register                                                     |              |                  |                         |            |          |           | 1111 1111                   |

| F51h    | T4CON                 |                                           |                                                                            | T4OUT        | PS<3:0>          |                         | TMR4ON     | T4CKP    | S<1:0>    | -000 0000                   |

| F50h    | TMR5H                 |                                           | Holding Register for the Most Significant Byte of the 16-bit TMR5 Register |              |                  |                         |            |          |           | 0000 0000                   |

| F4Fh    | TMR5L                 |                                           |                                                                            | Least Signif | icant Byte of th | ne 16-bit TMR5          | 5 Register |          |           | 0000 0000                   |

| F4Eh    | T5CON                 | TMR5C                                     | S<1:0>                                                                     | T5CKF        | PS<1:0>          | T5SOSCEN                | T5SYNC     | T5RD16   | TMR5ON    | 0000 0000                   |

| F4Dh    | T5GCON                | TMR5GE                                    | T5GPOL                                                                     | T5GTM        | T5GSPM           | T <u>5GGO</u> /<br>DONE | T5GVAL     | T5GSS    | S<1:0>    | 0000 0x00                   |

| F4Ch    | TMR6                  |                                           | •                                                                          | •            | Timer6 Regist    | er                      | •          | •        |           | 0000 0000                   |

| F4Bh    | PR6                   |                                           |                                                                            |              | Timer6 Period    | Register                |            |          |           | 1111 1111                   |

| F4Ah    | T6CON                 |                                           |                                                                            | T6OUT        | PS<3:0>          |                         | TMR6ON     | T6CKP    | S<1:0>    | -000 0000                   |

| F49h    | CCPTMRS0              | C3TSE                                     | L<1:0>                                                                     | _            | C2TSE            | L<1:0>                  | _          | C1TSE    | L<1:0>    | 00-0 0-00                   |

| F48h    | CCPTMRS1              |                                           | _                                                                          | _            | _                | C5TSE                   | EL<1:0>    | C4TSE    | L<1:0>    | 0000                        |

| F47h    | SRCON0                | SRLEN                                     |                                                                            | SRCLK<2:0>   | •                | SRQEN                   | SRNQEN     | SRPS     | SRPR      | 0000 0000                   |

| F46h    | SRCON1                | SRSPE                                     | SRSCKE                                                                     | SRSC2E       | SRSC1E           | SRRPE                   | SRRCKE     | SRRC2E   | SRRC1E    | 0000 0000                   |

| F45h    | CTMUCONH              | CTMUEN                                    | _                                                                          | CTMUSIDL     | TGEN             | EDGEN                   | EDGSEQEN   | IDISSEN  | CTTRIG    | 0000 0000                   |

| F44h    | CTMUCONL              | EDG2POL                                   | EDG2S                                                                      | EL<1:0>      | EDG1POL          | EDG1S                   | EL<1:0>    | EDG2STAT | EDG1STAT  | 0000 0000                   |

| F43h    | CTMUICON              |                                           |                                                                            | ITRI         | M<5:0>           |                         |            | IRNG     | <1:0>     | 0000 0000                   |

| F42h    | VREFCON0              | FVREN                                     | FVRST                                                                      | FVRS         | S<1:0>           | _                       | _          | —        | _         | 0001                        |

| F41h    | VREFCON1              | DACEN                                     | DACLPS                                                                     | DACOE        | _                | DACPS                   | SS<1:0>    | —        | DACNSS    | 000- 00-0                   |

| F40h    | VREFCON2              | _                                         | —                                                                          | —            |                  |                         | DACR<4:0>  |          |           | 0 0000                      |

| F3Fh    | PMD0                  | UART2MD                                   | UART1MD                                                                    | TMR6MD       | TMR5MD           | TMR4MD                  | TMR3MD     | TMR2MD   | TMR1MD    | 0000 0000                   |

| F3Eh    | PMD1                  | MSSP2MD                                   | MSSP1MD                                                                    | _            | CCP5MD           | CCP4MD                  | CCP3MD     | CCP2MD   | CCP1MD    | 00-0 0000                   |

| F3Dh    | PMD2                  | _                                         | _                                                                          | _            | _                | CTMUMD                  | CMP2MD     | CMP1MD   | ADCMD     | 0000                        |

| F3Ch    | ANSELE <sup>(1)</sup> | _                                         | _                                                                          | _            | _                | _                       | ANSE2      | ANSE1    | ANSE0     | 111                         |

| F3Bh    | ANSELD <sup>(1)</sup> | ANSD7                                     | ANSD6                                                                      | ANSD5        | ANSD4            | ANSD3                   | ANSD2      | ANSD1    | ANSD0     | 1111 1111                   |

### TABLE 5-2: REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES (CONTINUED)

$\label{eq:Legend: Legend: Legend: Legend: u = unchanged, --= unimplemented, q = value depends on condition$

Note 1: PIC18(L)F4XK22 devices only.

2: PIC18(L)F2XK22 devices only.

3: PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

| R/W-0/u          | R/W-0/u                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0/u                                                                   | R/W-0/u                          | R/W/HC-0/u                                                                         | R-x/x           | R/W-0/u          | R/W-0/u    |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------|-----------------|------------------|------------|--|

| TMRxGE           | TxGPOL                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TxGTM                                                                     | TxGSPM                           | TxGGO/DONE                                                                         | TxGVAL          | TxGSS            | S<1:0>     |  |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |                                  |                                                                                    |                 |                  | bit 0      |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |                                  |                                                                                    |                 |                  |            |  |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |                                  |                                                                                    |                 |                  |            |  |

| R = Readable     | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                | W = Writable                                                              | bit                              | U = Unimplemer                                                                     |                 |                  |            |  |

| u = Bit is unch  | nanged                                                                                                                                                                                                                                                                                                                                                                                                                                                             | x = Bit is unkr                                                           | nown                             | -n/n = Value at P                                                                  | OR and BOR      | /Value at all ot | her Resets |  |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '0' = Bit is clea                                                         | ared                             | HC = Bit is clear                                                                  | ed by hardwa    | re               |            |  |

| bit 7            | If TMRxON =<br>This bit is ign<br>If TMRxON =<br>1 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                                                      | <br>ored<br><u>1</u> :<br>/5 counting is c                                | controlled by th                 | ne Timer1/3/5 gate<br>r1/3/5 gate function                                         |                 |                  |            |  |

| bit 6            | 1 = Timer1/3<br>0 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                                                                                       | /5 gate is activ                                                          | e-high (Timer1<br>e-low (Timer1/ | /3/5 counts when<br>3/5 counts when g                                              |                 |                  |            |  |

| bit 5            | 1 = Timer1/3<br>0 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                                                                                       | er1/3/5 Gate To<br>/5 Gate Toggle<br>/5 Gate Toggle<br>ate flip-flop togg | mode is enab                     | led<br>bled and toggle flip                                                        | -flop is cleare | d                |            |  |

| bit 4            | 1 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ner1/3/5 Gate 3<br>/5 gate Single-<br>/5 gate Single-                     | Pulse mode is                    | enabled and is co                                                                  | ontrolling Time | r1/3/5 gate      |            |  |

| bit 3            | 1 = Timer1/3<br>0 = Timer1/3                                                                                                                                                                                                                                                                                                                                                                                                                                       | /5 gate single- <sub> </sub><br>/5 gate single- <sub> </sub>              | oulse acquisition                | ulse Acquisition St<br>on is ready, waiting<br>on has completed<br>SPM is cleared. | g for an edge   | en started       |            |  |

| bit 2            | Indicates the                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           | f the Timer1/3/                  | /5 gate that could I                                                               | be provided to  | TMRxH:TMR        | xL.        |  |

| bit 1-0          | Indicates the current state of the Timer1/3/5 gate that could be provided to TMRxH:TMRxL.<br>Unaffected by Timer1/3/5 Gate Enable (TMRxGE).<br><b>TxGSS&lt;1:0&gt;:</b> Timer1/3/5 Gate Source Select bits<br>00 = Timer1/3/5 Gate pin<br>01 = Timer2/4/6 Match PR2/4/6 output (See Table 12-5 for proper timer match selection)<br>10 = Comparator 1 optionally synchronized output (sync_C1OUT)<br>11 = Comparator 2 optionally synchronized output (sync_C2OUT) |                                                                           |                                  |                                                                                    |                 |                  |            |  |

## REGISTER 12-2: TXGCON: TIMER1/3/5 GATE CONTROL REGISTER

## 13.1 Timer2/4/6 Operation

The clock input to the Timer2/4/6 module is the system instruction clock (Fosc/4).

TMRx increments from 00h on each clock edge.

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, TxCKPS<1:0> of the TxCON register. The value of TMRx is compared to that of the Period register, PRx, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMRx to 00h on the next cycle and drives the output counter/postscaler (see Section 13.2 "Timer2/4/6 Interrupt").

The TMRx and PRx registers are both directly readable and writable. The TMRx register is cleared on any device Reset, whereas the PRx register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMRx register

- a write to the TxCON register

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- Watchdog Timer (WDT) Reset

- Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

Note: TMRx is not cleared when TxCON is written.

## 13.2 Timer2/4/6 Interrupt

Timer2/4/6 can also generate an optional device interrupt. The Timer2/4/6 output signal (TMRx-to-PRx match) provides the input for the 4-bit counter/postscaler. This counter generates the TMRx match interrupt flag which is latched in TMRxIF of the PIR1/PIR5 registers. The interrupt is enabled by setting the TMRx Match Interrupt Enable bit, TMRxIE of the PIE1/PIE5 registers. Interrupt Priority is selected with the TMRxIP bit in the IPR1/IPR5 registers.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, TxOUTPS<3:0>, of the TxCON register.

## 13.3 Timer2/4/6 Output

The unscaled output of TMRx is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode. The timer to be used with a specific CCP module is selected using the CxTSEL<1:0> bits in the CCPTMRS0 and CCPTMRS1 registers.

Timer2 can be optionally used as the shift clock source for the MSSPx modules operating in SPI mode by setting SSPM<3:0> = 0011 in the SSPxCON1 register. Additional information is provided in Section 15.0 "Master Synchronous Serial Port (MSSP1 and MSSP2) Module".

## 13.4 Timer2/4/6 Operation During Sleep

The Timer2/4/6 timers cannot be operated while the processor is in Sleep mode. The contents of the TMRx and PRx registers will remain unchanged while the processor is in Sleep mode.

## 13.5 Peripheral Module Disable

When a peripheral module is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bits for Timer2 (TMR2MD), Timer4 (TMR4MD) and Timer6 (TMR6MD) are in the PMD0 Register. See Section 3.0 "Power-Managed Modes" for more information.

| .egend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reservers         it 7-6       PxM       '0' = Bit is cleared         it 7-6       PxM       CPxM<3:2> = 00, 01, 10: (Capture/Compare modes)         xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins         Half-Bridge ECCP Modules <sup>(1)</sup> :       If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA, modulated; PxB assigned as port pin       1x = Half-Bridge output; PxA, PxB modulated with dead-band control         Full-Bridge ECCP Modules <sup>(1)</sup> :       If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA, nodulated; PxB assigned as port pin         1x = Half-Bridge output; PxA, PxB modulated with dead-band control         Full-Bridge ECCP Modules <sup>(1)</sup> :         If CCPxM<3:2> = 11: (PWM modes)         00 = Single output; PxA, modulated; PxB, PxC, PxD assigned as port pins         01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive         10 = Half-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as port pins         11 = Full-Bridge output; reverse; PxB modulated; PxC active; PxA, PxD inactive                                                                                                                                                                                                                                    | R/x-0            | R/W-0                                                                                          | R/W-0                                                                       | R/W-0                                                          | R/W-0                                                 | R/W-0                             | R/W-0                   | R/W-0         |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------|-----------------------------------|-------------------------|---------------|--|

| Aregend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         I = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Rese         I' = Bit is set       '0' = Bit is cleared         it 7-6 <b>PxM&lt;1:0</b> >: Enhanced PWM Output Configuration bits         If CCPxM<3:2> = 00, 01, 10: (Capture/Compare modes)         xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins         Half-Bridge ECCP Modules <sup>(1)</sup> :         If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA modulated; PxB assigned as port pin         1x = Half-Bridge output; PxA, modulated; PxB, PxC, PxD assigned as port pin         1x = Half-Bridge output; PxA, modulated; PxB, PxC, PxD assigned as port pin         1x = Half-Bridge output; PxA, modulated; PxB, PxC, PxD assigned as port pins         01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive         10 = Half-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as port pins         11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive         10 = Half-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive         11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive         11 = Full-Bridge output coverse; PxB modulated; PxC active; PxA, PxD inactive         11 = Full-Bridge output; PxA, PxB modulat                                                                                           | PxM<1:0>         |                                                                                                | DCx                                                                         | 3<1:0>                                                         |                                                       | CCPx                              | V<3:0>                  |               |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         i = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reserverse         i' = Bit is set       '0' = Bit is cleared         wit 7-6       PxM<1:0>: Enhanced PWM Output Configuration bits         If CCPxM<3:2> = 00, 01, 10: (Capture/Compare modes)         xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins         Half-Bridge ECCP Modules <sup>(1)</sup> :         If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA modulated; PxB assigned as port pin         1x = Half-Bridge output; PxA, PxB modulated with dead-band control         Full-Bridge ECCP Modules <sup>(1)</sup> :         If CCPxM<3:2> = 11: (PWM modes)         00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pin         1x = Half-Bridge output; PxA, PxB modulated; PxA active; PxB, PxC inactive         10 = Single output; PxA, modulated; PxB pxC, PxD assigned as port pins         01 = Full-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as port pins         11 = Full-Bridge output; PxA, PxB modulated; with dead-band control; PxC, PxD assigned as port pins         11 = Full-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive         10 = Half-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive         11 = Full-Bridge output cycle Least Significant bits                                                                                                   | bit 7            |                                                                                                |                                                                             |                                                                |                                                       |                                   |                         | bit (         |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         i = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reserverse         i' = Bit is set       '0' = Bit is cleared         wit 7-6       PxM<1:0>: Enhanced PWM Output Configuration bits         If CCPxM<3:2> = 00, 01, 10: (Capture/Compare modes)         xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins         Half-Bridge ECCP Modules <sup>(1)</sup> :         If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA modulated; PxB assigned as port pin         1x = Half-Bridge output; PxA, PxB modulated with dead-band control         Full-Bridge ECCP Modules <sup>(1)</sup> :         If CCPxM<3:2> = 11: (PWM modes)         00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pin         1x = Half-Bridge output; PxA, PxB modulated; PxA active; PxB, PxC inactive         10 = Single output; PxA, modulated; PxB pxC, PxD assigned as port pins         01 = Full-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as port pins         11 = Full-Bridge output; PxA, PxB modulated; with dead-band control; PxC, PxD assigned as port pins         11 = Full-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive         10 = Half-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive         11 = Full-Bridge output cycle Least Significant bits                                                                                                   |                  |                                                                                                |                                                                             |                                                                |                                                       |                                   |                         |               |  |

| a = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reservers         it 7-6       PxM<1:0>: Enhanced PWM Output Configuration bits       If CCPxM<3:2> = 00, 01, 10: (Capture/Compare modes)         xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins       Half-Bridge ECCP Modules <sup>(1)</sup> :       If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA modulated; PxB assigned as port pin       1x = Half-Bridge cutput; PxA, PxB modulated with dead-band control         Full-Bridge ECCP Modules <sup>(1)</sup> :       If CCPxM<3:2> = 11: (PWM modes)       00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins         00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins       If CCPxM<3:2> = 11: (PWM modes)       00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins         01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive       10 = Half-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD assigned as port pins         11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive       11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive         11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive       Capture mode:         Unused       Compare mode:       Unused         Compare mode:       Unused       Compare mode:         Unused       PWM mode:       These bits are the two LSbs of the PWM duty cycle. The eight MSb | Legend:          |                                                                                                |                                                                             |                                                                |                                                       |                                   |                         |               |  |

| <ul> <li>i' = Bit is set</li> <li>'0' = Bit is cleared</li> <li>it 7-6</li> <li>PxM&lt;1:0&gt;: Enhanced PWM Output Configuration bits<br/>If CCPxM&lt;3:2&gt; = 00, 01, 10: (Capture/Compare modes)<br/>xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins</li> <li>Half-Bridge ECCP Modules<sup>(1)</sup>:<br/>If CCPxM&lt;3:2&gt; = 11: (PWM modes)</li> <li>0x = Single output; PxA modulated; PxB assigned as port pin<br/>1x = Half-Bridge output; PxA, PxB modulated with dead-band control</li> <li>Full-Bridge ECCP Modules<sup>(1)</sup>:<br/>If CCPxM&lt;3:2&gt; = 11: (PWM modes)</li> <li>00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins<br/>01 = Full-Bridge output; PxA modulated; PxB, PxC, PxD assigned as port pins<br/>01 = Full-Bridge output; PxA modulated; PxB modulated; PxA active; PxB, PxC inactive<br/>10 = Half-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD assigned as port<br/>pins<br/>11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive</li> <li>it 5-4</li> <li>DCxB&lt;1:0&gt;: PWM Duty Cycle Least Significant bits<br/>Capture mode:<br/>Unused<br/>Compare mode:<br/>Unused</li> <li>PWM mode:<br/>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.</li> </ul>                                                                                                                                                                                                                                                                                            | R = Readable     | e bit                                                                                          | W = Writable b                                                              | bit                                                            | U = Unimple                                           | mented bit, rea                   | ad as '0'               |               |  |

| <ul> <li>PxM&lt;1:0&gt;: Enhanced PWM Output Configuration bits<br/>If CCPxM&lt;3:2&gt; = 00, 01, 10: (Capture/Compare modes)<br/>xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins<br/>Half-Bridge ECCP Modules<sup>(1)</sup>:<br/>If CCPxM&lt;3:2&gt; = 11: (PWM modes)<br/>0x = Single output; PxA modulated; PxB assigned as port pin<br/>1x = Half-Bridge output; PxA, PxB modulated with dead-band control<br/>Full-Bridge ECCP Modules<sup>(1)</sup>:<br/>If CCPxM&lt;3:2&gt; = 11: (PWM modes)<br/>00 = Single output; PxA, modulated; PxB, PxC, PxD assigned as port pins<br/>01 = Full-Bridge output; PxA modulated; PxB, PxC, PxD assigned as port pins<br/>01 = Full-Bridge output; PxA, PxB modulated; PxA active; PxB, PxC inactive<br/>10 = Half-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive<br/>11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive<br/>12 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive<br/>13 = Full-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive<br/>14 = Full-Bridge output; PxB modulated; PxC active; PxA, PxD inactive<br/>15 = Unused<br/>Compare mode:<br/>Unused<br/><u>PWM mode:</u><br/>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.</li> </ul>                                                                                                                                                                                                                                                                 | u = Bit is unc   | hanged                                                                                         | x = Bit is unkn                                                             | own                                                            | -n/n = Value                                          | at POR and B                      | OR/Value at al          | I other Reset |  |

| If CCPxM<3:2> = 00, 01, 10: (Capture/Compare modes)<br>xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins<br>Half-Bridge ECCP Modules <sup>(1)</sup> :<br>If CCPxM<3:2> = 11: (PWM modes)<br>0x = Single output; PxA modulated; PxB assigned as port pin<br>1x = Half-Bridge output; PxA, PxB modulated with dead-band control<br>Full-Bridge ECCP Modules <sup>(1)</sup> :<br>If CCPxM<3:2> = 11: (PWM modes)<br>00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins<br>01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive<br>10 = Half-Bridge output forward; PxD modulated with dead-band control; PxC, PxD assigned as port<br>pins<br>11 = Full-Bridge output; PxA, PxB modulated; PxC active; PxA, PxD inactive<br>11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive<br>11 = Full-Bridge output cycle Least Significant bits<br>Capture mode:<br>Unused<br>Compare mode:<br>Unused<br>PWM mode:<br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | '1' = Bit is set | t                                                                                              | '0' = Bit is clea                                                           | red                                                            |                                                       |                                   |                         |               |  |

| If CCPxM<3:2> = 11: (PWM modes)         0x = Single output; PxA modulated; PxB assigned as port pin         1x = Half-Bridge output; PxA, PxB modulated with dead-band control         Full-Bridge ECCP Modules <sup>(1)</sup> :<br>If CCPxM<3:2> = 11: (PWM modes)         00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins         01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive         10 = Half-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as por<br>pins         11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive         it 5-4       DCxB<1:0>: PWM Duty Cycle Least Significant bits         Capture mode:<br>Unused       Unused         PWM mode:<br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 7-6          | ľ                                                                                              | f CCPxM<3:2> =                                                              | 00, 01, 10:                                                    | (Capture/Comp                                         | ,                                 | l as port pins          |               |  |

| <ul> <li>If CCPxM&lt;3:2&gt; = 11: (PWM modes)</li> <li>00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins</li> <li>01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive</li> <li>10 = Half-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as por pins</li> <li>11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive</li> <li>bit 5-4</li> <li>bit 5-4</li> <li>bit 5-4</li> <li>bit 5-4</li> <li>capture mode:<br/>Unused</li> <li>Unused</li> <li>compare mode:<br/>Unused</li> <li>PWM mode:<br/>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  | If CCPxM<3:2> = 11: (PWM modes)<br>0x = Single output; PxA modulated; PxB assigned as port pin |                                                                             |                                                                |                                                       |                                   |                         |               |  |

| Capture mode:<br>Unused<br>Compare mode:<br>Unused<br><u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  | ا<br>00 = Singl<br>01 = Full-E<br>10 = Half-<br>pins                                           | CCPxM<3:2> =<br>e output; PxA mo<br>Bridge output forw<br>Bridge output; Px | 11: (PWM mod<br>dulated; PxB,<br>vard; PxD mod<br>A, PxB modul | PxC, PxD assig<br>ulated; PxA acti<br>ated with dead- | ve; PxB, PxC i<br>band control; I | nactive<br>PxC, PxD ass | igned as por  |  |

| Unused<br><u>Compare mode:</u><br>Unused<br><u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 5-4          | DCxB<1:0:                                                                                      | -: PWM Duty Cyc                                                             | le Least Signi                                                 | ficant bits                                           |                                   |                         |               |  |

| Unused<br><u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  | Capture mode:                                                                                  |                                                                             |                                                                |                                                       |                                   |                         |               |  |

| These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  | •                                                                                              | node:                                                                       |                                                                |                                                       |                                   |                         |               |  |

| lote 1: See Table 14-1 to determine full-bridge and half-bridge ECCPs for the device being used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                                                                                                |                                                                             | of the PWM d                                                   | uty cycle. The e                                      | ight MSbs are t                   | found in CCPF           | RxL.          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Note 1: Se       | ee Table 14-1 t                                                                                | o determine full-b                                                          | oridge and half                                                | -bridge ECCPs                                         | for the device b                  | being used.             |               |  |

### REGISTER 14-2: CCPxCON: ENHANCED CCPx CONTROL REGISTER

## 15.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPxOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 15-5.

An MSSPx interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCLx will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 15.2.3 "SPI Master Mode"** for more detail.

#### 15.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSPx module configured as an  $I^2C$  slave in 7-bit Addressing mode. All decisions made by hardware or software and their effect on reception. Figure 15-14 and Figure 15-5 are used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $\mathsf{I}^2\mathsf{C}$  communication.

- 1. Start bit detected.

- S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCLx line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes Idle.

## 15.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the 8th falling edge of SCLx. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 15-16 displays a module using both address and data holding. Figure 15-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- 1. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the 8th falling edge of SCLx.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPx-CON3 register to <u>determine</u> if the SSPxIF was after or before the ACK.

- 5. Slave reads the address value from SSPxBUF, clearing the BF flag.

- Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF

**Note:** SSPxIF is still set after the 9th falling edge of SCLx even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPxIF not set.

- 11. SSPxIF set and CKP cleared after 8th falling edge of SCLx for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

#### 15.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the 8th falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 15-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the 8th falling edge of the SCLx line the CKP bit is cleared and SSPxIF interrupt is generated.

- 4. Slave software clears SSPxIF.

- Slave software reads ACKTIM bit of SSPxCON3 register, and R/W and D/A of the SSPxSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPxBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCLx.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

Note: <u>SSPxBUF</u> cannot be loaded until after the ACK.

- 13. Slave sets CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the 9th SCLx pulse.

- 15. Slave hardware copies the  $\overline{ACK}$  value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCLx line to receive a Stop.

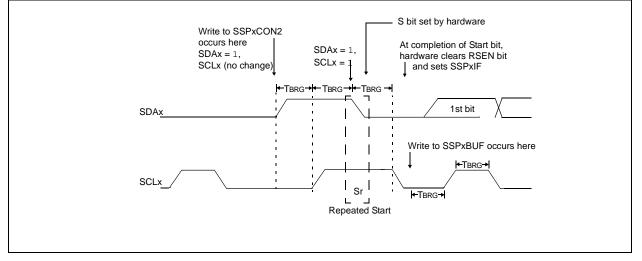

## 15.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING