Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2014110                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 35                                                                           |

| Program Memory Size        | 8KB (4K x 16)                                                                |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 30x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 40-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 40-UQFN (5x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf43k22t-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|  | Pin Number<br>PDIP, QFN,<br>SOIC UQFN |        |          | Pin  | Buffer |                                          |

|--|---------------------------------------|--------|----------|------|--------|------------------------------------------|

|  |                                       |        | Pin Name | Туре | Туре   | Description                              |

|  | 20                                    | 17 VDD |          | Р    | _      | Positive supply for logic and I/O pins.  |

|  | 8, 19                                 | 5, 16  | Vss      | Р    | _      | Ground reference for logic and I/O pins. |

#### TABLE 1-2: PIC18(L)F2XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

| TABLE 1-3: | PIC18(L)F4XK22 PINOUT I/O DESCRIPTIONS |

|------------|----------------------------------------|

|------------|----------------------------------------|

| Pin Number |      | Din Nama | Pin  | Buffer               | Description     |        |                                        |  |  |

|------------|------|----------|------|----------------------|-----------------|--------|----------------------------------------|--|--|

| PDIP       | TQFP | QFN      | UQFN | Pin Name             | Туре            | Туре   | Description                            |  |  |

| 2          | 19   | 19       | 17   | RA0/C12IN0-/AN0      |                 |        |                                        |  |  |

|            |      |          |      | RA0                  | I/O             | TTL    | Digital I/O.                           |  |  |

|            |      |          |      | C12IN0-              | Ι               | Analog | Comparators C1 and C2 inverting input. |  |  |

|            |      |          |      | AN0                  | Ι               | Analog | Analog input 0.                        |  |  |

| 3          | 20   | 20       | 18   | RA1/C12IN1-/AN1      |                 |        |                                        |  |  |

|            |      |          |      | RA1                  | I/O             | TTL    | Digital I/O.                           |  |  |

|            |      |          |      | C12IN1-              | I               | Analog | Comparators C1 and C2 inverting input. |  |  |

|            |      |          |      | AN1                  | I               | Analog | Analog input 1.                        |  |  |

| 4          | 21   | 21       | 19   | RA2/C2IN+/AN2/DACOUT | Wref-           |        |                                        |  |  |

|            |      |          |      | RA2                  | I/O             | TTL    | Digital I/O.                           |  |  |

|            |      |          |      | C2IN+                | I               | Analog | Comparator C2 non-inverting input.     |  |  |

|            |      |          |      | AN2                  | I               | Analog | Analog input 2.                        |  |  |

|            |      |          |      | DACOUT               | 0               | Analog | DAC Reference output.                  |  |  |

|            |      |          |      | VREF-                | I               | Analog | A/D reference voltage (low) input.     |  |  |

| 5          | 22   | 22       | 20   | RA3/C1IN+/AN3/VREF+  |                 |        |                                        |  |  |

|            |      |          |      | RA3                  | I/O             | TTL    | Digital I/O.                           |  |  |

|            |      |          |      | C1IN+                | I               | Analog | Comparator C1 non-inverting input.     |  |  |

|            |      |          |      | AN3                  | I               | Analog | Analog input 3.                        |  |  |

|            |      |          |      | VREF+                | I               | Analog | A/D reference voltage (high) input.    |  |  |

| 6          | 23   | 23       | 21   | RA4/C1OUT/SRQ/T0CKI  |                 |        |                                        |  |  |

|            |      |          |      | RA4                  | I/O             | ST     | Digital I/O.                           |  |  |

|            |      |          |      | C1OUT                | 0               | CMOS   | Comparator C1 output.                  |  |  |

|            |      |          |      | SRQ                  | 0               | TTL    | SR latch Q output.                     |  |  |

|            |      |          |      | TOCKI                | l<br>atible inc | ST     | Timer0 external clock input.           |  |  |

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

#### 2.2 Oscillator Control

The OSCCON, OSCCON2 and OSCTUNE registers (Register 2-1 to Register 2-3) control several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

- Main System Clock Selection (SCS)

- Primary Oscillator Circuit Shutdown (PRISD)

- Secondary Oscillator Enable (SOSCGO)

- Primary Clock Frequency 4x multiplier (PLLEN)

- Internal Frequency selection bits (IRCF, INTSRC)

- Clock Status bits (OSTS, HFIOFS, MFIOFS, LFIOFS. SOSCRUN, PLLRDY)

- Power management selection (IDLEN)

#### 2.2.1 MAIN SYSTEM CLOCK SELECTION

The System Clock Select bits, SCS<1:0>, select the main clock source. The available clock sources are

- Primary clock defined by the FOSC<3:0> bits of CONFIG1H. The primary clock can be the primary oscillator, an external clock, or the internal oscillator block.

- Secondary clock (secondary oscillator)

- Internal oscillator block (HFINTOSC, MFINTOSC and LFINTOSC).

The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared to select the primary clock on all forms of Reset.

#### 2.2.2 INTERNAL FREQUENCY SELECTION

The Internal Oscillator Frequency Select bits (IRCF<2:0>) select the frequency output of the internal oscillator block. The choices are the LFINTOSC source (31.25 kHz), the MFINTOSC source (31.25 kHz, 250 kHz or 500 kHz) and the HFINTOSC source (16 MHz) or one of the frequencies derived from the HFINTOSC postscaler (31.25 kHz to 8 MHz). If the internal oscillator block is supplying the main clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the output frequency of the internal oscillator is set to the default frequency of 1 MHz.

#### 2.2.3 LOW FREQUENCY SELECTION

When a nominal output frequency of 31.25 kHz is selected (IRCF<2:0> = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit of the OSCTUNE register and MFIOSEL bit of the OSCCON2 register. See Figure 2-2 and Register 2-1 for specific 31.25 kHz selection. This option allows users to select a 31.25 kHz clock (MFINTOSC or HFINTOSC) that can be tuned using the TUN<5:0> bits in OSCTUNE register, while maintaining power savings with a very low clock speed. LFINTOSC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor, regardless of the setting of INTSRC and MFIOSEL bits

This option allows users to select the tunable and more precise HFINTOSC as a clock source, while maintaining power savings with a very low clock speed.

#### 2.2.4 POWER MANAGEMENT

The IDLEN bit of the OSCCON register determines whether the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

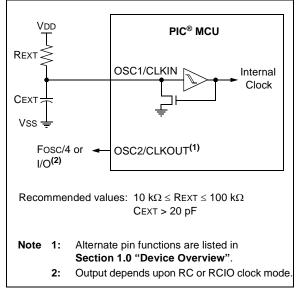

#### 2.5.4 EXTERNAL RC MODES

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO.

#### 2.5.4.1 RC Mode

In RC mode, the RC circuit connects to OSC1. OSC2/ CLKOUT outputs the RC oscillator frequency divided by four. This signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements. Figure 2-8 shows the external RC mode connections.

#### FIGURE 2-8: EXTERNAL RC MODES

#### 2.5.4.2 RCIO Mode

In RCIO mode, the RC circuit is connected to OSC1. OSC2 becomes a general purpose I/O pin.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- input threshold voltage variation

- component tolerances

- · packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

#### 2.6 Internal Clock Modes

The oscillator module has three independent, internal oscillators that can be configured or selected as the system clock source.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 2-3).

- The MFINTOSC (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 2-3).

- The LFINTOSC (Low-Frequency Internal Oscillator) is factory calibrated and operates at 31.25 kHz. The LFINTOSC cannot be useradjusted, but is designed to be stable over temperature and voltage.

The system clock speed can be selected via software using the Internal Oscillator Frequency select bits IRCF<2:0> of the OSCCON register.

The system clock can be selected between external or internal clock sources via the System Clock Selection (SCS<1:0>) bits of the OSCCON register. See **Section 2.11 "Clock Switching"** for more information.

#### 2.6.1 INTOSC WITH I/O OR CLOCKOUT

Two of the clock modes selectable with the FOSC<3:0> bits of the CONFIG1H Configuration register configure the internal oscillator block as the primary oscillator. Mode selection determines whether the OSC2/ CLKOUT pin will be configured as general purpose I/O or FOSC/4 (CLKOUT). In both modes, the OSC1/CLKIN pin is configured as general purpose I/O. See **Section 24.0 "Special Features of the CPU"** for more information.

The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

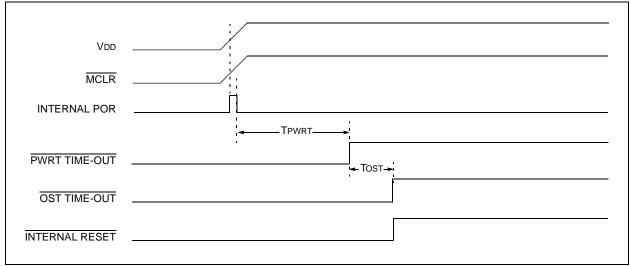

#### TABLE 4-2: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator     | Power-up <sup>(2)</sup> ar                             | Power-up <sup>(2)</sup> and Brown-out |                                 |  |  |  |  |

|----------------|--------------------------------------------------------|---------------------------------------|---------------------------------|--|--|--|--|

| Configuration  | <b>PWRTEN</b> = 0                                      | PWRTEN = 1                            | Power-Managed Mode              |  |  |  |  |

| HSPLL          | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup>       | 1024 Tosc + 2 ms <sup>(2)</sup> |  |  |  |  |

| HS, XT, LP     | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                             | 1024 Tosc                       |  |  |  |  |

| EC, ECIO       | 66 ms <sup>(1)</sup>                                   | _                                     | —                               |  |  |  |  |

| RC, RCIO       | 66 ms <sup>(1)</sup>                                   | _                                     | —                               |  |  |  |  |

| INTIO1, INTIO2 | 66 ms <sup>(1)</sup>                                   |                                       | —                               |  |  |  |  |

Note 1: 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.2: 2 ms is the nominal time required for the PLL to lock.

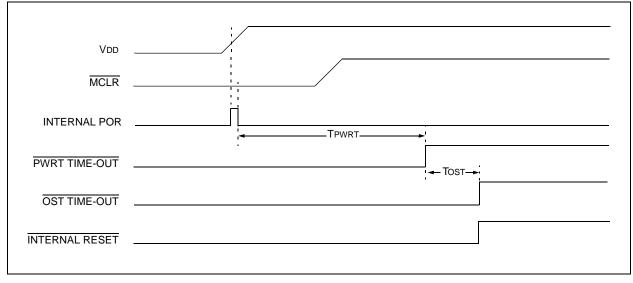

#### FIGURE 4-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD, VDD RISE < TPWRT)

### FIGURE 4-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

|          | 00111 |       |       |       |        |        |        |        |                     |  |  |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|--|--|

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |  |

| CONFIG2L |       |       |       | BORV  | <1:0>  | BOREI  | N<1:0> | PWRTEN | 346                 |  |  |

| CONFIG2H | _     | -     |       | WDPS  | 6<3:0> |        | WDTE   | N<1:0> | 347                 |  |  |

| CONFIG3H | MCLRE | —     | P2BMX | T3CMX | HFOFST | CCP3MX | PBADEN | CCP2MX | 348                 |  |  |

| CONFIG4L | DEBUG | XINST |       |       |        | LVP    |        | STRVEN | 349                 |  |  |

TABLE 4-5: CONFIGURATION REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for Resets.

| Address | Name     | Bit 7       | Bit 6                                     | Bit 5           | Bit 4           | Bit 3                           | Bit 2           | Bit 1           | Bit 0            | <u>Value c</u><br>POR, BO |     |

|---------|----------|-------------|-------------------------------------------|-----------------|-----------------|---------------------------------|-----------------|-----------------|------------------|---------------------------|-----|

| FFFh    | TOSU     | —           | — — Top-of-Stack, Upper Byte (TOS<20:16>) |                 |                 |                                 |                 |                 |                  |                           | 000 |

| FFEh    | TOSH     |             |                                           | Тор             | -of-Stack, High | Byte (TOS<15                    | 5:8>)           |                 |                  | 0000 00                   | 000 |

| FFDh    | TOSL     |             | Top-of-Stack, Low Byte (TOS<7:0>)         |                 |                 |                                 |                 |                 |                  |                           |     |

| FFCh    | STKPTR   | STKFUL      | STKUNF                                    | _               |                 | ç                               | STKPTR<4:0>     |                 |                  | 00-00                     | 000 |

| FFBh    | PCLATU   | _           | _                                         | _               |                 | Holding F                       | Register for PC | <20:16>         |                  | 0 00                      | 000 |

| FFAh    | PCLATH   |             | •                                         | ŀ               | Holding Regist  | er for PC<15:8                  | >               |                 |                  | 0000 00                   | 000 |

| FF9h    | PCL      |             |                                           |                 | Holding Regis   | ter for PC<7:0>                 | •               |                 |                  | 0000 00                   | 000 |

| FF8h    | TBLPTRU  | _           | _                                         | Pi              | rogram Memor    | y Table Pointer                 | Upper Byte(T    | BLPTR<21:16     | 6>)              | 00 00                     | 000 |

| FF7h    | TBLPTRH  |             | F                                         | Program Memo    | ory Table Point | ter High Byte(T                 | BLPTR<15:8>     | )               |                  | 0000 00                   | 000 |

| FF6h    | TBLPTRL  |             | Р                                         | rogram Memo     | ory Table Point | er Low Byte(TE                  | 3LPTR<7:0>)     |                 |                  | 0000 00                   | 000 |

| FF5h    | TABLAT   |             |                                           |                 | Program Men     | ory Table Latc                  | h               |                 |                  | 0000 00                   | 000 |

| FF4h    | PRODH    |             |                                           |                 | Product Regis   | ter, High Byte                  |                 |                 |                  | XXXX XX                   | xxx |

| FF3h    | PRODL    |             |                                           |                 | Product Regis   | ster, Low Byte                  |                 |                 |                  | XXXX XX                   | xxx |

| FF2h    | INTCON   | GIE/GIEH    | PEIE/GIEL                                 | TMR0IE          | INTOIE          | RBIE                            | TMR0IF          | INT0IF          | RBIF             | 0000 00                   | 00x |

| FF1h    | INTCON2  | RBPU        | INTEDG0                                   | INTEDG1         | INTEDG2         | _                               | TMR0IP          | _               | RBIP             | 1111 -1                   | 1-1 |

| FF0h    | INTCON3  | INT2IP      | INT1IP                                    | _               | INT2IE          | INT1IE                          | _               | INT2IF          | INT1IF           | 11-0 0-                   | -00 |

| FEFh    | INDF0    | Uses cont   | ents of FSR0                              | to address da   | ta memorv – v   | alue of FSR0 r                  | ot changed (no  | ot a physical r | egister)         |                           |     |

| FEEh    | POSTINCO |             |                                           |                 |                 | alue of FSR0 p                  | <b>.</b> .      |                 | • ,              |                           |     |

| FEDh    | POSTDEC0 |             |                                           |                 | ,               | alue of FSR0 p                  |                 | · · · ·         | 0 /              |                           |     |

| FECh    | PREINC0  |             |                                           |                 | ,               | alue of FSR0 p                  |                 | · · · ·         | 0 /              |                           |     |

| FEBh    | PLUSW0   |             |                                           |                 |                 | ie of FSR0 pre                  |                 |                 | <b>v</b> ,       |                           |     |

| FEAh    | FSR0H    | _           | _                                         | _               | _               | Indirect Dat                    | a Memory Add    | ress Pointer 0  | ), High Byte     | 00                        | 000 |

| FE9h    | FSR0L    | In          | direct Data Me                            | emory Addres    | s Pointer 0, Lo | w Byte                          |                 |                 |                  | XXXX XX                   | xxx |

| FE8h    | WREG     |             |                                           | 1               | Working Regis   | ter                             |                 |                 |                  | XXXX XX                   | xxx |

| FE7h    | INDF1    | Uses cor    | ntents of FSR1                            | to address d    | ata memory -    | value of FSR1                   | not changed (i  | not a physical  | reaister)        |                           |     |

| FE6h    | POSTINC1 |             |                                           |                 |                 | value of FSR1                   | 0 (             |                 | • <i>i</i>       |                           |     |

| FE5h    | POSTDEC1 |             |                                           |                 |                 | value of FSR1                   |                 |                 |                  |                           |     |

| FE4h    | PREINC1  |             |                                           |                 |                 | value of FSR1                   |                 |                 |                  |                           |     |

| FE3h    | PLUSW1   |             |                                           |                 | memory – val    | ue of FSR1 pre                  |                 |                 |                  |                           |     |

| FE2h    | FSR1H    | _           | _                                         | —               | _               | Indirect Dat                    | a Memory Add    | ress Pointer 1  | , High Byte      | 00                        | 000 |

| FE1h    | FSR1L    |             | •                                         | Indirect Data I | Memory Addre    | ss Pointer 1, L                 | ow Byte         |                 |                  | XXXX XX                   | xxx |

| FE0h    | BSR      | —           | —                                         | —               | —               |                                 | Bank Selec      | t Register      |                  | 00                        | 000 |

| FDFh    | INDF2    | Uses co     | ntents of FSR                             | 2 to address of | ata memory -    | value of FSR2                   | not changed (   | not a physical  | l register)      |                           |     |

| FDEh    | POSTINC2 | Uses co     | ntents of FSR                             | 2 to address d  | lata memory –   | value of FSR2                   | post-incremer   | ited (not a phy | /sical register) |                           |     |

| FDDh    | POSTDEC2 | Uses co     | ntents of FSR2                            | 2 to address d  | ata memory –    | value of FSR2                   | post-decreme    | nted (not a ph  | vsical register  | )                         |     |

| FDCh    | PREINC2  |             |                                           |                 |                 | - value of FSR2                 |                 |                 |                  |                           |     |

| FDBh    | PLUSW2   |             |                                           |                 | memory – val    | ue of FSR2 pre<br>2 offset by W |                 |                 | , s              |                           |     |

| FDAh    | FSR2H    | _           |                                           |                 |                 |                                 |                 |                 | 00               | 000                       |     |

| FD9h    | FSR2L    |             |                                           | ndirect Data N  | lemory Addres   | s Pointer 2, Lo                 | w Byte          |                 |                  | XXXX XX                   | xxx |

| FD8h    | STATUS   | N OV Z DC C |                                           |                 |                 |                                 |                 |                 | x xx             |                           |     |

| FD7h    | TMR0H    |             |                                           |                 |                 |                                 |                 |                 |                  | 0000 00                   |     |

| FD6h    | TMR0L    |             |                                           |                 |                 |                                 |                 |                 |                  | xxxx xx                   |     |

| FD5h    | TOCON    | TMR0ON      | T08BIT                                    | TOCS            | TOSE            | PSA                             |                 | T0PS<2:0>       |                  | 1111 11                   |     |

| FD3h    | OSCCON   | IDLEN       | 100011                                    | IRCF<2:0>       | 1002            | OSTS                            | HFIOFS          |                 | <1:0>            | 0011 q                    |     |

| FD2h    | OSCCON2  | PLLRDY      | SOSCRUN                                   |                 | MFIOSEL         | SOSCGO                          | PRISD           | MFIOFS          | LFIOFS           | 00-0 01                   |     |

| Legend: |          |             |                                           |                 |                 | nds on conditio                 |                 |                 |                  | 00.000                    | -70 |

TABLE 5-2: REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES

Note 1: PIC18(L)F4XK22 devices only.

2: PIC18(L)F2XK22 devices only.

3: PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

#### 8.0 8 x 8 HARDWARE MULTIPLIER

#### 8.1 Introduction

All PIC18 devices include an 8 x 8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 8-1.

#### 8.2 Operation

Example 8-1 shows the instruction sequence for an 8 x 8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 8-2 shows the sequence to do an 8 x 8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 8-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MULWF ARG2 ; ARG1 * ARG2 -><br>; PRODH:PRODL | MOVF  | ARG1, | W | ; |       |     |       |    |  |

|----------------------------------------------|-------|-------|---|---|-------|-----|-------|----|--|

| ; PRODH:PRODL                                | MULWF | ARG2  |   | ; | ARG1  | *   | ARG2  | -> |  |

|                                              |       |       |   | ; | PRODE | I:1 | PRODL |    |  |

#### EXAMPLE 8-2: 8 x 8 SIGNED MULTIPLY

| MOVF  | ARG1, W  |   |                |

|-------|----------|---|----------------|

| MULWF | ARG2     | ; | ARG1 * ARG2 -> |

|       |          | ; | PRODH:PRODL    |

| BTFSC | ARG2, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG1         |

| MOVF  | ARG2, W  |   |                |

| BTFSC | ARG1, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG2         |

|       |          |   |                |

|                  |                           | Program           | Cycles | Time     |          |          |         |  |  |

|------------------|---------------------------|-------------------|--------|----------|----------|----------|---------|--|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 64 MHz | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |  |

| Q v Q unoignod   | Without hardware multiply | 13                | 69     | 4.3 μs   | 6.9 μs   | 27.6 μs  | 69 μs   |  |  |

| 8 x 8 unsigned   | Hardware multiply         | 1                 | 1      | 62.5 ns  | 100 ns   | 400 ns   | 1 μs    |  |  |

| Q v Q aignad     | Without hardware multiply | 33                | 91     | 5.7 μs   | 9.1 μs   | 36.4 μs  | 91 μs   |  |  |

| 8 x 8 signed     | Hardware multiply         | 6                 | 6      | 375 ns   | 600 ns   | 2.4 μs   | 6 μs    |  |  |

| 16 x 16 uppigpod | Without hardware multiply | 21                | 242    | 15.1 μs  | 24.2 μs  | 96.8 μs  | 242 μs  |  |  |

| 16 x 16 unsigned | Hardware multiply         | 28                | 28     | 1.8 μs   | 2.8 μs   | 11.2 μs  | 28 μs   |  |  |

| 16 x 16 signed   | Without hardware multiply | 52                | 254    | 15.9 μs  | 25.4 μs  | 102.6 μs | 254 μs  |  |  |

| 16 x 16 signed   | Hardware multiply         | 35                | 40     | 2.5 μs   | 4.0 μs   | 16.0 μs  | 40 μs   |  |  |

#### TABLE 8-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

#### TABLE 10-1: PORTA I/O SUMMARY

| Pin Name                       | Function | TRIS<br>Setting | ANSEL<br>Setting | Pin<br>Type | Buffer<br>Type | Description                                                                                                          |  |  |  |

|--------------------------------|----------|-----------------|------------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| RA0/C12IN0-/AN0                | RA0      | 0               | 0                | 0           | DIG            | LATA<0> data output; not affected by analog input.                                                                   |  |  |  |

|                                |          | 1               | 0                | Ι           | TTL            | PORTA<0> data input; disabled when analog input enabled.                                                             |  |  |  |

|                                | C12IN0-  | 1               | 1                | Ι           | AN             | Comparators C1 and C2 inverting input.                                                                               |  |  |  |

|                                | AN0      | 1               | 1                | I           | AN             | Analog input 0.                                                                                                      |  |  |  |

| RA1/C12IN1-/AN1                | RA1      | 0               | 0                | 0           | DIG            | LATA<1> data output; not affected by analog input.                                                                   |  |  |  |

|                                |          | 1               | 0                | I           | TTL            | PORTA<1> data input; disabled when analog input enabled.                                                             |  |  |  |

|                                | C12IN1-  | 1               | 1                | I           | AN             | Comparators C1 and C2 inverting input.                                                                               |  |  |  |

|                                | AN1      | 1               | 1                | I           | AN             | Analog input 1.                                                                                                      |  |  |  |

| RA2/C2IN+/AN2/<br>DACOUT/VREF- | RA2      | 0               | 0                | 0           | DIG            | LATA<2> data output; not affected by analog input; disabled when DACOUT enabled.                                     |  |  |  |

|                                |          | 1               | 0                | Ι           | TTL            | PORTA<2> data input; disabled when analog input enabled;<br>disabled when DACOUT enabled.                            |  |  |  |

|                                | C2IN+    | 1               | 1                | Ι           | AN             | Comparator C2 non-inverting input.                                                                                   |  |  |  |

|                                | AN2      | 1               | 1                | Ι           | AN             | Analog output 2.                                                                                                     |  |  |  |

|                                | DACOUT   | x               | 1                | 0           | AN             | DAC Reference output.                                                                                                |  |  |  |

|                                | VREF-    | 1               | 1                | Ι           | AN             | A/D reference voltage (low) input.                                                                                   |  |  |  |

| RA3/C1IN+/AN3/                 | RA3      | 0               |                  | 0           | DIG            | LATA<3> data output; not affected by analog input.                                                                   |  |  |  |

| VREF+                          |          | 1               | 0                | I           | TTL            | PORTA<3> data input; disabled when analog input enabled.                                                             |  |  |  |

|                                | C1IN+    | 1               | 1                | I           | AN             | Comparator C1 non-inverting input.                                                                                   |  |  |  |

|                                | AN3      | 1               | 1                | I           | AN             | Analog input 3.                                                                                                      |  |  |  |

|                                | VREF+    | 1               | 1                | I           | AN             | A/D reference voltage (high) input.                                                                                  |  |  |  |

| RA4/CCP5/C1OUT/                | RA4      | 0               | —                | 0           | DIG            | LATA<4> data output.                                                                                                 |  |  |  |

| SRQ/T0CKI                      |          | 1               | _                | I           | ST             | PORTA<4> data input; default configuration on POR.                                                                   |  |  |  |

|                                | CCP5     | 0               | _                | 0           | DIG            | CCP5 Compare output/PWM output, takes priority over RA4 output                                                       |  |  |  |

|                                |          | 1               | —                | Ι           | ST             | Capture 5 input/Compare 5 output/ PWM 5 output.                                                                      |  |  |  |

|                                | C1OUT    | 0               | _                | 0           | DIG            | Comparator C1 output.                                                                                                |  |  |  |

|                                | SRQ      | 0               | _                | 0           | DIG            | SR latch Q output; take priority over CCP 5 output.                                                                  |  |  |  |

|                                | TOCKI    | 1               | _                | I           | ST             | Timer0 external clock input.                                                                                         |  |  |  |

| RA5/C2OUT/SRNQ/                | RA5      | 0               | 0                | 0           | DIG            | LATA<5> data output; not affected by analog input.                                                                   |  |  |  |

| SS1/<br>HLVDIN/AN4             |          | 1               | 0                | I           | TTL            | PORTA<5> data input; disabled when analog input enabled.                                                             |  |  |  |

| HLVDIN/AN4                     | C2OUT    | 0               | 0                | 0           | DIG            | Comparator C2 output.                                                                                                |  |  |  |

|                                | SRNQ     | 0               | 0                | 0           | DIG            | SR latch $\overline{Q}$ output.                                                                                      |  |  |  |

|                                | SS1      | 1               | 0                | I           | TTL            | SPI slave select input (MSSP1).                                                                                      |  |  |  |

|                                | HLVDIN   | 1               | 1                | I           | AN             | High/Low-Voltage Detect input.                                                                                       |  |  |  |

|                                | AN4      | 1               | 1                | 1           | AN             | A/D input 4.                                                                                                         |  |  |  |

| RA6/CLKO/OSC2                  | RA6      | 0               | _                | 0           | DIG            | LATA<6> data output; enabled in INTOSC modes when CLKO is no<br>enabled.                                             |  |  |  |

|                                |          | 1               | —                | Ι           | TTL            | PORTA<6> data input; enabled in INTOSC modes when CLKO is not enabled.                                               |  |  |  |

|                                | CLKO     | x               | —                | 0           | DIG            | In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the fre-<br>quency of OSC1 and denotes the instruction cycle rate. |  |  |  |

|                                | OSC2     | x               | _                | 0           | XTAL           | Oscillator crystal output; connects to crystal or resonator in Crystal Oscillator mode.                              |  |  |  |

| RA7/CLKI/OSC1                  | RA7      | 0               | _                | 0           | DIG            | LATA<7> data output; disabled in external oscillator modes.                                                          |  |  |  |

|                                |          | 1               | —                | Ι           | TTL            | PORTA<7> data input; disabled in external oscillator modes.                                                          |  |  |  |

|                                | CLKI     | x               | —                | I           | AN             | External clock source input; always associated with pin function OSC1.                                               |  |  |  |

|                                | OSC1     | x               |                  | Ι           | XTAL           | Oscillator crystal input or external clock source input ST buffer wher<br>configured in RC mode; CMOS otherwise.     |  |  |  |

Legend: AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C.

#### TABLE 10-8: PORTC I/O SUMMARY

| Pin Name           | Function             | TRIS<br>Setting | ANSEL setting | Pin<br>Type | Buffer<br>Type   | Description                                                 |

|--------------------|----------------------|-----------------|---------------|-------------|------------------|-------------------------------------------------------------|

| RC0/P2B/T3CKI/T3G/ | RC0                  | 0               | _             | 0           | DIG              | LATC<0> data output; not affected by analog input.          |

| T1CKI/SOSCO        |                      | 1               | _             | I           | ST               | PORTC<0> data input; disabled when analog input enabled.    |

|                    | P2B <sup>(2)</sup>   | 0               |               | 0           | DIG              | Enhanced CCP2 PWM output 2.                                 |

|                    | T3CKI <sup>(1)</sup> | 1               | _             | I           | ST               | Timer3 clock input.                                         |

|                    | T3G                  | 1               |               | I           | ST               | Timer3 external clock gate input.                           |

|                    | T1CKI                | 1               |               | I           | ST               | Timer1 clock input.                                         |

|                    | SOSCO                | x               |               | 0           | XTAL             | Secondary oscillator output.                                |

| RC1/P2A/CCP2/SOSCI | RC1                  | 0               |               | 0           | DIG              | LATC<1> data output; not affected by analog input.          |

|                    |                      | 1               | _             | I           | ST               | PORTC<1> data input; disabled when analog input enabled.    |

|                    | P2A                  | 0               |               | 0           | DIG              | Enhanced CCP2 PWM output 1.                                 |

|                    | CCP2 <sup>(1)</sup>  | 0               |               | 0           | DIG              | Compare 2 output/PWM 2 output.                              |

|                    |                      | 1               |               | I           | ST               | Capture 2 input.                                            |

|                    | SOSCI                | х               |               | I           | XTAL             | Secondary oscillator input.                                 |

| RC2/CTPLS/P1A/     | RC2                  | 0               | 0             | 0           | DIG              | LATC<2> data output; not affected by analog input.          |

| CCP1/T5CKI/AN14    |                      | 1               | 0             | I           | ST               | PORTC<2> data input; disabled when analog input<br>enabled. |

|                    | CTPLS                | 0               | 0             | 0           | DIG              | CTMU pulse generator output.                                |

|                    | P1A                  | 0               | 0             | 0           | DIG              | Enhanced CCP1 PWM output 1.                                 |

|                    | CCP1                 | 0               | 0             | 0           | DIG              | Compare 1 output/PWM 1 output.                              |

|                    |                      | 1               | 0             | I           | ST               | Capture 1 input.                                            |

|                    | T5CKI                | 1               | 0             | I           | ST               | Timer5 clock input.                                         |

|                    | AN14                 | 1               | 1             | I           | AN               | Analog input 14.                                            |

| RC3/SCK1/SCL1/AN15 | RC3                  | 0               | 0             | 0           | DIG              | LATC<3> data output; not affected by analog input.          |

|                    |                      | 1               | 0             | I           | ST               | PORTC<3> data input; disabled when analog input<br>enabled. |

|                    | SCK1                 | 0               | 0             | 0           | DIG              | MSSP1 SPI Clock output.                                     |

|                    |                      | 1               | 0             | I           | ST               | MSSP1 SPI Clock input.                                      |

|                    | SCL1                 | 0               | 0             | 0           | DIG              | MSSP1 I <sup>2</sup> C Clock output.                        |

|                    |                      | 1               | 0             | I           | l <sup>2</sup> C | MSSP1 I <sup>2</sup> C Clock input.                         |

|                    | AN15                 | 1               | 1             | I           | AN               | Analog input 15.                                            |

| RC4/SDI1/SDA1/AN16 | RC4                  | 0               | 0             | 0           | DIG              | LATC<4> data output; not affected by analog input.          |

|                    |                      | 1               | 0             | I           | ST               | PORTC<4> data input; disabled when analog input<br>enabled. |

|                    | SDI1                 | 1               | 0             | I           | ST               | MSSP1 SPI data input.                                       |

|                    | SDA1                 | 0               | 0             | 0           | DIG              | MSSP1 I <sup>2</sup> C data output.                         |

|                    |                      | 1               | 0             | Ι           | l <sup>2</sup> C | MSSP1 I <sup>2</sup> C data input.                          |

|                    | AN16                 | 1               | 1             | I           | AN               | Analog input 16.                                            |

**Legend:** AN = Analog input or output; TTL = TTL compatible input;  $HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; <math>I^2C = Schmitt Trigger input with I^2C$ .

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

3: Function on PORTD and PORTE for PIC18(L)F4XK22 devices.

#### 12.1 Timer1/3/5 Operation

The Timer1/3/5 module is a 16-bit incrementing counter which is accessed through the TMRxH:TMRxL register pair. Writes to TMRxH or TMRxL directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1/3/5 is enabled by configuring the TMRxON and TMRxGE bits in the TxCON and TxGCON registers, respectively. Table 12-1 displays the Timer1/3/5 enable selections.

### TABLE 12-1:TIMER1/3/5 ENABLESELECTIONS

| TMRXON | TMRxGE | Timer1/3/5<br>Operation |

|--------|--------|-------------------------|

| 0      | 0      | Off                     |

| 0      | 1      | Off                     |

| 1      | 0      | Always On               |

| 1      | 1      | Count Enabled           |

#### 12.2 Clock Source Selection

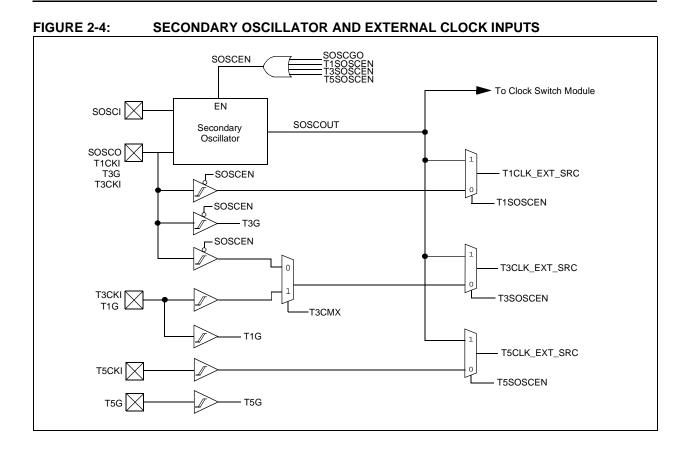

The TMRxCS<1:0> and TxSOSCEN bits of the TxCON register are used to select the clock source for Timer1/3/5. The dedicated Secondary Oscillator circuit can be used as the clock source for Timer1, Timer3 and Timer5, simultaneously. Any of the TxSOSCEN bits will enable the Secondary Oscillator circuit and select it as the clock source for that particular timer. Table 12-2 displays the clock source selections.

#### 12.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMRxH:TMRxL register pair will increment on multiples of Fosc as determined by the Timer1/3/5 prescaler.

When the Fosc internal clock source is selected, the Timer1/3/5 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1/3/5 value. To utilize the full resolution of Timer1/3/5, an asynchronous input signal must be used to gate the Timer1/3/5 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the TxG pin to Timer1/3/5 Gate

- C1 or C2 comparator input to Timer1/3/5 Gate

#### 12.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1/3/5 module may work as a timer or a counter.

When enabled to count, Timer1/3/5 is incremented on the rising edge of the external clock input of the TxCKI pin. This external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated secondary internal oscillator circuit.

| In Counter mode, a falling edge must be      |

|----------------------------------------------|

| registered by the counter prior to the first |

| incrementing rising edge after any one or    |

| more of the following conditions:            |

|                                              |

- Timer1/3/5 enabled after POR

- Write to TMRxH or TMRxL

- Timer1/3/5 is disabled

- Timer1/3/5 is disabled (TMRxON = 0) when TxCKI is high then Timer1/3/5 is enabled (TMRxON=1) when TxCKI is low.

| TMRxCS1 | TMRxCS0 | TxSOSCEN | Clock Source                    |

|---------|---------|----------|---------------------------------|

| 0       | 1       | х        | System Clock (FOSC)             |

| 0       | 0       | х        | Instruction Clock (Fosc/4)      |

| 1       | 0       | 0        | External Clocking on TxCKI Pin  |

| 1       | 0       | 1        | Osc.Circuit On SOSCI/SOSCO Pins |

#### TABLE 12-2: CLOCK SOURCE SELECTIONS

#### 14.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is selected (CCPxM<3:0> = 1011), and a match of the TMRxH:TMRxL and the CCPRxH:CCPRxL registers occurs, all CCPx and ECCPx modules will immediately:

- Set the CCP interrupt flag bit CCPxIF

- CCP5 will start an ADC conversion, if the ADC is enabled

On the next TimerX rising clock edge:

• A Reset of TimerX register pair occurs – TMRxH:TMRxL = 0x0000,

This Special Event Trigger mode does not:

- Assert control over the CCPx or ECCPx pins.

- Set the TMRxIF interrupt bit when the TMRxH:TMRxL register pair is reset. (TMRxIF gets set on a TimerX overflow.)

If the value of the CCPRxH:CCPRxL registers are modified when a match occurs, the user should be aware that the automatic reset of TimerX occurs on the next rising edge of the clock. Therefore, modifying the CCPRxH:CCPRxL registers before this reset occurs will allow the TimerX to continue without being reset, inadvertently resulting in the next event being advanced or delayed.

The Special Event Trigger mode allows the CCPRxH:CCPRxL register pair to effectively provide a 16-bit programmable period register for TimerX.

#### Register Bit 4 Name Bit 7 Bit 6 Bit 5 Bit 3 Bit 2 Bit 1 Bit 0 on Page CCP1CON P1M<1:0> DC1B<1.0>CCP1M<3:0> 198 P2M<1:0> CCP2CON DC2B<1.0> CCP2M<3:0> 198 CCP3CON P3M<1:0> DC3B<1:0> CCP3M<3:0> 198 CCP4CON DC4B<1:0> CCP4M<3:0> 198 CCP5CON CCP5M<3:0> DC5B<1:0> 198 CCPR1H Capture/Compare/PWM Register 1 High Byte (MSB) CCPR1L Capture/Compare/PWM Register 1 Low Byte (LSB) CCPR2H Capture/Compare/PWM Register 2 High Byte (MSB) \_\_\_\_ CCPR2L Capture/Compare/PWM Register 2 Low Byte (LSB) \_ CCPR3H Capture/Compare/PWM Register 3 High Byte (MSB) \_ CCPR3L Capture/Compare/PWM Register 3 Low Byte (LSB) CCPR4H Capture/Compare/PWM Register 4 High Byte (MSB) \_\_\_\_ CCPR4L Capture/Compare/PWM Register 4 Low Byte (LSB) CCPR5H Capture/Compare/PWM Register 5 High Byte (MSB) \_\_\_\_ CCPR5L Capture/Compare/PWM Register 5 Low Byte (LSB) CCPTMRS0 C3TSEL<1:0> C2TSEL<1:0> C1TSEL<1:0> \_\_\_\_\_ 201 CCPTMRS1 C5TSEL<1:0> C4TSEL<1:0> 201 INTCON RBIE TMR0IF **INTOIF GIE/GIEH** PEIE/GIEL TMR0IE **INTOIE** RBIF 109 IPR1 ADIP RC1IP TX1IP SSP1IP CCP1IP TMR2IP TMR1IP 121

#### TABLE 14-5: REGISTERS ASSOCIATED WITH COMPARE

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Compare mode.

Note 1: These registers/bits are available on PIC18(L)F4XK22 devices.

#### 14.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

#### 15.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCKx. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCKx pin. The Idle state is determined by the CKP bit of the SSPxCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCKx pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCKx pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake up from Sleep.

#### 15.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisychain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisychain feature only requires a single Slave Select line from the master device.

Figure 15-7 shows the block diagram of a typical daisy-chain connection when operating in SPI Mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPxCON3 register will enable writes to the SSPxBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

#### 15.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission (Figure 15-8).

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SSx}$  pin control enabled (SSPxCON1<3:0> = 0100).

When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the SDOx pin is driven.

When the  $\overline{SSx}$  pin goes high, the SDOx pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

- Note 1: When the SPI is in Slave mode with SSx pin control enabled (SSPxCON1<3:0> = 0100), the SPI module will reset if the SSx pin is set to VDD.

- 2: When the SPI is used in Slave mode with CKE set; the user must enable SSx pin control.

- **3:** While operated in SPI Slave mode the SMP bit of the SSPxSTAT register must remain clear.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SSx pin to a high level or clearing the SSPxEN bit.

#### 23.7 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

#### 23.8 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| HLVDCON | VDIRMAG  | BGVST     | IRVST  | HLVDEN |        | HLVDI  | _<3:0> |        | 337                        |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 109                        |

| IPR2    | OSCFIP   | C1IP      | C2IP   | EEIP   | BCL1IP | HLVDIP | TMR3IP | CCP2IP | 122                        |

| PIE2    | OSCFIE   | C1IE      | C2IE   | EEIE   | BCL1IE | HLVDIE | TMR3IE | CCP2IE | 118                        |

| PIR2    | OSCFIF   | C1IF      | C2IF   | EEIF   | BCL1IF | HLVDIF | TMR3IF | CCP2IF | 113                        |

| TRISA   | TRISA7   | TRISA6    | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 151                        |

#### TABLE 23-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are unused by the HLVD module.

| DEV<10:3> | DEV<2:0> | Part Number  |

|-----------|----------|--------------|

|           | 000      | PIC18F46K22  |

| 0101 0100 | 001      | PIC18LF46K22 |

| 0101 0100 | 010      | PIC18F26K22  |

|           | 011      | PIC18LF26K22 |

|           | 000      | PIC18F45K22  |

| 0101 0101 | 001      | PIC18LF45K22 |

|           | 010      | PIC18F25K22  |

|           | 011      | PIC18LF25K22 |

|           | 000      | PIC18F44K22  |

| 0101 0110 | 001      | PIC18LF44K22 |

| 0101 0110 | 010      | PIC18F24K22  |

|           | 011      | PIC18LF24K22 |

|           | 000      | PIC18F43K22  |

| 0101 0111 | 001      | PIC18LF43K22 |

| 0101 0111 | 010      | PIC18F23K22  |

|           | 011      | PIC18LF23K22 |

TABLE 24-2: DEVICE ID TABLE FOR THE PIC18(L)F2X/4XK22 FAMILY

# PIC18(L)F2X/4XK22

| CPFSGT               | Compare                           | f with W, sk                         | ip if f > W     |  |  |  |  |

|----------------------|-----------------------------------|--------------------------------------|-----------------|--|--|--|--|

| Syntax:              | CPFSGT                            | f {,a}                               |                 |  |  |  |  |

| Operands:            | 0 ≤ f ≤ 255                       | () - y                               |                 |  |  |  |  |

| oporaliaol           | a ∈ [0,1]                         |                                      |                 |  |  |  |  |

| Operation:           | (f) – (W),                        |                                      |                 |  |  |  |  |

|                      | skip if (f) > (                   |                                      |                 |  |  |  |  |

|                      | (unsigned c                       | omparison)                           |                 |  |  |  |  |

| Status Affected:     | None                              | None                                 |                 |  |  |  |  |

| Encoding:            | 0110                              | 010a fff                             | f fff           |  |  |  |  |

| Description:         | Compares t                        | he contents of                       | data memory     |  |  |  |  |

|                      |                                   | o the contents                       |                 |  |  |  |  |

|                      | 1 0                               | an unsigned s                        |                 |  |  |  |  |

|                      |                                   | nts of 'f' are gre                   |                 |  |  |  |  |

|                      |                                   | WREG, then t<br>s discarded ar       |                 |  |  |  |  |

|                      |                                   | stead, making                        |                 |  |  |  |  |

|                      | 2-cycle inst                      |                                      |                 |  |  |  |  |

|                      | lf 'a' is '0', tl                 | he Access Bar                        | nk is selected. |  |  |  |  |

|                      | ,                                 | he BSR is used                       | d to select the |  |  |  |  |

|                      | GPR bank.                         | nd the extende                       | dinstruction    |  |  |  |  |

|                      |                                   | ed, this instruc                     |                 |  |  |  |  |

|                      |                                   | _iteral Offset A                     | •               |  |  |  |  |

|                      |                                   | ever f ≤ 95 (5F                      |                 |  |  |  |  |

|                      |                                   | .2.3 "Byte-Ori                       |                 |  |  |  |  |

|                      |                                   | Bit-Oriented Instructions in Indexed |                 |  |  |  |  |

|                      | Literal Offset Mode" for details. |                                      |                 |  |  |  |  |

| Words:               | 1                                 |                                      |                 |  |  |  |  |

| Cycles:              | 1(2)                              |                                      | l felleure d    |  |  |  |  |

|                      | •                                 | cles if skip and<br>2-word instrue   |                 |  |  |  |  |

| Q Cycle Activity:    | by a                              |                                      |                 |  |  |  |  |

| Q1                   | Q2                                | Q3                                   | Q4              |  |  |  |  |

| Decode               | Read                              | Process                              | No              |  |  |  |  |

| Decoud               | register 'f'                      | Data                                 | operation       |  |  |  |  |

| lf skip:             | 0                                 |                                      |                 |  |  |  |  |

| Q1                   | Q2                                | Q3                                   | Q4              |  |  |  |  |

| No                   | No                                | No                                   | No              |  |  |  |  |

| operation            | operation                         | operation                            | operation       |  |  |  |  |

| If skip and followed |                                   |                                      |                 |  |  |  |  |

| Q1                   | Q2                                | Q3                                   | Q4              |  |  |  |  |

| No                   | No                                | No                                   | No              |  |  |  |  |

| operation<br>No      | operation<br>No                   | operation<br>No                      | operation<br>No |  |  |  |  |

| operation            | operation                         | operation                            | operation       |  |  |  |  |

|                      |                                   |                                      |                 |  |  |  |  |

| Example:             | HERE                              | CPFSGT RE                            | G, 0            |  |  |  |  |

|                      | NGREATER                          | :                                    |                 |  |  |  |  |

|                      | GREATER                           | :                                    |                 |  |  |  |  |

| Before Instruc       |                                   |                                      |                 |  |  |  |  |

| PC                   |                                   | dress (HERE)                         | )               |  |  |  |  |

| W                    | = ?                               |                                      |                 |  |  |  |  |

| After Instruction    |                                   |                                      |                 |  |  |  |  |

| If REG               | > W;                              |                                      |                 |  |  |  |  |

| PC<br>If REG         | = Ad                              | dress (GREAT                         | LEK)            |  |  |  |  |

| CPFSLT                                                                    | Compare                                                                                                                            | f with W, s                                                                                                                     |                                                        |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Syntax:                                                                   | CPFSLT f                                                                                                                           | {,a}                                                                                                                            |                                                        |

| Operands:                                                                 | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                           |                                                                                                                                 |                                                        |

| Operation:                                                                | (f) – (W),<br>skip if (f) < (<br>(unsigned c                                                                                       | · ·                                                                                                                             |                                                        |

| Status Affected:                                                          | None                                                                                                                               | . ,                                                                                                                             |                                                        |

| Encoding:                                                                 | 0110                                                                                                                               | 000a ff                                                                                                                         | ff ffff                                                |

| Description:                                                              | location 'f' t<br>performing<br>If the conten<br>contents of<br>instruction i<br>executed in<br>2-cycle instr<br>If 'a' is '0', tl | o the content<br>an unsigned<br>nts of 'f' are le<br>W, then the f<br>s discarded a<br>stead, makin<br>ruction.<br>ne Access Ba | subtraction.<br>ess than the<br>etched<br>and a NOP is |

| Words:                                                                    | 1                                                                                                                                  |                                                                                                                                 |                                                        |

| Cycles:                                                                   |                                                                                                                                    | ycles if skip a<br>a 2-word inst                                                                                                |                                                        |

| Q Cycle Activity:                                                         |                                                                                                                                    |                                                                                                                                 |                                                        |

| Q1                                                                        | Q2                                                                                                                                 | Q3                                                                                                                              | Q4                                                     |

| Decode                                                                    | Read<br>register 'f'                                                                                                               | Process<br>Data                                                                                                                 | No<br>operation                                        |

| If skip:                                                                  | register i                                                                                                                         | Dala                                                                                                                            | operation                                              |

| Q1                                                                        | Q2                                                                                                                                 | Q3                                                                                                                              | Q4                                                     |

| No                                                                        | No                                                                                                                                 | No                                                                                                                              | No                                                     |

| operation                                                                 | operation                                                                                                                          | operation                                                                                                                       | operation                                              |

| If skip and followed                                                      | d by 2-word in                                                                                                                     | struction:                                                                                                                      |                                                        |

| Q1                                                                        | Q2                                                                                                                                 | Q3                                                                                                                              | Q4                                                     |

| No                                                                        | No                                                                                                                                 | No                                                                                                                              | No                                                     |