Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 30x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf44k22-e-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

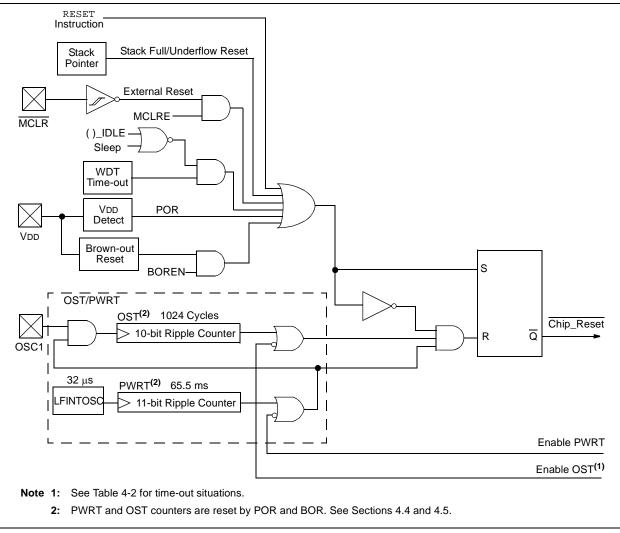

# 4.0 RESET

The PIC18(L)F2X/4XK22 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR and covers the operation of the various start-up timers. Stack Reset events are covered in Section 5.2.0.1 "Stack Full and Underflow Resets". WDT Resets are covered in Section 24.3 "Watchdog Timer (WDT)". A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 4-1.

# 4.1 RCON Register

Device Reset events are tracked through the RCON register (Register 4-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be cleared by the event and must be set by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 4.7 "Reset State of Registers"**.

The RCON register also has control bits for setting interrupt priority (IPEN) and software control of the BOR (SBOREN). Interrupt priority is discussed in Section 9.0 "Interrupts". BOR is covered in Section 4.5 "Brown-out Reset (BOR)".

### 6.3.1 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 6.3.2 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the device ID, the user ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations on the TBLPTR affect only the low-order 21 bits.

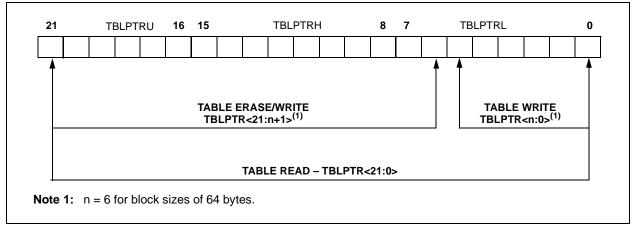

#### 6.3.3 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory directly into the TABLAT register.

When a TBLWT is executed the byte in the TABLAT register is written, not to Flash memory but, to a holding register in preparation for a program memory write. The holding registers constitute a write block which varies depending on the device (see Table 6-1). The 3, 4, or 5 LSbs of the TBLPTRL register determine which specific address within the holding register block is written to. The MSBs of the Table Pointer have no effect during TBLWT operations.

When a program memory write is executed the entire holding register block is written to the Flash memory at the address determined by the MSbs of the TBLPTR. The 3, 4, or 5 LSBs are ignored during Flash memory writes. For more detail, see **Section 6.6** "**Writing to Flash Program Memory**".

When an erase of program memory is executed, the 16 MSbs of the Table Pointer register (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 6-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

# TABLE 6-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

#### FIGURE 6-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

| R/W-0                                                                                                                                    | R/W-0                                                                                                                                  | R/W-0                               | R/W-0           | R/W-0            | R/W-0            | R/W-0            | R/W-0       |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|------------------|------------------|------------------|-------------|

| OSCFIF                                                                                                                                   | C1IF                                                                                                                                   | C2IF                                | EEIF            | BCL1IF           | HLVDIF           | TMR3IF           | CCP2IF      |

| bit 7                                                                                                                                    |                                                                                                                                        |                                     |                 |                  |                  |                  | bit 0       |

|                                                                                                                                          |                                                                                                                                        |                                     |                 |                  |                  |                  |             |

| Legend:                                                                                                                                  |                                                                                                                                        |                                     |                 |                  |                  |                  |             |

| R = Readable                                                                                                                             |                                                                                                                                        | W = Writable                        |                 | -                | mented bit, read |                  |             |

| -n = Value at                                                                                                                            | POR                                                                                                                                    | '1' = Bit is set                    |                 | '0' = Bit is cle | ared             | x = Bit is unk   | nown        |

| bit 7                                                                                                                                    | OSCFIF: Os                                                                                                                             | cillator Fail Inte                  | rrupt Flag bit  |                  |                  |                  |             |

|                                                                                                                                          |                                                                                                                                        | oscillator failed,                  |                 | as changed to I  | HFINTOSC (mu     | ust be cleared b | y software) |

|                                                                                                                                          |                                                                                                                                        | clock operating                     |                 | 0                | × ×              |                  |             |

| bit 6                                                                                                                                    | C1IF: Compa                                                                                                                            | arator C1 Interr                    | upt Flag bit    |                  |                  |                  |             |

|                                                                                                                                          |                                                                                                                                        | ator C1 output                      |                 |                  | ed by software)  |                  |             |

|                                                                                                                                          | -                                                                                                                                      | ator C1 output                      | -               | led              |                  |                  |             |

| bit 5                                                                                                                                    | •                                                                                                                                      | arator C2 Interr                    |                 |                  |                  |                  |             |

|                                                                                                                                          |                                                                                                                                        | ator C2 output  <br>ator C2 output  |                 |                  | ed by software)  |                  |             |

| bit 4                                                                                                                                    | -                                                                                                                                      | •                                   |                 |                  | a hit            |                  |             |

| DIL 4                                                                                                                                    | <b>EEIF:</b> Data EEPROM/Flash Write Operation Interrupt Flag bit<br>1 = The write operation is complete (must be cleared by software) |                                     |                 |                  |                  |                  |             |

| 1 = The write operation is not complete (must be cleared by software)<br>0 = The write operation is not complete or has not been started |                                                                                                                                        |                                     |                 |                  |                  |                  |             |

| bit 3                                                                                                                                    |                                                                                                                                        | SP1 Bus Collis                      | •               |                  |                  |                  |             |

|                                                                                                                                          |                                                                                                                                        | ollision occurred                   | -               | -                | re)              |                  |             |

|                                                                                                                                          | 0 = No bus                                                                                                                             | collision occurre                   | ed              |                  |                  |                  |             |

| bit 2                                                                                                                                    | HLVDIF: Low                                                                                                                            | w-Voltage Deteo                     | t Interrupt Fla | ıg bit           |                  |                  |             |

|                                                                                                                                          |                                                                                                                                        | oltage condition                    | occurred (dire  | ection determin  | ed by the VDIF   | RMAG bit of the  |             |

|                                                                                                                                          |                                                                                                                                        | ON register)<br>oltage condition    | haa not aaau    | rrad             |                  |                  |             |

| bit 1                                                                                                                                    |                                                                                                                                        | 0                                   |                 |                  |                  |                  |             |

|                                                                                                                                          |                                                                                                                                        | IR3 Overflow In<br>egister overflow | 1 0             |                  | (are)            |                  |             |

|                                                                                                                                          |                                                                                                                                        | egister did not c                   |                 | leared by solu   | vale)            |                  |             |

| bit 0                                                                                                                                    |                                                                                                                                        | P2 Interrupt Fla                    |                 |                  |                  |                  |             |

|                                                                                                                                          | Capture mod                                                                                                                            | -                                   | 0               |                  |                  |                  |             |

|                                                                                                                                          |                                                                                                                                        | register capture                    |                 | ist be cleared b | oy software)     |                  |             |

|                                                                                                                                          |                                                                                                                                        | R register captur                   | e occurred      |                  |                  |                  |             |

|                                                                                                                                          | Compare mo                                                                                                                             |                                     | a matab agai    | mad (must be a   | leared by coffy  | (070)            |             |

|                                                                                                                                          |                                                                                                                                        | register compar<br>R register compa |                 |                  | leared by solu   | /are)            |             |

|                                                                                                                                          | PWM mode:                                                                                                                              | •                                   |                 |                  |                  |                  |             |

|                                                                                                                                          |                                                                                                                                        |                                     |                 |                  |                  |                  |             |

# REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

|                                         |              |                  |          |                  | · ·              |                 |        |

|-----------------------------------------|--------------|------------------|----------|------------------|------------------|-----------------|--------|

| U-0                                     | U-0          | U-0              | U-0      | U-0              | R/W-0            | R/W-0           | R/W-0  |

|                                         | —            | —                | —        | —                | CCP5IE           | CCP4IE          | CCP3IE |

| bit 7 bit 0                             |              |                  |          |                  |                  |                 |        |

|                                         |              |                  |          |                  |                  |                 |        |

| Legend:                                 |              |                  |          |                  |                  |                 |        |

| R = Readable                            | bit          | W = Writable     | bit      | U = Unimpler     | mented bit, read | as '0'          |        |

| -n = Value at I                         | POR          | '1' = Bit is set |          | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|                                         |              |                  |          |                  |                  |                 |        |

| bit 7-3                                 | Unimplemen   | ted: Read as '   | 0'       |                  |                  |                 |        |

| bit 2                                   | CCP5IE: CCF  | P5 Interrupt En  | able bit |                  |                  |                 |        |

|                                         | 1 = Enabled  |                  |          |                  |                  |                 |        |

|                                         | 0 = Disabled |                  |          |                  |                  |                 |        |

| bit 1                                   | CCP4IE: CCF  | P4 Interrupt En  | able bit |                  |                  |                 |        |

| 1 = Enabled                             |              |                  |          |                  |                  |                 |        |

|                                         | 0 = Disabled |                  |          |                  |                  |                 |        |

| bit 0 CCP3IE: CCP3 Interrupt Enable bit |              |                  |          |                  |                  |                 |        |

|                                         | 1 = Enabled  |                  |          |                  |                  |                 |        |

|                                         | 0 = Disabled |                  |          |                  |                  |                 |        |

|                                         |              |                  |          |                  |                  |                 |        |

|                                         |              |                  |          |                  |                  |                 |        |

#### REGISTER 9-12: PIE4: PERIPHERAL INTERRUPT ENABLE (FLAG) REGISTER 4

# REGISTER 9-13: PIE5: PERIPHERAL INTERRUPT ENABLE (FLAG) REGISTER 5

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| —     | —   | —   | —   | —   | TMR6IE | TMR5IE | TMR4IE |

| bit 7 |     |     |     |     |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-3 | Unimplemented: Read as '0'                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| bit 2   | TMR6IE: TMR6 to PR6 Match Interrupt Enable bit                                                                        |

|         | <ul> <li>1 = Enables the TMR6 to PR6 match interrupt</li> <li>0 = Disables the TMR6 to PR6 match interrupt</li> </ul> |

| bit 1   | TMR5IE: TMR5 Overflow Interrupt Enable bit                                                                            |

|         | <ul><li>1 = Enables the TMR5 overflow interrupt</li><li>0 = Disables the TMR5 overflow interrupt</li></ul>            |

| bit 0   | TMR4IE: TMR4 to PR4 Match Interrupt Enable bit                                                                        |

|         | <ul> <li>1 = Enables the TMR4 to PR4 match interrupt</li> <li>0 = Disables the TMR4 to PR4 match interrupt</li> </ul> |

### 10.6 PORTE Registers

Depending on the particular PIC18(L)F2X/4XK22 device selected, PORTE is implemented in two different ways.

#### 10.6.1 PORTE ON 40/44-PIN DEVICES

For PIC18(L)F2X/4XK22 devices, PORTE is a 4-bit wide port. Three pins (RE0/P3A/CCP3/AN5, RE1/P3B/ AN6 and RE2/CCP5/AN7) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's.

The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., disable the output driver). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

TRISE controls the direction of the REx pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

Note: On a Power-on Reset, RE<2:0> are configured as analog inputs.

The fourth pin of PORTE ( $\overline{\text{MCLR}}/\text{VPP}/\text{RE3}$ ) is an input only pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin (MCLRE = 0), it functions as a digital input only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming.

**Note:** On a Power-on Reset, RE3 is enabled as a digital input only if Master Clear functionality is disabled.

#### EXAMPLE 10-5: INITIALIZING PORTE

| CLRF  | PORTE  | ; | Initialize PORTE by   |

|-------|--------|---|-----------------------|

|       |        | ; | clearing output       |

|       |        | ; | data latches          |

| CLRF  | LATE   | ; | Alternate method      |

|       |        | ; | to clear output       |

|       |        | ; | data latches          |

| CLRF  | ANSELE | ; | Configure analog pins |

|       |        | ; | for digital only      |

| MOVLW | 05h    | ; | Value used to         |

|       |        | ; | initialize data       |

|       |        | ; | direction             |

| MOVWF | TRISE  | ; | Set RE<0> as input    |

|       |        | ; | RE<1> as output       |

|       |        | ; | RE<2> as input        |

| 1     |        |   |                       |

# 10.6.2 PORTE ON 28-PIN DEVICES

For PIC18F2XK22 devices, PORTE is only available when Master Clear functionality is disabled (MCLR = 0). In these cases, PORTE is a single bit, input only port comprised of RE3 only. The pin operates as previously described.

### 10.6.3 RE3 WEAK PULL-UP

The port RE3 pin has an individually controlled weak internal pull-up. When set, the WPUE3 (TRISE<7>) bit enables the RE3 pin pull-up. The RBPU bit of the INT-CON2 register controls pull-ups on both PORTB and PORTE. When RBPU = 0, the weak pull-ups become active on all pins which have the WPUE3 or WPUBx bits set. When set, the RBPU bit disables all weak pull-ups. The pull-ups are disabled on a Power-on Reset. When the RE3 port pin is configured as MCLR, (CON-FIG3H<7>, MCLRE=1 and CONFIG4L<2>, LVP=0), or configured for Low Voltage Programming, (MCLRE=x and LVP=1), the pull-up is always enabled and the WPUE3 bit has no effect.

# 10.6.4 PORTE OUTPUT PRIORITY

Each PORTE pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the higher priority. Table 10-4 lists the PORTE pin functions from the highest to the lowest priority.

Analog input functions, such as ADC, comparator and SR latch inputs, are not shown in the priority lists.

These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below.

| REGISTER I       | U-Z. FURI   | C. FURIERI        | EGISTER     |                    |                         |                         |                         |

|------------------|-------------|-------------------|-------------|--------------------|-------------------------|-------------------------|-------------------------|

| U-0              | U-0         | U-0               | U-0         | R/W-u/x            | R/W-u/x                 | R/W-u/x                 | R/W-u/x                 |

| _                | —           | —                 | —           | RE3 <sup>(1)</sup> | RE2 <sup>(2), (3)</sup> | RE1 <sup>(2), (3)</sup> | RE0 <sup>(2), (3)</sup> |

| bit 7            |             |                   |             |                    |                         |                         | bit C                   |

|                  |             |                   |             |                    |                         |                         |                         |

| Legend:          |             |                   |             |                    |                         |                         |                         |

| R = Readable     | bit         | W = Writable      | bit         | U = Unimpler       | mented bit, read        | d as '0'                |                         |

| '1' = Bit is set |             | '0' = Bit is clea | ared        | x = Bit is unk     | nown                    |                         |                         |

| -n/n = Value at  | POR and BOR | R/Value at all o  | ther Resets |                    |                         |                         |                         |

|                  |             |                   |             |                    |                         |                         |                         |

|                  |             |                   |             |                    |                         |                         |                         |

#### REGISTER 10-2: PORTE: PORTE REGISTER

bit 3 **RE3:** PORTE Input bit value<sup>(1)</sup>

bit 2-0 **RE<2:0>:** PORTE I/O bit values<sup>(2), (3)</sup>

**Note 1:** Port is available as input only when MCLRE = 0.

- 2: Writes to PORTx are written to corresponding LATx register. Reads from PORTx register is return of I/O pin values.

- 3: Available on PIC18(L)F4XK22 devices.

### REGISTER 10-3: ANSELA – PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| —     | —   | ANSA5 | —   | ANSA3 | ANSA2 | ANSA1 | ANSA0 |

| bit 7 |     |       |     |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                   |

|---------|----------------------------------------------------------------------------------------------|

| bit 5   | ANSA5: RA5 Analog Select bit                                                                 |

|         | <ul><li>1 = Digital input buffer disabled</li><li>0 = Digital input buffer enabled</li></ul> |

| bit 4   | Unimplemented: Read as '0'                                                                   |

| bit 3-0 | ANSA<3:0>: RA<3:0> Analog Select bit                                                         |

|         | 1 = Digital input buffer disabled                                                            |

0 = Digital input buffer enabled

| U-0 | U-0              | U-0 | U-0              | R/W-1                            | R/W-1                                                                                           | R/W-1                                                                              |

|-----|------------------|-----|------------------|----------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| —   | —                | —   | —                | ANSE2 <sup>(1)</sup>             | ANSE1 <sup>(1)</sup>                                                                            | ANSE0 <sup>(1)</sup>                                                               |

|     |                  |     |                  |                                  |                                                                                                 | bit 0                                                                              |

|     |                  |     |                  |                                  |                                                                                                 |                                                                                    |

|     |                  |     |                  |                                  |                                                                                                 |                                                                                    |

| bit | W = Writable     | bit | U = Unimple      | mented bit, read                 | d as '0'                                                                                        |                                                                                    |

| OR  | '1' = Bit is set |     | '0' = Bit is cle | eared                            | x = Bit is unkr                                                                                 | nown                                                                               |

|     |                  |     |                  | Dit W = Writable bit U = Unimple | —     —     —     ANSE2 <sup>(1)</sup> Dit     W = Writable bit     U = Unimplemented bit, read | $ ANSE2^{(1)} ANSE1^{(1)}$ Dit W = Writable bit U = Unimplemented bit, read as '0' |

#### REGISTER 10-7: ANSELE – PORTE ANALOG SELECT REGISTER

bit 7-3 Unimplemented: Read as '0'

bit 2-0 ANSE<2:0>: RE<2:0> Analog Select bit<sup>(1)</sup>

1 = Digital input buffer disabled

0 = Digital input buffer enabled

**Note 1:** Available on PIC18(L)F4XK22 devices only.

#### REGISTER 10-8: TRISx: PORTx TRI-STATE REGISTER<sup>(1)</sup>

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISx7 | TRISx6 | TRISx5 | TRISx4 | TRISx3 | TRISx2 | TRISx1 | TRISx0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 TRISx<7:0>: PORTx Tri-State Control bit

1 = PORTx pin configured as an input (tri-stated)

0 = PORTx pin configured as an output

**Note 1:** Register description for TRISA, TRISB, TRISC and TRISD.

#### REGISTER 10-9: TRISE: PORTE TRI-STATE REGISTER

| R/W-1 | U-0 | U-0 | U-0 | U-0 | R/W-1                 | R/W-1                 | R/W-1                 |

|-------|-----|-----|-----|-----|-----------------------|-----------------------|-----------------------|

| WPUE3 | —   | —   | —   | —   | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> |

| bit 7 |     |     |     |     |                       |                       | bit 0                 |

| Legend:    |         |                                                   |                       |                    |

|------------|---------|---------------------------------------------------|-----------------------|--------------------|

| R = Reada  | ble bit | W = Writable bit                                  | U = Unimplemented bit | , read as '0'      |

| -n = Value | at POR  | '1' = Bit is set                                  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7      | WPUE3:  | Weak Pull-up Register bits                        |                       |                    |

|            |         | up enabled on PORT pin<br>up disabled on PORT pin |                       |                    |

| 1.11.0.0   |         |                                                   |                       |                    |

bit 6-3 Unimplemented: Read as '0'

bit 2-0 TRISE<7:0>: PORTE Tri-State Control bit<sup>(1)</sup>

1 = PORTE pin configured as an input (tri-stated)

0 = PORTE pin configured as an output

Note 1: Available on PIC18(L)F4XK22 devices only.

© 2010-2016 Microchip Technology Inc.

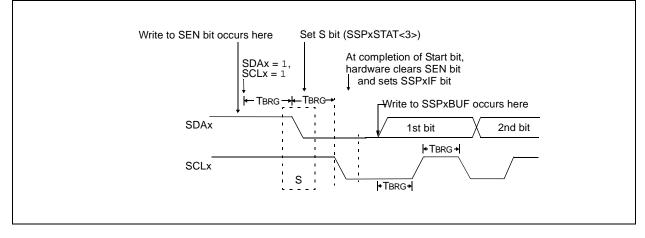

### 15.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition (Figure 15-26), the user sets the Start Enable bit, SEN, of the SSPxCON2 register. If the SDAx and SCLx pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCLx and SDAx are both sampled high when the Baud Rate Generator times out (TBRG), the SDAx pin is driven low. The action of the SDAx being driven low while SCLx is high is the Start condition and causes the S bit of the SSPxSTAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and resumes its count.

When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDAx line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDAx and SCLx pins are already sampled low, or if during the Start condition, the SCLx line is sampled low before the SDAx line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- 2: The Philips I<sup>2</sup>C Specification states that a bus collision cannot occur on a Start.

### FIGURE 15-26: FIRST START BIT TIMING

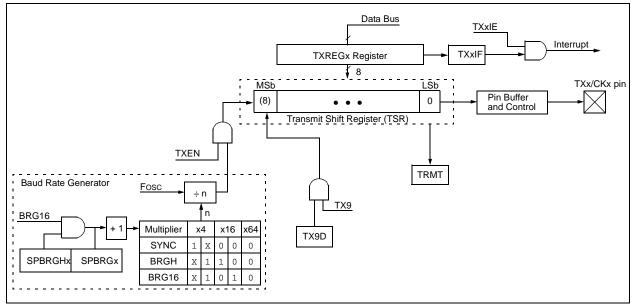

# 16.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- Half-duplex synchronous slave

- · Programmable clock and data polarity

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 16-1 and Figure 16-2.

#### FIGURE 16-1: EUSART TRANSMIT BLOCK DIAGRAM

# 22.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- ADC input channel

- DACOUT pin

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the VREFCON1 register.

# 22.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the VREFCON2 register.

The DAC output voltage is determined by the following equations:

# EQUATION 22-1: DAC OUTPUT VOLTAGE

$$VOUT = \left( (VSRC+ - VSRC-) \neq \frac{DACR < 4:0>}{2^5} \right) + VSRC-$$

$$VSRC+ = VDD, VREF+ or FVR1$$

$$VSRC- = VSS or VREF-$$

# 22.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 27.0** "**Electrical Specifications**".

# 22.3 Low-Power Voltage State

In order for the DAC module to consume the least amount of power, one of the two voltage reference input sources to the resistor ladder must be disconnected. Either the positive voltage source, (VSRC+), or the negative voltage source, (VSRC-) can be disabled. The negative voltage source is disabled by setting the DACLPS bit in the VREFCON1 register. Clearing the DACLPS bit in the VREFCON1 register disables the positive voltage source.

### 22.4 Output Clamped to Positive Voltage Source

The DAC output voltage can be set to VsRC+ with the least amount of power consumption by performing the following:

- Clearing the DACEN bit in the VREFCON1 register.

- Setting the DACLPS bit in the VREFCON1 register.

- Configuring the DACPSS bits to the proper positive source.

- Configuring the DACRx bits to '11111' in the VREFCON2 register.

This is also the method used to output the voltage level from the FVR to an output pin. See **Section 22.6 "DAC Voltage Reference Output"** for more information.

# 22.5 Output Clamped to Negative Voltage Source

The DAC output voltage can be set to VSRC- with the least amount of power consumption by performing the following:

- Clearing the DACEN bit in the VREFCON1 register.

- Clearing the DACLPS bit in the VREFCON1 register.

- Configuring the DACPSS bits to the proper negative source.

- Configuring the DACRx bits to '00000' in the VREFCON2 register.

This allows the comparator to detect a zero-crossing while not consuming additional current through the DAC module.

# 22.6 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the VREFCON1 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 22-2 shows an example buffering technique.

| U-0           | U-0                                                                                                                                                                                       | U-0                                                                                                                                                                                                                | R/P-1                                                                                                     | R/P-1                                   | R/P-1             | R/P-1            | R/P-1                 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------|------------------|-----------------------|

| _             | _                                                                                                                                                                                         | _                                                                                                                                                                                                                  | BORV                                                                                                      | ′<1:0> <sup>(1)</sup>                   | BOREN             | <1:0> <b>(2)</b> | PWRTEN <sup>(2)</sup> |

| bit 7         |                                                                                                                                                                                           |                                                                                                                                                                                                                    |                                                                                                           |                                         |                   |                  | bit                   |

|               |                                                                                                                                                                                           |                                                                                                                                                                                                                    |                                                                                                           |                                         |                   |                  |                       |

| Legend:       | 1.12                                                                                                                                                                                      |                                                                                                                                                                                                                    |                                                                                                           |                                         |                   | <b>0</b> 1       |                       |

| R = Readable  |                                                                                                                                                                                           | P = Programma                                                                                                                                                                                                      | able bit                                                                                                  | •                                       | nted bit, read as | 0'               |                       |

| -n = Value wh | nen device is unprogr                                                                                                                                                                     | ammed                                                                                                                                                                                                              |                                                                                                           | x = Bit is unkno                        | wn                |                  |                       |

|               |                                                                                                                                                                                           |                                                                                                                                                                                                                    |                                                                                                           |                                         |                   |                  |                       |

| bit 7-5       | Unimplementee                                                                                                                                                                             | d: Read as '0'                                                                                                                                                                                                     |                                                                                                           |                                         |                   |                  |                       |

| L 4 4 0       |                                                                                                                                                                                           |                                                                                                                                                                                                                    | / IA I I I (1)                                                                                            |                                         |                   |                  |                       |

| bit 4-3       |                                                                                                                                                                                           | own-out Reset \                                                                                                                                                                                                    | oltage bits                                                                                               |                                         |                   |                  |                       |

| DIT 4-3       | 11 = VBOR set to                                                                                                                                                                          | o 1.9V nominal                                                                                                                                                                                                     | oltage bits(")                                                                                            |                                         |                   |                  |                       |

| dit 4-3       | 11 = VBOR set to<br>10 = VBOR set to                                                                                                                                                      | o 1.9V nominal<br>o 2.2V nominal                                                                                                                                                                                   | oltage bits                                                                                               |                                         |                   |                  |                       |

| dit 4-3       | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to                                                                                                                                  | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal                                                                                                                                                                 | Oltage Dits."                                                                                             |                                         |                   |                  |                       |

|               | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to                                                                                                              | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal                                                                                                                                              | J                                                                                                         |                                         |                   |                  |                       |

|               | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br>BOREN<1:0>: E                                                                                             | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset                                                                                                                           | Enable bits <sup>(2)</sup>                                                                                | / (SBOREN is dis                        | abled)            |                  |                       |

|               | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br>BOREN<1:0>: E<br>11 = Brown-ou                                                                            | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset<br>tt Reset enabled                                                                                                       | Enable bits <sup>(2)</sup><br>in hardware only                                                            | / (SBOREN is dis<br>/ and disabled in { |                   |                  |                       |

|               | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br>BOREN<1:0>: E<br>11 = Brown-ou<br>10 = Brown-ou                                                           | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset<br>tt Reset enabled                                                                                                       | Enable bits <sup>(2)</sup><br>in hardware only                                                            | ۲ (SBOREN is dis<br>۲ and disabled in 5 |                   |                  |                       |

|               | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br><b>BOREN&lt;1:0&gt;:</b> E<br>11 = Brown-ou<br>10 = Brown-ou<br>(SBOREN                                   | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset<br>it Reset enabled<br>t Reset enabled<br>N is disabled)                                                                  | Enable bits <sup>(2)</sup><br>in hardware only<br>in hardware only                                        |                                         | Sleep mode        |                  |                       |

| bit 2-1       | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br><b>BOREN&lt;1:0&gt;:</b> E<br>11 = Brown-ou<br>10 = Brown-ou<br>(SBOREN                                   | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset<br>it Reset enabled<br>it Reset enabled<br>v is disabled)<br>it Reset enabled                                             | Enable bits <sup>(2)</sup><br>in hardware only<br>in hardware only<br>and controlled b                    | y and disabled in S<br>y software (SBOF | Sleep mode        |                  |                       |

|               | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br>BOREN<1:0>: F<br>11 = Brown-ou<br>10 = Brown-ou<br>(SBOREN<br>01 = Brown-ou                               | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset<br>tt Reset enabled<br>tt Reset enabled<br>v is disabled)<br>tt Reset enabled<br>tt Reset disabled                        | Enable bits <sup>(2)</sup><br>in hardware only<br>in hardware only<br>and controlled b<br>in hardware and | y and disabled in S<br>y software (SBOF | Sleep mode        |                  |                       |

| bit 2-1       | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br><b>BOREN&lt;1:0&gt;:</b> F<br>11 = Brown-ou<br>10 = Brown-ou<br>(SBOREN<br>01 = Brown-ou<br>00 = Brown-ou | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset<br>it Reset enabled<br>it Reset enabled<br>v is disabled)<br>it Reset enabled<br>it Reset disabled<br>er-up Timer Enabled | Enable bits <sup>(2)</sup><br>in hardware only<br>in hardware only<br>and controlled b<br>in hardware and | y and disabled in S<br>y software (SBOF | Sleep mode        |                  |                       |

2: The Power-up Timer is decoupled from Brown-out Reset, allowing these features to be independently controlled.

| Mnemo     | nic,                            |                                          |            | 16-  | Bit Instr | uction W | ord  | Status          |            |

|-----------|---------------------------------|------------------------------------------|------------|------|-----------|----------|------|-----------------|------------|

| Operar    | •                               | Description                              | Cycles     | MSb  |           |          | LSb  | Affected        | Notes      |

| BYTE-ORIE | ENTED C                         | OPERATIONS                               |            |      |           |          |      |                 |            |

| ADDWF     | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC    | f, d, a                         | Add WREG and CARRY bit to f              | 1          | 0010 | 00da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF     | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da      | ffff     | ffff | Z, N            | 1,2        |

| CLRF      | f, a                            | Clear f                                  | 1          | 0110 | 101a      | ffff     | ffff | Z               | 2          |

| COMF      | f, d, a                         | Complement f                             | 1          | 0001 | 11da      | ffff     | ffff | Z, N            | 1, 2       |

| CPFSEQ    | f, a                            | Compare f with WREG, skip =              | 1 (2 or 3) | 0110 | 001a      | ffff     | ffff | None            | 4          |

| CPFSGT    | f, a                            | Compare f with WREG, skip >              | 1 (2 or 3) | 0110 | 010a      | ffff     | ffff | None            | 4          |

| CPFSLT    | f, a                            | Compare f with WREG, skip <              | 1 (2 or 3) | 0110 | 000a      | ffff     | ffff | None            | 1, 2       |

| DECF      | f, d, a                         | Decrement f                              | 1          | 0000 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff     | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ    | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da      | ffff     | ffff | None            | 1, 2       |

| INCF      | f, d, a                         | Increment f                              | 1          | 0010 | 10da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff     | ffff | None            | 4          |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da      | ffff     | ffff | None            | 1, 2       |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001 | 00da      | ffff     | ffff | Z, N            | 1, 2       |

| MOVF      | f, d, a                         | Move f                                   | 1          | 0101 | 00da      | ffff     | ffff | Z, N            | 1          |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100 | ffff      | ffff     | ffff | None            |            |

|           | 0 u                             | f <sub>d</sub> (destination) 2nd word    |            | 1111 | ffff      | ffff     | ffff |                 |            |

| MOVWF     | f, a                            | Move WREG to f                           | 1          | 0110 | 111a      | ffff     | ffff | None            |            |

| MULWF     | f, a                            | Multiply WREG with f                     | 1          | 0000 | 001a      | ffff     | ffff | None            | 1, 2       |

| NEGF      | f, a                            | Negate f                                 | 1          | 0110 | 110a      | ffff     | ffff | C, DC, Z, OV, N |            |

| RLCF      | f, d, a                         | Rotate Left f through Carry              | 1          | 0011 | 01da      | ffff     | ffff | C, Z, N         | 1, 2       |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100 | 01da      | ffff     | ffff | Z, N            |            |

| RRCF      | f, d, a                         | Rotate Right f through Carry             | 1          | 0011 | 00da      | ffff     | ffff | C, Z, N         |            |

| RRNCF     | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100 | 00da      | ffff     | ffff | Z, N            |            |

| SETF      | f, a                            | Set f                                    | 1          | 0110 | 100a      | ffff     | ffff | None            | 1, 2       |

| SUBFWB    | f, d, a                         | Subtract f from WREG with<br>borrow      | 1          | 0101 | 01da      | ffff     | ffff | C, DC, Z, OV, N |            |

| SUBWF     | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB    | f, d, a                         | Subtract WREG from f with                | 1          | 0101 | 10da      | ffff     | ffff | C, DC, Z, OV, N | ,          |

|           | , . , .                         | borrow                                   |            |      |           |          | _    | , _, , _ , _    |            |

| SWAPF     | f, d, a                         | Swap nibbles in f                        | 1          | 0011 | 10da      | ffff     | ffff | None            | 4          |

| TSTFSZ    | f, a                            | Test f, skip if 0                        | 1 (2 or 3) | 0110 | 011a      | ffff     | ffff | None            | 1, 2       |

| XORWF     | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001 | 10da      | ffff     | ffff | Z, N            | , _        |

TABLE 25-2: PIC18(L)F2X/4XK22 INSTRUCTION SET

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| LFS         | R                 | Load FSF                                                            | R                                   |                                         | MOVF                          | Move f                                            |                                                              |                                             |

|-------------|-------------------|---------------------------------------------------------------------|-------------------------------------|-----------------------------------------|-------------------------------|---------------------------------------------------|--------------------------------------------------------------|---------------------------------------------|

| Synta       | ax:               | LFSR f, k                                                           |                                     |                                         | Syntax:                       | MOVF f{,                                          | d {,a}}                                                      |                                             |

| Oper        | ands:             | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 409 \end{array}$ | 5                                   |                                         | Operands:                     | $0 \le f \le 255$<br>$d \in [0,1]$                |                                                              |                                             |

| Oper        | ation:            | $k\toFSRf$                                                          |                                     |                                         |                               | a ∈ [0,1]                                         |                                                              |                                             |

| Statu       | s Affected:       | None                                                                |                                     |                                         | Operation:                    | $f \rightarrow dest$                              |                                                              |                                             |

| Enco        | ding:             | 1110<br>1111                                                        | 1110 00<br>0000 k <sub>7</sub> }    | 11                                      | Status Affected:<br>Encoding: | N, Z                                              | 00da ff                                                      | ff ffff                                     |

| Desc        | ription:          |                                                                     | literal 'k' is loa<br>Register poin |                                         | Description:                  | a destinatio                                      | n dependent                                                  | •                                           |

| Word        | ls:               | 2                                                                   |                                     |                                         |                               |                                                   | . If 'd' is '0', th<br>′. If 'd' is '1', th                  |                                             |

| Cycle       | es:               | 2                                                                   |                                     |                                         |                               |                                                   | tin register 'f'                                             |                                             |

| QC          | ycle Activity:    |                                                                     |                                     |                                         |                               | Location 'f'                                      | can be anywh                                                 | · ,                                         |

|             | Q1                | Q2                                                                  | Q3                                  | Q4                                      |                               | 256-byte ba                                       |                                                              | nk is selected.                             |

|             | Decode            | Read literal<br>'k' MSB                                             | Process<br>Data                     | Write<br>literal 'k'<br>MSB to<br>FSRfH |                               | lf 'a' is '1', tl<br>GPR bank.<br>If 'a' is '0' a | he BSR is use<br>nd the extend                               | ed instruction<br>ction operates            |

|             | Decode            | Read literal<br>'k' LSB                                             | Process<br>Data                     | Write literal<br>'k' to FSRfL           |                               | in Indexed I<br>mode when<br><b>Section 25</b>    | _iteral Offset A<br>ever f ≤ 95 (5<br>. <b>2.3 "Byte-O</b> r | Addressing<br>Fh). See<br><b>iented and</b> |

| <u>Exan</u> | nple:             | LFSR 2,                                                             | 3ABh                                |                                         |                               |                                                   | d Instruction<br>et Mode" for                                | is in Indexed                               |

|             | After Instruction |                                                                     |                                     |                                         | Words:                        | 1                                                 |                                                              |                                             |

|             | FSR2H<br>FSR2L    | = 03<br>= AE                                                        |                                     |                                         | Cycles:                       | 1                                                 |                                                              |                                             |

|             |                   |                                                                     |                                     |                                         | Q Cycle Activity:             |                                                   |                                                              |                                             |