Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Product Status  Core Processor  Core Size  Speed  Connectivity | Active PIC 8-Bit 48MHz I²C, SPI, UART/USART                                |

|----------------------------------------------------------------|----------------------------------------------------------------------------|

| Core Processor<br>Core Size<br>Speed                           | PIC<br>8-Bit<br>48MHz                                                      |

| Core Size<br>Speed                                             | 8-Bit<br>48MHz                                                             |

| Speed                                                          | 48MHz                                                                      |

| •                                                              |                                                                            |

|                                                                |                                                                            |

| Peripherals                                                    | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O                                                  | 35                                                                         |

| Program Memory Size                                            | 16KB (8K x 16)                                                             |

| Program Memory Type                                            | FLASH                                                                      |

| EEPROM Size                                                    | 256 x 8                                                                    |

| RAM Size                                                       | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd)                                     | 1.8V ~ 3.6V                                                                |

| Data Converters                                                | A/D 30x10b                                                                 |

| Oscillator Type                                                | Internal                                                                   |

| Operating Temperature                                          | -40°C ~ 125°C (TA)                                                         |

| Mounting Type                                                  | Through Hole                                                               |

| Package / Case                                                 | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package                                        | 40-PDIP                                                                    |

| Purchase URL                                                   | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf44k22-e-p |

TABLE 1-3: PIC18(L)F4XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

|      | Pin N | lumber |      | Din Nama              | Pin  | Buffer | Description                                                             |

|------|-------|--------|------|-----------------------|------|--------|-------------------------------------------------------------------------|

| PDIP | TQFP  | QFN    | UQFN | Pin Name              | Туре | Туре   | Description                                                             |

| 18   | 37    | 37     | 33   | RC3/SCK1/SCL1/AN15    |      |        |                                                                         |

|      |       |        |      | RC3                   | I/O  | ST     | Digital I/O.                                                            |

|      |       |        |      | SCK1                  | I/O  | ST     | Synchronous serial clock input/output for SPI mode (MSSP).              |

|      |       |        |      | SCL1                  | I/O  | ST     | Synchronous serial clock input/output for I <sup>2</sup> C mode (MSSP). |

|      |       |        |      | AN15                  | I    | Analog | Analog input 15.                                                        |

| 23   | 42    | 42     | 38   | RC4/SDI1/SDA1/AN16    |      |        |                                                                         |

|      |       |        |      | RC4                   | I/O  | ST     | Digital I/O.                                                            |

|      |       |        |      | SDI1                  | I    | ST     | SPI data in (MSSP).                                                     |

|      |       |        |      | SDA1                  | I/O  | ST     | I <sup>2</sup> C data I/O (MSSP).                                       |

|      |       |        |      | AN16                  | I    | Analog | Analog input 16.                                                        |

| 24   | 43    | 43     | 39   | RC5/SDO1/AN17         |      |        |                                                                         |

|      |       |        |      | RC5                   | I/O  | ST     | Digital I/O.                                                            |

|      |       |        |      | SDO1                  | 0    | _      | SPI data out (MSSP).                                                    |

|      |       |        |      | AN17                  | - 1  | Analog | Analog input 17.                                                        |

| 25   | 44    | 44     | 40   | RC6/TX1/CK1/AN18      |      |        |                                                                         |

|      |       |        |      | RC6                   | I/O  | ST     | Digital I/O.                                                            |

|      |       |        |      | TX1                   | 0    | _      | EUSART asynchronous transmit.                                           |

|      |       |        |      | CK1                   | I/O  | ST     | EUSART synchronous clock (see related RXx/DTx).                         |

|      |       |        |      | AN18                  | - 1  | Analog | Analog input 18.                                                        |

| 26   | 1     | 1      | 1    | RC7/RX1/DT1/AN19      |      |        |                                                                         |

|      |       |        |      | RC7                   | I/O  | ST     | Digital I/O.                                                            |

|      |       |        |      | RX1                   | I    | ST     | EUSART asynchronous receive.                                            |

|      |       |        |      | DT1                   | I/O  | ST     | EUSART synchronous data (see related TXx/CKx).                          |

|      |       |        |      | AN19                  | - 1  | Analog | Analog input 19.                                                        |

| 19   | 38    | 38     | 34   | RD0/SCK2/SCL2/AN20    |      |        |                                                                         |

|      |       |        |      | RD0                   | I/O  | ST     | Digital I/O.                                                            |

|      |       |        |      | SCK2                  | I/O  | ST     | Synchronous serial clock input/output for SPI mode (MSSP).              |

|      |       |        |      | SCL2                  | I/O  | ST     | Synchronous serial clock input/output for I <sup>2</sup> C mode (MSSP). |

|      |       |        |      | AN20                  | I    | Analog | Analog input 20.                                                        |

| 20   | 39    | 39     | 35   | RD1/CCP4/SDI2/SDA2/AN | N21  |        |                                                                         |

|      |       |        |      | RD1                   | I/O  | ST     | Digital I/O.                                                            |

|      |       |        |      | CCP4                  | I/O  | ST     | Capture 4 input/Compare 4 output/PWM 4 output.                          |

|      |       |        |      | SDI2                  | I    | ST     | SPI data in (MSSP).                                                     |

|      |       |        |      | SDA2                  | I/O  | ST     | I <sup>2</sup> C data I/O (MSSP).                                       |

|      |       |        |      | AN21                  | I    | Analog | Analog input 21.                                                        |

**Legend:** TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

2: Alternate pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

Note 1: Default pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

### 3.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by any one of the following:

- · an interrupt

- a Reset

- a Watchdog Time-out

This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 3.2 "Run Modes", Section 3.3 "Sleep Mode" and Section 3.4 "Idle Modes").

#### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode or the Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

The instruction immediately following the SLEEP instruction is executed on all exits by interrupt from Idle or Sleep modes. Code execution then branches to the interrupt vector if the GIE/GIEH bit of the INTCON register is set, otherwise code execution continues without branching (see **Section 9.0 "Interrupts"**).

A fixed delay of interval TCSD following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

#### 3.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 3.2 "Run Modes" and Section 3.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 24.3 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by any one of the following:

- executing a SLEEP instruction

- executing a CLRWDT instruction

- the loss of the currently selected clock source when the Fail-Safe Clock Monitor is enabled

- modifying the IRCF bits in the OSCCON register when the internal oscillator block is the device clock source

#### 3.5.3 EXIT BY RESET

Exiting Sleep and Idle modes by Reset causes code execution to restart at address '0'. See **Section 4.0** "**Reset**" for more details.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator.

# 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC, INTOSC, and INTOSCIO modes). However, a fixed delay of interval Tcsp following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

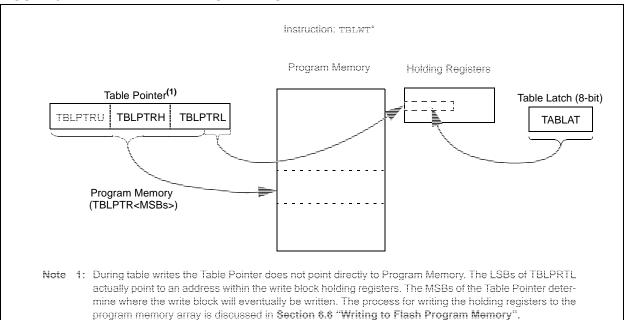

#### FIGURE 6-2: TABLE WRITE OPERATION

# 6.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- · EECON1 register

- EECON2 register

- · TABLAT register

- · TBLPTR registers

### 6.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 6-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When EEPGD is clear, any subsequent operations will operate on the data EEPROM memory. When EEPGD is set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When CFGS is set, subsequent operations will operate on Configuration registers regardless of EEPGD (see Section 24.0 "Special Features of the CPU"). When CFGS is clear, memory selection access is determined by EEPGD.

The FREE bit allows the program memory erase operation. When FREE is set, an erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. The WREN bit is clear on power-up.

The WRERR bit is set by hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

**Note:** During normal operation, the WRERR is read as '1'. This can indicate that a write operation was prematurely terminated by a Reset, or a write operation was attempted improperly.

The WR control bit initiates write operations. The WR bit cannot be cleared, only set, by firmware. Then WR bit is cleared by hardware at the completion of the write operation.

Note: The EEIF interrupt flag bit of the PIR2 register is set when the write is complete. The EEIF flag stays set until cleared by firmware.

#### REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-------|-------|-------|--------|--------|--------|--------|

| OSCFIF | C1IF  | C2IF  | EEIF  | BCL1IF | HLVDIF | TMR3IF | CCP2IF |

| bit 7  |       |       |       |        |        |        | bit 0  |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 7 OSCFIF: Oscillator Fail Interrupt Flag bit

1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by software)

0 = Device clock operating

bit 6 C1IF: Comparator C1 Interrupt Flag bit

1 = Comparator C1 output has changed (must be cleared by software)

0 = Comparator C1 output has not changed

bit 5 C2IF: Comparator C2 Interrupt Flag bit

1 = Comparator C2 output has changed (must be cleared by software)

0 = Comparator C2 output has not changed

bit 4 **EEIF:** Data EEPROM/Flash Write Operation Interrupt Flag bit

1 = The write operation is complete (must be cleared by software)

0 = The write operation is not complete or has not been started

BCL1IF: MSSP1 Bus Collision Interrupt Flag bit

1 = A bus collision occurred (must be cleared by software)

0 = No bus collision occurred

bit 2 **HLVDIF:** Low-Voltage Detect Interrupt Flag bit

1 = A low-voltage condition occurred (direction determined by the VDIRMAG bit of the

**HLVDCON** register)

0 = A low-voltage condition has not occurred

bit 1 **TMR3IF:** TMR3 Overflow Interrupt Flag bit

1 = TMR3 register overflowed (must be cleared by software)

0 = TMR3 register did not overflow

bit 0 CCP2IF: CCP2 Interrupt Flag bit

Capture mode:

bit 3

1 = A TMR register capture occurred (must be cleared by software)

0 = No TMR register capture occurred

Compare mode:

1 = A TMR register compare match occurred (must be cleared by software)

0 = No TMR register compare match occurred

PWM mode:

Unused in this mode.

### REGISTER 10-13: IOCB: INTERRUPT-ON-CHANGE PORTB CONTROL REGISTER

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| IOCB7 | IOCB6 | IOCB5 | IOCB4 | _   | _   | _   | _     |

| bit 7 |       |       |       |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-4 IOCB<7:4>: Interrupt-on-Change PORTB control bits

1 = Interrupt-on-change enabled<sup>(1)</sup>

0 = Interrupt-on-change disabled

Note 1: Interrupt-on-change requires that the RBIE bit (INTCON<3>) is set.

#### REGISTER 10-14: SLRCON: SLEW RATE CONTROL REGISTER

| U-0   | U-0 | U-0 | R/W-1               | R/W-1               | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|---------------------|---------------------|-------|-------|-------|

| _     | _   | _   | SLRE <sup>(1)</sup> | SLRD <sup>(1)</sup> | SLRC  | SLRB  | SLRA  |

| bit 7 |     |     |                     |                     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-5 **Unimplemented:** Read as '0'

bit 4 SLRE: PORTE Slew Rate Control bit<sup>(1)</sup>

1 = All outputs on PORTE slew at a limited rate

0 = All outputs on PORTE slew at the standard rate

bit 3 SLRD: PORTD Slew Rate Control bit<sup>(1)</sup>

1 = All outputs on PORTD slew at a limited rate

0 = All outputs on PORTD slew at the standard rate

bit 2 SLRC: PORTC Slew Rate Control bit

1 = All outputs on PORTC slew at a limited rate

0 = All outputs on PORTC slew at the standard rate

bit 1 SLRB: PORTB Slew Rate Control bit

1 = All outputs on PORTB slew at a limited rate

0 = All outputs on PORTB slew at the standard rate

bit 0 SLRA: PORTA Slew Rate Control bit

1 = All outputs on PORTA slew at a limited rate(2)

0 = All outputs on PORTA slew at the standard rate

Note 1: These bits are available on PIC18(L)F4XK22 devices.

2: The slew rate of RA6 defaults to standard rate when the pin is used as CLKOUT.

# 12.12 Peripheral Module Disable

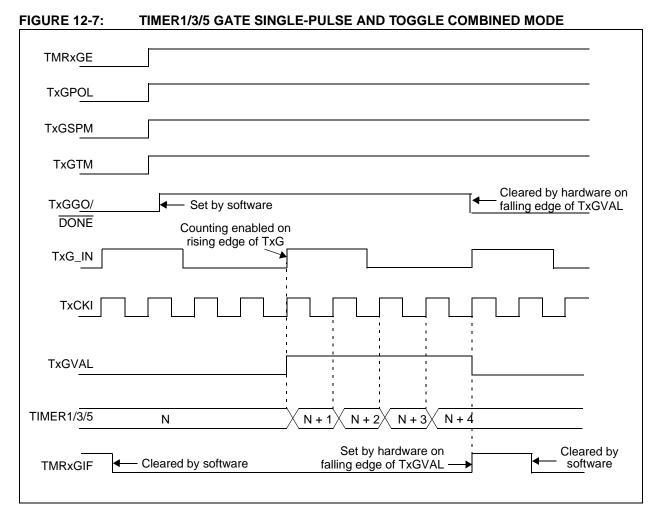

When a peripheral module is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bits for Timer1 (TMR1MD), Timer3 (TMR3MD) and Timer5 (TMR5MD) are in the PMD0 Register. See **Section 3.0** "**Power-Managed Modes**" for more information.

### 13.1 Timer2/4/6 Operation

The clock input to the Timer2/4/6 module is the system instruction clock (Fosc/4).

TMRx increments from 00h on each clock edge.

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, TxCKPS<1:0> of the TxCON register. The value of TMRx is compared to that of the Period register, PRx, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMRx to 00h on the next cycle and drives the output counter/postscaler (see Section 13.2 "Timer2/4/6 Interrupt").

The TMRx and PRx registers are both directly readable and writable. The TMRx register is cleared on any device Reset, whereas the PRx register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMRx register

- · a write to the TxCON register

- Power-on Reset (POR)

- · Brown-out Reset (BOR)

- MCLR Reset

- · Watchdog Timer (WDT) Reset

- · Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

**Note:** TMRx is not cleared when TxCON is written.

### 13.2 Timer2/4/6 Interrupt

Timer2/4/6 can also generate an optional device interrupt. The Timer2/4/6 output signal (TMRx-to-PRx match) provides the input for the 4-bit counter/postscaler. This counter generates the TMRx match interrupt flag which is latched in TMRxIF of the PIR1/PIR5 registers. The interrupt is enabled by setting the TMRx Match Interrupt Enable bit, TMRxIE of the PIE1/PIE5 registers. Interrupt Priority is selected with the TMRxIP bit in the IPR1/IPR5 registers.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, TxOUTPS<3:0>, of the TxCON register.

# 13.3 Timer2/4/6 Output

The unscaled output of TMRx is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode. The timer to be used with a specific CCP module is selected using the CxTSEL<1:0> bits in the CCPTMRS0 and CCPTMRS1 registers.

Timer2 can be optionally used as the shift clock source for the MSSPx modules operating in SPI mode by setting SSPM<3:0> = 0011 in the SSPxCON1 register. Additional information is provided in Section 15.0 "Master Synchronous Serial Port (MSSP1 and MSSP2) Module".

### 13.4 Timer2/4/6 Operation During Sleep

The Timer2/4/6 timers cannot be operated while the processor is in Sleep mode. The contents of the TMRx and PRx registers will remain unchanged while the processor is in Sleep mode.

### 13.5 Peripheral Module Disable

When a peripheral module is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bits for Timer2 (TMR2MD), Timer4 (TMR4MD) and Timer6 (TMR6MD) are in the PMD0 Register. See **Section 3.0** "**Power-Managed Modes**" for more information.

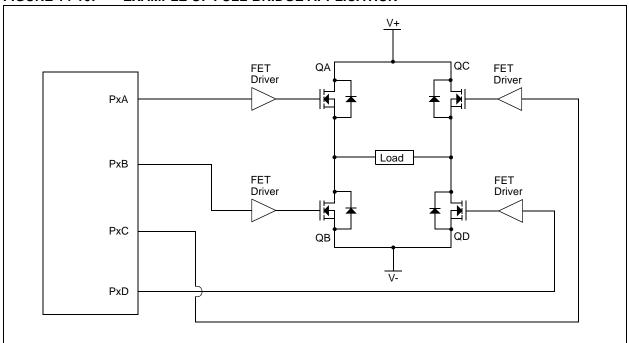

#### 14.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of full-bridge application is shown in Figure 14-10.

In the Forward mode, pin CCPx/PxA is driven to its active state, pin PxD is modulated, while PxB and PxC will be driven to their inactive state as shown in Figure 14-11.

In the Reverse mode, PxC is driven to its active state, pin PxB is modulated, while PxA and PxD will be driven to their inactive state as shown Figure 14-11.

PxA, PxB, PxC and PxD outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the PxA, PxB, PxC and PxD pins as outputs.

FIGURE 14-10: EXAMPLE OF FULL-BRIDGE APPLICATION

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCLx line, is called clock stretching. Clock stretching give slave devices a mechanism to control the flow of data. When this detection is used on the SDAx line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

#### 15.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCLx clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCLx line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCLx connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

#### 15.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDAx data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels don't match, loses arbitration, and must stop transmitting on the SDAx line.

For example, if one transmitter holds the SDAx line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDAx line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDAx line. If this transmitter is also a master device, it also must stop driving the SCLx line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDAx line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

#### 16.1.2.4 Receive Interrupts

The RCxIF interrupt flag bit of the PIR1/PIR3 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCxIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCxIF interrupts are enabled by setting the following bits:

- RCxIE interrupt enable bit of the PIE1/PIE3 register

- PEIE/GIEL peripheral interrupt enable bit of the INTCON register

- GIE/GIEH global interrupt enable bit of the INTCON register

The RCxIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### 16.1.2.5 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTAx register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.x

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTAx register which resets the EUSART. Clearing the CREN bit of the RCSTAx register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

Note:

If all receive characters in the receive FIFO have framing errors, repeated reads of the RCREGx will not clear the FERR bit.

#### 16.1.2.6 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTAx register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTAx register or by resetting the EUSART by clearing the SPEN bit of the RCSTAx register.

### 16.1.2.7 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTAx register is set, the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTAx register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREGx.

#### 16.1.2.8 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTAx register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCxIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

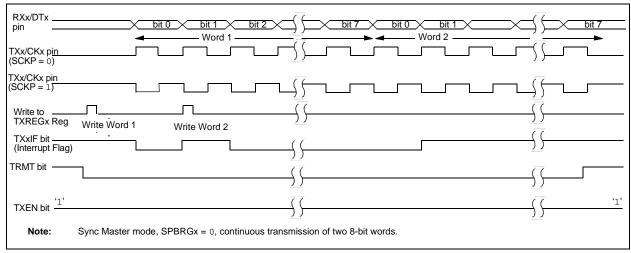

# 16.5.1.5 Synchronous Master Transmission Setup:

- Initialize the SPBRGHx, SPBRGx register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 16.4 "EUSART Baud Rate Generator (BRG)").

- Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC. Set the TRIS bits corresponding to the RXx/DTx and TXx/CKx I/O pins.

- Disable Receive mode by clearing bits SREN and CREN.

- 5. Enable Transmit mode by setting the TXEN bit.

- 6. If 9-bit transmission is desired, set the TX9 bit.

- 7. If interrupts are desired, set the TXxIE, GIE/ GIEH and PEIE/GIEL interrupt enable bits.

- 8. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 9. Start transmission by loading data to the TXREGx register.

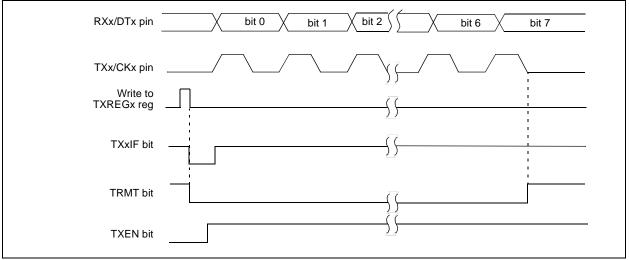

#### FIGURE 16-10: SYNCHRONOUS TRANSMISSION

# FIGURE 16-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

### 21.3 Register Definitions: FVR Control

#### REGISTER 21-1: VREFCON0: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0     | R/W-1 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----------|-------|-----|-----|-----|-------|

| FVREN | FVRST | FVRS<1:0> |       | _   | _   | _   | _     |

| bit 7 |       | •         |       | •   |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 **FVREN:** Fixed Voltage Reference Enable bit 0 = Fixed Voltage Reference is disabled 1 = Fixed Voltage Reference is enabled bit 6 FVRST: Fixed Voltage Reference Ready Flag bit 0 = Fixed Voltage Reference output is not ready or not enabled 1 = Fixed Voltage Reference output is ready for use bit 5-4 FVRS<1:0>: Fixed Voltage Reference Selection bits 00 = Fixed Voltage Reference Peripheral output is off 01 = Fixed Voltage Reference Peripheral output is 1x (1.024V) 10 = Fixed Voltage Reference Peripheral output is 2x (2.048V)<sup>(1)</sup> 11 = Fixed Voltage Reference Peripheral output is  $4x (4.096V)^{(1)}$ bit 3-2 Reserved: Read as '0'. Maintain these bits clear. bit 1-0 Unimplemented: Read as '0'.

Note 1: Fixed Voltage Reference output cannot exceed VDD.

### TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name     | Bit 7 | Bit 6 | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register on Page |

|----------|-------|-------|-----------|-------|-------|-------|-------|-------|------------------|

| VREFCON0 | FVREN | FVRST | FVRS<1:0> |       | _     | _     | _     | _     | 332              |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by the FVR module.

# 23.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

The PIC18(L)F2X/4XK22 devices have a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that sets both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution branches to the interrupt vector address and the software responds to the interrupt.

The High/Low-Voltage Detect Control register (Register 23-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The module's block diagram is shown in Figure 23-1.

#### 23.1 **Register - HLVD Control**

Legend:

R = Readable bit

#### **REGISTER 23-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER**

W = Writable bit

| R/W-0   | R-0   | R-0   | R/W-0  | R/W-0      | R/W-1 | R/W-0 | R/W-1 |

|---------|-------|-------|--------|------------|-------|-------|-------|

| VDIRMAG | BGVST | IRVST | HLVDEN | HLVDL<3:0> |       |       |       |

| bit 7   |       |       |        |            |       | bit 0 |       |

U = Unimplemented bit, read as '0'

|                 |                                                                                                                                                                                                                                                                                                   |                      |                       | .,                 |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|--------------------|--|--|--|--|--|

| -n = Value at P | OR '1' = Bit i                                                                                                                                                                                                                                                                                    | s set                | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |  |

| bit 7           | VDIRMAG: Voltage Dire                                                                                                                                                                                                                                                                             | ection Magnitude S   | elect hit             |                    |  |  |  |  |  |

| Dit 1           | 1 = Event occurs when<br>0 = Event occurs when                                                                                                                                                                                                                                                    | voltage equals or e  | xceeds trip point (HL | ,                  |  |  |  |  |  |

| bit 6           | bit 6 BGVST: Band Gap Reference Voltages Stable Status Flag bit                                                                                                                                                                                                                                   |                      |                       |                    |  |  |  |  |  |

|                 | <ul><li>1 = Internal band gap v</li><li>0 = Internal band gap v</li></ul>                                                                                                                                                                                                                         | •                    |                       |                    |  |  |  |  |  |

| bit 5           | IRVST: Internal Referen                                                                                                                                                                                                                                                                           | nce Voltage Stable I | Flag bit              |                    |  |  |  |  |  |

|                 | <ul> <li>1 = Indicates that the voltage detect logic will generate the interrupt flag at the specified voltage ran</li> <li>0 = Indicates that the voltage detect logic will not generate the interrupt flag at the specified volta range and the HLVD interrupt should not be enabled</li> </ul> |                      |                       |                    |  |  |  |  |  |

| bit 4           | HLVDEN: High/Low-Vo                                                                                                                                                                                                                                                                               | Itage Detect Power   | Enable bit            |                    |  |  |  |  |  |

|                 | <ul><li>1 = HLVD enabled</li><li>0 = HLVD disabled</li></ul>                                                                                                                                                                                                                                      |                      |                       |                    |  |  |  |  |  |

| bit 3-0         | HLVDL<3:0>: Voltage I                                                                                                                                                                                                                                                                             | Detection Level bits | (1)                   |                    |  |  |  |  |  |

|                 | 1111 = External analog                                                                                                                                                                                                                                                                            |                      | t comes from the HL\  | /DIN pin)          |  |  |  |  |  |

|                 | •                                                                                                                                                                                                                                                                                                 |                      |                       |                    |  |  |  |  |  |

|                 | •                                                                                                                                                                                                                                                                                                 |                      |                       |                    |  |  |  |  |  |

|                 | 0000 = Minimum settin                                                                                                                                                                                                                                                                             | g                    |                       |                    |  |  |  |  |  |

| Note 1: See     | Table 27-5 for specificat                                                                                                                                                                                                                                                                         | ions.                |                       |                    |  |  |  |  |  |

See Table 27-5 for specifications.

#### **TBLWT Table Write** Syntax: TBLWT ( \*; \*+; \*-; +\*) Operands: None Operation: if TBLWT\*, (TABLAT) → Holding Register; TBLPTR - No Change; if TBLWT\*+, (TABLAT) → Holding Register; (TBLPTR) + 1 $\rightarrow$ TBLPTR; if TBLWT\*-, (TABLAT) → Holding Register; $(TBLPTR) - 1 \rightarrow TBLPTR;$ if TBLWT+\*, (TBLPTR) + 1 $\rightarrow$ TBLPTR; (TABLAT) → Holding Register; Status Affected: None

0000

Description:

Encoding:

=2 \*-+\* = 3 This instruction uses the three LSBs of TBLPTR to determine which of the eight holding registers the TABLAT is written to. The holding registers are used to program the contents of Program Memory (P.M.).

0000

11nn

=1 \*+

nn=0 \*

0000

(Refer to Section 6.0 "Flash Program Memory" for additional details on programming Flash memory.)

The TBLPTR (a 21-bit pointer) points to each byte in the program memory. TBLPTR has a 2-MByte address range. The LSb of the TBLPTR selects which byte of the program memory location to access.

TBLPTR[0] = 0: Least Significant Byte of Program

TBLPTR[0] = 1: Byte of Program

Byte of Program

Memory Word

The TBLWT instruction can modify the value of TBLPTR as follows:

· no change

post-increment

post-decrement

pre-increment

Words: Cycles: 2

Q Cycle Activity:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| Decode    | No        | No        | No        |

|           | operation | operation | operation |

| No        | No        | No        | No        |

| operation | operation | operation | •         |

|           | (Read     |           | (Write to |

|           | TABLAT)   |           | Holding   |

|           |           |           | Register) |

```

TBLWT

Table Write (Continued)

Example1:

TBLWT *+;

Before Instruction

TABLAT

55h

TBLPTR

00A356h

HOLDING REGISTER

(00A356h)

FFh

After Instructions (table write completion)

TABLAT

55h

TBLPTR

00A357h

HOLDING REGISTER

(00A356h)

55h

Example 2:

TBLWT +*;

Before Instruction

TABLAT

34h

TBLPTR

HOLDING REGISTER

01389Ah

FFh

(01389Ah)

HOLDING REGISTER

FFh

(01389Bh)

After Instruction (table write completion)

TABLAT

34h

TBLPTR

01389Bh

HOLDING REGISTER

(01389Ah)

FFh

HOLDING REGISTER

(01389Bh)

34h

```

# 27.5 DC Characteristics: Primary Run Supply Current, PIC18(L)F2X/4XK22

| PIC18LF      | PIC18LF2X/4XK22             |                                                                                                    | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ |       |                 |            |                                                                         |  |  |  |  |

|--------------|-----------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|------------|-------------------------------------------------------------------------|--|--|--|--|

| PIC18F2      | X/4XK22                     | Standard Operating Conditions (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +125°C |                                                                                                                                               |       |                 |            |                                                                         |  |  |  |  |

| Param<br>No. | Device Characteristics      | Тур                                                                                                | Max                                                                                                                                           | Units | Conditions      |            |                                                                         |  |  |  |  |

| D070         | Supply Current (IDD)(1),(2) | 0.11                                                                                               | 0.20                                                                                                                                          | mA    | -40°C to +125°C | VDD = 1.8V | Fosc = 1 MHz                                                            |  |  |  |  |

| D071         |                             | 0.17                                                                                               | 0.25                                                                                                                                          | mA    | -40°C to +125°C | VDD = 3.0V | (PRI_RUN mode,<br>ECM source)                                           |  |  |  |  |

| D072         |                             | 0.15                                                                                               | 0.25                                                                                                                                          | mA    | -40°C to +125°C | VDD = 2.3V | Fosc = 1 MHz                                                            |  |  |  |  |

| D073         |                             | 0.20                                                                                               | 0.30                                                                                                                                          | mA    | -40°C to +125°C | VDD = 3.0V | (PRI_RUN mode,<br>ECM source)                                           |  |  |  |  |

| D074         |                             | 0.25                                                                                               | 0.35                                                                                                                                          | mA    | -40°C to +125°C | VDD = 5.0V | LOW Source)                                                             |  |  |  |  |

| D075         |                             | 1.45                                                                                               | 2.0                                                                                                                                           | mA    | -40°C to +125°C | VDD = 1.8V | Fosc = 20 MHz                                                           |  |  |  |  |

| D076         |                             | 2.60                                                                                               | 3.5                                                                                                                                           | mA    | -40°C to +125°C | VDD = 3.0V | (PRI_RUN mode,<br>ECH source)                                           |  |  |  |  |

| D077         |                             | 1.95                                                                                               | 2.5                                                                                                                                           | mA    | -40°C to +125°C | VDD = 2.3V | Fosc = 20 MHz                                                           |  |  |  |  |

| D078         |                             | 2.65                                                                                               | 3.5                                                                                                                                           | mA    | -40°C to +125°C | VDD = 3.0V | ( <b>PRI_RUN</b> mode,<br>ECH source)                                   |  |  |  |  |

| D079         |                             | 2.95                                                                                               | 4.5                                                                                                                                           | mA    | -40°C to +125°C | VDD = 5.0V | Lorr source)                                                            |  |  |  |  |

| D080         |                             | 7.5                                                                                                | 10                                                                                                                                            | mA    | -40°C to +125°C | VDD = 3.0V | Fosc = 64 MHz<br>(PRI_RUN,<br>ECH oscillator)                           |  |  |  |  |

| D081         |                             | 7.5                                                                                                | 10                                                                                                                                            | mA    | -40°C to +125°C | VDD = 3.0V | Fosc = 64 MHz                                                           |  |  |  |  |

| D082         |                             | 8.5                                                                                                | 11.5                                                                                                                                          | mA    | -40°C to +125°C | VDD = 5.0V | (PRI_RUN mode, ECH source)                                              |  |  |  |  |

| D083         |                             | 1.0                                                                                                | 1.5                                                                                                                                           | mA    | -40°C to +125°C | VDD = 1.8V | Fosc = 4 MHz                                                            |  |  |  |  |

| D084         |                             | 1.8                                                                                                | 3.0                                                                                                                                           | mA    | -40°C to +125°C | VDD = 3.0V | 16 MHz Internal<br>(PRI_RUN mode,<br>ECM + PLL source)                  |  |  |  |  |

| D085         |                             | 1.4                                                                                                | 2.0                                                                                                                                           | mA    | -40°C to +125°C | VDD = 2.3V | Fosc = 4 MHz                                                            |  |  |  |  |

| D086         |                             | 1.85                                                                                               | 2.5                                                                                                                                           | mA    | -40°C to +125°C | VDD = 3.0V | 16 MHz Internal<br>(PRI_RUN mode,<br>ECM + PLL source)                  |  |  |  |  |

| D087         |                             | 2.1                                                                                                | 3.0                                                                                                                                           | mA    | -40°C to +125°C | VDD = 5.0V |                                                                         |  |  |  |  |

| D088         |                             | 6.35                                                                                               | 9.0                                                                                                                                           | mA    | -40°C to +125°C | VDD = 3.0V | FOSC = 16 MHz<br>64 MHz Internal<br>(PRI_RUN mode,<br>ECH + PLL source) |  |  |  |  |

| D089         |                             | 6.35                                                                                               | 9.0                                                                                                                                           | mA    | -40°C to +125°C | VDD = 3.0V | Fosc = 16 MHz                                                           |  |  |  |  |

| D090         |                             | 7.0                                                                                                | 10                                                                                                                                            | mA    | -40°C to +125°C | VDD = 5.0V | 64 MHz Internal<br>(PRI_RUN mode,<br>ECH + PLL source)                  |  |  |  |  |

Note 1: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

Test condition: All Peripheral Module Control bits in PMD0, PMD1 and PMD2 set to '1'.

2: The test conditions for all IDD measurements in active operation mode are:

All I/O pins set as outputs driven to Vss;

$\overline{MCLR} = VDD;$

OSC1 = external square wave, from rail-to-rail (PRI\_RUN and PRI\_IDLE only).

# 27.9 Memory Programming Requirements

| DC CHA       | ARACTE | RISTICS                                                              | Standard C<br>Operating to |      |        |       | ess otherwise stated)<br>125°C                |

|--------------|--------|----------------------------------------------------------------------|----------------------------|------|--------|-------|-----------------------------------------------|

| Param<br>No. | Sym    | Characteristic                                                       | Min                        | Тур† | Max    | Units | Conditions                                    |

|              |        | Internal Program Memory<br>Programming Specifications <sup>(1)</sup> |                            |      |        |       |                                               |

| D170         | VPP    | Voltage on MCLR/VPP pin                                              | 8                          | _    | 9      | V     | (Note 3), (Note 4)                            |

| D171         | IDDP   | Supply Current during<br>Programming                                 | _                          | _    | 10     | mA    |                                               |

|              |        | Data EEPROM Memory                                                   |                            |      |        |       |                                               |

| D172         | ED     | Byte Endurance                                                       | 100K                       | _    | _      | E/W   | -40°C to +85°C                                |

| D173         | VDRW   | VDD for Read/Write                                                   | VDDMIN                     | _    | VDDMAX | V     | Using EECON to read/<br>write                 |

| D175         | TDEW   | Erase/Write Cycle Time                                               | _                          | 3    | 4      | ms    |                                               |

| D176         | TRETD  | Characteristic Retention                                             | _                          | 40   | _      | Year  | Provided no other specifications are violated |

| D177         | TREF   | Number of Total Erase/Write Cycles before Refresh <sup>(2)</sup>     | 1M                         | 10M  | _      | E/W   | -40°C to +85°C                                |

|              |        | Program Flash Memory                                                 |                            |      |        |       |                                               |

| D178         | ЕР     | Cell Endurance                                                       | 10K                        | _    | _      | E/W   | -40°C to +85°C (Note 5)                       |

| D179         | VPR    | VDD for Read                                                         | VDDMIN                     | _    | VDDMAX | V     |                                               |

| D181         | Viw    | VDD for Row Erase or Write                                           | 2.2                        | _    | VDDMAX | V     | PIC18LF24K22                                  |

| D182         | VIW    |                                                                      | VDDMIN                     | _    | VDDMAX | V     | PIC18(L)F26K22                                |

| D183         | Tıw    | Self-timed Write Cycle Time                                          | _                          | 2    | _      | ms    |                                               |

| D184         | TRETD  | Characteristic Retention                                             | _                          | 40   | _      | Year  | Provided no other specifications are violated |

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** These specifications are for programming the on-chip program memory through the use of table write instructions.

- 2: Refer to Section 7.8 "Using the Data EEPROM" for a more detailed discussion on data EEPROM endurance

- **3:** Required only if single-supply programming is disabled.

- **4:** The MPLAB ICD 2 does not support variable VPP output. Circuitry to limit the MPLAB ICD 2 VPP voltage must be placed between the MPLAB ICD 2 and target system when programming or debugging with the MPLAB ICD 2.

- 5: Self-write and Block Erase.

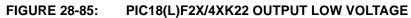

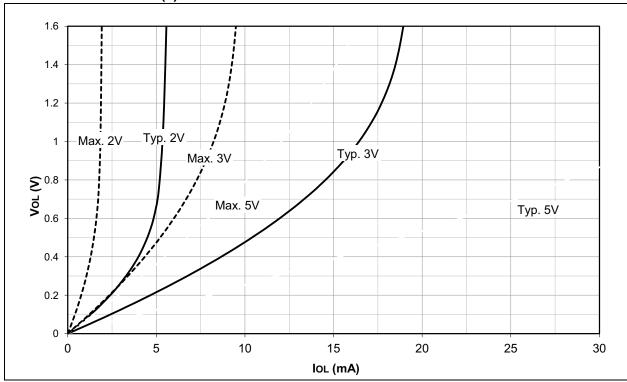

FIGURE 28-86: PIC18(L)F2X/4XK22 OUTPUT HIGH VOLTAGE

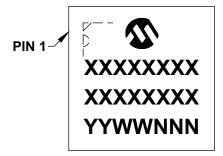

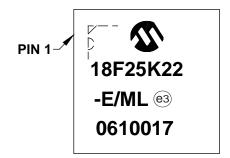

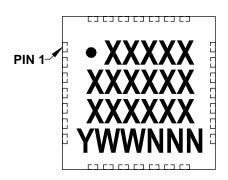

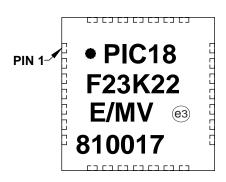

# **Package Marking Information (Continued)**

28-Lead QFN (6x6 mm)

Example

28-Lead UQFN (4x4x0.5 mm)

Example

40-Lead PDIP (600 mil)

Example

**Legend:** XX...X Customer-specific information or Microchip part number Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3) can be found on the outer packaging for this package.

**lote**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

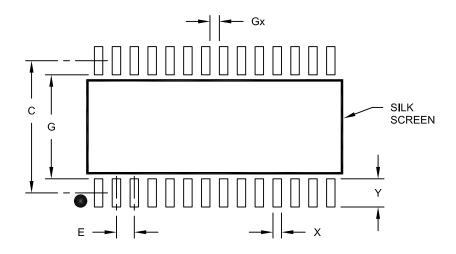

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units |          | MILLIMETERS |      |  |

|--------------------------|-------|----------|-------------|------|--|

| Dimension Limits         |       | MIN      | NOM         | MAX  |  |

| Contact Pitch            | Е     | 1.27 BSC |             |      |  |

| Contact Pad Spacing      | С     |          | 9.40        |      |  |

| Contact Pad Width (X28)  | Х     |          |             | 0.60 |  |

| Contact Pad Length (X28) | Υ     |          |             | 2.00 |  |

| Distance Between Pads    | Gx    | 0.67     |             |      |  |

| Distance Between Pads    | G     | 7.40     |             |      |  |

#### Notes:

Note:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

# 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |           | MILLIMETERS |      |  |  |

|------------------------|-------|-----------|-------------|------|--|--|

| Dimension Limits       |       | MIN       | NOM         | MAX  |  |  |

| Number of Pins         | Z     | 28        |             |      |  |  |

| Pitch                  | е     | 0.40 BSC  |             |      |  |  |

| Overall Height         | Α     | 0.45      | 0.50        | 0.55 |  |  |

| Standoff               | A1    | 0.00      | 0.02        | 0.05 |  |  |

| Contact Thickness      | A3    | 0.127 REF |             |      |  |  |

| Overall Width          | Е     | 4.00 BSC  |             |      |  |  |

| Exposed Pad Width      | E2    | 2.55      | 2.65        | 2.75 |  |  |

| Overall Length         | О     | 4.00 BSC  |             |      |  |  |

| Exposed Pad Length     | D2    | 2.55      | 2.65        | 2.75 |  |  |

| Contact Width          | b     | 0.15      | 0.20        | 0.25 |  |  |

| Contact Length         | Г     | 0.30      | 0.40        | 0.50 |  |  |

| Contact-to-Exposed Pad | K     | 0.20      | -           | -    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-152A Sheet 2 of 2