Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 30x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf44k22-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| OSC Mode               | OSC1 Pin                                              | OSC2 Pin                                              |

|------------------------|-------------------------------------------------------|-------------------------------------------------------|

| RC, INTOSC with CLKOUT | Floating, external resistor should pull high          | At logic low (clock/4 output)                         |

| RC with IO             | Floating, external resistor should pull high          | Configured as PORTA, bit 6                            |

| INTOSC with IO         | Configured as PORTA, bit 7                            | Configured as PORTA, bit 6                            |

| EC with IO             | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |

| EC with CLKOUT         | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |

| LP, XT, HS             | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |

TABLE 2-3:OSC1 AND OSC2 PIN STATES IN SLEEP MODE

Note: See Table 4-2 in Section 4.0 "Reset" for time-outs due to Sleep and MCLR Reset.

# 2.11 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS<1:0>) bits of the OSCCON register.

PIC18(L)F2X/4XK22 devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 3.1.2 "Entering Power-Managed Modes"**.

#### 2.11.1 SYSTEM CLOCK SELECT (SCS<1:0>) BITS

The System Clock Select (SCS<1:0>) bits of the OSCCON register select the system clock source that is used for the CPU and peripherals.

- When SCS<1:0> = 00, the system clock source is determined by configuration of the FOSC<3:0> bits in the CONFIG1H Configuration register.

- When SCS<1:0> = 10, the system clock source is chosen by the internal oscillator frequency selected by the INTSRC bit of the OSCTUNE register, the MFIOSEL bit of the OSCCON2 register and the IRCF<2:0> bits of the OSCCON register.

- When SCS<1:0> = 01, the system clock source is the 32.768 kHz secondary oscillator shared with Timer1, Timer3 and Timer5.

After a Reset, the SCS<1:0> bits of the OSCCON register are always cleared.

Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS<1:0> bits of the OSCCON register. The user can monitor the SOSCRUN, MFIOFS and LFIOFS bits of the OSCCON2 register, and the HFIOFS and OSTS bits of the OSCCON register to determine the current system clock source.

# 2.11.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCCON register indicates whether the system clock is running from the external clock source, as defined by the FOSC<3:0> bits in the CONFIG1H Configuration register, or from the internal clock source. In particular, when the primary oscillator is the source of the primary clock, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes.

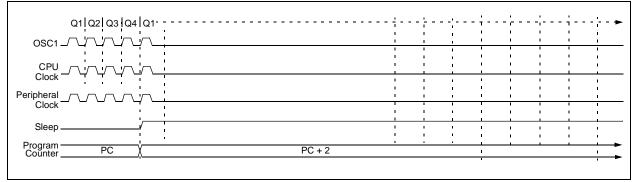

# 3.3 Sleep Mode

The Power-Managed Sleep mode in the PIC18(L)F2X/ 4XK22 devices is identical to the legacy Sleep mode offered in all other PIC microcontroller devices. It is entered by clearing the IDLEN bit of the OSCCON register and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 3-4) and all clock source Status bits are cleared.

Entering the Sleep mode from either Run or Idle mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the LFINTOSC source will continue to operate. If the SOSC oscillator is enabled, it will also continue to run.

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS<1:0> bits becomes ready (see Figure 3-5), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see **Section 24.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

# 3.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected by the SCS<1:0> bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the LFINTOSC source will continue to operate. If the SOSC oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out, or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT time-out will result in a WDT wake-up to the Run mode currently specified by the SCS<1:0> bits.

# FIGURE 3-4: TRANSITION TIMING FOR ENTRY TO SLEEP MODE

| dress<br>F5Fh<br>F5Eh<br>F5Dh<br>F5Ch<br>F5Bh<br>F58h<br>F57h<br>F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F54h | Name<br>CCPR3H<br>CCPR3L<br>CCP3CON<br>PWM3CON<br>ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCPR4L<br>CCPR5H<br>CCPR5H<br>CCPR5L<br>CCP5CON |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| F5Eh<br>F5Dh<br>F5Ch<br>F5Bh<br>F58h<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F55h<br>F54h<br>F53h          | CCPR3L<br>CCP3CON<br>PWM3CON<br>ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                       |

| F5Dh<br>F5Ch<br>F5Bh<br>F5Ah<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F53h                          | CCP3CON<br>PWM3CON<br>ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                 |

| F5Ch<br>F5Bh<br>F5Ah<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F53h                                  | PWM3CON<br>ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                            |

| F5Bh<br>F5Ah<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F55h<br>F53h                                          | ECCP3AS<br>PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                                       |

| F5Ah<br>F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F55h<br>F53h                                                  | PSTR3CON<br>CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                                                  |

| F59h<br>F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F53h                                                          | CCPR4H<br>CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                                                              |

| F58h<br>F57h<br>F56h<br>F55h<br>F54h<br>F53h                                                                  | CCPR4L<br>CCP4CON<br>CCPR5H<br>CCPR5L                                                                                                        |

| F57h<br>F56h<br>F55h<br>F54h<br>F53h                                                                          | CCP4CON<br>CCPR5H<br>CCPR5L                                                                                                                  |

| F56h<br>F55h<br>F54h<br>F53h                                                                                  | CCPR5H<br>CCPR5L                                                                                                                             |

| F55h<br>F54h<br>F53h                                                                                          | CCPR5L                                                                                                                                       |

| F54h<br>F53h                                                                                                  |                                                                                                                                              |

| F53h                                                                                                          | CCF5CON                                                                                                                                      |

|                                                                                                               | TMR4                                                                                                                                         |

| EEDh                                                                                                          | PR4                                                                                                                                          |

| F52h<br>F51h                                                                                                  | T4CON                                                                                                                                        |

|                                                                                                               | T4CON<br>TMR5H                                                                                                                               |

|                                                                                                               | TMR5L                                                                                                                                        |

|                                                                                                               | T5CON                                                                                                                                        |

|                                                                                                               | T5GCON                                                                                                                                       |

|                                                                                                               | TMR6                                                                                                                                         |

|                                                                                                               | PR6                                                                                                                                          |

|                                                                                                               | T6CON                                                                                                                                        |

|                                                                                                               | CCPTMRS0                                                                                                                                     |

|                                                                                                               | CCPTMRS1                                                                                                                                     |

|                                                                                                               | SRCON0                                                                                                                                       |

|                                                                                                               | SRCON1                                                                                                                                       |

|                                                                                                               | CTMUCONH                                                                                                                                     |

|                                                                                                               | CTMUCONL                                                                                                                                     |

|                                                                                                               | CTMUICON                                                                                                                                     |

|                                                                                                               | VREFCON0                                                                                                                                     |

|                                                                                                               | VREFCON1                                                                                                                                     |

| F40h                                                                                                          | VREFCON2                                                                                                                                     |

| F3Fh                                                                                                          | PMD0                                                                                                                                         |

| F3Eh                                                                                                          | PMD1                                                                                                                                         |

| F3Dh                                                                                                          | PMD2                                                                                                                                         |

| F3Ch                                                                                                          | ANSELE                                                                                                                                       |

| F3Bh                                                                                                          | ANSELD                                                                                                                                       |

| F3Ah                                                                                                          | ANSELC                                                                                                                                       |

| F39h                                                                                                          | ANSELB                                                                                                                                       |

| F38h                                                                                                          | ANSELA                                                                                                                                       |

|                                                                                                               | F3Fh<br>F3Eh<br>F3Dh<br>F3Ch<br>F3Bh<br>F3Ah<br>F39h                                                                                         |

# TABLE 5-1: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F2X/4XK22 DEVICES

**Note 1:** This is not a physical register.

2: Unimplemented registers are read as '0'.

3: PIC18(L)F4XK22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

| U-0          | R/W-0                             | R-0                                                | R-0              | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|--------------|-----------------------------------|----------------------------------------------------|------------------|------------------|------------------|-----------------|--------|

| —            | ADIF                              | RC1IF                                              | TX1IF            | SSP1IF           | CCP1IF           | TMR2IF          | TMR1IF |

| bit 7        |                                   |                                                    |                  |                  |                  |                 | bit (  |

| 1            |                                   |                                                    |                  |                  |                  |                 |        |

| Legend:      | 1- 1-14                           |                                                    | L.14             |                  |                  | 1 (0)           |        |

| R = Readab   |                                   | W = Writable                                       |                  | -                | mented bit, read |                 |        |

| -n = Value a | IT POR                            | '1' = Bit is se                                    | t                | '0' = Bit is cle | ared             | x = Bit is unkr | lown   |

| bit 7        | Unimpleme                         | nted: Read as                                      | ʻ0'.             |                  |                  |                 |        |

| bit 6        | ADIF: A/D C                       | Converter Interre                                  | upt Flag bit     |                  |                  |                 |        |

|              |                                   | conversion con                                     |                  |                  |                  |                 |        |

|              |                                   | ) conversion is                                    | -                |                  | n started        |                 |        |

| bit 5        |                                   | SART1 Receive                                      |                  |                  |                  |                 |        |

|              |                                   | SART1 receive<br>SART1 receive                     |                  |                  | red when RCR     | EG1 is read)    |        |

| bit 4        |                                   | ART1 Transmit                                      | -                | -                |                  |                 |        |

|              |                                   |                                                    |                  |                  | cleared when T   | XREG1 is writte | en)    |

|              |                                   | SART1 transmi                                      |                  |                  |                  |                 |        |

| bit 3        |                                   | ster Synchrono                                     |                  | -                | -                |                 |        |

|              |                                   | nsmission/receptor to transmit/receptor            | •                | ete (must be cle | eared by softwa  | re)             |        |

| bit 2        | CCP1IF: CC                        | P1 Interrupt Fl                                    | ag bit           |                  |                  |                 |        |

|              |                                   | <u>de:</u><br>register capture<br>R register captu |                  | ist be cleared b | oy software)     |                 |        |

|              | Compare me                        |                                                    |                  |                  |                  |                 |        |

|              |                                   |                                                    |                  |                  | cleared by softw | are)            |        |

|              | <u>PWM mode</u>                   | R register comp                                    | are match occ    | unea             |                  |                 |        |

|              | Unused in th                      |                                                    |                  |                  |                  |                 |        |

| bit 1        | TMR2IF: TM                        | IR2 to PR2 Mat                                     | tch Interrupt Fl | ag bit           |                  |                 |        |

|              |                                   | o PR2 match o<br>R2 to PR2 matc                    |                  | be cleared by s  | software)        |                 |        |

| bit 0        | TMR1IF: TM                        | IR1 Overflow Ir                                    | terrupt Flag b   | it               |                  |                 |        |

|              |                                   | egister overflov<br>egister did not (              |                  | leared by softw  | vare)            |                 |        |

|              |                                   |                                                    |                  |                  |                  |                 |        |

| Note 1:      | Interrupt flag I                  | oits are set                                       | when an          |                  |                  |                 |        |

|              | interrupt condition               |                                                    |                  |                  |                  |                 |        |

|              | the state of its of the Global Ir |                                                    |                  |                  |                  |                 |        |

|              | GIEH of the INT                   |                                                    | bit, Gi∟/        |                  |                  |                 |        |

|              |                                   | 0                                                  |                  |                  |                  |                 |        |

# REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

Note: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

# 13.6 Register Definitions: Timer2/4/6 Control

REGISTER 13-1: TxCON: TIMER2/TIMER4/TIMER6 CONTROL REGISTER

| U-0            | R/W-0              | R/W-0                        | R/W-0       | R/W-0           | R/W-0            | R/W-0           | R/W-0        |  |  |

|----------------|--------------------|------------------------------|-------------|-----------------|------------------|-----------------|--------------|--|--|

| _              |                    | TxOUTF                       | PS<3:0>     |                 | TMRxON           | TxCKP           | S<1:0>       |  |  |

| bit 7          |                    |                              |             |                 |                  |                 | bit (        |  |  |

|                |                    |                              |             |                 |                  |                 |              |  |  |

| Legend:        |                    |                              |             |                 |                  |                 |              |  |  |

| R = Readal     | ble bit            | W = Writable                 | bit         | U = Unimple     | mented bit, read | as '0'          |              |  |  |

| u = Bit is ur  | nchanged           | x = Bit is unkr              | iown        | -n/n = Value    | at POR and BOR   | /Value at all o | other Resets |  |  |

| '1' = Bit is s | set                | '0' = Bit is clea            | ared        |                 |                  |                 |              |  |  |

| bit 7          | Unimplem           | nented: Read as '            | <b>`</b>    |                 |                  |                 |              |  |  |

| bit 6-3        | -                  | <3:0>: TimerX Ou             |             | ler Select bits |                  |                 |              |  |  |

|                |                    | 1 Postscaler                 |             |                 |                  |                 |              |  |  |

|                | 0001 = 1:2         | 2 Postscaler                 |             |                 |                  |                 |              |  |  |

|                | 0010 = 1:3         | 0010 = 1:3 Postscaler        |             |                 |                  |                 |              |  |  |

|                |                    | 0011 = 1:4 Postscaler        |             |                 |                  |                 |              |  |  |

|                |                    | 0100 = 1:5 Postscaler        |             |                 |                  |                 |              |  |  |

|                |                    | 6 Postscaler                 |             |                 |                  |                 |              |  |  |

|                |                    | 7 Postscaler<br>3 Postscaler |             |                 |                  |                 |              |  |  |

|                |                    | 9 Postscaler                 |             |                 |                  |                 |              |  |  |

|                |                    | 10 Postscaler                |             |                 |                  |                 |              |  |  |

|                |                    | 11 Postscaler                |             |                 |                  |                 |              |  |  |

|                | 1011 <b>= 1</b> :1 | 12 Postscaler                |             |                 |                  |                 |              |  |  |

|                | 1100 <b>= 1</b> :  | 13 Postscaler                |             |                 |                  |                 |              |  |  |

|                |                    | 14 Postscaler                |             |                 |                  |                 |              |  |  |

|                |                    | 15 Postscaler                |             |                 |                  |                 |              |  |  |

|                | 1111 <b>= 1</b> :1 | 16 Postscaler                |             |                 |                  |                 |              |  |  |

| bit 2          | TMRxON:            | TMRxON: TimerX On bit        |             |                 |                  |                 |              |  |  |

|                |                    | 1 = TimerX is on             |             |                 |                  |                 |              |  |  |

|                | 0 = Timer          | X is off                     |             |                 |                  |                 |              |  |  |

| bit 1-0        | TxCKPS<            | 1:0>: Timer2-type            | Clock Presc | ale Select bits |                  |                 |              |  |  |

|                | 00 = Preso         | caler is 1                   |             |                 |                  |                 |              |  |  |

|                | 01 = Preso         | caler is 4                   |             |                 |                  |                 |              |  |  |

|                | 1x = Presc         | polor in 16                  |             |                 |                  |                 |              |  |  |

# 14.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 14-1 demonstrates the code to perform this function.

#### EXAMPLE 14-1: CHANGING BETWEEN CAPTURE PRESCALERS

| #define NEW_CAPT_PS 0x06 | //Capture          |

|--------------------------|--------------------|

|                          | // Prescale 4th    |

|                          | // rising edge     |

| CCPxCON = 0;             | // Turn the CCP    |

|                          | // Module Off      |

| CCPxCON = NEW_CAPT_PS;   | // Turn CCP module |

|                          | // on with new     |

|                          | // prescale value  |

# 14.1.5 CAPTURE DURING SLEEP

Capture mode requires a 16-bit TimerX module for use as a time base. There are four options for driving the 16-bit TimerX module in Capture mode. It can be driven by the system clock (Fosc), the instruction clock (Fosc/ 4), or by the external clock sources, the Secondary Oscillator (Sosc), or the TxCKI clock input. When the 16-bit TimerX resource is clocked by Fosc or Fosc/4, TimerX will not increment during Sleep. When the device wakes from Sleep, TimerX will continue from its previous state. Capture mode will operate during Sleep when the 16-bit TimerX resource is clocked by one of the external clock sources (Sosc or the TxCKI pin).

# TABLE 14-3: REGISTERS ASSOCIATED WITH CAPTURE

| Name     | Bit 7    | Bit 6                                          | Bit 5      | Bit 4       | Bit 3              | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |  |

|----------|----------|------------------------------------------------|------------|-------------|--------------------|-----------|--------|--------|---------------------|--|

| CCP1CON  | P1M-     | <1:0>                                          | DC1B       | <1:0>       |                    | CCP1M<    | 3:0>   |        | 198                 |  |

| CCP2CON  | P2M-     | <1:0>                                          | DC2B       | <1:0>       |                    | CCP2M<    | 3:0>   |        | 198                 |  |

| CCP3CON  | P3M-     | <1:0>                                          | DC3B       | <1:0>       |                    | CCP3M<    | 3:0>   |        | 198                 |  |

| CCP4CON  | —        | _                                              | DC4B       | <1:0>       |                    | CCP4M<    | 3:0>   |        | 198                 |  |

| CCP5CON  | —        | —                                              | DC5B       | <1:0>       |                    | CCP5M<    | 3:0>   |        | 198                 |  |

| CCPR1H   |          |                                                | Capture/Co | mpare/PWM F | Register 1 High By | te (MSB)  |        |        | _                   |  |

| CCPR1L   |          |                                                | Capture/Co | mpare/PWM   | Register 1 Low By  | rte (LSB) |        |        | _                   |  |

| CCPR2H   |          | Capture/Compare/PWM Register 2 High Byte (MSB) |            |             |                    |           |        |        | _                   |  |

| CCPR2L   |          | Capture/Compare/PWM Register 2 Low Byte (LSB)  |            |             |                    |           |        |        |                     |  |

| CCPR3H   |          | Capture/Compare/PWM Register 3 High Byte (MSB) |            |             |                    |           |        |        |                     |  |

| CCPR3L   |          | Capture/Compare/PWM Register 3 Low Byte (LSB)  |            |             |                    |           |        |        |                     |  |

| CCPR4H   |          |                                                | Capture/Co | mpare/PWM F | Register 4 High By | te (MSB)  |        |        | _                   |  |

| CCPR4L   |          |                                                | Capture/Co | mpare/PWM   | Register 4 Low By  | rte (LSB) |        |        | _                   |  |

| CCPR5H   |          |                                                | Capture/Co | mpare/PWM F | Register 5 High By | te (MSB)  |        |        | —                   |  |

| CCPR5L   |          |                                                | Capture/Co | mpare/PWM   | Register 5 Low By  | rte (LSB) |        |        | _                   |  |

| CCPTMRS0 | C3TSE    | :L<1:0>                                        | —          | C2TS        | SEL<1:0>           | _         | C1TSEI | _<1:0> | 201                 |  |

| CCPTMRS1 | —        | _                                              | _          | —           | C5TSEL∢            | <1:0>     | C4TSEI | _<1:0> | 201                 |  |

| INTCON   | GIE/GIEH | PEIE/GIEL                                      | TMR0IE     | INTOIE      | RBIE               | TMR0IF    | INT0IF | RBIF   | 109                 |  |

| IPR1     | —        | ADIP                                           | RC1IP      | TX1IP       | SSP1IP             | CCP1IP    | TMR2IP | TMR1IP | 121                 |  |

| IPR2     | OSCFIP   | C1IP                                           | C2IP       | EEIP        | BCL1IP             | HLVDIP    | TMR3IP | CCP2IP | 122                 |  |

| IPR4     | —        | —                                              | —          | —           | —                  | CCP5IP    | CCP4IP | CCP3IP | 124                 |  |

| PIE1     | —        | ADIE                                           | RC1IE      | TX1IE       | SSP1IE             | CCP1IE    | TMR2IE | TMR1IE | 117                 |  |

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Capture mode.

**Note 1:** These registers/bits are available on PIC18(L)F4XK22 devices.

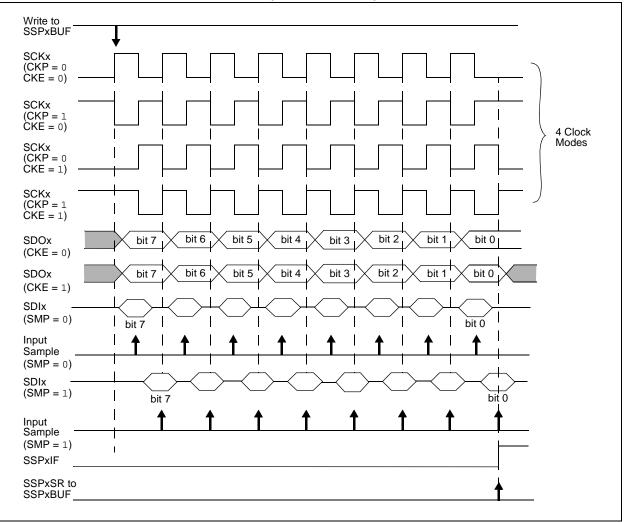

# 15.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCKx line. The master determines when the slave (Processor 2, Figure 15-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPxBUF register is written to. If the SPI is only going to receive, the SDOx output could be disabled (programmed as an input). The SSPxSR register will continue to shift in the signal present on the SDIx pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPxBUF register as if a normal received byte (interrupts and Status bits appropriately set).

The clock polarity is selected by appropriately programming the CKP bit of the SSPxCON1 register and the CKE bit of the SSPxSTAT register.

This then, would give waveforms for SPI communication as shown in Figure 15-6, Figure 15-8, Figure 15-9 and Figure 15-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPxADD + 1))

Figure 15-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDOx data is valid before there is a clock edge on SCKx. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPxBUF is loaded with the received data is shown.

# 15.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPxOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 15-5.

An MSSPx interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCLx will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 15.2.3 "SPI Master Mode"** for more detail.

#### 15.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSPx module configured as an  $I^2C$  slave in 7-bit Addressing mode. All decisions made by hardware or software and their effect on reception. Figure 15-14 and Figure 15-5 are used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $\mathsf{I}^2\mathsf{C}$  communication.

- 1. Start bit detected.

- S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCLx line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes Idle.

# 15.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the 8th falling edge of SCLx. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 15-16 displays a module using both address and data holding. Figure 15-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- 1. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the 8th falling edge of SCLx.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPx-CON3 register to <u>determine</u> if the SSPxIF was after or before the ACK.

- 5. Slave reads the address value from SSPxBUF, clearing the BF flag.

- Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF

**Note:** SSPxIF is still set after the 9th falling edge of SCLx even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPxIF not set.

- 11. SSPxIF set and CKP cleared after 8th falling edge of SCLx for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

# 17.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF flag bit

- Update the ADRESH:ADRESL registers with new conversion result

#### 17.2.3 DISCHARGE

The discharge phase is used to initialize the value of the capacitor array. The array is discharged after every sample. This feature helps to optimize the unity-gain amplifier, as the circuit always needs to charge the capacitor array, rather than charge/discharge based on previous measure values.

#### 17.2.4 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared by software. The ADRESH:ADRESL registers will not be updated with the partially complete Analog-to-Digital conversion sample. Instead, the ADRESH:ADRESL register pair will retain the value of the previous conversion.

**Note:** A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

# 17.2.5 DELAY BETWEEN CONVERSIONS

After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, the currently selected channel is reconnected to the charge holding capacitor commencing the next acquisition.

#### 17.2.6 ADC OPERATION IN POWER-MANAGED MODES

The selection of the automatic acquisition time and A/D conversion clock is determined in part by the clock source and frequency while in a power-managed mode.

If the A/D is expected to operate while the device is in a power-managed mode, the ACQT<2:0> and ADCS<2:0> bits in ADCON2 should be updated in accordance with the clock source to be used in that mode. After entering the mode, an A/D acquisition or conversion may be started. Once started, the device should continue to be clocked by the same clock source until the conversion has been completed.

If desired, the device may be placed into the corresponding Idle mode during the conversion. If the device clock frequency is less than 1 MHz, the A/D FRC clock source should be selected.

# 17.2.7 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

# 17.2.8 SPECIAL EVENT TRIGGER

Two Special Event Triggers are available to start an A/D conversion: CTMU and CCP5. The Special Event Trigger source is selected using the TRIGSEL bit in ADCON1.

When TRIGSEL = 0, the CCP5 module is selected as the Special Event Trigger source. To enable the Special Event Trigger in the CCP module, set CCP5M<3:0> = 1011, in the CCP5CON register.

When TRIGSEL = 1, the CTMU module is selected. The CTMU module requires that the CTTRIG bit in CTMUCONH is set to enable the Special Event Trigger.

In addition to TRIGSEL bit, the following steps are required to start an A/D conversion:

- The A/D module must be enabled (ADON = 1)

- The appropriate analog input channel selected

- The minimum acquisition period set one of these ways:

- Timing provided by the user

- Selection made of an appropriate TACQ time

With these conditions met, the trigger sets the GO/DONE bit and the A/D acquisition starts.

If the A/D module is not enabled (ADON = 0), the module ignores the Special Event Trigger.

# 17.2.9 PERIPHERAL MODULE DISABLE

When a peripheral module is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bit for the ADC module is ADCMD in the PMD2 Register. See **Section 3.0 "Power-Managed Modes"** for more information.

# EXAMPLE 19-2: CURRENT CALIBRATION ROUTINE

```

#include "pl8cxxx.h"

#define COUNT 500

//@ 8MHz = 125uS.

#define DELAY for(i=0;i<COUNT;i++)</pre>

#define RCAL .027

//R value is 4200000 (4.2M)

//scaled so that result is in

//1/100th of uA

#define ADSCALE 1023

//for unsigned conversion 10 sig bits

#define ADREF 3.3

//Vdd connected to A/D Vr+

int main(void)

{

int i;

int j = 0;

//index for loop

unsigned int Vread = 0;

double VTot = 0;

//assume CTMU and A/D have been set up correctly

//see Example 25-1 for CTMU & A/D setup

setup();

CTMUCONHbits.CTMUEN = 1;

//Enable the CTMU

CTMUCONLbits.EDG1STAT = 0;

// Set Edge status bits to zero

CTMUCONLbits.EDG2STAT = 0;

for(j=0;j<10;j++)</pre>

{

CTMUCONHbits.IDISSEN = 1;

//drain charge on the circuit

DELAY;

//wait 125us

CTMUCONHbits.IDISSEN = 0;

//end drain of circuit

CTMUCONLbits.EDG1STAT = 1;

//Begin charging the circuit

//using CTMU current source

DELAY;

//wait for 125us

CTMUCONLbits.EDG1STAT = 0;

//Stop charging circuit

PIR1bits.ADIF = 0;

//make sure A/D Int not set

ADCON0bits.GO=1;

//and begin A/D conv.

while(!PIR1bits.ADIF);

//Wait for A/D convert complete

//Get the value from the A/D

Vread = ADRES;

PIR1bits.ADIF = 0;

//Clear A/D Interrupt Flag

VTot += Vread;

//Add the reading to the total

}

Vavg = (float)(VTot/10.000);

//Average of 10 readings

Vcal = (float)(Vavg/ADSCALE*ADREF);

CTMUISrc = Vcal/RCAL;

//CTMUISrc is in 1/100ths of uA

```

| U-0                                     | U-0 | U-0               | R/W-0          | R/W-0         | R/W-0            | R/W-0       | R/W-0 |

|-----------------------------------------|-----|-------------------|----------------|---------------|------------------|-------------|-------|

| —                                       | —   | —                 |                |               | DACR<4:0>        |             |       |

| bit 7                                   |     |                   |                |               |                  |             | bit 0 |

|                                         |     |                   |                |               |                  |             |       |

| Legend:                                 |     |                   |                |               |                  |             |       |

| R = Readable bit W = Writable b         |     |                   | bit            | U = Unimpler  | nented bit, read | as '0'      |       |

| u = Bit is unchanged x = Bit is unknown |     | nown              | -n/n = Value a | at POR and BO | R/Value at all o | ther Resets |       |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared           |               |                  |             |       |

# REGISTER 22-2: VREFCON2: VOLTAGE REFERENCE CONTROL REGISTER 1

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DACR<4:0>: DAC Voltage Output Select bits VOUT = ((VSRC+) - (VSRC-))\*(DACR<4:0>/(2<sup>5</sup>)) + VSRC-

#### TABLE 22-1: REGISTERS ASSOCIATED WITH DAC MODULE

| Name     | Bit 7 | Bit 6  | Bit 5     | Bit 4     | Bit 3 | Bit 2       | Bit 1 | Bit 0  | Register<br>on Page |

|----------|-------|--------|-----------|-----------|-------|-------------|-------|--------|---------------------|

| VREFCON0 | FVREN | FVRST  | FVRS<1:0> |           | _     | _           | _     | _      | 332                 |

| VREFCON1 | DACEN | DACLPS | DACOE     | _         | DACPS | DACPSS<1:0> |       | DACNSS | 335                 |

| VREFCON2 | _     | _      | _         | DACR<4:0> |       |             |       |        | 336                 |

**Legend:** — = Unimplemented locations, read as '0'. Shaded bits are not used by the DAC module.

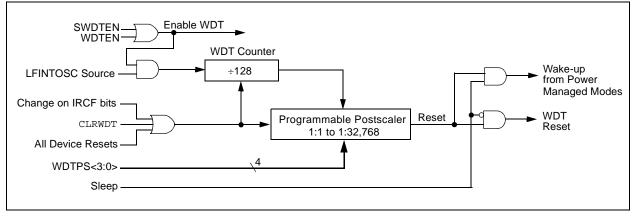

# 24.3 Watchdog Timer (WDT)

For PIC18(L)F2X/4XK22 devices, the WDT is driven by the LFINTOSC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the LFINTOSC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration Register 2H. Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: a SLEEP or CLRWDT instruction is executed, the IRCF bits of the OSCCON register are changed or a clock failure has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: Changing the setting of the IRCF bits of the OSCCON register clears the WDT and postscaler counts.

- **3:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

#### FIGURE 24-1: WDT BLOCK DIAGRAM

# 25.2 Extended Instruction Set

In addition to the standard 75 instructions of the PIC18 instruction set, PIC18(L)F2X/4XK22 devices also provide an optional extension to the core CPU functionality. The added features include eight additional instructions that augment indirect and indexed addressing operations and the implementation of Indexed Literal Offset Addressing mode for many of the standard PIC18 instructions.

The additional features of the extended instruction set are disabled by default. To enable them, users must set the XINST Configuration bit.

The instructions in the extended set can all be classified as literal operations, which either manipulate the File Select Registers, or use them for indexed addressing. Two of the instructions, ADDFSR and SUBFSR, each have an additional special instantiation for using FSR2. These versions (ADDULNK and SUBULNK) allow for automatic return after execution.

The extended instructions are specifically implemented to optimize re-entrant program code (that is, code that is recursive or that uses a software stack) written in high-level languages, particularly C. Among other things, they allow users working in high-level languages to perform certain operations on data structures more efficiently. These include:

- dynamic allocation and deallocation of software stack space when entering and leaving subroutines

- function pointer invocation

- software Stack Pointer manipulation

- manipulation of variables located in a software stack

A summary of the instructions in the extended instruction set is provided in Table 25-3. Detailed descriptions are provided in **Section 25.2.2 "Extended Instruction Set**". The opcode field descriptions in Table 25-1 apply to both the standard and extended PIC18 instruction sets.

Note: The instruction set extension and the Indexed Literal Offset Addressing mode were designed for optimizing applications written in C; the user may likely never use these instructions directly in assembler. The syntax for these commands is provided as a reference for users who may be reviewing code that has been generated by a compiler.

# 25.2.1 EXTENDED INSTRUCTION SYNTAX

Most of the extended instructions use indexed arguments, using one of the File Select Registers and some offset to specify a source or destination register. When an argument for an instruction serves as part of indexed addressing, it is enclosed in square brackets ("[]"). This is done to indicate that the argument is used as an index or offset. MPASM<sup>™</sup> Assembler will flag an error if it determines that an index or offset value is not bracketed.

When the extended instruction set is enabled, brackets are also used to indicate index arguments in byteoriented and bit-oriented instructions. This is in addition to other changes in their syntax. For more details, see Section 25.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands".

Note: In the past, square brackets have been used to denote optional arguments in the PIC18 and earlier instruction sets. In this text and going forward, optional arguments are denoted by braces ("{ }").

| Mnemonic,<br>Operands |                                 | Description                              | Cycles | 16-  | Bit Instru | uction W | ord      | Status |

|-----------------------|---------------------------------|------------------------------------------|--------|------|------------|----------|----------|--------|

|                       |                                 | Description                              | Cycles | MSb  |            | LSb      | Affected |        |

| ADDFSR                | f, k                            | Add literal to FSR                       | 1      | 1110 | 1000       | ffkk     | kkkk     | None   |

| ADDULNK               | k                               | Add literal to FSR2 and return           | 2      | 1110 | 1000       | 11kk     | kkkk     | None   |

| CALLW                 |                                 | Call subroutine using WREG               | 2      | 0000 | 0000       | 0001     | 0100     | None   |

| MOVSF                 | z <sub>s</sub> , f <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2      | 1110 | 1011       | 0zzz     | ZZZZ     | None   |

|                       |                                 | f <sub>d</sub> (destination) 2nd word    |        | 1111 | ffff       | ffff     | ffff     |        |

| MOVSS                 | z <sub>s</sub> , z <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2      | 1110 | 1011       | lzzz     | ZZZZ     | None   |

|                       |                                 | z <sub>d</sub> (destination) 2nd word    |        | 1111 | xxxx       | XZZZ     | ZZZZ     |        |

| PUSHL                 | k                               | Store literal at FSR2,<br>decrement FSR2 | 1      | 1110 | 1010       | kkkk     | kkkk     | None   |

| SUBFSR                | f, k                            | Subtract literal from FSR                | 1      | 1110 | 1001       | ffkk     | kkkk     | None   |

| SUBULNK               | k                               | Subtract literal from FSR2 and return    | 2      | 1110 | 1001       | 11kk     | kkkk     | None   |

# TABLE 25-3: EXTENSIONS TO THE PIC18 INSTRUCTION SET

| Param.<br>No. | Symbol  | Charac           | teristic                  | Min              | Max  | Units | Conditions                                    |

|---------------|---------|------------------|---------------------------|------------------|------|-------|-----------------------------------------------|

| 100           | Тнідн   | Clock High Time  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                                               |

|               |         |                  | 400 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    |                                               |

|               |         |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                               |

| 101           | TLOW    | Clock Low Time   | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    |                                               |

|               |         |                  | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                                               |

|               |         |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    |                                               |

| 102           | TR      | SDA and SCL      | 100 kHz mode              | —                | 1000 | ns    | CB is specified to be                         |

|               |         | Rise Time        | 400 kHz mode              | 20 + 0.1 Св      | 300  | ns    | from<br>10 to 400 pF                          |

|               |         |                  | 1 MHz mode <sup>(1)</sup> | —                | 300  | ns    | 10 to 400 pr                                  |

| 103           | TF      | SDA and SCL      | 100 kHz mode              | —                | 300  | ns    | CB is specified to be                         |

|               |         | Fall Time        | 400 kHz mode              | 20 + 0.1 Св      | 300  | ns    | from<br>10 to 400 pF                          |

|               |         |                  | 1 MHz mode <sup>(1)</sup> | —                | 100  | ns    | 10 to 400 pr                                  |

| 90            | TSU:STA | Start Condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    | Only relevant for                             |

|               |         | Setup Time       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | Repeated Start condition                      |

|               |         |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    | condition                                     |

| 91            | THD:STA | Start Condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | After this period, the first                  |

|               |         | Hold Time        | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | clock pulse is generated                      |

|               |         |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    |                                               |

| 106           | THD:DAT | Data Input       | 100 kHz mode              | 0                | _    | ns    |                                               |

|               |         | Hold Time        | 400 kHz mode              | 0                | 0.9  | ms    |                                               |

| 107           | TSU:DAT | Data Input       | 100 kHz mode              | 250              |      | ns    | (Note 2)                                      |

|               |         | Setup Time       | 400 kHz mode              | 100              | _    | ns    |                                               |

| 92            | TSU:STO | Stop Condition   | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                                               |

|               |         | Setup Time       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                                               |

|               |         |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                               |

| 109           | ΤΑΑ     | Output Valid     | 100 kHz mode              | —                | 3500 | ns    |                                               |

|               |         | from Clock       | 400 kHz mode              | —                | 1000 | ns    |                                               |

|               |         |                  | 1 MHz mode <sup>(1)</sup> | —                | —    | ns    |                                               |

| 110           | TBUF    | Bus Free Time    | 100 kHz mode              | 4.7              | —    | ms    | Time the bus must be                          |

|               |         |                  | 400 kHz mode              | 1.3              | —    | ms    | free before a new trans-<br>mission can start |

| D102          | Св      | Bus Capacitive L | oading                    | —                | 400  | pF    |                                               |

| TABLE 27-18: | MASTER SSP I <sup>2</sup> C BUS DATA REQUIREMENTS |

|--------------|---------------------------------------------------|

|--------------|---------------------------------------------------|

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins.

<sup>2:</sup> A fast mode I<sup>2</sup>C bus device can be used in a standard mode I<sup>2</sup>C bus system, but parameter 107 ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the Low period of the SCL signal. If such a device does stretch the Low period of the SCL signal, it must output the next data bit to the SDA line, parameter 102 + parameter 107 = 1000 + 250 = 1250 ns (for 100 kHz mode), before the SCL line is released.

# PIC18(L)F2X/4XK22

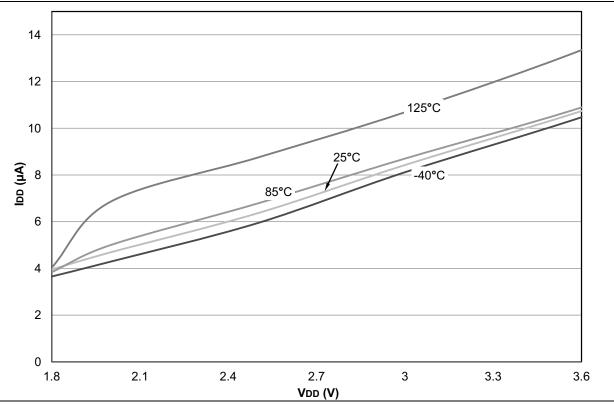

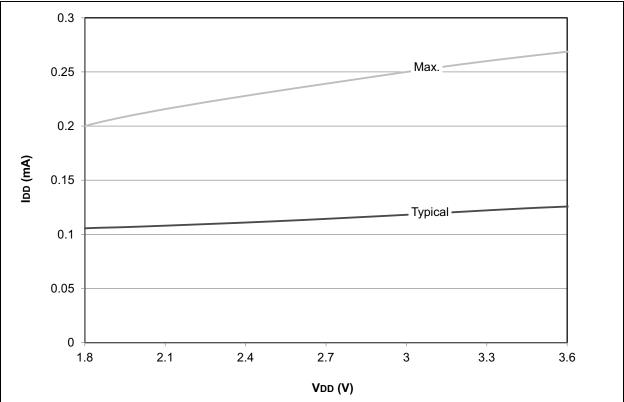

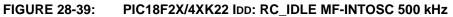

FIGURE 28-21: PIC18LF2X/4XK22 MAXIMUM IDD: RC\_RUN LF-INTOSC 31 kHz

# PIC18(L)F2X/4XK22

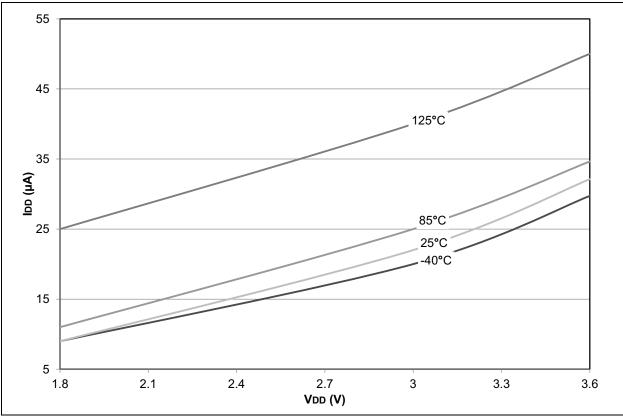

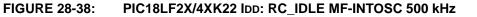

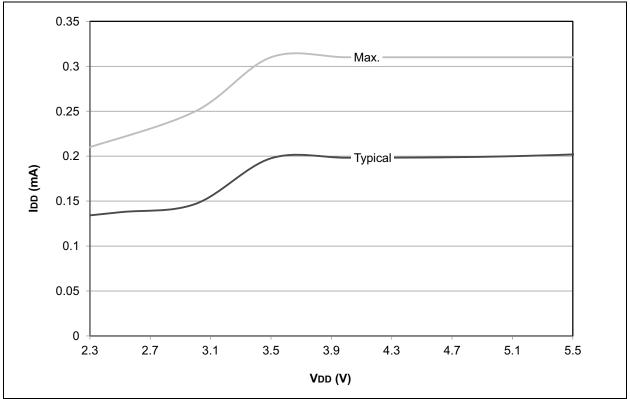

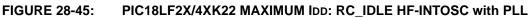

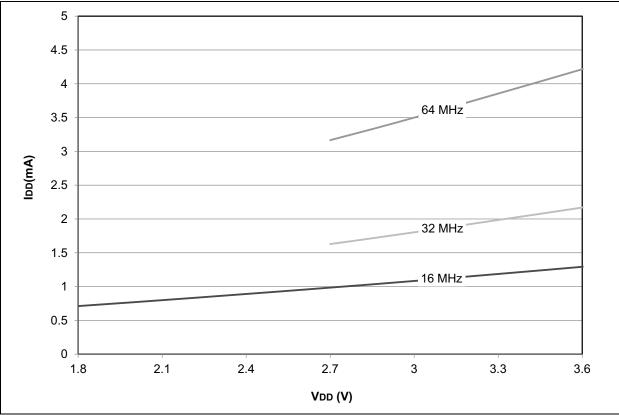

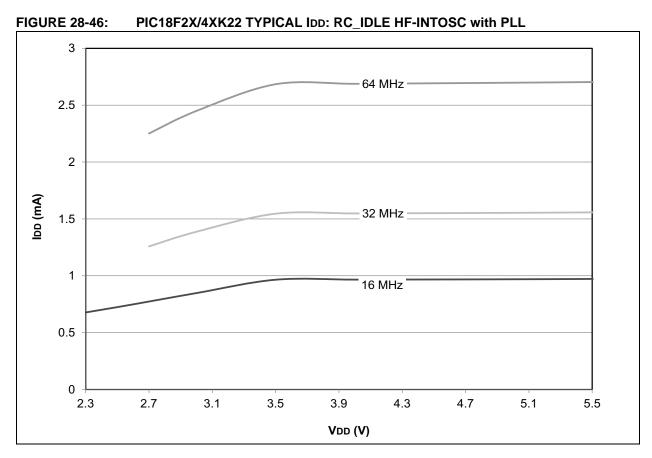

FIGURE 28-44: PIC18LF2X/4XK22 TYPICAL IDD: RC\_IDLE HF-INTOSC with PLL

# PIC18(L)F2X/4XK22

© 2010-2016 Microchip Technology Inc.

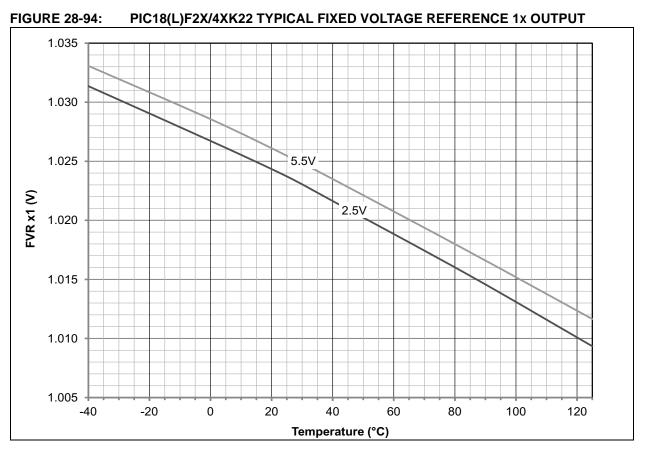

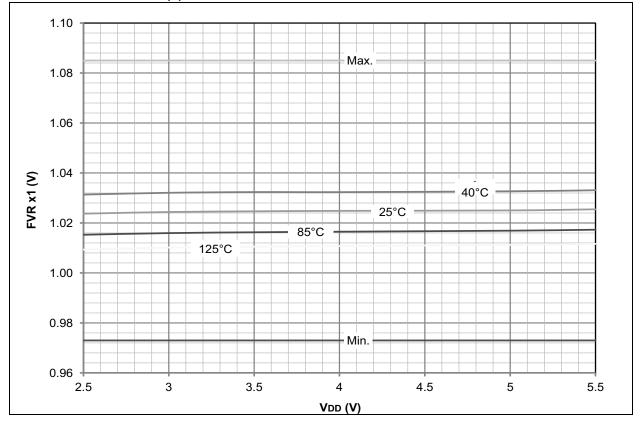

FIGURE 28-95: PIC18(L)F2X/4XK22 TYPICAL FIXED VOLTAGE REFERENCE 1x OUTPUT

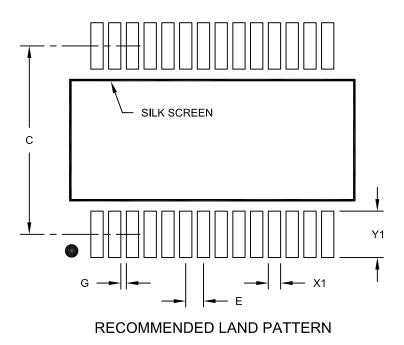

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |      |      |

|--------------------------|----|-------------|------|------|

| Dimension Limits         |    | MIN         | NOM  | MAX  |

| Contact Pitch            | E  | 0.65 BSC    |      |      |

| Contact Pad Spacing      | С  |             | 7.20 |      |

| Contact Pad Width (X28)  | X1 |             |      | 0.45 |

| Contact Pad Length (X28) | Y1 |             |      | 1.75 |

| Distance Between Pads    | G  | 0.20        |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A