Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 35                                                                           |

| Program Memory Size        | 16KB (8K x 16)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 768 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 30x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 44-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf44k22t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

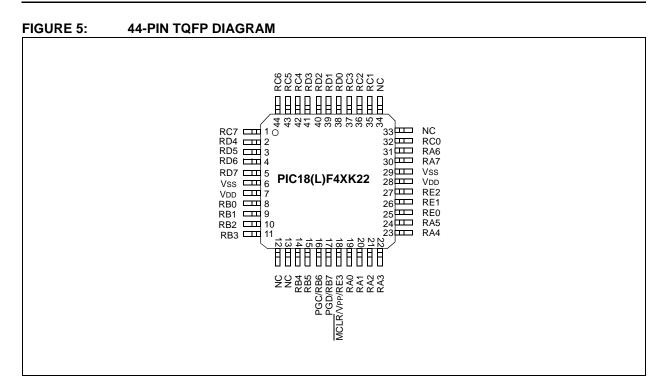

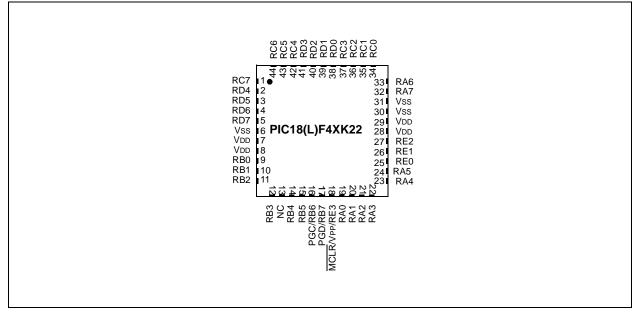

# PIC18(L)F2X/4XK22

|       | Pin N           | lumber          |       | Din Nomo     | Pin  | Buffer | Description                                   |  |  |  |

|-------|-----------------|-----------------|-------|--------------|------|--------|-----------------------------------------------|--|--|--|

| PDIP  | TQFP            | QFN             | UQFN  | Pin Name     | Туре | Туре   | Description                                   |  |  |  |

| 10    | 27              | 27              | 25    | RE2/CCP5/AN7 |      |        |                                               |  |  |  |

|       |                 |                 |       | RE2          | I/O  | ST     | Digital I/O.                                  |  |  |  |

|       |                 |                 |       | CCP5         | I/O  | ST     | Capture 5 input/Compare 5 output/PWM 5 output |  |  |  |

|       |                 |                 |       | AN7          | I    | Analog | Analog input 7.                               |  |  |  |

| 1     | 18              | 18              | 16    | RE3/VPP/MCLR |      |        |                                               |  |  |  |

|       |                 |                 |       | RE3          | I    | ST     | Digital input.                                |  |  |  |

|       |                 |                 |       | Vpp          | Р    |        | Programming voltage input.                    |  |  |  |

|       |                 |                 |       | MCLR         | I    | ST     | Active-low Master Clear (device Reset) input. |  |  |  |

| 11,32 | 7, 28           | 7, 8,<br>28, 29 | 7, 26 | Vdd          | Р    | —      | Positive supply for logic and I/O pins.       |  |  |  |

| 12,31 | 6, 29           | 6,30,<br>31     | 6, 27 | Vss          | Р    | _      | Ground reference for logic and I/O pins.      |  |  |  |

|       | 12,13,<br>33,34 | 13              |       | NC           |      |        |                                               |  |  |  |

## TABLE 1-3: PIC18(L)F4XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

# 2.7.1 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a 31.25 kHz internal clock source. The LFINTOSC is not tunable, but is designed to be stable across temperature and voltage. See **Section 27.0 "Electrical Specifications"** for the LFINTOSC accuracy specifications.

The output of the LFINTOSC can be a clock source to the primary clock or the INTOSC clock (see Figure 2-1). The LFINTOSC is also the clock source for the Powerup Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

# 2.7.2 FREQUENCY SELECT BITS (IRCF)

The HFINTOSC (16 MHz) and MFINTOSC (500 MHz) outputs connect to a divide circuit that provides frequencies of 16 MHz to 31.25 kHz. These divide circuit frequencies, along with the 31.25 kHz LFINTOSC output, are multiplexed to provide a single INTOSC clock output (see Figure 2-1). The IRCF<2:0> bits of the OSCCON register, the MFIOSEL bit of the OSCCON2 register and the INTSRC bit of the OSCTUNE register, select the output frequency of the internal oscillators. One of eight frequencies can be selected via software:

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz (default after Reset)

- 500 kHz (MFINTOSC or HFINTOSC)

- 250 kHz (MFINTOSC or HFINTOSC)

- 31 kHz (LFINTOSC, MFINTOSC or HFINTOSC)

# 2.7.3 INTOSC FREQUENCY DRIFT

The factory calibrates the internal oscillator block outputs (HFINTOSC/MFINTOSC) for 16 MHz/500 kHz. However, this frequency may drift as VDD or temperature changes. It is possible to adjust the HFINTOSC/MFINTOSC frequency by modifying the value of the TUN<5:0> bits in the OSCTUNE register. This has no effect on the LFINTOSC clock source frequency.

Tuning the HFINTOSC/MFINTOSC source requires knowing when to make the adjustment, in which direction it should be made and, in some cases, how large a change is needed. Three possible compensation techniques are discussed in the following sections. However, other techniques may be used.

# 2.7.3.1 Compensating with the EUSART

An adjustment may be required when the EUSART begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high; to adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low; to compensate, increment OSCTUNE to increase the clock frequency.

## 2.7.3.2 Compensating with the Timers

This technique compares device clock speed to some reference clock. Two timers may be used; one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator.

Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

# 2.7.3.3 Compensating with the CCP Module in Capture Mode

A CCP module can use free running Timer1, Timer3 or Timer5 clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast; to compensate, decrement the OSCTUNE register. If the measured time is much less than the calculated time, the internal oscillator block is running too slow; to compensate, increment the OSCTUNE register.

| Name     | Bit 7   | Bit 6  | Bit 5    | Bit 4              | Bit 3  | Bit 2   | Bit 1    | Bit 0  | Register<br>on Page |

|----------|---------|--------|----------|--------------------|--------|---------|----------|--------|---------------------|

| ANSELA   | —       | _      | ANSA5    | _                  | ANSA3  | ANSA2   | ANSA1    | ANSA0  | 149                 |

| CM1CON0  | C1ON    | C10UT  | C10E     | C1POL              | C1SP   | C1R     | C1CH     | <1:0>  | 308                 |

| CM2CON0  | C2ON    | C2OUT  | C2OE     | C2POL              | C2SP   | C2R     | C2CH     | l<1:0> | 308                 |

| LATA     | LATA7   | LATA6  | LATA5    | LATA4              | LATA3  | LATA2   | LATA1    | LATA0  | 152                 |

| VREFCON1 | DACEN   | DACLPS | DACOE    | —                  | DACP   | SS<1:0> | —        | DACNSS | 335                 |

| VREFCON2 | —       | —      | _        | DACR<4:0>          |        |         |          |        | 336                 |

| HLVDCON  | VDIRMAG | BGVST  | IRVST    | HLVDEN             |        | HLVDL   | <3:0>    |        | 337                 |

| PORTA    | RA7     | RA6    | RA5      | RA4                | RA3    | RA2     | RA1      | RA0    | 148                 |

| SLRCON   | —       | —      | _        | SLRE               | SLRD   | SLRC    | SLRB     | SLRA   | 153                 |

| SRCON0   | SRLEN   | S      | RCLK<2:0 | >                  | SRQEN  | SRNQEN  | SRPS     | SRPR   | 329                 |

| SSP1CON1 | WCOL    | SSPOV  | SSPEN    | SPEN CKP SSPM<3:0> |        |         |          | 253    |                     |

| T0CON    | TMR0ON  | T08BIT | TOCS     | T0SE               | PSA    | Т       | 0PS<2:0> |        | 154                 |

| TRISA    | TRISA7  | TRISA6 | TRISA5   | TRISA4             | TRISA3 | TRISA2  | TRISA1   | TRISA0 | 151                 |

|          |         |        |          |                    |        |         |          |        |                     |

TABLE 10-2: REGISTERS ASSOCIATED WITH PORTA

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTA.

## TABLE 10-3: CONFIGURATION REGISTERS ASSOCIATED WITH PORTA

| Name     | Bit 7                                                                           | Bit 6 | Bit 5    | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|----------|---------------------------------------------------------------------------------|-------|----------|--------|-------|-------|-------|-------|---------------------|

| CONFIG1H | IESO                                                                            | FCMEN | PRICLKEN | PLLCFG |       | FOSC  | <3:0> |       | 345                 |

| Levend   | Levende unimplemented leasting used as (o). Checked hits are not used for DODTA |       |          |        |       |       |       |       |                     |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTA.

# PIC18(L)F2X/4XK22

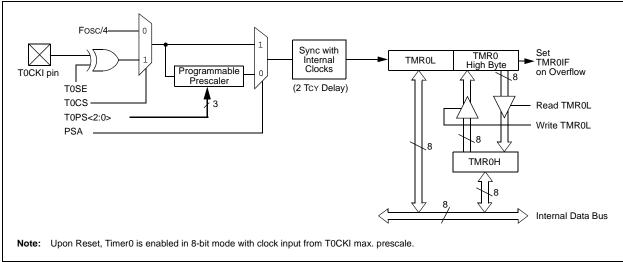

# FIGURE 11-2: TIMER0 BLOCK DIAGRAM (16-BIT MODE)

# 11.4 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS<2:0> bits of the T0CON register which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When the prescaler is assigned, prescale values from 1:2 through 1:256 in integer power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

# 11.4.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

# 11.5 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit of the INTCON register. Before re-enabling the interrupt, the TMR0IF bit must be cleared by software in the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name    | Bit 7                      | Bit 6     | Bit 5   | Bit 4   | Bit 3  | Bit 2  | Bit 1         | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------------|-----------|---------|---------|--------|--------|---------------|--------|----------------------------|

| INTCON  | GIE/GIEH                   | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE   | TMR0IF | <b>INT0IF</b> | RBIF   | 109                        |

| INTCON2 | RBPU                       | INTEDG0   | INTEDG1 | INTEDG2 | —      | TMR0IP |               | RBIP   | 110                        |

| T0CON   | TMR0ON                     | T08BIT    | TOCS    | T0SE    | PSA    |        | T0PS<2:0>     |        | 154                        |

| TMR0H   | Timer0 Register, High Byte |           |         |         |        |        |               |        | —                          |

| TMR0L   | Timer0 Register, Low Byte  |           |         |         |        |        |               | —      |                            |

| TRISA   | TRISA7                     | TRISA6    | TRISA5  | TRISA4  | TRISA3 | TRISA2 | TRISA1        | TRISA0 | 151                        |

# TABLE 11-1: REGISTERS ASSOCIATED WITH TIMER0

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by Timer0.

## 14.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 14-1 demonstrates the code to perform this function.

### EXAMPLE 14-1: CHANGING BETWEEN CAPTURE PRESCALERS

| #define NEW_CAPT_PS 0x06 | //Capture          |

|--------------------------|--------------------|

|                          | // Prescale 4th    |

|                          | // rising edge     |

| CCPxCON = 0;             | // Turn the CCP    |

|                          | // Module Off      |

| CCPxCON = NEW_CAPT_PS;   | // Turn CCP module |

|                          | // on with new     |

|                          | // prescale value  |

# 14.1.5 CAPTURE DURING SLEEP

Capture mode requires a 16-bit TimerX module for use as a time base. There are four options for driving the 16-bit TimerX module in Capture mode. It can be driven by the system clock (Fosc), the instruction clock (Fosc/ 4), or by the external clock sources, the Secondary Oscillator (Sosc), or the TxCKI clock input. When the 16-bit TimerX resource is clocked by Fosc or Fosc/4, TimerX will not increment during Sleep. When the device wakes from Sleep, TimerX will continue from its previous state. Capture mode will operate during Sleep when the 16-bit TimerX resource is clocked by one of the external clock sources (Sosc or the TxCKI pin).

## TABLE 14-3: REGISTERS ASSOCIATED WITH CAPTURE

| Name     | Bit 7    | Bit 6                                          | Bit 5      | Bit 4       | Bit 3              | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |  |

|----------|----------|------------------------------------------------|------------|-------------|--------------------|-----------|--------|--------|---------------------|--|

| CCP1CON  | P1M-     | <1:0>                                          | DC1B       | <1:0>       |                    | CCP1M<    | 3:0>   |        | 198                 |  |

| CCP2CON  | P2M-     | <1:0>                                          | DC2B       | <1:0>       |                    |           | 198    |        |                     |  |

| CCP3CON  | P3M-     | <1:0>                                          | DC3B       | <1:0>       | CCP3M<3:0>         |           |        |        | 198                 |  |

| CCP4CON  | —        | _                                              | DC4B       | <1:0>       |                    | CCP4M<    | 3:0>   |        | 198                 |  |

| CCP5CON  | —        | —                                              | DC5B       | <1:0>       |                    | CCP5M<    | 3:0>   |        | 198                 |  |

| CCPR1H   |          |                                                | Capture/Co | mpare/PWM F | Register 1 High By | te (MSB)  |        |        | _                   |  |

| CCPR1L   |          | Capture/Compare/PWM Register 1 Low Byte (LSB)  |            |             |                    |           |        |        |                     |  |

| CCPR2H   |          | Capture/Compare/PWM Register 2 High Byte (MSB) |            |             |                    |           |        |        |                     |  |

| CCPR2L   |          | Capture/Compare/PWM Register 2 Low Byte (LSB)  |            |             |                    |           |        |        |                     |  |

| CCPR3H   |          | Capture/Compare/PWM Register 3 High Byte (MSB) |            |             |                    |           |        |        |                     |  |

| CCPR3L   |          |                                                | Capture/Co | ompare/PWM  | Register 3 Low By  | rte (LSB) |        |        | _                   |  |

| CCPR4H   |          |                                                | Capture/Co | mpare/PWM F | Register 4 High By | te (MSB)  |        |        | _                   |  |

| CCPR4L   |          |                                                | Capture/Co | mpare/PWM   | Register 4 Low By  | rte (LSB) |        |        | _                   |  |

| CCPR5H   |          |                                                | Capture/Co | mpare/PWM F | Register 5 High By | te (MSB)  |        |        | —                   |  |

| CCPR5L   |          |                                                | Capture/Co | ompare/PWM  | Register 5 Low By  | rte (LSB) |        |        | _                   |  |

| CCPTMRS0 | C3TSE    | :L<1:0>                                        | —          | C2TS        | SEL<1:0>           | _         | C1TSEI | _<1:0> | 201                 |  |

| CCPTMRS1 | —        | _                                              | _          | —           | C5TSEL∢            | <1:0>     | C4TSEI | _<1:0> | 201                 |  |

| INTCON   | GIE/GIEH | PEIE/GIEL                                      | TMR0IE     | INTOIE      | RBIE               | TMR0IF    | INT0IF | RBIF   | 109                 |  |

| IPR1     | —        | ADIP                                           | RC1IP      | TX1IP       | SSP1IP             | CCP1IP    | TMR2IP | TMR1IP | 121                 |  |

| IPR2     | OSCFIP   | C1IP                                           | C2IP       | EEIP        | BCL1IP             | HLVDIP    | TMR3IP | CCP2IP | 122                 |  |

| IPR4     | —        | —                                              | —          | —           | —                  | CCP5IP    | CCP4IP | CCP3IP | 124                 |  |

| PIE1     | —        | ADIE                                           | RC1IE      | TX1IE       | SSP1IE             | CCP1IE    | TMR2IE | TMR1IE | 117                 |  |

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Capture mode.

**Note 1:** These registers/bits are available on PIC18(L)F4XK22 devices.

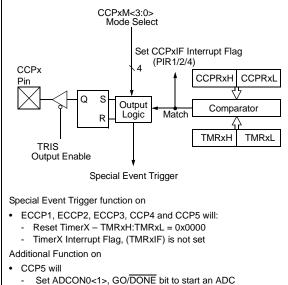

# 14.2 Compare Mode

The Compare mode function described in this section is identical for all CCP and ECCP modules available on this device family.

Compare mode makes use of the 16-bit TimerX resources, Timer1, Timer3 and Timer5. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMRxH:TMRxL register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output

- · Set the CCPx output

- Clear the CCPx output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 14-2 shows a simplified diagram of the Compare operation.

#### FIGURE 14-2: COMPARE MODE OPERATION BLOCK DIAGRAM

Conversion if ADCON<0>, ADON = 1.

# 14.2.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Some CCPx outputs are multiplexed on a couple of pins. Table 14-2 shows the CCP output pin Multiplexing. Selection of the output pin is determined by the CCPxMX bits in Configuration register 3H (CONFIG3H). Refer to Register 24-4 for more details.

Note: Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

# 14.2.2 TimerX MODE RESOURCE

In Compare mode, 16-bit TimerX resource must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 12.0 "Timer1/3/5 Module with Gate Control" for more information on configuring the 16-bit TimerX resources.

Note: Clocking TimerX from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TimerX must be clocked from the instruction clock (Fosc/4) or from an external clock source.

# 14.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

| Name                 | Bit 7           | Bit 6     | Bit 5             | Bit 4      | Bit 3         | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|----------------------|-----------------|-----------|-------------------|------------|---------------|-----------------------|-----------------------|-----------------------|---------------------|

| CCP1CON              | P1M-            | <1:0>     | DC1B              | <1:0>      |               | CCP1M<                | 3:0>                  |                       | 198                 |

| CCP2CON              | P2M-            | <1:0>     | DC2B              | <1:0>      |               | CCP2M<                | 3:0>                  |                       | 198                 |

| CCP3CON              | P3M-            | <1:0>     | DC3B              | <1:0>      |               | CCP3M<                | 3:0>                  |                       | 198                 |

| CCP4CON              | —               | —         | DC4B              | <1:0>      |               | CCP4M<                | 3:0>                  |                       | 198                 |

| CCP5CON              | —               | —         | DC5B              | <1:0>      |               |                       | 198                   |                       |                     |

| CCPTMRS0             | C3TSE           | L<1:0>    |                   | C2TS       | SEL<1:0>      | —                     | C1TSE                 | L<1:0>                | 201                 |

| CCPTMRS1             | —               | —         | _                 | —          | C5TSEL        | _<1:0>                | C4TSE                 | L<1:0>                | 201                 |

| INTCON               | GIE/GIEH        | PEIE/GIEL | TMR0IE            | INTOIE     | RBIE          | TMR0IF                | INTOIF                | RBIF                  | 109                 |

| IPR1                 | —               | ADIP      | RC1IP             | TX1IP      | SSP1IP        | CCP1IP                | TMR2IP                | TMR1IP                | 121                 |

| IPR2                 | OSCFIP          | C1IP      | C2IP              | EEIP       | BCL1IP        | HLVDIP                | TMR3IP                | CCP2IP                | 122                 |

| IPR4                 | —               | —         | _                 | —          | _             | CCP5IP                | CCP4IP                | CCP3IP                | 124                 |

| PIE1                 | —               | ADIE      | RC1IE             | TX1IE      | SSP1IE        | CCP1IE                | TMR2IE                | TMR1IE                | 117                 |

| PIE2                 | OSCFIE          | C1IE      | C2IE              | EEIE       | BCL1IE        | HLVDIE                | TMR3IE                | CCP2IE                | 118                 |

| PIE4                 | _               | _         | _                 | _          | _             | CCP5IE                | CCP4IE                | CCP3IE                | 120                 |

| PIR1                 | —               | ADIF      | RC1IF             | TX1IF      | SSP1IF        | CCP1IF                | TMR2IF                | TMR1IF                | 112                 |

| PIR2                 | OSCFIF          | C1IF      | C2IF              | EEIF       | BCL1IF        | HLVDIF                | TMR3IF                | CCP2IF                | 113                 |

| PIR4                 | —               | —         | _                 | —          | _             | CCP5IF                | CCP4IF                | CCP3IF                | 115                 |

| PMD0                 | UART2MD         | UART1MD   | TMR6MD            | TMR5MD     | TMR4MD        | TMR3MD                | TMR2MD                | TMR1MD                | 52                  |

| PMD1                 | MSSP2MD         | MSSP1MD   | _                 | CCP5MD     | CCP4MD        | CCP3MD                | CCP2MD                | CCP1MD                | 53                  |

| PR2                  |                 |           |                   | Timer2 Per | riod Register |                       |                       |                       | _                   |

| PR4                  |                 |           |                   | Timer4 Per | riod Register | er                    |                       |                       |                     |

| PR6                  |                 |           |                   | Timer6 Per | riod Register | _                     |                       |                       |                     |

| T2CON                | —               |           | T2OU              | TPS<3:0>   |               | TMR2ON                | T2CKP                 | S<1:0>                | 166                 |

| T4CON                | —               |           | T4OU              | TPS<3:0>   |               | TMR4ON                | T4CKP                 | S<1:0>                | 166                 |

| T6CON                | —               |           | T6OU <sup>-</sup> | TPS<3:0>   |               | TMR6ON                | T6CKP                 | S<1:0>                | 166                 |

| TMR2                 |                 |           |                   | Timer2     | Register      |                       |                       |                       | —                   |

| TMR4                 | Timer4 Register |           |                   |            |               |                       |                       | _                     |                     |

| TMR6                 |                 |           |                   | Timer6     | Register      |                       |                       |                       | —                   |

| TRISB                | TRISB7          | TRISB6    | TRISB5            | TRISB4     | TRISB3        | TRISB2                | TRISB1                | TRISB0                | 151                 |

| TRISC                | TRISC7          | TRISC6    | TRISC5            | TRISC4     | TRISC3        | TRISC2                | TRISC1                | TRISC0                | 151                 |

| TRISD <sup>(1)</sup> | TRISD7          | TRISD6    | TRISD5            | TRISD4     | TRISD3        | TRISD2                | TRISD1                | TRISD0                | 151                 |

| TRISE                | WPUE3           | —         | —                 | —          | _             | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 151                 |

# TABLE 14-10: REGISTERS ASSOCIATED WITH STANDARD PWM

**Legend:** — = Unimplemented location, read as '0'. Shaded bits are not used by Standard PWM mode.

Note 1: These registers/bits are available on PIC18(L)F4XK22 devices.

# TABLE 14-11: CONFIGURATION REGISTERS ASSOCIATED WITH STANDARD PWM

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| CONFIG3H | MCLRE | —     | P2BMX | T3CMX | HFOFST | CCP3MX | PBADEN | CCP2MX | 348                 |

**Legend:** — = Unimplemented location, read as '0'. Shaded bits are not used by Standard PWM mode.

#### 14.4.8 SETUP FOR ECCP PWM OPERATION USING ECCP1 AND TIMER2

The following steps should be taken when configuring the ECCP1 module for PWM operation using Timer2:

- 1. Configure the PWM pins to be used (P1A, P1B, P1C, and P1D):

- Configure PWM outputs to be used as inputs by setting the corresponding TRIS bits. This prevents spurious outputs during setup.

- Set the PSTR1CON bits for each PWM output to be used.

- Select Timer2 as the period timer by configuring CCPTMR0 register bits C1TSEL<1:0> = '00'.

- 3. Set the PWM period by loading the PR2 register.

- 4. Configure auto-shutdown as OFF or select the source with the CCP1AS<2:0> bits of the ECCP1AS register.

- 5. Configure the auto-shutdown sources as needed:

- Configure each comparator used.

- Configure the comparator inputs as analog.

- Configure the FLT0 input pin and clear ANSB0.

- 6. Force a shutdown condition (OFF included):

- Configure safe starting output levels by setting the default shutdown drive states with the PSS1AC<1:0> and PSS1BD<1:0> bits of the ECCP1AS register.

- Clear the P1RSEN bit of the PWM1CON register.

- Set the CCP1AS bit of the ECCP1AS register.

- Configure the ECCP1 module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M<1:0> bits.

- Select the polarities of the PWM output signals with the CCP1M<3:0> bits.

- 8. Set the 10-bit PWM duty cycle:

- Load the eight MSbs into the CCPR1L register.

- Load the two LSbs into the DC<1:0> bits of the CCP1CON register.

- For Half-Bridge Output mode, set the deadband delay by loading P1DC<6:0> bits of the PWM1CON register with the appropriate value.

- 10. Configure and start TMR2:

- Set the TMR2 prescale value by loading the T2CKPS bits of the T2CON register.

- Start Timer2 by setting the TMR2ON bit.

- 11. Enable the ECCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- 12. Start the PWM:

- If shutdown auto-restart is used, then set the P1RSEN bit of the PWM1CON register.

- If shutdown auto-restart is not used, then clear the CCP1ASE bit of the ECCP1AS register.

# © 2010-2016 Microchip Technology Inc

DS40001412G-page 226

PIC18(L)F2X/4XK22

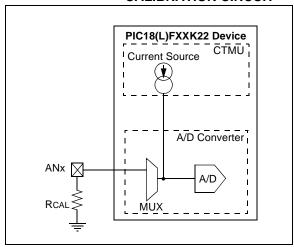

# 19.3 Calibrating the CTMU Module

The CTMU requires calibration for precise measurements of capacitance and time, as well as for accurate time delay. If the application only requires measurement of a relative change in capacitance or time, calibration is usually not necessary. An example of this type of application would include a capacitive touch switch, in which the touch circuit has a baseline capacitance, and the added capacitance of the human body changes the overall capacitance of a circuit.

If actual capacitance or time measurement is required, two hardware calibrations must take place: the current source needs calibration to set it to a precise current, and the circuit being measured needs calibration to measure and/or nullify all other capacitance other than that to be measured.

# 19.3.1 CURRENT SOURCE CALIBRATION

The current source on the CTMU module is trimable. Therefore, for precise measurements, it is possible to measure and adjust this current source by placing a high precision resistor, RCAL, onto an unused analog channel. An example circuit is shown in Figure 19-2. The current source measurement is performed using the following steps:

- 1. Initialize the A/D Converter.

- 2. Initialize the CTMU.

- Enable the current source by setting EDG1STAT (CTMUCONL<0>).

- 4. Issue settling time delay.

- 5. Perform A/D conversion.

- 6. Calculate the current source current using I = V/RCAL, where RCAL is a high precision resistance and *V* is measured by performing an A/D conversion.

The CTMU current source may be trimmed with the trim bits in CTMUICON using an iterative process to get an exact desired current. Alternatively, the nominal value without adjustment may be used; it may be stored by the software for use in all subsequent capacitive or time measurements.

To calculate the value for *RCAL*, the nominal current must be chosen, and then the resistance can be calculated. For example, if the A/D Converter reference voltage is 3.3V, use 70% of full scale, or 2.31V as the desired approximate voltage to be read by the A/D Converter. If the range of the CTMU current source is selected to be 0.55  $\mu$ A, the resistor value needed is calculated as *RCAL* = 2.31V/0.55  $\mu$ A, for a value of 4.2 MΩ. Similarly, if the current source is chosen to be 5.5  $\mu$ A, *RCAL* would be 420,000Ω, and 42,000Ω if the current source is set to 55  $\mu$ A.

#### FIGURE 19-2: CTMU CURRENT SOURCE CALIBRATION CIRCUIT

A value of 70% of full-scale voltage is chosen to make sure that the A/D Converter was in a range that is well above the noise floor. Keep in mind that if an exact current is chosen, that is to incorporate the trimming bits from CTMUICON, the resistor value of RCAL may need to be adjusted accordingly. RCAL may also be adjusted to allow for available resistor values. RCAL should be of the highest precision available, keeping in mind the amount of precision needed for the circuit that the CTMU will be used to measure. A recommended minimum would be 0.1% tolerance.

The following examples show one typical method for performing a CTMU current calibration. Example 19-1 demonstrates how to initialize the A/D Converter and the CTMU; this routine is typical for applications using both modules. Example 19-2 demonstrates one method for the actual calibration routine.

| R/C-1                                                                                                                                                                    | R/C-1              | R-1                                                    | U-0             | U-0            | U-0              | U-0      | U-0   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------|-----------------|----------------|------------------|----------|-------|

| WRTD                                                                                                                                                                     | WRTB               | WRTC <sup>(1)</sup>                                    | —               | _              | —                | —        | —     |

| bit 7                                                                                                                                                                    |                    |                                                        |                 |                |                  |          | bit 0 |

|                                                                                                                                                                          |                    |                                                        |                 |                |                  |          |       |

| Legend:                                                                                                                                                                  |                    |                                                        |                 |                |                  |          |       |

| R = Readable                                                                                                                                                             | bit                |                                                        |                 | U = Unimpler   | mented bit, read | 1 as '0' |       |

| -n = Value whe                                                                                                                                                           | en device is un    | programmed                                             |                 | C = Clearable  | e only bit       |          |       |

| bit 7                                                                                                                                                                    | 1 = Data EEF       | EEPROM Writ<br>PROM not write<br>PROM write-pro        | -protected      | t              |                  |          |       |

| bit 6                                                                                                                                                                    | 1 = Boot Bloc      | Block Write Pro<br>k not write-pro<br>k write-protecto | tected          |                |                  |          |       |

| bit 5 WRTC: Configuration Register Write Protection bit <sup>(1)</sup><br>1 = Configuration registers not write-protected<br>0 = Configuration registers write-protected |                    |                                                        |                 |                |                  |          |       |

| bit 4-0                                                                                                                                                                  | Unimplemen         | ted: Read as '                                         | 0'              |                |                  |          |       |

| Note 1: Thi                                                                                                                                                              | s bit is read-only | y in normal exe                                        | cution mode; it | can be written | only in Program  | mode.    |       |

## REGISTER 24-9: CONFIG6H: CONFIGURATION REGISTER 6 HIGH

# **REGISTER 24-10: CONFIG7L: CONFIGURATION REGISTER 7 LOW**

|       |     |     |     |                      | -                    |       |       |

|-------|-----|-----|-----|----------------------|----------------------|-------|-------|

| U-0   | U-0 | U-0 | U-0 | R/C-1                | R/C-1                | R/C-1 | R/C-1 |

| —     | —   | —   | —   | EBTR3 <sup>(1)</sup> | EBTR2 <sup>(1)</sup> | EBTR1 | EBTR0 |

| bit 7 |     |     |     |                      |                      |       | bit 0 |

| Legend:                                |                                    |

|----------------------------------------|------------------------------------|

| R = Readable bit                       | U = Unimplemented bit, read as '0' |

| -n = Value when device is unprogrammed | C = Clearable only bit             |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                       |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | EBTR3: Table Read Protection bit <sup>(1)</sup>                                                                                                                  |

|         | <ul> <li>1 = Block 3 not protected from table reads executed in other blocks</li> <li>0 = Block 3 protected from table reads executed in other blocks</li> </ul> |

| bit 2   | EBTR2: Table Read Protection bit <sup>(1)</sup>                                                                                                                  |

|         | <ul> <li>1 = Block 2 not protected from table reads executed in other blocks</li> <li>0 = Block 2 protected from table reads executed in other blocks</li> </ul> |

| bit 1   | EBTR1: Table Read Protection bit                                                                                                                                 |

|         | <ul> <li>1 = Block 1 not protected from table reads executed in other blocks</li> <li>0 = Block 1 protected from table reads executed in other blocks</li> </ul> |

| bit 0   | EBTR0: Table Read Protection bit                                                                                                                                 |

|         | <ul> <li>1 = Block 0 not protected from table reads executed in other blocks</li> <li>0 = Block 0 protected from table reads executed in other blocks</li> </ul> |

| Note 1  | Available on PIC18/LIEX5K22 and PIC18/LIEX6K22s devices                                                                                                          |

**Note 1:** Available on PIC18(L)FX5K22 and PIC18(L)FX6K22s devices.

### 24.5.1 PROGRAM MEMORY CODE PROTECTION

The program memory may be read to or written from any location using the table read and table write instructions. The device ID may be read with table reads. The Configuration registers may be read and written with the table read and table write instructions.

In Normal execution mode, the CPn bits have no direct effect. CPn bits inhibit external reads and writes. A block of user memory may be protected from table writes if the WRTn Configuration bit is '0'. The EBTRn bits control table reads. For a block of user memory with the EBTRn bit cleared to '0', a table READ instruction that executes from within that block is allowed to read. A table read instruction that executes from a location outside of that block is not allowed to read and will result in reading '0's. Figures 24-3 through 24-5 illustrate table write and table read protection.

| Note: | Code protection bits may only be written         |  |  |  |  |  |

|-------|--------------------------------------------------|--|--|--|--|--|

|       | to a '0' from a '1' state. It is not possible to |  |  |  |  |  |

|       | write a '1' to a bit in the '0' state. Code pro- |  |  |  |  |  |

|       | tection bits are only set to '1' by a full chip  |  |  |  |  |  |

|       | erase or block erase function. The full chip     |  |  |  |  |  |

|       | erase and block erase functions can only         |  |  |  |  |  |

|       | be initiated via ICSP™ or an external            |  |  |  |  |  |

|       | programmer.                                      |  |  |  |  |  |

# FIGURE 24-3: TABLE WRITE (WRTn) DISALLOWED

| <b>Register Values</b>       | Program Memory                     | Configuration Bit Settings |

|------------------------------|------------------------------------|----------------------------|

|                              | 0000001<br>0007FF<br>0008001       | WRTB, EBTRB = 11<br>h      |

| TBLPTR = 0008FFh             | ▶┍╼▶                               | WRT0, EBTR0 = 01           |

| PC = 001FFEh                 | ТВLWT* 001FFF<br>002000            |                            |

|                              | 003FFF<br>0040001                  |                            |

| PC = 005FFEh                 | TBLWT* 005FFF 006000               |                            |

|                              |                                    | WRT3, EBTR3 = 11           |

| Results: All table writes di | abled to Blockn whenever WRTn = 0. | n                          |

# PIC18(L)F2X/4XK22

| ADDWFC                                                                            | ADD W a                                                                                                                                                                                       | ADD W and CARRY bit to f                                                                                                                                                                            |                                                                                                                                                                      |  |  |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                                                           | ADDWFC                                                                                                                                                                                        | f {,d {,a}}                                                                                                                                                                                         |                                                                                                                                                                      |  |  |

| Operands:                                                                         | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$                                                                                                                |                                                                                                                                                                                                     |                                                                                                                                                                      |  |  |

| Operation:                                                                        | (W) + (f) + (                                                                                                                                                                                 | $(C) \rightarrow dest$                                                                                                                                                                              |                                                                                                                                                                      |  |  |

| Status Affected:                                                                  | N,OV, C, D                                                                                                                                                                                    | C, Z                                                                                                                                                                                                |                                                                                                                                                                      |  |  |

| Encoding:                                                                         | 0010                                                                                                                                                                                          | 00da ff                                                                                                                                                                                             | ff ffff                                                                                                                                                              |  |  |

| Description:                                                                      | ory location<br>placed in W<br>placed in da<br>If 'a' is '0', tl<br>If 'a' is '1', tl<br>GPR bank.<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode when<br>Section 25<br>Bit-Oriente | n 'f'. If 'd' is '0'<br>/. If 'd' is '1', ti<br>ata memory lo<br>he Access Ba<br>he BSR is use<br>nd the extend<br>led, this instru<br>Literal Offset<br>never $f \le 95$ (5<br><b>.2.3 "Byte-O</b> | he result is<br>boation 'f'.<br>Ink is selected.<br>ad to select the<br>led instruction<br>ction operates<br>Addressing<br>bFh). See<br>riented and<br>hs in Indexed |  |  |

| Words:                                                                            | 1                                                                                                                                                                                             |                                                                                                                                                                                                     |                                                                                                                                                                      |  |  |

| Cycles:                                                                           | 1                                                                                                                                                                                             |                                                                                                                                                                                                     |                                                                                                                                                                      |  |  |

| Q Cycle Activity:                                                                 |                                                                                                                                                                                               |                                                                                                                                                                                                     |                                                                                                                                                                      |  |  |

| Q1                                                                                | Q2                                                                                                                                                                                            | Q3                                                                                                                                                                                                  | Q4                                                                                                                                                                   |  |  |

| Decode                                                                            | Read<br>register 'f'                                                                                                                                                                          | Process<br>Data                                                                                                                                                                                     | Write to destination                                                                                                                                                 |  |  |

| Example:                                                                          | ADDWFC                                                                                                                                                                                        | REG, 0,                                                                                                                                                                                             | 1                                                                                                                                                                    |  |  |

| Before Instruct<br>CARRY b<br>REG<br>W<br>After Instructio<br>CARRY b<br>REG<br>W | bit = 1<br>= 02h<br>= 4Dh                                                                                                                                                                     |                                                                                                                                                                                                     |                                                                                                                                                                      |  |  |

| AND                | DLW               | AND liter                   | al with V         | N    |           |

|--------------------|-------------------|-----------------------------|-------------------|------|-----------|

| Synta              | ax:               | ANDLW                       | k                 |      |           |

| Oper               | ands:             | $0 \le k \le 255$           | ;                 |      |           |

| Oper               | ation:            | (W) .AND.                   | $k \rightarrow W$ |      |           |

| Statu              | s Affected:       | N, Z                        |                   |      |           |

| Enco               | ding:             | 0000                        | 1011              | kkkk | kkkk      |

| Desc               | ription:          | The conter<br>8-bit literal |                   |      |           |

| Word               | ls:               | 1                           |                   |      |           |

| Cycle              | es:               | 1                           |                   |      |           |

| QC                 | ycle Activity:    |                             |                   |      |           |

|                    | Q1                | Q2                          | Q3                |      | Q4        |

|                    | Decode            | Read literal<br>'k'         | Proce<br>Data     |      | rite to W |

| <u>Exan</u>        | nple:             | ANDLW                       | 05Fh              |      |           |

| Before Instruction |                   | tion                        |                   |      |           |

| W =                |                   | = A3h                       |                   |      |           |

|                    | After Instruction | on                          |                   |      |           |

|                    | W                 | = 03h                       |                   |      |           |

# 25.2.2 EXTENDED INSTRUCTION SET

| ADD   | FSR            | Add Lite         | Add Literal to FSR                    |           |   |          |  |

|-------|----------------|------------------|---------------------------------------|-----------|---|----------|--|

| Synta | ax:            | ADDFSR           | f, k                                  |           |   |          |  |

| Oper  | ands:          | $0 \le k \le 63$ |                                       |           |   |          |  |

|       |                | f ∈ [ 0, 1,      | 2]                                    |           |   |          |  |

| Oper  | ation:         | FSR(f) + k       | $s \rightarrow FSR($                  | f)        |   |          |  |

| Statu | s Affected:    | None             |                                       |           |   |          |  |

| Enco  | ding:          | 1110             | 1000                                  | 1000 ffkk |   | kkkk     |  |

| Desc  | ription:       | The 6-bit        | The 6-bit literal 'k' is added to the |           |   |          |  |

|       |                | contents of      | contents of the FSR specified by 'f'. |           |   |          |  |

| Word  | ls:            | 1                | 1                                     |           |   |          |  |

| Cycle | es:            | 1                |                                       |           |   |          |  |

| QC    | ycle Activity: |                  |                                       |           |   |          |  |

|       | Q1             | Q2               | Q3                                    |           |   | Q4       |  |

|       | Decode         | Read             | Process                               |           | V | Vrite to |  |

|       |                | literal 'k'      | literal 'k' Data FS                   |           |   | FSR      |  |

|       |                |                  |                                       |           |   |          |  |

| Example: | ADDFSR | 2. | 23h |

|----------|--------|----|-----|

| Before Instru     |   |       |  |  |  |  |

|-------------------|---|-------|--|--|--|--|

| FSR2              | = | 03FFh |  |  |  |  |

| After Instruction |   |       |  |  |  |  |

| FSR2              | = | 0422h |  |  |  |  |

| ADDULNK Add Literal to FSR2 and Retur |                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                               | ADDULNK k                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Operands:                             | $0 \le k \le 63$                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Operation:                            | $FSR2 + k \rightarrow FSR2$ ,                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                       | $(TOS) \rightarrow PC$                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Status Affected:                      | None                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Encoding:                             | 1110 1000 11kk kkkk                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Description:                          | The 6-bit literal 'k' is added to the<br>contents of FSR2. A RETURN is then<br>executed by loading the PC with the<br>TOS.<br>The instruction takes two cycles to<br>execute; a NOP is performed during<br>the second cycle.<br>This may be thought of as a special<br>case of the ADDFSR instruction,<br>where f = 3 (binary '11'); it operates<br>only on FSR2. |  |  |  |

| Words:                                | 1                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Cycles:                               | 2                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| O Cycle Activity:                     |                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

Q Cycle Activity:

| Q1        | Q2          | Q3        | Q4        |

|-----------|-------------|-----------|-----------|

| Decode    | Read        | Process   | Write to  |

|           | literal 'k' | Data      | FSR       |

| No        | No          | No        | No        |

| Operation | Operation   | Operation | Operation |

0422h

(TOS)

Example: ADDULNK 23h

=

=

| Before Instru   | ction |       |

|-----------------|-------|-------|

| FSR2            | =     | 03FFh |

| PC              | =     | 0100h |

| After Instructi | ion   |       |

FSR2

PC

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction syntax then becomes: {label} instruction argument(s).

| PIC18LF2X/4XK22 |                              | <b>Standar</b><br>Operatir                                                                                           |       |       | nditions (<br>≥ 40°C- | ( <b>unless c</b><br>≦ Ta ≤ +12 |      | e stated)              |

|-----------------|------------------------------|----------------------------------------------------------------------------------------------------------------------|-------|-------|-----------------------|---------------------------------|------|------------------------|

| PIC18F2X/4XK22  |                              | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |       |       |                       |                                 |      |                        |

| Param           | Device Characteristics       | Тур                                                                                                                  | Тур   | Max   | Max                   | Units                           |      | Conditions             |

| No.             | Device onaracteristics       | +25°C                                                                                                                | +60°C | +85°C | +125°C                | onits                           | Vdd  | Notes                  |

| D015            | Comparators                  | 7                                                                                                                    | 7     | 18    | 18                    | μA                              | 1.8V |                        |

|                 |                              | 7                                                                                                                    | 7     | 18    | 18                    | μΑ                              | 3.0V | LP mode                |

|                 |                              | 7                                                                                                                    | 7     | 18    | 18                    | μA                              | 2.3V |                        |

|                 |                              | 7                                                                                                                    | 7     | 18    | 18                    | μA                              | 3.0V |                        |

|                 |                              | 8                                                                                                                    | 8     | 20    | 20                    | μA                              | 5.0V |                        |

| D016            | Comparators                  | 38                                                                                                                   | 38    | 95    | 95                    | μΑ                              | 1.8V |                        |

|                 |                              | 40                                                                                                                   | 40    | 105   | 105                   | μΑ                              | 3.0V | HP mode                |

|                 |                              | 39                                                                                                                   | 39    | 95    | 95                    | μA                              | 2.3V | TH HIOLE               |

|                 |                              | 40                                                                                                                   | 40    | 105   | 105                   | μA                              | 3.0V |                        |

|                 |                              | 40                                                                                                                   | 40    | 105   | 105                   | μA                              | 5.0V |                        |

| D017            | DAC                          | 14                                                                                                                   | 14    | 25    | 25                    | μΑ                              | 2.0V |                        |

|                 |                              | 20                                                                                                                   | 20    | 35    | 35                    | μΑ                              | 3.0V |                        |

|                 |                              | 15                                                                                                                   | 15    | 30    | 30                    | μA                              | 2.3V |                        |

|                 |                              | 20                                                                                                                   | 20    | 35    | 35                    | μA                              | 3.0V |                        |

|                 |                              | 32                                                                                                                   | 32    | 60    | 60                    | μA                              | 5.0V |                        |

| D018            | FVR <sup>(2)</sup>           | 15                                                                                                                   | 16    | 25    | 25                    | μΑ                              | 1.8V |                        |

|                 |                              | 15                                                                                                                   | 16    | 25    | 25                    | μΑ                              | 3.0V |                        |

|                 |                              | 28                                                                                                                   | 28    | 45    | 45 μA 2.3V            |                                 |      |                        |

|                 |                              | 31                                                                                                                   | 31    | 55    | 55                    | μΑ                              | 3.0V |                        |

|                 |                              | 66                                                                                                                   | 66    | 100   | 100                   | μΑ                              | 5.0V |                        |

| D013            | A/D Converter <sup>(3)</sup> | 185                                                                                                                  | 185   | 370   | 370                   | μΑ                              | 1.8V |                        |

|                 |                              | 210                                                                                                                  | 210   | 400   | 400                   | μΑ                              | 3.0V | A/D on, not converting |

|                 |                              | 200                                                                                                                  | 200   | 380   | 380                   | μΑ                              | 2.3V |                        |

|                 |                              | 210                                                                                                                  | 210   | 400   | 400                   | μΑ                              | 3.0V |                        |

|                 |                              | 250                                                                                                                  | 250   | 450   | 450                   | μA                              | 5.0V |                        |

# 27.2 DC Characteristics: Power-Down Current, PIC18(L)F2X/4XK22 (Continued)

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: On PIC18LF2X/4XK22 the BOR, HLVD and FVR enable internal band gap reference. With more than one of these modules enabled, the current consumption will be less than the sum of the specifications. On PIC18F2X/4XK22, the internal band gap reference is always enabled and its current consumption is included in the Power-down Base Current (IPD).

**3:** A/D converter differential currents apply only in Run mode. In Sleep or Idle mode both the ADC and the FRC turn off as soon as conversion (if any) is complete.

| Param.<br>No. | Sym             | Characteristic                | Min | Max | Units | Conditions                         |

|---------------|-----------------|-------------------------------|-----|-----|-------|------------------------------------|

| F10           | Fosc            | Oscillator Frequency Range    | 4   | 5   | MHz   | VDD < 2.7V,<br>-40°C to +85°C      |

|               |                 |                               | 4   | 4   | MHz   | VDD < 2.7V,<br>+85°C to +125°C     |

|               |                 |                               | 4   | 16  | MHz   | $2.7V \le VDD$ ,<br>-40°C to +85°C |

|               |                 |                               | 4   | 12  | MHz   | 2.7V ≤ VDD,<br>+85°C to +125°C     |

| F11           | Fsys            | On-Chip VCO System Frequency  | 16  | 20  | MHz   | VDD < 2.7V,<br>-40°C to +85°C      |

|               |                 |                               | 16  | 16  | MHz   | VDD < 2.7V,<br>+85°C to +125°C     |

|               |                 |                               | 16  | 64  | MHz   | $2.7V \le VDD$ ,<br>-40°C to +85°C |

|               |                 |                               | 16  | 48  | MHz   | 2.7V ≤ VDD,<br>+85°C to +125°C     |

| F12           | t <sub>rc</sub> | PLL Start-up Time (Lock Time) | —   | 2   | ms    |                                    |

# TABLE 27-8: PLL CLOCK TIMING SPECIFICATIONS

# TABLE 27-9: AC CHARACTERISTICS:INTERNAL OSCILLATORS ACCURACY PIC18(L)F46K22

| Standard Operating Conditions (unless otherwise stated) |  |  |  |   |  |  |  |

|---------------------------------------------------------|--|--|--|---|--|--|--|

| Operating temperature $-40^{\circ}C \le TA \le$         |  |  |  | С |  |  |  |

|                                                         |  |  |  |   |  |  |  |

| Param.<br>No. | Characteristics                                          | Freq.<br>Tolerance | Min | Тур† | Мах | Units | Conditions                                                        |

|---------------|----------------------------------------------------------|--------------------|-----|------|-----|-------|-------------------------------------------------------------------|