Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 30x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45k22-e-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-2: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator     | Power-up <sup>(2)</sup> ar                             | nd Brown-out                    | Exit from                       |

|----------------|--------------------------------------------------------|---------------------------------|---------------------------------|

| Configuration  | <b>PWRTEN</b> = 0                                      | PWRTEN = 1                      | Power-Managed Mode              |

| HSPLL          | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> |

| HS, XT, LP     | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                       | 1024 Tosc                       |

| EC, ECIO       | 66 ms <sup>(1)</sup>                                   | _                               | —                               |

| RC, RCIO       | 66 ms <sup>(1)</sup>                                   | _                               | —                               |

| INTIO1, INTIO2 | 66 ms <sup>(1)</sup>                                   |                                 | —                               |

Note 1: 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.2: 2 ms is the nominal time required for the PLL to lock.

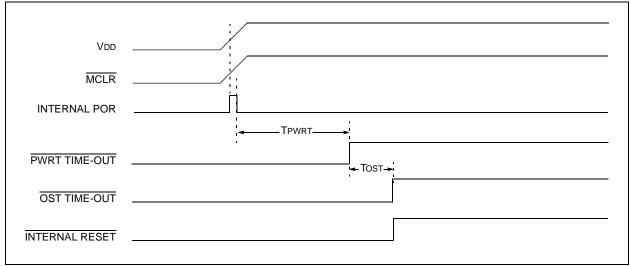

### FIGURE 4-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD, VDD RISE < TPWRT)

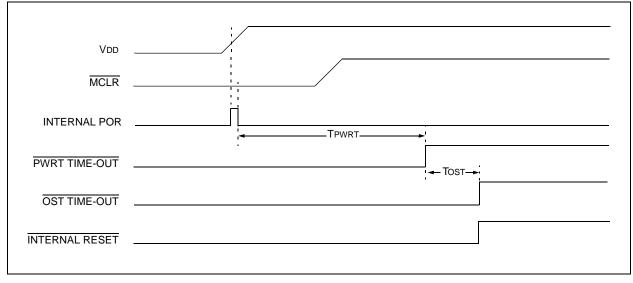

# FIGURE 4-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

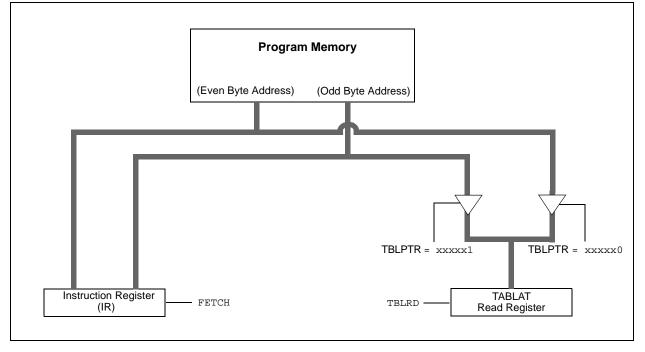

#### 6.4 Reading the Flash Program Memory

The TBLRD instruction retrieves data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation. The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU |   | Load TBLPTR with the base<br>address of the word |

|-----------|----------------|----------------------------|---|--------------------------------------------------|

|           | MOVLW          | CODE_ADDR_HIGH             | ' | address of the word                              |

|           | MOVWF          | TBLPTRH                    |   |                                                  |

|           |                |                            |   |                                                  |

|           | MOVLW          | CODE_ADDR_LOW              |   |                                                  |

|           | MOVWF          | TBLPTRL                    |   |                                                  |

| READ_WORD |                |                            |   |                                                  |

|           | TBLRD*+        |                            | ; | read into TABLAT and increment                   |

|           | MOVF           | TABLAT, W                  | ; | get data                                         |

|           | MOVWF          | WORD_EVEN                  |   |                                                  |

|           | TBLRD*+        |                            | ; | read into TABLAT and increment                   |

|           | MOVFW          | TABLAT, W                  | ; | get data                                         |

|           | MOVF           | WORD_ODD                   |   |                                                  |

|           |                |                            |   |                                                  |

| Name    | Bit 7          | Bit 6     | Bit 5       | Bit 4               | Bit 3               | Bit 2   | Bit 1  | Bit 0   | Register<br>on Page |

|---------|----------------|-----------|-------------|---------------------|---------------------|---------|--------|---------|---------------------|

| ANSELB  | —              | —         | ANSB5       | ANSB4               | ANSB3               | ANSB2   | ANSB1  | ANSB0   | 150                 |

| ECCP2AS | CCP2ASE        |           | CCP2AS<2:0> | >                   | PSS2AC<             | 1:0>    | PSS2B  | BD<1:0> | 202                 |

| CCP2CON | P2M            | <1:0>     | DC2B        | <1:0>               |                     | CCP2M<3 | :0>    |         | 198                 |

| ECCP3AS | <b>CCP3ASE</b> | (         | CCP3AS<2:0> |                     | PSS3AC<             | 1:0>    | PSS3B  | SD<1:0> | 202                 |

| CCP3CON | P3M            | <1:0>     | DC3B-       | <1:0>               |                     | CCP3M<3 | :0>    |         | 198                 |

| INTCON  | GIE/GIEH       | PEIE/GIEL | TMR0IE      | INT0IE              | RBIE                | TMR0IF  | INT0IF | RBIF    | 109                 |

| INTCON2 | RBPU           | INTEDG0   | INTEDG1     | INTEDG2             | —                   | TMR0IP  | _      | RBIP    | 110                 |

| INTCON3 | INT2IP         | INT1IP    | _           | INT2IE              | INT1IE              | _       | INT2IF | INT1IF  | 111                 |

| IOCB    | IOCB7          | IOCB6     | IOCB5       | IOCB4               | —                   |         | _      | _       | 153                 |

| LATB    | LATB7          | LATB6     | LATB5       | LATB4               | LATB3               | LATB2   | LATB1  | LATB0   | 152                 |

| PORTB   | RB7            | RB6       | RB5         | RB4                 | RB3                 | RB2     | RB1    | RB0     | 148                 |

| SLRCON  | —              |           |             | SLRE <sup>(1)</sup> | SLRD <sup>(1)</sup> | SLRC    | SLRB   | SLRA    | 153                 |

| T1GCON  | TMR1GE         | T1GPOL    | T1GTM       | T1GSPM              | T1GGO/DONE          | T1GVAL  | T1GS   | S<1:0>  | 167                 |

| T3CON   | TMR3C          | CS<1:0>   | T3CKP       | S<1:0>              | T3SOSCEN            | T3SYNC  | T3RD16 | TMR3ON  | 166                 |

| T5GCON  | TMR5GE         | T5GPOL    | T5GTM       | T5GSPM              | T5GGO/DONE          | T5GVAL  | T5GS   | S<1:0>  | 167                 |

| TRISB   | TRISB7         | TRISB6    | TRISB5      | TRISB4              | TRISB3              | TRISB2  | TRISB1 | TRISB0  | 151                 |

| WPUB    | WPUB7          | WPUB6     | WPUB5       | WPUB4               | WPUB3               | WPUB2   | WPUB1  | WPUB0   | 152                 |

#### TABLE 10-6: REGISTERS ASSOCIATED WITH PORTB

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTB.

**Note 1:** Available on PIC18(L)F4XK22 devices.

#### TABLE 10-7: CONFIGURATION REGISTERS ASSOCIATED WITH PORTB

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2              | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------|-------|-------|-------|--------|--------------------|--------|--------|---------------------|

| CONFIG3H | MCLRE | —     | P2BMX | T3CMX | HFOFST | ССРЗМХ             | PBADEN | CCP2MX | 348                 |

| CONFIG4L | DEBUG | XINST | _     | _     | _      | LVP <sup>(1)</sup> | —      | STRVEN | 349                 |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTB.

**Note 1:** Can only be changed when in high voltage programming mode.

| REGISTER I       | U-Z. FURI   | C. FURIERI        | EGISTER     |                    |                         |                         |                         |

|------------------|-------------|-------------------|-------------|--------------------|-------------------------|-------------------------|-------------------------|

| U-0              | U-0         | U-0               | U-0         | R/W-u/x            | R/W-u/x                 | R/W-u/x                 | R/W-u/x                 |

| _                | —           | —                 | —           | RE3 <sup>(1)</sup> | RE2 <sup>(2), (3)</sup> | RE1 <sup>(2), (3)</sup> | RE0 <sup>(2), (3)</sup> |

| bit 7            |             |                   |             |                    |                         |                         | bit C                   |

|                  |             |                   |             |                    |                         |                         |                         |

| Legend:          |             |                   |             |                    |                         |                         |                         |

| R = Readable     | bit         | W = Writable      | bit         | U = Unimpler       | mented bit, read        | d as '0'                |                         |

| '1' = Bit is set |             | '0' = Bit is clea | ared        | x = Bit is unk     | nown                    |                         |                         |

| -n/n = Value at  | POR and BOR | R/Value at all o  | ther Resets |                    |                         |                         |                         |

|                  |             |                   |             |                    |                         |                         |                         |

|                  |             |                   |             |                    |                         |                         |                         |

#### REGISTER 10-2: PORTE: PORTE REGISTER

bit 3 **RE3:** PORTE Input bit value<sup>(1)</sup>

bit 2-0 **RE<2:0>:** PORTE I/O bit values<sup>(2), (3)</sup>

**Note 1:** Port is available as input only when MCLRE = 0.

- 2: Writes to PORTx are written to corresponding LATx register. Reads from PORTx register is return of I/O pin values.

- 3: Available on PIC18(L)F4XK22 devices.

## REGISTER 10-3: ANSELA – PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| —     | —   | ANSA5 | —   | ANSA3 | ANSA2 | ANSA1 | ANSA0 |

| bit 7 |     |       |     |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                   |

|---------|----------------------------------------------------------------------------------------------|

| bit 5   | ANSA5: RA5 Analog Select bit                                                                 |

|         | <ul><li>1 = Digital input buffer disabled</li><li>0 = Digital input buffer enabled</li></ul> |

| bit 4   | Unimplemented: Read as '0'                                                                   |

| bit 3-0 | ANSA<3:0>: RA<3:0> Analog Select bit                                                         |

|         | 1 = Digital input buffer disabled                                                            |

0 = Digital input buffer enabled

# 15.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP1 AND MSSP2) MODULE

#### 15.1 Master SSPx (MSSPx) Module Overview

The Master Synchronous Serial Port (MSSPx) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSPx module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy chain connection of slave devices

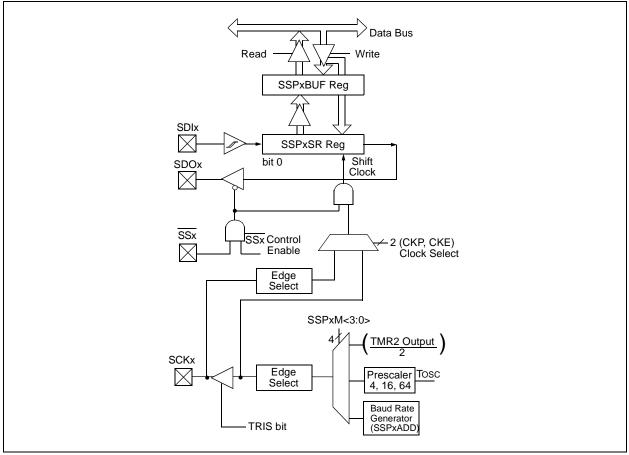

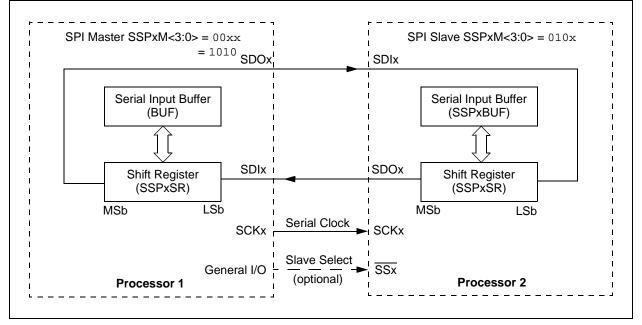

Figure 15-1 is a block diagram of the SPI interface module.

#### FIGURE 15-1: MSSPx BLOCK DIAGRAM (SPI MODE)

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

The MSSPx consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF of the SSPxSTAT register, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL of the SSPxCON1 register, will be

set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSPx interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCLx line, is called clock stretching. Clock stretching give slave devices a mechanism to control the flow of data. When this detection is used on the SDAx line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

#### 15.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCLx clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCLx line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCLx connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

### 15.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDAx data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels don't match, loses arbitration, and must stop transmitting on the SDAx line.

For example, if one transmitter holds the SDAx line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDAx line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDAx line. If this transmitter is also a master device, it also must stop driving the SCLx line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDAx line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

# 15.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception (Figure 15-29) is enabled by programming the Receive Enable bit, RCEN, of the SSPxCON2 register.

Note: The MSSPx module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCLx pin changes (high-to-low/ low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCLx low. The MSSPx is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN, of the SSPxCON2 register.

### 15.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

#### 15.6.7.2 SSPxOV Status Flag

In receive operation, the SSPxOV bit is set when eight bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

# 15.6.7.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### 15.6.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. User writes SSPxBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDAx pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 8. User sets the RCEN bit of the SSPxCON2 register and the Master clocks in a byte from the slave.

- 9. After the 8th falling edge of SCLx, SSPxIF and BF are set.

- 10. Master clears SSPxIF and reads the received byte from SSPxUF, clears BF.

- 11. Master sets ACK value sent to slave in ACKDT bit of the SSPxCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Masters ACK is clocked out to the slave and SSPxIF is set.

- 13. User clears SSPxIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

#### EXAMPLE 19-1: SETUP FOR CTMU CALIBRATION ROUTINES

```

#include "pl8cxxx.h"

void setup(void)

{ //CTMUCONH/1 - CTMU Control registers

CTMUCONH = 0x00; //make sure CTMU is disabled

CTMUCONL = 0x90;

//CTMU continues to run when emulator is stopped,CTMU continues

//to run in idle mode, Time Generation mode disabled, Edges are blocked

//No edge sequence order, Analog current source not grounded, trigger

//output disabled, Edge2 polarity = positive level, Edge2 source =

//source 0, Edgel polarity = positive level, Edgel source = source 0,

//CTMUICON - CTMU Current Control Register

CTMUICON = 0x01; //0.55uA, Nominal - No Adjustment

//Set up AD converter;

TRISA=0x04;

//set channel 2 as an input

// Configure AN2 as an analog channel

ANSELAbits ANSA2=1;

TRISAbits.TRISA2=1;

// ADCON2

ADCON2bits.ADFM=1; // Results format 1= Right justified

ADCON2bits.ACQT=1; // Acquition time 7 = 20TAD 2 = 4TAD 1=2TAD

ADCON2bits.ADCS=2; // Clock conversion bits 6= FOSC/64 2=FOSC/

// Clock conversion bits 6= FOSC/64 2=FOSC/32

ADCON2bits.ADCS=2;

// ADCON1

ADCON1bits.PVCFG0 =0;

// Vref+ = AVdd

ADCON1bits.NVCFG1 =0;

// Vref- = AVss

// ADCON0

// Select ADC channel

ADCON0bits.CHS=2;

ADCON0bits.ADON=1; // Turn on ADC

}

```

# 19.9 Effects of a Reset on CTMU

Upon Reset, all registers of the CTMU are cleared. This leaves the CTMU module disabled, its current source is turned off and all configuration options return to their default settings. The module needs to be re-initialized following any Reset.

If the CTMU is in the process of taking a measurement at the time of Reset, the measurement will be lost. A partial charge may exist on the circuit that was being measured, and should be properly discharged before the CTMU makes subsequent attempts to make a measurement. The circuit is discharged by setting and then clearing the IDISSEN bit (CTMUCONH<1>) while the A/D Converter is connected to the appropriate channel.

### 19.10 Registers

There are three control registers for the CTMU:

- CTMUCONH

- CTMUCONL

- CTMUICON

The CTMUCONH and CTMUCONL registers (Register 19-1 and Register 19-2) contain control bits for configuring the CTMU module edge source selection, edge source polarity selection, edge sequencing, A/D trigger, analog circuit capacitor discharge and enables. The CTMUICON register (Register 19-3) has bits for selecting the current source range and current source trim.

# 19.11 Register Definitions: CTMU Control

#### REGISTER 19-1: CTMUCONH: CTMU CONTROL REGISTER 0

|        |     |          |       |       | •        |         |        |

|--------|-----|----------|-------|-------|----------|---------|--------|

| R/W-0  | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0    | R/W-0   | U-0    |

| CTMUEN |     | CTMUSIDL | TGEN  | EDGEN | EDGSEQEN | IDISSEN | CTTRIG |

| bit 7  |     |          |       |       |          |         | bit 0  |

| Legend:    |          |                                                                  |                        |                    |

|------------|----------|------------------------------------------------------------------|------------------------|--------------------|

| R = Read   | able bit | W = Writable bit                                                 | U = Unimplemented bit  | , read as '0'      |

| -n = Value | e at POR | '1' = Bit is set                                                 | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7      | CTMUEN   | I: CTMU Enable bit                                               |                        |                    |

|            |          | ule is enabled<br>ule is disabled                                |                        |                    |

| bit 6      | Unimple  | mented: Read as '0'                                              |                        |                    |

| bit 5      | CTMUSI   | DL: Stop in Idle Mode bit                                        |                        |                    |

|            |          | ontinue module operation wh                                      |                        |                    |

| bit 4      | TGEN: T  | ime Generation Enable bit                                        |                        |                    |

|            |          | bles edge delay generation<br>bles edge delay generation         |                        |                    |

| bit 3      | EDGEN:   | Edge Enable bit                                                  |                        |                    |

|            | 0        | es are not blocked<br>es are blocked                             |                        |                    |

| bit 2      | EDGSEC   | EN: Edge Sequence Enable                                         | e bit                  |                    |

|            | •        | e 1 event must occur before l<br>dge sequence is needed          | Edge 2 event can occur |                    |

| bit 1      | IDISSEN  | : Analog Current Source Cor                                      | ntrol bit              |                    |

|            |          | og current source output is g<br>og current source output is n   |                        |                    |

| bit 0      | CTTRIG:  | CTMU Special Event Trigge                                        | r Control Bit          |                    |

|            |          | IU Special Event Trigger is ei<br>IU Special Event Trigger is di |                        |                    |

| U-0                                   | U-0 | U-0               | R/W-0 | R/W-0          | R/W-0            | R/W-0            | R/W-0       |

|---------------------------------------|-----|-------------------|-------|----------------|------------------|------------------|-------------|

| —                                     | —   | —                 |       |                | DACR<4:0>        |                  |             |

| bit 7                                 |     |                   |       |                |                  |                  | bit 0       |

|                                       |     |                   |       |                |                  |                  |             |

| Legend:                               |     |                   |       |                |                  |                  |             |

| R = Readable bit W = Writable bit     |     |                   |       | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is unchanged x = Bit is unkno |     |                   | nown  | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set                      |     | '0' = Bit is clea | ared  |                |                  |                  |             |

#### REGISTER 22-2: VREFCON2: VOLTAGE REFERENCE CONTROL REGISTER 1

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DACR<4:0>: DAC Voltage Output Select bits VOUT = ((VSRC+) - (VSRC-))\*(DACR<4:0>/(2<sup>5</sup>)) + VSRC-

#### TABLE 22-1: REGISTERS ASSOCIATED WITH DAC MODULE

| Name     | Bit 7 | Bit 6  | Bit 5     | Bit 4     | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on Page |

|----------|-------|--------|-----------|-----------|-------|--------|-------|--------|---------------------|

| VREFCON0 | FVREN | FVRST  | FVRS<1:0> |           | _     | _      | _     | _      | 332                 |

| VREFCON1 | DACEN | DACLPS | DACOE     | _         | DACPS | S<1:0> | _     | DACNSS | 335                 |

| VREFCON2 | _     | _      | _         | DACR<4:0> |       |        |       | 336    |                     |

**Legend:** — = Unimplemented locations, read as '0'. Shaded bits are not used by the DAC module.

| U-0           | U-0                                                                                                                                                                                       | U-0                                                                                                                                                                                                                | R/P-1                                                                                                     | R/P-1                                   | R/P-1                     | R/P-1      | R/P-1                 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------|------------|-----------------------|

| _             | _                                                                                                                                                                                         | _                                                                                                                                                                                                                  | BORV                                                                                                      | ′<1:0> <sup>(1)</sup>                   | BOREN<1:0> <sup>(2)</sup> |            | PWRTEN <sup>(2)</sup> |

| bit 7         |                                                                                                                                                                                           |                                                                                                                                                                                                                    |                                                                                                           |                                         |                           |            | bit                   |

|               |                                                                                                                                                                                           |                                                                                                                                                                                                                    |                                                                                                           |                                         |                           |            |                       |

| Legend:       | 1.12                                                                                                                                                                                      |                                                                                                                                                                                                                    |                                                                                                           |                                         |                           | <b>0</b> 1 |                       |

| R = Readable  |                                                                                                                                                                                           | P = Programma                                                                                                                                                                                                      | able bit                                                                                                  | •                                       | nted bit, read as         | 0,         |                       |

| -n = Value wh | nen device is unprogr                                                                                                                                                                     | ammed                                                                                                                                                                                                              |                                                                                                           | x = Bit is unkno                        | wn                        |            |                       |

|               |                                                                                                                                                                                           |                                                                                                                                                                                                                    |                                                                                                           |                                         |                           |            |                       |

| bit 7-5       | Unimplementee                                                                                                                                                                             | d: Read as '0'                                                                                                                                                                                                     |                                                                                                           |                                         |                           |            |                       |

| L 4 4 0       |                                                                                                                                                                                           |                                                                                                                                                                                                                    | / IA I I I (1)                                                                                            |                                         |                           |            |                       |

| bit 4-3       |                                                                                                                                                                                           | own-out Reset \                                                                                                                                                                                                    | oltage bits                                                                                               |                                         |                           |            |                       |

| DIT 4-3       | 11 = VBOR set to                                                                                                                                                                          | o 1.9V nominal                                                                                                                                                                                                     | oltage bits(")                                                                                            |                                         |                           |            |                       |

| dit 4-3       | 11 = VBOR set to<br>10 = VBOR set to                                                                                                                                                      | o 1.9V nominal<br>o 2.2V nominal                                                                                                                                                                                   | oltage bits                                                                                               |                                         |                           |            |                       |

| dit 4-3       | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to                                                                                                                                  | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal                                                                                                                                                                 | Oltage Dits."                                                                                             |                                         |                           |            |                       |

|               | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to                                                                                                              | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal                                                                                                                                              | J                                                                                                         |                                         |                           |            |                       |

|               | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br>BOREN<1:0>: E                                                                                             | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset                                                                                                                           | Enable bits <sup>(2)</sup>                                                                                | / (SBOREN is dis                        | abled)                    |            |                       |

|               | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br><b>BOREN&lt;1:0&gt;:</b> E<br>11 = Brown-ou                                                               | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset<br>tt Reset enabled                                                                                                       | Enable bits <sup>(2)</sup><br>in hardware only                                                            | / (SBOREN is dis<br>/ and disabled in { |                           |            |                       |

|               | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br>BOREN<1:0>: E<br>11 = Brown-ou<br>10 = Brown-ou                                                           | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset<br>tt Reset enabled                                                                                                       | Enable bits <sup>(2)</sup><br>in hardware only                                                            | ۲ (SBOREN is dis<br>۲ and disabled in S |                           |            |                       |

|               | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br><b>BOREN&lt;1:0&gt;:</b> E<br>11 = Brown-ou<br>10 = Brown-ou<br>(SBOREN                                   | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset<br>it Reset enabled<br>t Reset enabled<br>N is disabled)                                                                  | Enable bits <sup>(2)</sup><br>in hardware only<br>in hardware only                                        |                                         | Sleep mode                |            |                       |

| bit 2-1       | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br><b>BOREN&lt;1:0&gt;:</b> E<br>11 = Brown-ou<br>10 = Brown-ou<br>(SBOREN                                   | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset<br>it Reset enabled<br>it Reset enabled<br>v is disabled)<br>it Reset enabled                                             | Enable bits <sup>(2)</sup><br>in hardware only<br>in hardware only<br>and controlled b                    | y and disabled in S<br>y software (SBOF | Sleep mode                |            |                       |

|               | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br>BOREN<1:0>: E<br>11 = Brown-ou<br>10 = Brown-ou<br>(SBOREN<br>01 = Brown-ou                               | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset<br>tt Reset enabled<br>tt Reset enabled<br>v is disabled)<br>tt Reset enabled<br>tt Reset disabled                        | Enable bits <sup>(2)</sup><br>in hardware only<br>in hardware only<br>and controlled b<br>in hardware and | y and disabled in S<br>y software (SBOF | Sleep mode                |            |                       |

| bit 2-1       | 11 = VBOR set to<br>10 = VBOR set to<br>01 = VBOR set to<br>00 = VBOR set to<br><b>BOREN&lt;1:0&gt;:</b> F<br>11 = Brown-ou<br>10 = Brown-ou<br>(SBOREN<br>01 = Brown-ou<br>00 = Brown-ou | o 1.9V nominal<br>o 2.2V nominal<br>o 2.5V nominal<br>o 2.85V nominal<br>Brown-out Reset<br>it Reset enabled<br>it Reset enabled<br>v is disabled)<br>it Reset enabled<br>it Reset disabled<br>er-up Timer Enabled | Enable bits <sup>(2)</sup><br>in hardware only<br>in hardware only<br>and controlled b<br>in hardware and | y and disabled in S<br>y software (SBOF | Sleep mode                |            |                       |

2: The Power-up Timer is decoupled from Brown-out Reset, allowing these features to be independently controlled.

#### 24.5.1 PROGRAM MEMORY CODE PROTECTION

The program memory may be read to or written from any location using the table read and table write instructions. The device ID may be read with table reads. The Configuration registers may be read and written with the table read and table write instructions.

In Normal execution mode, the CPn bits have no direct effect. CPn bits inhibit external reads and writes. A block of user memory may be protected from table writes if the WRTn Configuration bit is '0'. The EBTRn bits control table reads. For a block of user memory with the EBTRn bit cleared to '0', a table READ instruction that executes from within that block is allowed to read. A table read instruction that executes from a location outside of that block is not allowed to read and will result in reading '0's. Figures 24-3 through 24-5 illustrate table write and table read protection.

| Note: | Code protection bits may only be written         |

|-------|--------------------------------------------------|

|       | to a '0' from a '1' state. It is not possible to |

|       | write a '1' to a bit in the '0' state. Code pro- |

|       | tection bits are only set to '1' by a full chip  |

|       | erase or block erase function. The full chip     |

|       | erase and block erase functions can only         |

|       | be initiated via ICSP™ or an external            |

|       | programmer.                                      |

# FIGURE 24-3: TABLE WRITE (WRTn) DISALLOWED

| <b>Register Values</b>       | Program Memory                      | Configuration Bit Settings |

|------------------------------|-------------------------------------|----------------------------|

|                              | 000000<br>0007Ff<br>000800          | WRTB, EBTRB = 11<br>Th     |

| TBLPTR = 0008FFh             | ▶┍╼                                 | WRT0, EBTR0 = 01           |

| PC = 001FFEh                 | TBLWT* 001FFI 002000                |                            |

|                              | 003FFI                              |                            |

| PC = 005FFEh                 | TBLWT* 005FFI 006000                |                            |

|                              |                                     | WRT3, EBTR3 = 11           |

| Results: All table writes di | sabled to Blockn whenever WRTn = 0. | -11                        |

# PIC18(L)F2X/4XK22

| SUBLW                | Subtract W from literal | SUBWF                              | Subt       | Subtract W from f |                      |                                            |                |

|----------------------|-------------------------|------------------------------------|------------|-------------------|----------------------|--------------------------------------------|----------------|

| Syntax:              | SUBLW k                 |                                    |            | Syntax:           | SUBW                 | /F f {,d {,a}}                             |                |

| Operands:            | $0 \le k \le 255$       |                                    |            | Operands:         | $0 \le f \le$        | 255                                        |                |

| Operation:           | $k - (W) \rightarrow V$ | W                                  |            |                   | d ∈ [0               | -                                          |                |

| Status Affected:     | N, OV, C, E             | DC, Z                              |            | Operation:        | a ∈ [0<br>/f) ()     |                                            |                |

| Encoding:            | 0000                    | 1000 kkł                           | k kkkk     | Status Affect     |                      | V) $\rightarrow$ dest                      |                |

| Description          |                         | acted from the                     |            | Encoding:         |                      | C, DC, Z                                   | ff ffff        |

|                      | literal 'k'. Tl         | he result is pla                   | aced in W. | Description:      |                      | ct W from registe                          |                |

| Words:               | 1                       |                                    |            | Description.      |                      | ement method). I                           |                |

| Cycles:              | 1                       |                                    |            |                   |                      | s stored in W. If                          |                |

| Q Cycle Activity:    |                         |                                    |            |                   | result<br>(defau     | is stored back in<br>It)                   | register 'f'   |

| Q1                   | Q2                      | Q3                                 | Q4         |                   | lf 'a' is            | '0', the Access E                          |                |

| Decode               | Read<br>literal 'k'     | Process<br>Data                    | Write to W |                   | to sele              | ed. If 'a' is '1', the<br>ect the GPR bank |                |

| Example 1:           | SUBLW 0                 | 2h                                 |            |                   |                      | '0' and the exten<br>enabled, this instr   |                |

| Before Instruc       |                         |                                    |            |                   |                      | es in Indexed Lite                         |                |

| W<br>C               | = 01h<br>= ?            |                                    |            |                   |                      | ssing mode wher                            |                |

| After Instructi<br>W | on<br>= 01h             |                                    |            |                   |                      | (5Fh). See Section<br>Oriented and Bit     |                |

| С                    | = 1 ; res               | sult is positive                   | •          |                   | Instru               | ctions in Indexed                          |                |

| Z<br>N               | = 0<br>= 0              |                                    |            |                   |                      | ' for details.                             |                |

| Example 2:           | SUBLW 0                 | 2h                                 |            | Words:            | 1                    |                                            |                |

| Before Instruc       |                         |                                    |            | Cycles:           | 1                    |                                            |                |

| W<br>C               | = 02h<br>= ?            |                                    |            | Q Cycle Ac        | -                    | 03                                         | 04             |

| After Instructi      |                         |                                    |            | 1                 | Q1 Q2<br>code Read   | Q3<br>Process                              | Q4<br>Write to |

| W<br>C               | = 00h<br>= 1 ; res      | sult is zero                       |            | 200               | register             |                                            | destination    |

| ZN                   | = 1<br>= 0              |                                    |            | Example 1:        | SUBWI                | REG, 1, 0                                  |                |

| Example 3:           | SUBLW 0                 | 2h                                 |            |                   | Instruction          |                                            |                |

| Before Instruc       | ction                   |                                    |            | R<br>W            | EG = 3<br>/ = 2      |                                            |                |

| W<br>C               | = 03h<br>= ?            |                                    |            | C<br>After Ir     | = ?                  |                                            |                |

| After Instructi      | on                      |                                    |            | R                 | EG = 1               |                                            |                |

| W<br>C               |                         | 2's complement<br>sult is negative |            | W<br>C            |                      | ; result is positiv                        | /e             |

| Z<br>N               | = 0<br>= 1              | 5                                  |            | Z                 | = 0                  | · · ·                                      |                |

|                      |                         |                                    |            | Example 2:        | -                    | REG, 0, 0                                  |                |

|                      |                         |                                    |            | Before            | Instruction          |                                            |                |

|                      |                         |                                    |            | R<br>W            | EG = 2<br>/ = 2      |                                            |                |

|                      |                         |                                    |            | С                 | = ?                  |                                            |                |

|                      |                         |                                    |            |                   | nstruction<br>EG = 2 |                                            |                |

|                      |                         |                                    |            | W<br>C            |                      | ; result is zero                           |                |

|                      |                         |                                    |            | Z                 | = 1                  | ,                                          |                |

|                      |                         |                                    |            | Example 3:        | -                    | REG, 1, 0                                  |                |

|                      |                         |                                    |            |                   | Instruction          | <u>ла</u> с, т, О                          |                |

|                      |                         |                                    |            | R<br>W<br>C       |                      |                                            |                |

|                      |                         |                                    |            | After Ir          | nstruction           |                                            |                |

|                      |                         |                                    |            | R                 | EG = FFh             | ;(2's compleme                             | nt)            |

|                      |                         |                                    |            |                   |                      |                                            |                |

|                      |                         |                                    |            | C                 | = 0                  | ; result is negat                          | ve             |

# 27.4 DC Characteristics: RC Idle Supply Current, PIC18(L)F2X/4XK22

| PIC18LF2X/4XK22              |                             | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |    |                 |            |                                            |  |  |

|------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------|------|----|-----------------|------------|--------------------------------------------|--|--|

| PIC18F2X/4XK22               |                             | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                 |      |    |                 |            |                                            |  |  |

| Param Device Characteristics |                             | Typ Max Units Condition                                                                                              |      |    |                 | 5          |                                            |  |  |

| D045                         | Supply Current (IDD)(1),(2) | 0.5                                                                                                                  | 18   | μΑ | -40°C           | VDD = 1.8V | Fosc = 31 kHz                              |  |  |

|                              |                             | 0.6                                                                                                                  | 18   | μΑ | +25°C           |            | ( <b>RC_IDLE</b> mode,<br>LFINTOSC source) |  |  |

|                              |                             | 0.7                                                                                                                  | —    | μΑ | +60°C           |            | LFINTOSC Source)                           |  |  |

|                              |                             | 0.75                                                                                                                 | 20   | μΑ | +85°C           |            |                                            |  |  |

|                              |                             | 2.3                                                                                                                  | 22   | μΑ | +125°C          |            |                                            |  |  |

| D046                         |                             | 1.1                                                                                                                  | 20   | μΑ | -40°C           | VDD = 3.0V |                                            |  |  |

|                              |                             | 1.2                                                                                                                  | 20   | μΑ | +25°C           |            |                                            |  |  |

|                              |                             | 1.3                                                                                                                  | —    | μΑ | +60°C           |            |                                            |  |  |

|                              |                             | 1.4                                                                                                                  | 22   | μΑ | +85°C           |            |                                            |  |  |

|                              |                             | 3.2                                                                                                                  | 25   | μΑ | +125°C          |            |                                            |  |  |

| D047                         |                             | 17                                                                                                                   | 30   | μΑ | -40°C           | VDD = 2.3V | Fosc = 31 kHz                              |  |  |

|                              |                             | 13                                                                                                                   | 30   | μΑ | +25°C           |            | ( <b>RC_IDLE</b> mode,<br>LFINTOSC source) |  |  |

|                              |                             | 14                                                                                                                   | 30   | μΑ | +85°C           |            |                                            |  |  |

|                              |                             | 15                                                                                                                   | 45   | μΑ | +125°C          |            |                                            |  |  |

| D048                         |                             | 19                                                                                                                   | 35   | μΑ | -40°C           | VDD = 3.0V |                                            |  |  |

|                              |                             | 15                                                                                                                   | 35   | μΑ | +25°C           |            |                                            |  |  |

|                              |                             | 16                                                                                                                   | 35   | μΑ | +85°C           |            |                                            |  |  |

|                              |                             | 17                                                                                                                   | 50   | μΑ | +125°C          |            |                                            |  |  |

| D049                         |                             | 21                                                                                                                   | 40   | μΑ | -40°C           | VDD = 5.0V |                                            |  |  |

|                              |                             | 15                                                                                                                   | 40   | μΑ | +25°C           |            |                                            |  |  |

|                              |                             | 16                                                                                                                   | 40   | μΑ | +85°C           |            |                                            |  |  |

|                              |                             | 18                                                                                                                   | 60   | μΑ | +125°C          |            |                                            |  |  |

| D050                         |                             | 0.11                                                                                                                 | 0.20 | mA | -40°C to +125°C | VDD = 1.8V | Fosc = 500 kHz                             |  |  |

| D051                         |                             | 0.12                                                                                                                 | 0.25 | mA | -40°C to +125°C | VDD = 3.0V | ( <b>RC_IDLE</b> mode,<br>MFINTOSC source) |  |  |

| D052                         |                             | 0.14                                                                                                                 | 0.21 | mA | -40°C to +125°C | VDD = 2.3V | Fosc = 500 kHz                             |  |  |

| D053                         |                             | 0.15                                                                                                                 | 0.25 | mA | -40°C to +125°C | VDD = 3.0V | ( <b>RC_IDLE</b> mode,<br>MFINTOSC source) |  |  |

| D054                         |                             | 0.20                                                                                                                 | 0.31 | mA | -40°C to +125°C | VDD = 5.0V |                                            |  |  |

**Note 1:** The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

Test condition: All Peripheral Module Control bits in PMD0, PMD1 and PMD2 set to '1'.

2: The test conditions for all IDD measurements in active operation mode are:

All I/O pins set as outputs driven to Vss;

$\overline{MCLR} = VDD;$

OSC1 = external square wave, from rail-to-rail (PRI\_RUN and PRI\_IDLE only).

# 27.11 AC (Timing) Characteristics

# 27.11.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created using one of the following formats:

| 1. TppS2p                | pS                                 | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|--------------------------|------------------------------------|-----------|----------------------------------------|

| 2. TppS                  |                                    | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                        |                                    |           |                                        |

| F                        | Frequency                          | Т         | Time                                   |

| Lowercase                | e letters (pp) and their meanings: |           |                                        |

| рр                       |                                    |           |                                        |

| сс                       | CCP1                               | osc       | OSC1                                   |

| ck                       | CLKOUT                             | rd        | RD                                     |

| cs                       | CS                                 | rw        | RD or WR                               |

| di                       | SDI                                | sc        | SCK                                    |

| do                       | SDO                                | SS        | SS                                     |

| dt                       | Data in                            | tO        | ТОСКІ                                  |

| io                       | I/O port                           | t1        | T13CKI                                 |

| mc                       | MCLR                               | wr        | WR                                     |

| Uppercase                | e letters and their meanings:      |           |                                        |

| S                        |                                    |           |                                        |

| F                        | Fall                               | Р         | Period                                 |

| Н                        | High                               | R         | Rise                                   |

| 1                        | Invalid (High-impedance)           | V         | Valid                                  |

| L                        | Low                                | Z         | High-impedance                         |

| I <sup>2</sup> C only    |                                    |           |                                        |

| AA                       | output access                      | High      | High                                   |

| BUF                      | Bus free                           | Low       | Low                                    |

| TCC:ST (I <sup>2</sup> C | Specifications only)               |           |                                        |

| CC                       |                                    |           |                                        |

| HD                       | Hold                               | SU        | Setup                                  |

| ST                       |                                    |           |                                        |

| DAT                      | DATA input hold                    | STO       | Stop condition                         |

| STA                      | Start condition                    |           |                                        |

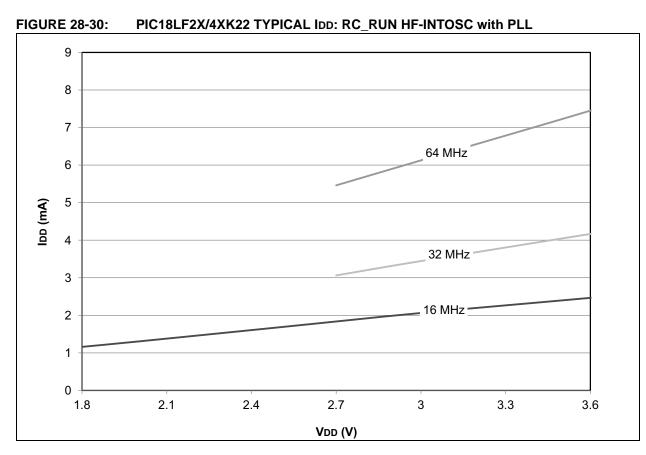

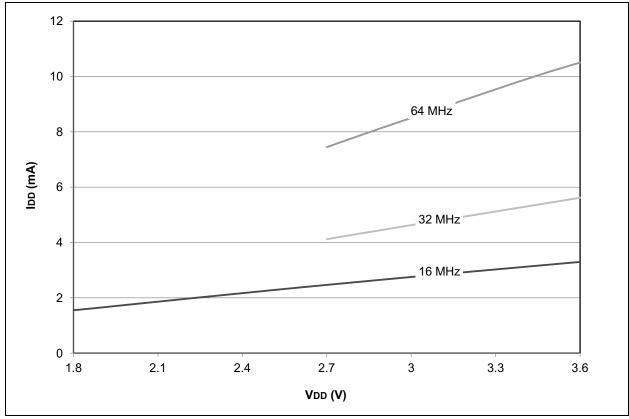

FIGURE 28-31: PIC18LF2X/4XK22 MAXIMUM IDD: RC\_RUN HF-INTOSC with PLL

© 2010-2016 Microchip Technology Inc.

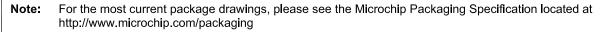

28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 4x4 mm Body [UQFN] With 0.40 mm Contact Length

|                            | MILLIMETERS |      |          |      |

|----------------------------|-------------|------|----------|------|

| Dimension                  | MIN         | NOM  | MAX      |      |

| Contact Pitch              | Е           |      | 0.40 BSC |      |

| Optional Center Pad Width  | W2          |      |          | 2.35 |

| Optional Center Pad Length | T2          |      |          | 2.35 |

| Contact Pad Spacing        | C1          |      | 4.00     |      |

| Contact Pad Spacing        | C2          |      | 4.00     |      |

| Contact Pad Width (X28)    | X1          |      |          | 0.20 |

| Contact Pad Length (X28)   | Y1          |      |          | 0.80 |

| Distance Between Pads      | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2152A

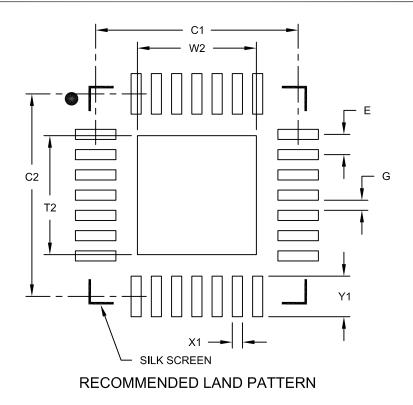

# 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |      |          |      |

|-------------------------|-------------|------|----------|------|

| Dimension               | MIN         | NOM  | MAX      |      |

| Number of Pins          | N           |      | 44       |      |

| Pitch                   | е           |      | 0.65 BSC |      |

| Overall Height          | Α           | 0.80 | 0.90     | 1.00 |

| Standoff                | A1          | 0.00 | 0.02     | 0.05 |

| Terminal Thickness      | A3          |      | 0.20 REF |      |

| Overall Width           | E           |      | 8.00 BSC |      |

| Exposed Pad Width       | E2          | 6.25 | 6.45     | 6.60 |

| Overall Length          | D           |      | 8.00 BSC |      |

| Exposed Pad Length      | D2          | 6.25 | 6.45     | 6.60 |

| Terminal Width          | b           | 0.20 | 0.30     | 0.35 |

| Terminal Length         | L           | 0.30 | 0.40     | 0.50 |

| Terminal-to-Exposed-Pad | K           | 0.20 | -        | -    |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103D Sheet 2 of 2

# APPENDIX A: REVISION HISTORY

# **Revision A (February 2010)**

Initial release of this document.

# **Revision B (April 2010)**

Updated Figures 2-4, 12-1 and 18-2; Updated Registers 2-2, 10-4, 10-5, 10-7, 17-2, 24-1 and 24-5; Updated Sections 10.3.2, 18.8.4, Synchronizing Comparator Output to Timer1; Updated Sections 27.2, 27-3, 27-4, 27-5, 27-6, 27-7 and 27-9; Updated Tables 27-2, 27-3, 27-4 and 27-7; Other minor corrections.

# Revision C (July 2010)

Added 40-pin UQFN diagram; Updated Table 2 and Table 1-3 to add 40-UQFN column; Updated Table 1-1 to add "40-pin UQFN"; Updated Figure 27-1; Added Figure 27-2; Updated Table 27-6; Added 40-Lead UQFN Package Marking Information and Details; Updated Packaging Information section; Updated Table B-1 to add "40-pin UQFN"; Updated Product Identification System section; Other minor corrections.

# **Revision D (November 2010)**

Updated the data sheet to new format; Revised Tables 1-2, 1-3, 5-2, 10-1, 10-5, 10-6, 10-8, 10-9, 10-11, 10-14, 14-13 and Register 14-5; Updated the Electrical Characteristics section.

# Revision E (January 2012)

Updated Section 2.5.2, EC Mode; Updated Table 3-2; Removed Table 3-3; Updated Section 14.4.8; Removed CM2CON Register; Updated the Electrical Characteristics section; Updated the Packaging Information section; Updated the Char. Data section; Other minor corrections.

# Revision F (May 2012)

Minor corrections; release of Final data sheet.

# **Revision G (August 2016)**

Minor corrections to Tables 1-2, 17-1, 27-11, 27-14, 27-22, Section 2.6.1, Example 7-3, Registers 9-4, 9-5, 9-11, 14-5, Figures 10-1, 17-3, 17-4, 27-23; Updated Packaging Information Section.