Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 30x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8×8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45k22-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 5-2:   REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES (CONTINUED) |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | <u>Value on</u><br>POR, BOR |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------------|

| F3Ah    | ANSELC | ANSC7 | ANSC6 | ANSC5 | ANSC4 | ANSC3 | ANSC2 | _     |       | 1111 11                     |

| F39h    | ANSELB | _     | _     | ANSB5 | ANSB4 | ANSB3 | ANSB2 | ANSB1 | ANSB0 | 11 1111                     |

| F38h    | ANSELA |       | -     | ANSA5 |       | ANSA3 | ANSA2 | ANSA1 | ANSA0 | 1- 1111                     |

**Legend:** x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: PIC18(L)F4XK22 devices only.

2: PIC18(L)F2XK22 devices only.

3: PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

#### 5.6 Data Addressing Modes

Note: The execution of some instructions in the core PIC18 instruction set are changed when the PIC18 extended instruction set is enabled. See Section 5.7 "Data Memory and the Extended Instruction Set" for more information.

While the program memory can be addressed in only one way – through the program counter – information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 5.7.1** "**Indexed Addressing with Literal Offset**".

### 5.6.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 5.6.2 DIRECT ADDRESSING

Direct addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byteoriented instructions use some version of direct addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (**Section 5.4.3 "General**  **Purpose Register File**") or a location in the Access Bank (Section 5.4.2 "Access Bank") as the data source for the instruction.

The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 5.4.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

#### 5.6.3 INDIRECT ADDRESSING

Indirect addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations which are to be read or written. Since the FSRs are themselves located in RAM as Special File Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for indirect addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 5-5.

#### EXAMPLE 5-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0, 100h | ; |                |

|---------|-------|------------|---|----------------|

| NEXT    | CLRF  | POSTINC0   | ; | Clear INDF     |

|         |       |            | ; | register then  |

|         |       |            | ; | inc pointer    |

|         | BTFSS | FSROH, 1   | ; | All done with  |

|         |       |            | ; | Bank1?         |

|         | BRA   | NEXT       | ; | NO, clear next |

| CONTINU | JE    |            | ; | YES, continue  |

#### EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY (CONTINUED)

|                | DECFSZ | COUNTER             | ; loop until holding registers are full |

|----------------|--------|---------------------|-----------------------------------------|

|                | BRA    | WRITE_WORD_TO_HREGS |                                         |

| PROGRAM_MEMORY |        |                     |                                         |

|                | BSF    | EECON1, EEPGD       | ; point to Flash program memory         |

|                | BCF    | EECON1, CFGS        | ; access Flash program memory           |

|                | BSF    | EECON1, WREN        | ; enable write to memory                |

|                | BCF    | INTCON, GIE         | ; disable interrupts                    |

|                | MOVLW  | 55h                 |                                         |

| Required       | MOVWF  | EECON2              | ; write 55h                             |

| Sequence       | MOVLW  | 0AAh                |                                         |

|                | MOVWF  | EECON2              | ; write OAAh                            |

|                | BSF    | EECON1, WR          | ; start program (CPU stall)             |

|                | DCFSZ  | COUNTER2            | ; repeat for remaining write blocks     |

|                | BRA    | WRITE_BYTE_TO_HREGS | ;                                       |

|                | BSF    | INTCON, GIE         | ; re-enable interrupts                  |

|                | BCF    | EECON1, WREN        | ; disable write to memory               |

| 1              |        |                     |                                         |

#### 6.6.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 6.6.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the WRERR bit will be set which the user can check to decide whether a rewrite of the location(s) is needed.

#### 6.6.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See **Section 24.0** "**Special Features of the CPU**" for more detail.

#### 6.7 Flash Program Operation During Code Protection

See Section 24.5 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7                                                 | Bit 6                                                   | Bit 5     | Bit 4            | Bit 3          | Bit 2     | Bit 1  | Bit 0  | Reset<br>Values on<br>page |

|---------|-------------------------------------------------------|---------------------------------------------------------|-----------|------------------|----------------|-----------|--------|--------|----------------------------|

| TBLPTRU |                                                       | Program Memory Table Pointer Upper Byte (TBLPTR<21:16>) |           |                  |                |           |        |        |                            |

| TBLPTRH | Program Memory Table Pointer High Byte (TBLPTR<15:8>) |                                                         |           |                  |                |           |        |        | —                          |

| TBLPTRL | Program Memory Table Pointer Low Byte (TBLPTR<7:0>)   |                                                         |           |                  |                |           |        |        | —                          |

| TABLAT  | Program Memory Table Latch                            |                                                         |           |                  |                |           |        | —      |                            |

| INTCON  | GIE/GIEH                                              | PEIE/GIEL                                               | TMR0IE    | INT0IE           | RBIE           | TMR0IF    | INT0IF | RBIF   | 109                        |

| EECON2  |                                                       | EEPR                                                    | OM Contro | ol Register 2 (I | not a physical | register) |        |        | —                          |

| EECON1  | EEPGD                                                 | CFGS                                                    | —         | FREE             | WRERR          | WREN      | WR     | RD     | 92                         |

| IPR2    | OSCFIP                                                | C1IP                                                    | C2IP      | EEIP             | BCL1IP         | HLVDIP    | TMR3IP | CCP2IP | 122                        |

| PIR2    | OSCFIF                                                | C1IF                                                    | C2IF      | EEIF             | BCL1IF         | HLVDIF    | TMR3IF | CCP2IF | 113                        |

| PIE2    | OSCFIE                                                | C1IE                                                    | C2IE      | EEIE             | BCL1IE         | HLVDIE    | TMR3IE | CCP2IE | 118                        |

#### TABLE 6-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

Legend: — = unimplemented, read as '0'. Shaded bits are not used during Flash/EEPROM access.

#### TABLE 10-1: PORTA I/O SUMMARY

| Pin Name                       | Function | TRIS<br>Setting | ANSEL<br>Setting | Pin<br>Type | Buffer<br>Type | Description                                                                                                          |

|--------------------------------|----------|-----------------|------------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------|

| RA0/C12IN0-/AN0                | RA0      | 0               | 0                | 0           | DIG            | LATA<0> data output; not affected by analog input.                                                                   |

|                                |          | 1               | 0                | Ι           | TTL            | PORTA<0> data input; disabled when analog input enabled.                                                             |

|                                | C12IN0-  | 1               | 1                | I           | AN             | Comparators C1 and C2 inverting input.                                                                               |

|                                | AN0      | 1               | 1                | I           | AN             | Analog input 0.                                                                                                      |

| RA1/C12IN1-/AN1                | RA1      | 0               | 0                | 0           | DIG            | LATA<1> data output; not affected by analog input.                                                                   |

|                                |          | 1               | 0                | Ι           | TTL            | PORTA<1> data input; disabled when analog input enabled.                                                             |

|                                | C12IN1-  | 1               | 1                | I           | AN             | Comparators C1 and C2 inverting input.                                                                               |

|                                | AN1      | 1               | 1                | I           | AN             | Analog input 1.                                                                                                      |

| RA2/C2IN+/AN2/<br>DACOUT/VREF- | RA2      | 0               | 0                | 0           | DIG            | LATA<2> data output; not affected by analog input; disabled when DACOUT enabled.                                     |

|                                |          | 1               | 0                | Ι           | TTL            | PORTA<2> data input; disabled when analog input enabled;<br>disabled when DACOUT enabled.                            |

|                                | C2IN+    | 1               | 1                | Ι           | AN             | Comparator C2 non-inverting input.                                                                                   |

|                                | AN2      | 1               | 1                | Ι           | AN             | Analog output 2.                                                                                                     |

|                                | DACOUT   | x               | 1                | 0           | AN             | DAC Reference output.                                                                                                |

|                                | VREF-    | 1               | 1                | Ι           | AN             | A/D reference voltage (low) input.                                                                                   |

| RA3/C1IN+/AN3/                 | RA3      | 0               |                  | 0           | DIG            | LATA<3> data output; not affected by analog input.                                                                   |

| VREF+                          |          | 1               | 0                | Ι           | TTL            | PORTA<3> data input; disabled when analog input enabled.                                                             |

|                                | C1IN+    | 1               | 1                | I           | AN             | Comparator C1 non-inverting input.                                                                                   |

|                                | AN3      | 1               | 1                | I           | AN             | Analog input 3.                                                                                                      |

|                                | VREF+    | 1               | 1                | I           | AN             | A/D reference voltage (high) input.                                                                                  |

| RA4/CCP5/C1OUT/                | RA4      | 0               | —                | 0           | DIG            | LATA<4> data output.                                                                                                 |

| SRQ/T0CKI                      |          | 1               | _                | I           | ST             | PORTA<4> data input; default configuration on POR.                                                                   |

|                                | CCP5     | 0               | _                | 0           | DIG            | CCP5 Compare output/PWM output, takes priority over RA4 output                                                       |

|                                |          | 1               | —                | I           | ST             | Capture 5 input/Compare 5 output/ PWM 5 output.                                                                      |

|                                | C1OUT    | 0               | _                | 0           | DIG            | Comparator C1 output.                                                                                                |

|                                | SRQ      | 0               | _                | 0           | DIG            | SR latch Q output; take priority over CCP 5 output.                                                                  |

|                                | TOCKI    | 1               | _                | I           | ST             | Timer0 external clock input.                                                                                         |

| RA5/C2OUT/SRNQ/                | RA5      | 0               | 0                | 0           | DIG            | LATA<5> data output; not affected by analog input.                                                                   |

| SS1/<br>HLVDIN/AN4             |          | 1               | 0                | I           | TTL            | PORTA<5> data input; disabled when analog input enabled.                                                             |

| HLVDIN/AN4                     | C2OUT    | 0               | 0                | 0           | DIG            | Comparator C2 output.                                                                                                |

|                                | SRNQ     | 0               | 0                | 0           | DIG            | SR latch $\overline{Q}$ output.                                                                                      |

|                                | SS1      | 1               | 0                | I           | TTL            | SPI slave select input (MSSP1).                                                                                      |

|                                | HLVDIN   | 1               | 1                | I           | AN             | High/Low-Voltage Detect input.                                                                                       |

|                                | AN4      | 1               | 1                | 1           | AN             | A/D input 4.                                                                                                         |

| RA6/CLKO/OSC2                  | RA6      | 0               | _                | 0           | DIG            | LATA<6> data output; enabled in INTOSC modes when CLKO is no<br>enabled.                                             |

|                                |          | 1               | —                | Ι           | TTL            | PORTA<6> data input; enabled in INTOSC modes when CLKO is not enabled.                                               |

|                                | CLKO     | x               | —                | 0           | DIG            | In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the fre-<br>quency of OSC1 and denotes the instruction cycle rate. |

|                                | OSC2     | x               | _                | 0           | XTAL           | Oscillator crystal output; connects to crystal or resonator in Crystal Oscillator mode.                              |

| RA7/CLKI/OSC1                  | RA7      | 0               | _                | 0           | DIG            | LATA<7> data output; disabled in external oscillator modes.                                                          |

|                                |          | 1               | —                | Ι           | TTL            | PORTA<7> data input; disabled in external oscillator modes.                                                          |

|                                | CLKI     | x               | —                | I           | AN             | External clock source input; always associated with pin function OSC1.                                               |

|                                | OSC1     | x               |                  | Ι           | XTAL           | Oscillator crystal input or external clock source input ST buffer wher<br>configured in RC mode; CMOS otherwise.     |

Legend: AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C.

| Name                  | Bit 7  | Bit 6  | Bit 5     | Bit 4     | Bit 3  | Bit 2      | Bit 1  | Bit 0  | Register on<br>Page |  |

|-----------------------|--------|--------|-----------|-----------|--------|------------|--------|--------|---------------------|--|

| ANSELD <sup>(1)</sup> | ANSD7  | ANSD6  | ANSD5     | ANSD4     | ANSD3  | ANSD2      | ANSD1  | ANSD0  | 150                 |  |

| BAUDCON2              | ABDOVF | RCIDL  | DTRXP     | CKTXP     | BRG16  | _          | WUE    | ABDEN  | 271                 |  |

| CCP1CON               | P1M<   | :1:0>  | DC1E      | 3<1:0>    |        | CCP1N      | l<3:0> |        | 198                 |  |

| CCP2CON               | P2M<   | :1:0>  | DC2B<1:0> |           |        | 198        |        |        |                     |  |

| CCP4CON               | —      | —      | DC4E      | DC4B<1:0> |        | CCP4M<3:0> |        |        |                     |  |

| LATD <sup>(1)</sup>   | LATD7  | LATD6  | LATD5     | LATD4     | LATD3  | LATD2      | LATD1  | LATD0  | 152                 |  |

| PORTD <sup>(1)</sup>  | RD7    | RD6    | RD5       | RD4       | RD3    | RD2        | RD1    | RD0    | 148                 |  |

| RCSTA2                | SPEN   | RX9    | SREN      | CREN      | ADDEN  | FERR       | OERR   | RX9D   | 270                 |  |

| SLRCON <sup>(1)</sup> | —      | —      | _         | SLRE      | SLRD   | SLRC       | SLRB   | SLRA   | 153                 |  |

| SSP2CON1              | WCOL   | SSPOV  | SSPEN CKP |           |        | SSPM       | <3:0>  |        | 253                 |  |

| TRISD <sup>(1)</sup>  | TRISD7 | TRISD6 | TRISD5    | TRISD4    | TRISD3 | TRISD2     | TRISD1 | TRISD0 | 151                 |  |

#### TABLE 10-12: REGISTERS ASSOCIATED WITH PORTD

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for PORTD.

Note 1: Available on PIC18(L)F4XK22 devices.

#### TABLE 10-13: CONFIGURATION REGISTERS ASSOCIATED WITH PORTD

| Name   | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|----------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| CONFIG | BH MCLRE | —     | P2BMX | T3CMX | HFOFST | CCP3MX | PBADEN | CCP2MX | 348                 |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTD.

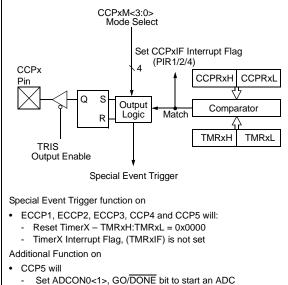

### 14.2 Compare Mode

The Compare mode function described in this section is identical for all CCP and ECCP modules available on this device family.

Compare mode makes use of the 16-bit TimerX resources, Timer1, Timer3 and Timer5. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMRxH:TMRxL register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output

- · Set the CCPx output

- Clear the CCPx output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 14-2 shows a simplified diagram of the Compare operation.

#### FIGURE 14-2: COMPARE MODE OPERATION BLOCK DIAGRAM

Conversion if ADCON<0>, ADON = 1.

### 14.2.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Some CCPx outputs are multiplexed on a couple of pins. Table 14-2 shows the CCP output pin Multiplexing. Selection of the output pin is determined by the CCPxMX bits in Configuration register 3H (CONFIG3H). Refer to Register 24-4 for more details.

Note: Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

### 14.2.2 TimerX MODE RESOURCE

In Compare mode, 16-bit TimerX resource must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 12.0 "Timer1/3/5 Module with Gate Control" for more information on configuring the 16-bit TimerX resources.

Note: Clocking TimerX from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TimerX must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 14.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

#### REGISTER 14-2: CCPxCON: ENHANCED CCPx CONTROL REGISTER (CONTINUED)

- bit 3-0 CCPxM<3:0>: ECCPx Mode Select bits

- 0000 = Capture/Compare/PWM off (resets the module)

- 0001 = Reserved

- 0010 = Compare mode: toggle output on match

- 0011 = Reserved

- 0100 = Capture mode: every falling edge

- 0101 = Capture mode: every rising edge

- 0110 = Capture mode: every 4th rising edge

- 0111 = Capture mode: every 16th rising edge

- 1000 = Compare mode: set output on compare match (CCPx pin is set, CCPxIF is set)

- 1001 = Compare mode: clear output on compare match (CCPx pin is cleared, CCPxIF is set)

- 1010 = Compare mode: generate software interrupt on compare match (CCPx pin is unaffected, CCPxIF is set)

- 1011 = Compare mode: Special Event Trigger (CCPx pin is unaffected, CCPxIF is set) TimerX is reset

Half-Bridge ECCP Modules<sup>(1)</sup>:

- 1100 = PWM mode: PxA active-high; PxB active-high

- 1101 = PWM mode: PxA active-high; PxB active-low

- 1110 = PWM mode: PxA active-low; PxB active-high

- 1111 = PWM mode: PxA active-low; PxB active-low

Full-Bridge ECCP Modules<sup>(1)</sup>:

- 1100 = PWM mode: PxA, PxC active-high; PxB, PxD active-high

- 1101 = PWM mode: PxA, PxC active-high; PxB, PxD active-low

- 1110 = PWM mode: PxA, PxC active-low; PxB, PxD active-high

- 1111 = PWM mode: PxA, PxC active-low; PxB, PxD active-low

- Note 1: See Table 14-1 to determine full-bridge and half-bridge ECCPs for the device being used.

| R/W-0                                                                          | R/W-0                                                                                                                           | R/W-0             | R/W-0                                                           | R/W-0        | R/W-0            | R/W-0    | R/W-0 |  |  |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------|--------------|------------------|----------|-------|--|--|

| PxRSEN                                                                         |                                                                                                                                 |                   |                                                                 | PxDC<6:0>    |                  |          |       |  |  |

| bit 7                                                                          |                                                                                                                                 |                   |                                                                 |              |                  |          | bit 0 |  |  |

|                                                                                |                                                                                                                                 |                   |                                                                 |              |                  |          |       |  |  |

| Legend:                                                                        |                                                                                                                                 |                   |                                                                 |              |                  |          |       |  |  |

| R = Readable                                                                   | e bit                                                                                                                           | W = Writable      | bit                                                             | U = Unimpler | nented bit, read | d as '0' |       |  |  |

| u = Bit is unchanged x = Bi                                                    |                                                                                                                                 | x = Bit is unkr   | x = Bit is unknown -n/n = Value at POR and BOR/Value at all oth |              |                  |          |       |  |  |

| '1' = Bit is set                                                               | t                                                                                                                               | '0' = Bit is clea | ared                                                            |              |                  |          |       |  |  |

|                                                                                |                                                                                                                                 |                   |                                                                 |              |                  |          |       |  |  |

| bit 7                                                                          | PxRSEN: P                                                                                                                       | WM Restart Ena    | able bit                                                        |              |                  |          |       |  |  |

|                                                                                | 1 = Upon auto-shutdown, the CCPxASE bit clears automatically once the shutdown event goes awa<br>the PWM restarts automatically |                   |                                                                 |              |                  |          |       |  |  |

| 0 = Upon auto-shutdown, CCPxASE must be cleared in software to restart the PWM |                                                                                                                                 |                   |                                                                 |              |                  |          |       |  |  |

| bit 6-0                                                                        | PxDC<6:0>                                                                                                                       | : PWM Delay Co    | ount bits                                                       |              |                  |          |       |  |  |

|                                                                                | PxDCx = Number of Fosc/4 (4 * Tosc) cycles between the scheduled time when a PWM signal                                         |                   |                                                                 |              |                  |          |       |  |  |

#### REGISTER 14-6: PWMxCON: ENHANCED PWM CONTROL REGISTER

#### REGISTER 14-7: PSTRxCON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-1 |

|-------|-----|-----|----------|-------|-------|-------|-------|

| —     | —   | —   | STRxSYNC | STRxD | STRxC | STRxB | STRxA |

| bit 7 |     |     |          |       |       |       | bit 0 |

should transition active and the actual time it transitions active

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                         |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <b>STRxSYNC:</b> Steering Sync bit<br>1 = Output steering update occurs on next PWM period<br>0 = Output steering update occurs at the beginning of the instruction cycle boundary |

| bit 3   | <b>STRxD:</b> Steering Enable bit D<br>1 = PxD pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxD pin is assigned to port pin                               |

| bit 2   | <b>STRxC:</b> Steering Enable bit C<br>1 = PxC pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxC pin is assigned to port pin                               |

| bit 1   | <b>STRxB:</b> Steering Enable bit B<br>1 = PxB pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxB pin is assigned to port pin                               |

| bit 0   | <b>STRxA:</b> Steering Enable bit A<br>1 = PxA pin has the PWM waveform with polarity control from CCPxM<1:0><br>0 = PxA pin is assigned to port pin                               |

| Note 1. | The DWM Steering mode is evoluble only when the CCDyCON register hits CCDyM (20) 11.0                                                                                              |

**Note 1:** The PWM Steering mode is available only when the CCPxCON register bits CCPxM<3:2> = 11 and PxM<1:0> = 00.

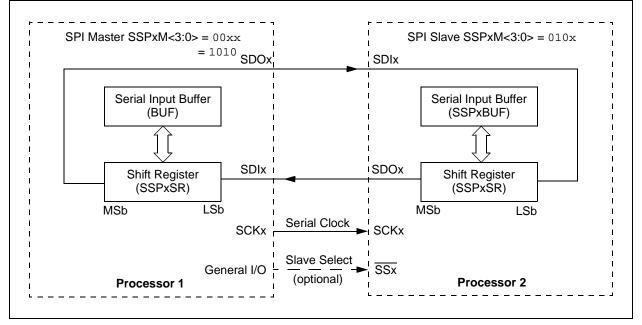

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

The MSSPx consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF of the SSPxSTAT register, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL of the SSPxCON1 register, will be

set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSPx interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

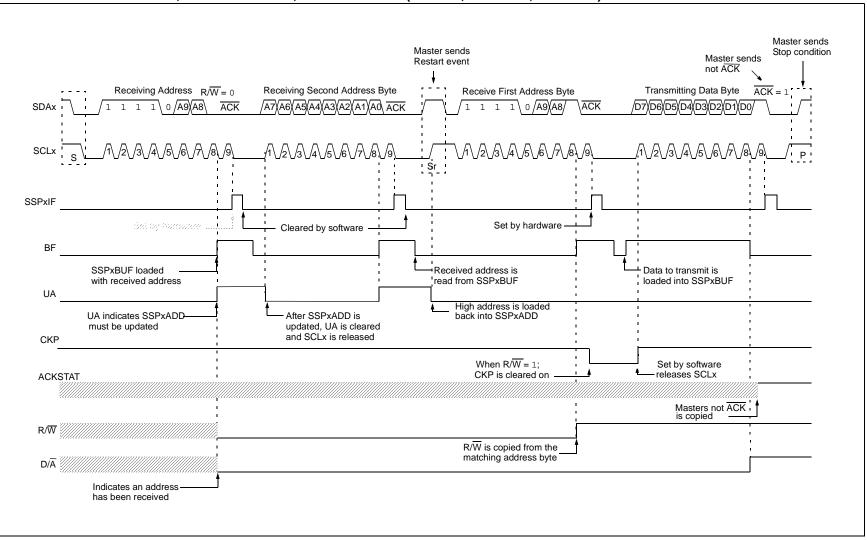

#### FIGURE 15-22: I<sup>2</sup>C SLAVE, 10-BIT ADDRESS, TRANSMISSION (SEN = 0, AHEN = 0, DHEN = 0)

PIC18(L)F2X/4XK22

#### 16.4.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RXx signal, the RXx signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCONx register starts the auto-baud calibration sequence (Section 16.4.2 "Auto-baud Overflow"). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRGx begins counting up using the BRG counter clock as shown in Table 16-6. The fifth rising edge will occur on the RXx/ DTx pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGHx:SPBRGx register pair, the ABDEN bit is automatically cleared, and the RCxIF interrupt flag is set. A read operation on the RCREGx needs to be performed to clear the RCxIF interrupt. RCREGx content should be discarded. When calibrating for modes that do not use the SPBRGHx register the user can verify that the SPBRGx register did not overflow by checking for 00h in the SPBRGHx register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 16-6. During ABD, both the SPBRGHx and SPBRGx registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGHx and SPBRGx registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte <u>following</u> the Break character (see Section 16.4.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the autobaud counter starts counting at one. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract one from the SPBRGHx:SPBRGx register pair.

| TABLE 16-6: | BRG COUNTER CLOCK |

|-------------|-------------------|

|             | RATES             |

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

Note: During the ABD sequence, SPBRGx and SPBRGHx registers are both used as a 16-bit counter, independent of BRG16 setting.

| BRG Value   | XXXXh         | 0000h                  |                                                                               | 001Ch            |

|-------------|---------------|------------------------|-------------------------------------------------------------------------------|------------------|

| RXx/DTx pin |               | Start                  | Edge #1 Edge #2 Edge #3 Edge #4 bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit | Edge #5 Stop bit |

| BRG Clock   |               |                        |                                                                               | (                |

|             | Set by User — | ı<br><del> </del>      |                                                                               | Auto Cleared     |

| ABDEN bit   |               | ]                      | I                                                                             |                  |

| RCIDL       |               | <u>.</u>               | 1                                                                             |                  |

| RCxIF bit   |               | 1 <u> </u>             |                                                                               |                  |

| (Interrupt) |               | 1                      |                                                                               |                  |

| Read        |               | I<br>I                 | -                                                                             |                  |

| RCREGx      |               | 1                      | 1                                                                             |                  |

| SPBRGx      |               | 1<br>1                 | XXh                                                                           | X 1Ch            |

| SPBRGHx     |               | 1                      | XXh                                                                           | 00h              |

|             |               | ence requires the EUS. | -<br>-                                                                        |                  |

### FIGURE 16-6: AUTOMATIC BAUD RATE CALIBRATION

| FIGURE 16-12:                                     | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                              |

|---------------------------------------------------|------------------------------------------------------------------------|

| RXx/DTx<br>pin<br>TXx/CKx pin<br>(SCKP = 0)       | X bit 0 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7                            |

| TXx/CKx pin<br>(SCKP = 1)<br>Write to<br>bit SREN |                                                                        |

| SREN bit                                          | ·0,                                                                    |

| RCxIF bit<br>(Interrupt) ———<br>Read              |                                                                        |

| RCREGx — Note: Timing dia                         | gram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0. |

#### TABLE 16-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name     | Bit 7    | Bit 6     | Bit 5  | Bit 4       | Bit 3        | Bit 2     | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|-----------|--------|-------------|--------------|-----------|---------|---------|---------------------|

| BAUDCON1 | ABDOVF   | RCIDL     | DTRXP  | CKTXP       | BRG16        | —         | WUE     | ABDEN   | 271                 |

| BAUDCON2 | ABDOVF   | RCIDL     | DTRXP  | CKTXP       | BRG16        | _         | WUE     | ABDEN   | 271                 |

| INTCON   | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE      | RBIE         | TMR0IF    | INT0IF  | RBIF    | 109                 |

| IPR1     | _        | ADIP      | RC1IP  | TX1IP       | SSP1IP       | CCP1IP    | TMR2IP  | TMR1IP  | 121                 |

| IPR3     | SSP2IP   | BCL2IP    | RC2IP  | TX2IP       | CTMUIP       | TMR5GIP   | TMR3GIP | TMR1GIP | 123                 |

| PIE1     | _        | ADIE      | RC1IE  | TX1IE       | SSP1IE       | CCP1IE    | TMR2IE  | TMR1IE  | 117                 |

| PIE3     | SSP2IE   | BCL2IE    | RC2IE  | TX2IE       | CTMUIE       | TMR5GIE   | TMR3GIE | TMR1GIE | 119                 |

| PIR1     | _        | ADIF      | RC1IF  | TX1IF       | SSP1IF       | CCP1IF    | TMR2IF  | TMR1IF  | 112                 |

| PIR3     | SSP2IF   | BCL2IF    | RC2IF  | TX2IF       | CTMUIF       | TMR5GIF   | TMR3GIF | TMR1GIF | 114                 |

| PMD0     | UART2MD  | UART1MD   | TMR6MD | TMR5MD      | TMR4MD       | TMR3MD    | TMR2MD  | TMR1MD  | 52                  |

| RCREG1   |          |           | E      | USART1 Re   | ceive Regis  | ter       |         |         | —                   |

| RCSTA1   | SPEN     | RX9       | SREN   | CREN        | ADDEN        | FERR      | OERR    | RX9D    | 270                 |

| RCREG2   |          |           | E      | USART2 Re   | ceive Regis  | ter       |         |         | —                   |

| RCSTA2   | SPEN     | RX9       | SREN   | CREN        | ADDEN        | FERR      | OERR    | RX9D    | 270                 |

| SPBRG1   |          |           | EUSART | 1 Baud Rate | e Generator, | Low Byte  |         |         | —                   |

| SPBRGH1  |          |           | EUSART | 1 Baud Rate | Generator,   | High Byte |         |         | —                   |

| SPBRG2   |          |           | EUSART | 2 Baud Rate | e Generator, | Low Byte  |         |         | —                   |

| SPBRGH2  |          |           | EUSART | 2 Baud Rate | Generator,   | High Byte |         |         | —                   |

| TXSTA1   | CSRC     | TX9       | TXEN   | SYNC        | SENDB        | BRGH      | TRMT    | TX9D    | 269                 |

| TXSTA2   | CSRC     | TX9       | TXEN   | SYNC        | SENDB        | BRGH      | TRMT    | TX9D    | 269                 |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for synchronous master reception.

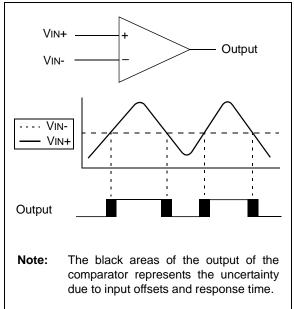

### 18.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of the program execution. The analog comparator module includes the following features:

- Independent comparator control

- Programmable input selection

- Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- Wake-up from Sleep

- Programmable Speed/Power optimization

- PWM shutdown

- · Programmable and fixed voltage reference

- Selectable Hysteresis

#### 18.1 Comparator Overview

A single comparator is shown in Figure 18-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

#### FIGURE 18-1: SINGLE COMPARATOR

| BNC          | ;                                                   | Branch if                                                                                | Not Carry                                                                                                                                                                                                                                                                             | /    |                |  |  |  |

|--------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|--|--|--|

| Synta        | ax:                                                 | BNC n                                                                                    | BNC n                                                                                                                                                                                                                                                                                 |      |                |  |  |  |

| Operands:    |                                                     | -128 ≤ n ≤ ′                                                                             | 127                                                                                                                                                                                                                                                                                   |      |                |  |  |  |

| Oper         | ation:                                              | if CARRY b<br>(PC) + 2 + 2                                                               |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

| Statu        | s Affected:                                         | None                                                                                     |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

| Enco         | ding:                                               | 1110                                                                                     | 0011 :                                                                                                                                                                                                                                                                                | nnnn | nnnn           |  |  |  |

| Description: |                                                     | will branch.<br>The 2's con<br>added to the<br>incremente<br>instruction,<br>PC + 2 + 2r | If the CARRY bit is '0', then the program<br>will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction. |      |                |  |  |  |

| Word         | ls:                                                 | 1                                                                                        |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

| Cycle        | es:                                                 | 1(2)                                                                                     |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

| Q C<br>If Ju | ycle Activity:<br>mp:                               |                                                                                          |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

|              | Q1                                                  | Q2                                                                                       | Q3                                                                                                                                                                                                                                                                                    |      | Q4             |  |  |  |

|              | Decode                                              | Read literal<br>'n'                                                                      | Process<br>Data                                                                                                                                                                                                                                                                       | s Wr | ite to PC      |  |  |  |

|              | No<br>operation                                     | No<br>operation                                                                          | No<br>operation                                                                                                                                                                                                                                                                       | n op | No<br>peration |  |  |  |

| lf No        | o Jump:                                             |                                                                                          |                                                                                                                                                                                                                                                                                       |      |                |  |  |  |

|              | Q1                                                  | Q2                                                                                       | Q3                                                                                                                                                                                                                                                                                    |      | Q4             |  |  |  |

|              | Decode                                              | Read literal<br>'n'                                                                      | Process<br>Data                                                                                                                                                                                                                                                                       |      | No<br>peration |  |  |  |

| <u>Exan</u>  |                                                     | HERE                                                                                     | BNC Ju                                                                                                                                                                                                                                                                                | mp   |                |  |  |  |

|              | Before Instruc<br>PC<br>After Instructio<br>If CARR | = ad<br>on<br>( = 0;                                                                     | dress (HE                                                                                                                                                                                                                                                                             | ŗ    |                |  |  |  |

|              | PC<br>If CARR<br>PC                                 | <i>(</i> = 1;                                                                            | dress (Jum<br>dress (HE                                                                                                                                                                                                                                                               |      | 2)             |  |  |  |

| BNN                                                                                                                                                      | Branch if                                                                            | Not Nega                                                                                                                                                                                                                                                                                 | tive |                |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|--|--|--|--|--|

| Syntax:                                                                                                                                                  | BNN n                                                                                | BNN n                                                                                                                                                                                                                                                                                    |      |                |  |  |  |  |  |

| Operands:                                                                                                                                                | -128 ≤ n ≤ 1                                                                         | $-128 \le n \le 127$                                                                                                                                                                                                                                                                     |      |                |  |  |  |  |  |

| Operation:                                                                                                                                               |                                                                                      | if NEGATIVE bit is '0' (PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                    |      |                |  |  |  |  |  |

| Status Affected:                                                                                                                                         | None                                                                                 |                                                                                                                                                                                                                                                                                          |      |                |  |  |  |  |  |

| Encoding:                                                                                                                                                | 1110                                                                                 | 0111 1                                                                                                                                                                                                                                                                                   | nnnn | nnnn           |  |  |  |  |  |

| Description:                                                                                                                                             | program wi<br>The 2's cor<br>added to th<br>incremente<br>instruction,<br>PC + 2 + 2 | If the NEGATIVE bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction. |      |                |  |  |  |  |  |

| Words:                                                                                                                                                   | 1                                                                                    | 1                                                                                                                                                                                                                                                                                        |      |                |  |  |  |  |  |

| Cycles:                                                                                                                                                  | 1(2)                                                                                 | 1(2)                                                                                                                                                                                                                                                                                     |      |                |  |  |  |  |  |

| Q Cycle Activity:<br>If Jump:                                                                                                                            | 00                                                                                   | 00                                                                                                                                                                                                                                                                                       |      | 04             |  |  |  |  |  |

| Q1                                                                                                                                                       | Q2                                                                                   | Q3                                                                                                                                                                                                                                                                                       | 10/- | Q4             |  |  |  |  |  |

| Decode                                                                                                                                                   | Read literal<br>'n'                                                                  | Process<br>Data                                                                                                                                                                                                                                                                          | VVF  | ite to PC      |  |  |  |  |  |

| No                                                                                                                                                       | No                                                                                   | No                                                                                                                                                                                                                                                                                       |      | No             |  |  |  |  |  |

| operation                                                                                                                                                | operation                                                                            | operatior                                                                                                                                                                                                                                                                                | n op | peration       |  |  |  |  |  |

| If No Jump:                                                                                                                                              |                                                                                      |                                                                                                                                                                                                                                                                                          |      |                |  |  |  |  |  |

| Q1                                                                                                                                                       | Q2                                                                                   | Q3                                                                                                                                                                                                                                                                                       |      | Q4             |  |  |  |  |  |

| Decode                                                                                                                                                   | Read literal<br>'n'                                                                  | Process<br>Data                                                                                                                                                                                                                                                                          |      | No<br>peration |  |  |  |  |  |

|                                                                                                                                                          |                                                                                      | Daia                                                                                                                                                                                                                                                                                     | U O  |                |  |  |  |  |  |

| Example:                                                                                                                                                 | HERE                                                                                 | BNN Ju                                                                                                                                                                                                                                                                                   | mp   |                |  |  |  |  |  |

| Before Instruction<br>PC = address (HERE)<br>After Instruction<br>If NEGATIVE = 0;<br>PC = address (Jump)<br>If NEGATIVE = 1;<br>PC = address (HERE + 2) |                                                                                      |                                                                                                                                                                                                                                                                                          |      |                |  |  |  |  |  |

CNT Z C DC

After Instruction

CNT Z C DC

FFh 0 ? ?

00h

= = = =

= = = 1 1 1

| GOTO                                   | Uncondit                    | ional Bran                                                    | ch                      |                                        | INCF                   | Incremen                                           | tf                                                                                                             |                                              |  |

|----------------------------------------|-----------------------------|---------------------------------------------------------------|-------------------------|----------------------------------------|------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| Syntax:                                | GOTO k                      |                                                               |                         |                                        | Syntax:                | INCF f{,c                                          | d {,a}}                                                                                                        |                                              |  |

| Operands:                              | $0 \le k \le 104$           | 8575                                                          |                         |                                        | Operands:              | $0 \leq f \leq 255$                                |                                                                                                                |                                              |  |

| Operation:                             | $k \rightarrow PC < 20:1 >$ |                                                               |                         |                                        | d ∈ [0,1]<br>a ∈ [0,1] |                                                    |                                                                                                                |                                              |  |

| Status Affected:                       | None                        | None                                                          |                         |                                        | Operation:             | $a \in [0, 1]$<br>(f) + 1 $\rightarrow$ definition | aet                                                                                                            |                                              |  |

| Encoding:                              |                             |                                                               |                         |                                        | Status Affected:       | $(1) \neq 1 \rightarrow 0$<br>C, DC, N,            |                                                                                                                |                                              |  |

| 1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110<br>) 1111              |                                                               | <sub>7</sub> kkk<br>kkk | kkkk <sub>0</sub><br>kkkk <sub>8</sub> | Encoding:              | 0010                                               | 10da ff                                                                                                        | ff ffff                                      |  |

| Description:                           |                             | vs an uncon                                                   |                         | Ũ                                      | Description:           |                                                    | ts of register "                                                                                               |                                              |  |

|                                        | 2-Mbyte me<br>value 'k' is  | within entire<br>emory range<br>loaded into I<br>ways a 2-cyc | PC<20                   |                                        |                        | placed in W<br>placed bac<br>If 'a' is '0', t      | d. If 'd' is '0', t<br>/. If 'd' is '1', th<br>k in register 'f'<br>he Access Ba<br>he BSR is use              | ne result is<br>(default).<br>nk is selected |  |

| Words:                                 | 2                           |                                                               |                         |                                        |                        | GPR bank.                                          |                                                                                                                | ! : <b>!</b>                                 |  |