Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 35                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1.5K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 30x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45k22t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Nu        | ımber        |                                 |             |                |                                                                                                               |

|---------------|--------------|---------------------------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------|

| PDIP,<br>SOIC | QFN,<br>UQFN | Pin Name                        | Pin<br>Type | Buffer<br>Type | Description                                                                                                   |

| 9             | 6            | RA7/CLKI/OSC1                   |             |                |                                                                                                               |

|               |              | RA7                             | I/O         | TTL            | Digital I/O.                                                                                                  |

|               |              | CLKI                            | Ι           | CMOS           | External clock source input. Always associated with pin function OSC1.                                        |

|               |              | OSC1                            | Ι           | ST             | Oscillator crystal input or external clock source input ST buffer when configured in RC mode; CMOS otherwise. |

| 21            | 18           | RB0/INT0/CCP4/FLT0/SRI/SS2/AN12 | 2           |                |                                                                                                               |

|               |              | RB0                             | I/O         | TTL            | Digital I/O.                                                                                                  |

|               |              | ΙΝΤΟ                            | I           | ST             | External interrupt 0.                                                                                         |

|               |              | CCP4                            | I/O         | ST             | Capture 4 input/Compare 4 output/PWM 4 output.                                                                |

|               |              | FLTO                            | I           | ST             | PWM Fault input for ECCP Auto-Shutdown.                                                                       |

|               |              | SRI                             | I           | ST             | SR latch input.                                                                                               |

|               |              | SS2                             | 1           | TTL            | SPI slave select input (MSSP).                                                                                |

|               |              | AN12                            | I           | Analog         | Analog input 12.                                                                                              |

| 22            | 19           | RB1/INT1/P1C/SCK2/SCL2/C12IN3-/ | 'AN10       |                |                                                                                                               |

|               |              | RB1                             | I/O         | TTL            | Digital I/O.                                                                                                  |

|               |              | INT1                            | Ι           | ST             | External interrupt 1.                                                                                         |

|               |              | P1C                             | 0           | CMOS           | Enhanced CCP1 PWM output.                                                                                     |

|               |              | SCK2                            | I/O         | ST             | Synchronous serial clock input/output for SPI mode (MSSP).                                                    |

|               |              | SCL2                            | I/O         | ST             | Synchronous serial clock input/output for I <sup>2</sup> C mode (MSSP).                                       |

|               |              | C12IN3-                         | Ι           | Analog         | Comparators C1 and C2 inverting input.                                                                        |

|               |              | AN10                            | Ι           | Analog         | Analog input 10.                                                                                              |

| 23            | 20           | RB2/INT2/CTED1/P1B/SDI2/SDA2/A  | N8          |                |                                                                                                               |

|               |              | RB2                             | I/O         | TTL            | Digital I/O.                                                                                                  |

|               |              | INT2                            | Ι           | ST             | External interrupt 2.                                                                                         |

|               |              | CTED1                           | Ι           | ST             | CTMU Edge 1 input.                                                                                            |

|               |              | P1B                             | 0           | CMOS           | Enhanced CCP1 PWM output.                                                                                     |

|               |              | SDI2                            | Ι           | ST             | SPI data in (MSSP).                                                                                           |

|               |              | SDA2                            | I/O         | ST             | I <sup>2</sup> C data I/O (MSSP).                                                                             |

|               |              | AN8                             | I           | Analog         | Analog input 8.                                                                                               |

| 24            | 21           | RB3/CTED2/P2A/CCP2/SDO2/C12IN   | 2-/AN9      | )              |                                                                                                               |

|               |              | RB3                             | I/O         | TTL            | Digital I/O.                                                                                                  |

|               |              | CTED2                           | Т           | ST             | CTMU Edge 2 input.                                                                                            |

|               |              | P2A                             | 0           | CMOS           | Enhanced CCP2 PWM output.                                                                                     |

|               |              | CCP2 <sup>(2)</sup>             | I/O         | ST             | Capture 2 input/Compare 2 output/PWM 2 output.                                                                |

|               |              | SDO2                            | 0           | —              | SPI data out (MSSP).                                                                                          |

|               |              | C12IN2-                         | I           | Analog         | Comparators C1 and C2 inverting input.                                                                        |

|               |              | AN9                             | I           | Analog         | Analog input 9.                                                                                               |

| l eaend.      |              |                                 |             |                | t or output: ST - Schmitt Trigger input with CMOS levels:                                                     |

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

| Pin Nu        | umber        |                                | <b>D</b> '  | Duffer         |                                                     |  |  |  |  |  |  |  |

|---------------|--------------|--------------------------------|-------------|----------------|-----------------------------------------------------|--|--|--|--|--|--|--|

| PDIP,<br>SOIC | QFN,<br>UQFN | Pin Name                       | Pin<br>Type | Buffer<br>Type | Description                                         |  |  |  |  |  |  |  |

| 25            | 22           | RB4/IOC0/P1D/T5G/AN11          |             |                |                                                     |  |  |  |  |  |  |  |

|               |              | RB4                            | I/O         | TTL            | Digital I/O.                                        |  |  |  |  |  |  |  |

|               |              | IOC0                           | I           | TTL            | Interrupt-on-change pin.                            |  |  |  |  |  |  |  |

|               |              | P1D                            | 0           | CMOS           | Enhanced CCP1 PWM output.                           |  |  |  |  |  |  |  |

|               |              | T5G                            | I           | ST             | Timer5 external clock gate input.                   |  |  |  |  |  |  |  |

|               |              | AN11                           | I           | Analog         | Analog input 11.                                    |  |  |  |  |  |  |  |

| 26            | 23           | RB5/IOC1/P2B/P3A/CCP3/T3CKI/T1 | G/AN13      | 3              |                                                     |  |  |  |  |  |  |  |

|               |              | RB5                            | I/O         | TTL            | Digital I/O.                                        |  |  |  |  |  |  |  |

|               |              | IOC1                           | I           | TTL            | Interrupt-on-change pin.                            |  |  |  |  |  |  |  |

|               |              | P2B <sup>(1)</sup>             | 0           | CMOS           | Enhanced CCP2 PWM output.                           |  |  |  |  |  |  |  |

|               |              | P3A <sup>(1)</sup>             | 0           | CMOS           | Enhanced CCP3 PWM output.                           |  |  |  |  |  |  |  |

|               |              | CCP3 <sup>(1)</sup>            | I/O         | ST             | Capture 3 input/Compare 3 output/PWM 3 output.      |  |  |  |  |  |  |  |

|               |              | ТЗСКІ <sup>(2)</sup>           | I           | ST             | Timer3 clock input.                                 |  |  |  |  |  |  |  |

|               |              | T1G                            | I           | ST             | Timer1 external clock gate input.                   |  |  |  |  |  |  |  |

|               |              | AN13                           | I           | Analog         | Analog input 13.                                    |  |  |  |  |  |  |  |

| 27            | 24           | RB6/IOC2/TX2/CK2/PGC           |             |                |                                                     |  |  |  |  |  |  |  |

|               |              | RB6                            | I/O         | TTL            | Digital I/O.                                        |  |  |  |  |  |  |  |

|               |              | IOC2                           | I           | TTL            | Interrupt-on-change pin.                            |  |  |  |  |  |  |  |

|               |              | TX2                            | 0           | _              | EUSART asynchronous transmit.                       |  |  |  |  |  |  |  |

|               |              | CK2                            | I/O         | ST             | EUSART synchronous clock (see related RXx/DTx).     |  |  |  |  |  |  |  |

|               |              | PGC                            | I/O         | ST             | In-Circuit Debugger and ICSP™ programming clock pir |  |  |  |  |  |  |  |

| 28            | 25           | RB7/IOC3/RX2/DT2/PGD           |             |                |                                                     |  |  |  |  |  |  |  |

|               |              | RB7                            | I/O         | TTL            | Digital I/O.                                        |  |  |  |  |  |  |  |

|               |              | IOC3                           | I           | TTL            | Interrupt-on-change pin.                            |  |  |  |  |  |  |  |

|               |              | RX2                            | I           | ST             | EUSART asynchronous receive.                        |  |  |  |  |  |  |  |

|               |              | DT2                            | I/O         | ST             | EUSART synchronous data (see related TXx/CKx).      |  |  |  |  |  |  |  |

|               |              | PGD                            | I/O         | ST             | In-Circuit Debugger and ICSP™ programming data pin  |  |  |  |  |  |  |  |

| 11            | 8            | RC0/P2B/T3CKI/T3G/T1CKI/SOSCC  | )           |                |                                                     |  |  |  |  |  |  |  |

|               |              | RC0                            | I/O         | ST             | Digital I/O.                                        |  |  |  |  |  |  |  |

|               |              | P2B <sup>(2)</sup>             | 0           | CMOS           | Enhanced CCP1 PWM output.                           |  |  |  |  |  |  |  |

|               |              | ТЗСКІ <sup>(1)</sup>           | I           | ST             | Timer3 clock input.                                 |  |  |  |  |  |  |  |

|               |              | T3G                            | I           | ST             | Timer3 external clock gate input.                   |  |  |  |  |  |  |  |

|               |              | T1CKI                          | I           | ST             | Timer1 clock input.                                 |  |  |  |  |  |  |  |

|               |              | SOSCO                          | 0           | _              | Secondary oscillator output.                        |  |  |  |  |  |  |  |

| 12            | 9            | RC1/P2A/CCP2/SOSCI             | 1           | 1              |                                                     |  |  |  |  |  |  |  |

|               |              | RC1                            | I/O         | ST             | Digital I/O.                                        |  |  |  |  |  |  |  |

|               |              | P2A                            | 0           | CMOS           | Enhanced CCP2 PWM output.                           |  |  |  |  |  |  |  |

|               |              | CCP2 <sup>(1)</sup>            | I/O         | ST             | Capture 2 input/Compare 2 output/PWM 2 output.      |  |  |  |  |  |  |  |

|               |              | SOSCI                          | 1           | Analog         | Secondary oscillator input.                         |  |  |  |  |  |  |  |

#### TABLE 1-2: PIC18(L)F2XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

### TABLE 10-1: PORTA I/O SUMMARY

| Pin Name                       | Function | TRIS<br>Setting | ANSEL<br>Setting | Pin<br>Type | Buffer<br>Type | Description                                                                                                          |

|--------------------------------|----------|-----------------|------------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------|

| RA0/C12IN0-/AN0                | RA0      | 0               | 0                | 0           | DIG            | LATA<0> data output; not affected by analog input.                                                                   |

|                                |          | 1               | 0                | Ι           | TTL            | PORTA<0> data input; disabled when analog input enabled.                                                             |

|                                | C12IN0-  | 1               | 1                | Ι           | AN             | Comparators C1 and C2 inverting input.                                                                               |

|                                | AN0      | 1               | 1                | I           | AN             | Analog input 0.                                                                                                      |

| RA1/C12IN1-/AN1                | RA1      | 0               | 0                | 0           | DIG            | LATA<1> data output; not affected by analog input.                                                                   |

|                                |          | 1               | 0                | I           | TTL            | PORTA<1> data input; disabled when analog input enabled.                                                             |

|                                | C12IN1-  | 1               | 1                | I           | AN             | Comparators C1 and C2 inverting input.                                                                               |

|                                | AN1      | 1               | 1                | I           | AN             | Analog input 1.                                                                                                      |

| RA2/C2IN+/AN2/<br>DACOUT/VREF- | RA2      | 0               | 0                | 0           | DIG            | LATA<2> data output; not affected by analog input; disabled when DACOUT enabled.                                     |

|                                |          | 1               | 0                | Ι           | TTL            | PORTA<2> data input; disabled when analog input enabled;<br>disabled when DACOUT enabled.                            |

|                                | C2IN+    | 1               | 1                | Ι           | AN             | Comparator C2 non-inverting input.                                                                                   |

|                                | AN2      | 1               | 1                | Ι           | AN             | Analog output 2.                                                                                                     |

|                                | DACOUT   | x               | 1                | 0           | AN             | DAC Reference output.                                                                                                |

|                                | VREF-    | 1               | 1                | Ι           | AN             | A/D reference voltage (low) input.                                                                                   |

| RA3/C1IN+/AN3/                 | RA3      | 0               |                  | 0           | DIG            | LATA<3> data output; not affected by analog input.                                                                   |

| VREF+                          |          | 1               | 0                | I           | TTL            | PORTA<3> data input; disabled when analog input enabled.                                                             |

|                                | C1IN+    | 1               | 1                | I           | AN             | Comparator C1 non-inverting input.                                                                                   |

|                                | AN3      | 1               | 1                | I           | AN             | Analog input 3.                                                                                                      |

|                                | VREF+    | 1               | 1                | I           | AN             | A/D reference voltage (high) input.                                                                                  |

| RA4/CCP5/C1OUT/                | RA4      | 0               | —                | 0           | DIG            | LATA<4> data output.                                                                                                 |

| RQ/T0CKI                       |          | 1               | _                | I           | ST             | PORTA<4> data input; default configuration on POR.                                                                   |

|                                | CCP5     | 0               | _                | 0           | DIG            | CCP5 Compare output/PWM output, takes priority over RA4 output                                                       |

|                                |          | 1               | —                | I           | ST             | Capture 5 input/Compare 5 output/ PWM 5 output.                                                                      |

|                                | C1OUT    | 0               | _                | 0           | DIG            | Comparator C1 output.                                                                                                |

|                                | SRQ      | 0               | _                | 0           | DIG            | SR latch Q output; take priority over CCP 5 output.                                                                  |

|                                | TOCKI    | 1               | _                | I           | ST             | Timer0 external clock input.                                                                                         |

| RA5/C2OUT/SRNQ/                | RA5      | 0               | 0                | 0           | DIG            | LATA<5> data output; not affected by analog input.                                                                   |

| SS1/<br>HLVDIN/AN4             |          | 1               | 0                | I           | TTL            | PORTA<5> data input; disabled when analog input enabled.                                                             |

| HLVDIN/AN4                     | C2OUT    | 0               | 0                | 0           | DIG            | Comparator C2 output.                                                                                                |

|                                | SRNQ     | 0               | 0                | 0           | DIG            | SR latch $\overline{Q}$ output.                                                                                      |

|                                | SS1      | 1               | 0                | I           | TTL            | SPI slave select input (MSSP1).                                                                                      |

|                                | HLVDIN   | 1               | 1                | I           | AN             | High/Low-Voltage Detect input.                                                                                       |

|                                | AN4      | 1               | 1                | 1           | AN             | A/D input 4.                                                                                                         |

| RA6/CLKO/OSC2                  | RA6      | 0               | _                | 0           | DIG            | LATA<6> data output; enabled in INTOSC modes when CLKO is no<br>enabled.                                             |

|                                |          | 1               | —                | I           | TTL            | PORTA<6> data input; enabled in INTOSC modes when CLKO is not enabled.                                               |

|                                | CLKO     | x               | —                | 0           | DIG            | In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the fre-<br>quency of OSC1 and denotes the instruction cycle rate. |

|                                | OSC2     | x               | _                | 0           | XTAL           | Oscillator crystal output; connects to crystal or resonator in Crystal Oscillator mode.                              |

| RA7/CLKI/OSC1                  | RA7      | 0               | _                | 0           | DIG            | LATA<7> data output; disabled in external oscillator modes.                                                          |

|                                |          | 1               | —                | Ι           | TTL            | PORTA<7> data input; disabled in external oscillator modes.                                                          |

|                                | CLKI     | x               | —                | I           | AN             | External clock source input; always associated with pin function OSC1.                                               |

|                                | OSC1     | x               |                  | Ι           | XTAL           | Oscillator crystal input or external clock source input ST buffer wher<br>configured in RC mode; CMOS otherwise.     |

Legend: AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C.

### **10.7 Port Analog Control**

Most port pins are multiplexed with analog functions such as the Analog-to-Digital Converter and comparators. When these I/O pins are to be used as analog inputs it is necessary to disable the digital input buffer to avoid excessive current caused by improper biasing of the digital input. Individual control of the digital input buffers on pins which share analog functions is provided by the ANSELA, ANSELB, ANSELC, ANSELD and ANSELE registers. Setting an ANSx bit high will disable the associated digital input buffer and cause all reads of that pin to return '0' while allowing analog functions of that pin to operate correctly.

The state of the ANSx bits has no affect on digital output functions. A pin with the associated TRISx bit clear and ANSx bit set will still operate as a digital output but the input mode will be analog. This can cause unexpected behavior when performing readmodify-write operations on the affected port.

All ANSEL register bits default to '1' upon POR and BOR, disabling digital inputs for their associated port pins. All TRIS register bits default to '1' upon POR or BOR, disabling digital outputs for their associated port pins. As a result, all port pins that have an ANSEL register will default to analog inputs upon POR or BOR.

### 10.8 Port Slew Rate Control

The output slew rate of each port is programmable to select either the standard transition rate or a reduced transition rate of approximately 0.1 times the standard to minimize EMI. The reduced transition time is the default slew rate for all ports.

| 10.9 | Register | <b>Definitions</b> – | Port Control |

|------|----------|----------------------|--------------|

|------|----------|----------------------|--------------|

## REGISTER 10-1: PORTX<sup>(1)</sup>: PORTX REGISTER

| R/W-u/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

| Rx7     | Rx6     | Rx5     | Rx4     | Rx3     | Rx2     | Rx1     | Rx0     |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Logona.                    |                             |                                    |

|----------------------------|-----------------------------|------------------------------------|

| R = Readable bit           | W = Writable bit            | U = Unimplemented bit, read as '0' |

| '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown                 |

| -n/n = Value at POR and BO | R/Value at all other Resets |                                    |

bit 7-0 Rx<7:0>: PORTx I/O bit values<sup>(2)</sup>

**Note 1:** Register Description for PORTA, PORTB, PORTC and PORTD.

2: Writes to PORTx are written to corresponding LATx register. Reads from PORTx register is return of I/O pin values.

| Name                 | Bit 7    | Bit 6     | Bit 5             | Bit 4              | Bit 3                   | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|----------------------|----------|-----------|-------------------|--------------------|-------------------------|-----------------------|-----------------------|-----------------------|---------------------|

| CCP1CON              | P1M-     | <1:0>     | DC1B              | <1:0>              |                         | CCP1M<                | 3:0>                  |                       | 198                 |

| CCP2CON              | P2M-     | <1:0>     | DC2B              | <1:0>              |                         | CCP2M<                | 3:0>                  |                       | 198                 |

| CCP3CON              | P3M-     | <1:0>     | DC3B              | <1:0>              |                         | 198                   |                       |                       |                     |

| CCP4CON              | —        | —         | DC4B              | 4B<1:0> CCP4M<3:0> |                         |                       |                       |                       | 198                 |

| CCP5CON              | —        | —         | DC5B              | <1:0>              |                         | CCP5M<                | 3:0>                  |                       | 198                 |

| CCPTMRS0             | C3TSE    | L<1:0>    |                   | C2TS               | TSEL<1:0> — C1TSEL<1:0> |                       |                       |                       |                     |

| CCPTMRS1             | —        | —         | _                 | —                  | C5TSEL                  | _<1:0>                | C4TSE                 | L<1:0>                | 201                 |

| INTCON               | GIE/GIEH | PEIE/GIEL | TMR0IE            | INTOIE             | RBIE                    | TMR0IF                | INTOIF                | RBIF                  | 109                 |

| IPR1                 | —        | ADIP      | RC1IP             | TX1IP              | SSP1IP                  | CCP1IP                | TMR2IP                | TMR1IP                | 121                 |

| IPR2                 | OSCFIP   | C1IP      | C2IP              | EEIP               | BCL1IP                  | HLVDIP                | TMR3IP                | CCP2IP                | 122                 |

| IPR4                 | —        | —         | _                 | —                  | _                       | CCP5IP                | CCP4IP                | CCP3IP                | 124                 |

| PIE1                 | —        | ADIE      | RC1IE             | TX1IE              | SSP1IE                  | CCP1IE                | TMR2IE                | TMR1IE                | 117                 |

| PIE2                 | OSCFIE   | C1IE      | C2IE              | EEIE               | BCL1IE                  | HLVDIE                | TMR3IE                | CCP2IE                | 118                 |

| PIE4                 | _        | _         | _                 | _                  | _                       | CCP5IE                | CCP4IE                | CCP3IE                | 120                 |

| PIR1                 | —        | ADIF      | RC1IF             | TX1IF              | SSP1IF                  | CCP1IF                | TMR2IF                | TMR1IF                | 112                 |

| PIR2                 | OSCFIF   | C1IF      | C2IF              | EEIF               | BCL1IF                  | HLVDIF                | TMR3IF                | CCP2IF                | 113                 |

| PIR4                 | —        | —         | _                 | —                  | _                       | CCP5IF                | CCP4IF                | CCP3IF                | 115                 |

| PMD0                 | UART2MD  | UART1MD   | TMR6MD            | TMR5MD             | TMR4MD                  | TMR3MD                | TMR2MD                | TMR1MD                | 52                  |

| PMD1                 | MSSP2MD  | MSSP1MD   | _                 | CCP5MD             | CCP4MD                  | CCP3MD                | CCP2MD                | CCP1MD                | 53                  |

| PR2                  |          |           |                   | Timer2 Per         | riod Register           |                       |                       |                       | _                   |

| PR4                  |          |           |                   | Timer4 Per         | riod Register           |                       |                       |                       | _                   |

| PR6                  |          |           |                   | Timer6 Per         | riod Register           |                       |                       |                       | _                   |

| T2CON                | —        |           | T2OU              | TPS<3:0>           |                         | TMR2ON                | T2CKP                 | S<1:0>                | 166                 |

| T4CON                | —        |           | T4OU              | TPS<3:0>           |                         | TMR4ON                | T4CKP                 | S<1:0>                | 166                 |

| T6CON                | —        |           | T6OU <sup>-</sup> | TPS<3:0>           |                         | TMR6ON                | T6CKP                 | S<1:0>                | 166                 |

| TMR2                 |          |           |                   | Timer2             | Register                |                       |                       |                       | —                   |

| TMR4                 |          |           |                   | Timer4             | Register                |                       |                       |                       | _                   |

| TMR6                 |          |           |                   | Timer6             | Register                |                       |                       |                       | —                   |

| TRISB                | TRISB7   | TRISB6    | TRISB5            | TRISB4             | TRISB3                  | TRISB2                | TRISB1                | TRISB0                | 151                 |

| TRISC                | TRISC7   | TRISC6    | TRISC5            | TRISC4             | TRISC3                  | TRISC2                | TRISC1                | TRISC0                | 151                 |

| TRISD <sup>(1)</sup> | TRISD7   | TRISD6    | TRISD5            | TRISD4             | TRISD3                  | TRISD2                | TRISD1                | TRISD0                | 151                 |

| TRISE                | WPUE3    | —         | —                 | —                  | _                       | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 151                 |

## TABLE 14-10: REGISTERS ASSOCIATED WITH STANDARD PWM

**Legend:** — = Unimplemented location, read as '0'. Shaded bits are not used by Standard PWM mode.

Note 1: These registers/bits are available on PIC18(L)F4XK22 devices.

## TABLE 14-11: CONFIGURATION REGISTERS ASSOCIATED WITH STANDARD PWM

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| CONFIG3H | MCLRE | —     | P2BMX | T3CMX | HFOFST | CCP3MX | PBADEN | CCP2MX | 348                 |

**Legend:** — = Unimplemented location, read as '0'. Shaded bits are not used by Standard PWM mode.

© 2010-2016 Microchip Technology Inc.

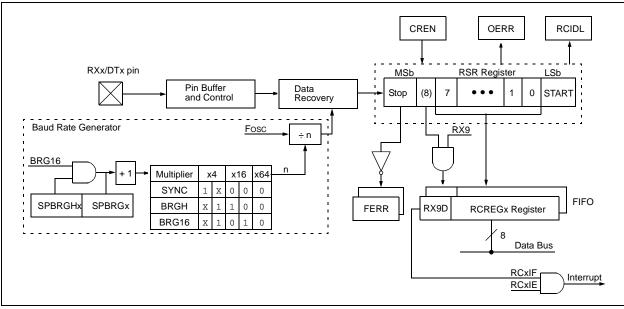

## FIGURE 16-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTAx)

- Receive Status and Control (RCSTAx)

- Baud Rate Control (BAUDCONx)

These registers are detailed in Register 16-1, Register 16-2 and Register 16-3, respectively.

For all modes of EUSART operation, the TRIS control bits corresponding to the RXx/DTx and TXx/CKx pins should be set to '1'. The EUSART control will automatically reconfigure the pin from input to output, as needed.

When the receiver or transmitter section is not enabled then the corresponding RXx/DTx or TXx/CKx pin may be used for general purpose input and output.

|        |                   | SYNC = 0, BRGH = 1, BRG16 = 0 |                              |                   |            |                              |                   |            |                              |                    |            |                              |  |  |  |

|--------|-------------------|-------------------------------|------------------------------|-------------------|------------|------------------------------|-------------------|------------|------------------------------|--------------------|------------|------------------------------|--|--|--|

| BAUD   | Fosc = 64.000 MHz |                               |                              | Fosc = 18.432 MHz |            |                              | Fosc = 16.000 MHz |            |                              | Fosc = 11.0592 MHz |            |                              |  |  |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRGx<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRGx<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRGx<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRGx<br>value<br>(decimal) |  |  |  |

| 300    | —                 | —                             | —                            |                   | —          | —                            |                   | —          | _                            |                    |            | —                            |  |  |  |

| 1200   | _                 | _                             | _                            | —                 | _          | _                            | _                 | _          | _                            | _                  | _          | _                            |  |  |  |

| 2400   | —                 | —                             | —                            | —                 | —          | —                            | _                 | _          | _                            | _                  | _          | _                            |  |  |  |

| 9600   | _                 | _                             | _                            | 9600              | 0.00       | 119                          | 9615              | 0.16       | 103                          | 9600               | 0.00       | 71                           |  |  |  |

| 10417  | —                 | _                             | _                            | 10378             | -0.37      | 110                          | 10417             | 0.00       | 95                           | 10473              | 0.53       | 65                           |  |  |  |

| 19.2k  | 19.23k            | 0.16                          | 207                          | 19.20k            | 0.00       | 59                           | 19.23k            | 0.16       | 51                           | 19.20k             | 0.00       | 35                           |  |  |  |

| 57.6k  | 57.97k            | 0.64                          | 68                           | 57.60k            | 0.00       | 19                           | 58.82k            | 2.12       | 16                           | 57.60k             | 0.00       | 11                           |  |  |  |

| 115.2k | 114.29k           | -0.79                         | 34                           | 115.2k            | 0.00       | 9                            | 111.1k            | -3.55      | 8                            | 115.2k             | 0.00       | 5                            |  |  |  |

## TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                              |                  |            |                              |                   |            |                              |                  |            |                              |  |  |

|--------|-------------------------------|------------|------------------------------|------------------|------------|------------------------------|-------------------|------------|------------------------------|------------------|------------|------------------------------|--|--|

| BAUD   | Fosc = 8.000 MHz              |            |                              | Fosc = 4.000 MHz |            |                              | Fosc = 3.6864 MHz |            |                              | Fosc = 1.000 MHz |            |                              |  |  |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRGx<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRGx<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SxBRGx<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRGx<br>value<br>(decimal) |  |  |

| 300    | —                             | _          | _                            |                  |            | _                            | _                 |            | _                            | 300              | 0.16       | 207                          |  |  |

| 1200   | _                             | _          | _                            | 1202             | 0.16       | 207                          | 1200              | 0.00       | 191                          | 1202             | 0.16       | 51                           |  |  |

| 2400   | 2404                          | 0.16       | 207                          | 2404             | 0.16       | 103                          | 2400              | 0.00       | 95                           | 2404             | 0.16       | 25                           |  |  |

| 9600   | 9615                          | 0.16       | 51                           | 9615             | 0.16       | 25                           | 9600              | 0.00       | 23                           | _                | _          | _                            |  |  |

| 10417  | 10417                         | 0.00       | 47                           | 10417            | 0.00       | 23                           | 10473             | 0.53       | 21                           | 10417            | 0.00       | 5                            |  |  |

| 19.2k  | 19231                         | 0.16       | 25                           | 19.23k           | 0.16       | 12                           | 19.2k             | 0.00       | 11                           | _                | _          | _                            |  |  |

| 57.6k  | 55556                         | -3.55      | 8                            | _                | _          | _                            | 57.60k            | 0.00       | 3                            | —                | _          | _                            |  |  |

| 115.2k | _                             | _          | _                            | _                | _          | _                            | 115.2k            | 0.00       | 1                            | —                | _          | _                            |  |  |

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                                 |                   |            |                                 |                   |            |                                 |                    |            |                                 |

|--------|-------------------------------|------------|---------------------------------|-------------------|------------|---------------------------------|-------------------|------------|---------------------------------|--------------------|------------|---------------------------------|

| BAUD   | Fosc = 64.000 MHz             |            |                                 | Fosc = 18.432 MHz |            |                                 | Fosc = 16.000 MHz |            |                                 | Fosc = 11.0592 MHz |            |                                 |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRGHx:<br>SPBRGx<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRGHx:<br>SPBRGx<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRGHx<br>:SPBRGx<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRGHx:<br>SPBRGx<br>(decimal) |

| 300    | 300.0                         | 0.00       | 13332                           | 300.0             | 0.00       | 3839                            | 300.03            | 0.01       | 3332                            | 300.0              | 0.00       | 2303                            |

| 1200   | 1200.1                        | 0.01       | 3332                            | 1200              | 0.00       | 959                             | 1200.5            | 0.04       | 832                             | 1200               | 0.00       | 575                             |

| 2400   | 2399                          | -0.02      | 1666                            | 2400              | 0.00       | 479                             | 2398              | -0.08      | 416                             | 2400               | 0.00       | 287                             |

| 9600   | 9592                          | -0.08      | 416                             | 9600              | 0.00       | 119                             | 9615              | 0.16       | 103                             | 9600               | 0.00       | 71                              |

| 10417  | 10417                         | 0.00       | 383                             | 10378             | -0.37      | 110                             | 10417             | 0.00       | 95                              | 10473              | 0.53       | 65                              |

| 19.2k  | 19.23k                        | 0.16       | 207                             | 19.20k            | 0.00       | 59                              | 19.23k            | 0.16       | 51                              | 19.20k             | 0.00       | 35                              |

| 57.6k  | 57.97k                        | 0.64       | 68                              | 57.60k            | 0.00       | 19                              | 58.82k            | 2.12       | 16                              | 57.60k             | 0.00       | 11                              |

| 115.2k | 114.29k                       | -0.79      | 34                              | 115.2k            | 0.00       | 9                               | 111.11k           | -3.55      | 8                               | 115.2k             | 0.00       | 5                               |

## 17.4 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 17-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 17-5. The maximum recommended impedance for analog sources is  $3 \ k\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D

acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 17-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

## EQUATION 17-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature = 50°C and external impedance of 10k

$$\Omega$$

3.0V VDD

$$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

= 5µs + TC + [(Temperature - 25°C)(0.05µs/°C)]

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{2047}\right) = V_{CHOLD} \qquad :[1] V_{CHOLD} charged to within 1/2 lsb

$$V_{APPLIED}\left(1 - e^{-\frac{TC}{RC}}\right) = V_{CHOLD} \qquad :[2] V_{CHOLD} charge response to VAPPLIED

$$V_{APPLIED}\left(1 - e^{-\frac{TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{2047}\right) \qquad :combining [1] and [2]$$

Solving for Tc:

$$T_{C} = -CHOLD(RIC + RSS + RS) ln(1/2047)$$

$$= -13.5pF(Ik\Omega + 700\Omega + 10k\Omega) ln(0.0004885)$$

$$= 1.20\mu s$$$$$$$$

$TACQ = 5\mu s + 1.20\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$ = 7.45\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

## 21.3 Register Definitions: FVR Control

| REGISTER       | <u> 21-1: VREF</u>                                                                                                                                                                                                                                                                                                                                                                                                                                       | CON0: FIXED                                           |                | REFERENC          | E CONTROL F      | REGISTER         |              |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------|-------------------|------------------|------------------|--------------|--|

| R/W-0          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                 | R/W-1          | U-0               | U-0              | U-0              | U-0          |  |

| FVREN          | FVREN FVRST FVRS<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       | 6<1:0>         | —                 | —                | —                | —            |  |

| bit 7          |                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ·                                                     |                | -                 |                  |                  | bit          |  |

| Legend:        |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                       |                |                   |                  |                  |              |  |

| R = Readat     | ole bit                                                                                                                                                                                                                                                                                                                                                                                                                                                  | W = Writable                                          | bit            | U = Unimplei      | mented bit, read | as '0'           |              |  |

| u = Bit is ur  | nchanged                                                                                                                                                                                                                                                                                                                                                                                                                                                 | x = Bit is unk                                        | nown           | -n/n = Value      | at POR and BO    | R/Value at all o | other Resets |  |

| '1' = Bit is s | et                                                                                                                                                                                                                                                                                                                                                                                                                                                       | '0' = Bit is cle                                      | ared           |                   |                  |                  |              |  |

| bit 6          | 0 = Fixed V                                                                                                                                                                                                                                                                                                                                                                                                                                              | ed Voltage Refe<br>oltage Referenc<br>oltage Referenc | e output is no | ot ready or not e | enabled          |                  |              |  |

| bit 5-4        | <ul> <li>1 = Fixed Voltage Reference output is ready for use</li> <li>FVRS&lt;1:0&gt;: Fixed Voltage Reference Selection bits</li> <li>00 = Fixed Voltage Reference Peripheral output is off</li> <li>01 = Fixed Voltage Reference Peripheral output is 1x (1.024V)</li> <li>10 = Fixed Voltage Reference Peripheral output is 2x (2.048V)<sup>(1)</sup></li> <li>11 = Fixed Voltage Reference Peripheral output is 4x (4.096V)<sup>(1)</sup></li> </ul> |                                                       |                |                   |                  |                  |              |  |

| bit 3-2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Read as '0'. Mai                                      | •              | •                 |                  |                  |              |  |

| bit 1-0        | Unimpleme                                                                                                                                                                                                                                                                                                                                                                                                                                                | nted: Read as '                                       | 0'.            |                   |                  |                  |              |  |

| Note 1.        | Fixed Voltage B                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                       |                |                   |                  |                  |              |  |

#### REGISTER 21-1: VREFCON0: FIXED VOLTAGE REFERENCE CONTROL REGISTER

Note 1: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name     | Bit 7 | Bit 6 | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|----------|-------|-------|-----------|-------|-------|-------|-------|-------|---------------------|

| VREFCON0 | FVREN | FVRST | FVRS<1:0> |       | _     |       |       |       | 332                 |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by the FVR module.

## 24.0 SPECIAL FEATURES OF THE CPU

PIC18(L)F2X/4XK22 devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in Section 2.0 "Oscillator Module (With Fail-Safe Clock Monitor)".

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, PIC18(L)F2X/4XK22 devices have a Watchdog Timer, which is either permanently enabled via the Configuration bits or software controlled (if configured as disabled).

The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

## 24.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In Normal operation mode, a TBLWT instruction with the TBLPTR pointing to the Configuration register sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration register. The Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 6.6 "Writing to Flash Program Memory".

| BTFSC                                                | BTFSC Bit Test File, Skip if Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                    |                 | BTFSS                                                                                                                                                                                                                                                 | Bit Test File, Skip if Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   |           |  |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------|--|

| Syntax:                                              | BTFSC f, b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | {,a}                               |                 | Syntax:                                                                                                                                                                                                                                               | BTFSS f, b {                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | {,a}                              |           |  |

| Operands:                                            | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                    |                 | Operands:                                                                                                                                                                                                                                             | $0 \le f \le 255$<br>$0 \le b < 7$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                   |           |  |

| Operation:                                           | skip if (f <b>)</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | = 0                                |                 | Operation:                                                                                                                                                                                                                                            | skip if (f <b>) = 1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   |           |  |

| Status Affected:                                     | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |                 | Status Affected:                                                                                                                                                                                                                                      | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                   |           |  |