Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I²C, SPI, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 30x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k22-e-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.11.3 CLOCK SWITCH TIMING

When switching between one oscillator and another, the new oscillator may not be operating which saves power (see Figure 2-9). If this is the case, there is a delay after the SCS<1:0> bits of the OSCCON register are modified before the frequency change takes place. The OSTS and IOFS bits of the OSCCON register will reflect the current active status of the external and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- 1. SCS<1:0> bits of the OSCCON register are modified.

- 2. The old clock continues to operate until the new clock is ready.

- 3. Clock switch circuitry waits for two consecutive rising edges of the old clock after the new clock ready signal goes true.

- 4. The system clock is held low starting at the next falling edge of the old clock.

- 5. Clock switch circuitry waits for an additional two rising edges of the new clock.

- 6. On the next falling edge of the new clock the low hold on the system clock is released and new clock is switched in as the system clock.

- 7. Clock switch is complete.

See Figure 2-1 for more details.

If the HFINTOSC is the source of both the old and new frequency, there is no start-up delay before the new frequency is active. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in **Section 27.0 "Electrical Specifications**", under AC Specifications (Oscillator Module).

# 2.12 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device.

This mode allows the application to wake-up from Sleep, perform a few instructions using the HFINTOSC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

Note: Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCCON register to remain clear.

When the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) is enabled (see **Section 2.5.1 "Oscillator Start-up Timer (OST)**"). The OST will suspend program execution until 1024 oscillations are counted. Two-Speed Start-up mode minimizes the delay in code execution by operating from the internal oscillator as the OST is counting. When the OST count reaches 1024 and the OSTS bit of the OSCCON register is set, program execution switches to the external oscillator.

#### 2.12.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is enabled when all of the following settings are configured as noted:

- Two-Speed Start-up mode is enabled when the IESO of the CONFIG1H Configuration register is set.

- SCS<1:0> (of the OSCCON register) = 00.

- FOSC<2:0> bits of the CONFIG1H Configuration register are configured for LP, XT or HS mode.

Two-Speed Start-up mode becomes active after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

## EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR      |

|-----------------|-------------------------|

|                 | ;SAVED IN FAST REGISTER |

|                 | ; STACK                 |

| •               |                         |

| •               |                         |

|                 |                         |

| SUB1 •          |                         |

| •               |                         |

| RETURN, FAST    |                         |

|                 | ;IN FAST REGISTER STACK |

#### 5.2.2 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 5.2.2.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of two (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 5-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, | W |

|-------|-------|---------|---|

|       | CALL  | TABLE   |   |

| ORG   | nn00h |         |   |

| TABLE | ADDWF | PCL     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | •     |         |   |

|       | •     |         |   |

|       | •     |         |   |

|       |       |         |   |

### 5.2.2.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 6.1 "Table Reads and Table Writes".

# 5.6 Data Addressing Modes

Note: The execution of some instructions in the core PIC18 instruction set are changed when the PIC18 extended instruction set is enabled. See Section 5.7 "Data Memory and the Extended Instruction Set" for more information.

While the program memory can be addressed in only one way – through the program counter – information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 5.7.1** "**Indexed Addressing with Literal Offset**".

# 5.6.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 5.6.2 DIRECT ADDRESSING

Direct addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byteoriented instructions use some version of direct addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (**Section 5.4.3 "General**  **Purpose Register File**") or a location in the Access Bank (Section 5.4.2 "Access Bank") as the data source for the instruction.

The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 5.4.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

# 5.6.3 INDIRECT ADDRESSING

Indirect addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations which are to be read or written. Since the FSRs are themselves located in RAM as Special File Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for indirect addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 5-5.

# EXAMPLE 5-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0, 100h | ; |                |

|---------|-------|------------|---|----------------|

| NEXT    | CLRF  | POSTINC0   | ; | Clear INDF     |

|         |       |            | ; | register then  |

|         |       |            | ; | inc pointer    |

|         | BTFSS | FSROH, 1   | ; | All done with  |

|         |       |            | ; | Bank1?         |

|         | BRA   | NEXT       | ; | NO, clear next |

| CONTINU | JE    |            | ; | YES, continue  |

# 8.0 8 x 8 HARDWARE MULTIPLIER

# 8.1 Introduction

All PIC18 devices include an 8 x 8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 8-1.

#### 8.2 Operation

Example 8-1 shows the instruction sequence for an 8 x 8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 8-2 shows the sequence to do an 8 x 8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 8-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MULWF ARG2 ; ARG1 * ARG2 -><br>; PRODH:PRODL | MOVF  | ARG1, | W | ; |       |     |       |    |  |

|----------------------------------------------|-------|-------|---|---|-------|-----|-------|----|--|

| ; PRODH:PRODL                                | MULWF | ARG2  |   | ; | ARG1  | *   | ARG2  | -> |  |

|                                              |       |       |   | ; | PRODE | I:1 | PRODL |    |  |

# EXAMPLE 8-2: 8 x 8 SIGNED MULTIPLY

| MOVF  | ARG1, W  |   |                |

|-------|----------|---|----------------|

| MULWF | ARG2     | ; | ARG1 * ARG2 -> |

|       |          | ; | PRODH:PRODL    |

| BTFSC | ARG2, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG1         |

| MOVF  | ARG2, W  |   |                |

| BTFSC | ARG1, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG2         |

|       |          |   |                |

|                  |                           | Program<br>Memory<br>(Words) | Cycles<br>(Max) | Time     |          |          |         |

|------------------|---------------------------|------------------------------|-----------------|----------|----------|----------|---------|

| Routine          | Multiply Method           |                              |                 | @ 64 MHz | @ 40 MHz | @ 10 MHz | @ 4 MHz |

| Q v Q unoignod   | Without hardware multiply | 13                           | 69              | 4.3 μs   | 6.9 μs   | 27.6 μs  | 69 μs   |

| 8 x 8 unsigned   | Hardware multiply         | 1                            | 1               | 62.5 ns  | 100 ns   | 400 ns   | 1 μs    |

| Q v Q aignad     | Without hardware multiply | 33                           | 91              | 5.7 μs   | 9.1 μs   | 36.4 μs  | 91 μs   |

| 8 x 8 signed     | Hardware multiply         | 6                            | 6               | 375 ns   | 600 ns   | 2.4 μs   | 6 μs    |

| 16 x 16 uppigpod | Without hardware multiply | 21                           | 242             | 15.1 μs  | 24.2 μs  | 96.8 μs  | 242 μs  |

| 16 x 16 unsigned | Hardware multiply         | 28                           | 28              | 1.8 μs   | 2.8 μs   | 11.2 μs  | 28 μs   |

| 16 x 16 signed   | Without hardware multiply | 52                           | 254             | 15.9 μs  | 25.4 μs  | 102.6 μs | 254 μs  |

| 16 x 16 signed   | Hardware multiply         | 35                           | 40              | 2.5 μs   | 4.0 μs   | 16.0 μs  | 40 μs   |

### TABLE 8-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

### 10.2 PORTB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., disable the output driver). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

| EXAMPLE 10-2: | INITIALIZING PORTB |

|---------------|--------------------|

| EXAMPLE 10-2: | INITIALIZING PURIB |

| MOVLB | 0xF    | ; Set BSR for banked SFRs     |

|-------|--------|-------------------------------|

| CLRF  | PORTB  | ; Initialize PORTB by         |

|       |        | ; clearing output             |

|       |        | ; data latches                |

| CLRF  | LATB   | ; Alternate method            |

|       |        | ; to clear output             |

|       |        | ; data latches                |

| MOVLW | 0F0h   | ; Value for init              |

| MOVWF | ANSELB | ; Enable RB<3:0> for          |

|       |        | ; digital input pins          |

|       |        | ; (not required if config bit |

|       |        | ; PBADEN is clear)            |

| MOVLW | 0CFh   | ; Value used to               |

|       |        | ; initialize data             |

|       |        | ; direction                   |

| MOVWF | TRISB  | ; Set RB<3:0> as inputs       |

|       |        | ; RB<5:4> as outputs          |

|       |        | ; RB<7:6> as inputs           |

|       |        |                               |

#### 10.2.1 PORTB OUTPUT PRIORITY

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the higher priority. Table 10-4 lists the PORTB pin functions from the highest to the lowest priority.

Analog input functions, such as ADC, comparator and SR latch inputs, are not shown in the priority lists.

These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below.

# **10.3 Additional PORTB Pin Functions**

PORTB pins RB<7:4> have an interrupt-on-change option. All PORTB pins have a weak pull-up option.

#### 10.3.1 WEAK PULL-UPS

Each of the PORTB pins has an individually controlled weak internal pull-up. When set, each bit of the WPUB register enables the corresponding pin pull-up. When cleared, the RBPU bit of the INTCON2 register enables pull-ups on all pins which also have their corresponding WPUB bit set. When set, the RBPU bit disables all weak pull-ups. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

| Note: | On a Power-on Reset, RB<5:0> are configured as analog inputs by default and read as '0'; RB<7:6> are configured as digital inputs. |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | When the PBADEN Configuration bit is set to '1', RB<5:0> will alternatively be configured as digital inputs on POR.                |

|       |                                                                                                                                    |

#### 10.3.2 INTERRUPT-ON-CHANGE

Four of the PORTB pins (RB<7:4>) are individually configurable as interrupt-on-change pins. Control bits in the IOCB register enable (when set) or disable (when clear) the interrupt function for each pin.

When set, the RBIE bit of the INTCON register enables interrupts on all pins which also have their corresponding IOCB bit set. When clear, the RBIE bit disables all interrupt-on-changes.

Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt-on-change comparison).

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of PORTB. The 'mismatch' outputs of the last read are OR'd together to set the PORTB Change Interrupt flag bit (RBIF) in the INTCON register.

This interrupt can wake the device from the Sleep mode, or any of the Idle modes. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- Any read or write of PORTB to clear the mismatch condition (except when PORTB is the source or destination of a MOVFF instruction).

- b) Execute at least one instruction after reading or writing PORTB, then clear the flag bit, RBIF.

## 10.6 PORTE Registers

Depending on the particular PIC18(L)F2X/4XK22 device selected, PORTE is implemented in two different ways.

#### 10.6.1 PORTE ON 40/44-PIN DEVICES

For PIC18(L)F2X/4XK22 devices, PORTE is a 4-bit wide port. Three pins (RE0/P3A/CCP3/AN5, RE1/P3B/ AN6 and RE2/CCP5/AN7) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's.

The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., disable the output driver). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

TRISE controls the direction of the REx pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

Note: On a Power-on Reset, RE<2:0> are configured as analog inputs.

The fourth pin of PORTE ( $\overline{\text{MCLR}}/\text{VPP}/\text{RE3}$ ) is an input only pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin (MCLRE = 0), it functions as a digital input only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming.

Note: On a Power-on Reset, RE3 is enabled as a digital input only if Master Clear functionality is disabled.

#### EXAMPLE 10-5: INITIALIZING PORTE

| CLRF  | PORTE  | ; | Initialize PORTE by   |

|-------|--------|---|-----------------------|

|       |        | ; | clearing output       |

|       |        | ; | data latches          |

| CLRF  | LATE   | ; | Alternate method      |

|       |        | ; | to clear output       |

|       |        | ; | data latches          |

| CLRF  | ANSELE | ; | Configure analog pins |

|       |        | ; | for digital only      |

| MOVLW | 05h    | ; | Value used to         |

|       |        | ; | initialize data       |

|       |        | ; | direction             |

| MOVWF | TRISE  | ; | Set RE<0> as input    |

|       |        | ; | RE<1> as output       |

|       |        | ; | RE<2> as input        |

| 1     |        |   |                       |

# 10.6.2 PORTE ON 28-PIN DEVICES

For PIC18F2XK22 devices, PORTE is only available when Master Clear functionality is disabled (MCLR = 0). In these cases, PORTE is a single bit, input only port comprised of RE3 only. The pin operates as previously described.

# 10.6.3 RE3 WEAK PULL-UP

The port RE3 pin has an individually controlled weak internal pull-up. When set, the WPUE3 (TRISE<7>) bit enables the RE3 pin pull-up. The RBPU bit of the INT-CON2 register controls pull-ups on both PORTB and PORTE. When RBPU = 0, the weak pull-ups become active on all pins which have the WPUE3 or WPUBx bits set. When set, the RBPU bit disables all weak pull-ups. The pull-ups are disabled on a Power-on Reset. When the RE3 port pin is configured as MCLR, (CON-FIG3H<7>, MCLRE=1 and CONFIG4L<2>, LVP=0), or configured for Low Voltage Programming, (MCLRE=x and LVP=1), the pull-up is always enabled and the WPUE3 bit has no effect.

# 10.6.4 PORTE OUTPUT PRIORITY

Each PORTE pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the higher priority. Table 10-4 lists the PORTE pin functions from the highest to the lowest priority.

Analog input functions, such as ADC, comparator and SR latch inputs, are not shown in the priority lists.

These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below.

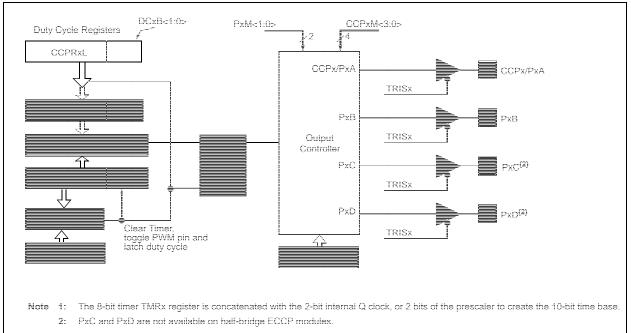

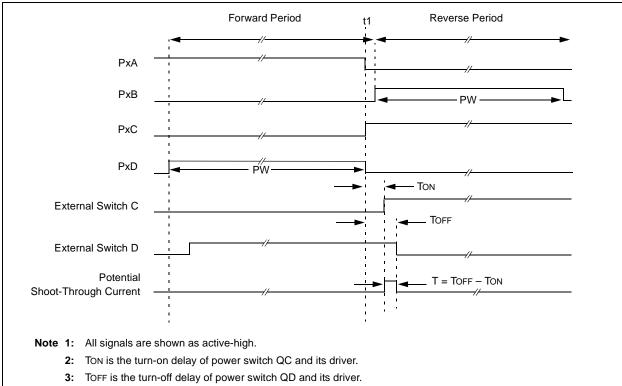

# 14.4 PWM (Enhanced Mode)

The enhanced PWM function described in this section is available for CCP modules ECCP1, ECCP2 and ECCP3, with any differences between modules noted.

The enhanced PWM mode generates a Pulse-Width Modulation (PWM) signal on up to four different output pins with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PRx registers

- TxCON registers

- CCPRxL registers

- CCPxCON registers

The ECCP modules have the following additional PWM registers which control Auto-shutdown, Auto-restart, Dead-band Delay and PWM Steering modes:

- ECCPxAS registers

- PSTRxCON registers

- PWMxCON registers

The enhanced PWM module can generate the following five PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

- Single PWM with PWM Steering mode

To select an Enhanced PWM Output mode, the PxM<1:0> bits of the CCPxCON register must be configured appropriately.

The PWM outputs are multiplexed with I/O pins and are designated PxA, PxB, PxC and PxD. The polarity of the PWM pins is configurable and is selected by setting the CCPxM bits in the CCPxCON register appropriately.

Figure 14-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Table 14-12 shows the pin assignments for various Enhanced PWM modes.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

- **3:** Any pin not used in the enhanced PWM mode is available for alternate pin functions, if applicable.

- 4: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

### FIGURE 14-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

#### 14.4.3 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the CCPxAS<2:0> bits of the ECCPxAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- Comparator Cx (async\_CxOUT)

- Setting the CCPxASE bit in firmware

A shutdown condition is indicated by the CCPxASE (Auto-Shutdown Event Status) bit of the ECCPxAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The CCPxASE bit is set to '1'. The CCPxASE will remain set until cleared in firmware or an auto-restart occurs (see Section 14.4.4 "Auto-Restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [PxA/PxC] and [PxB/PxD].

The state of each pin pair is determined by the PSSxAC<1:0> and PSSxBD<1:0> bits of the ECCPxAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

Note 1: The auto-shutdown condition is a levelbased signal, not an edge-based signal. As long as the level is present, the autoshutdown will persist.

- 2: Writing to the CCPxASE bit is disabled while an auto-shutdown condition persists.

- 3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

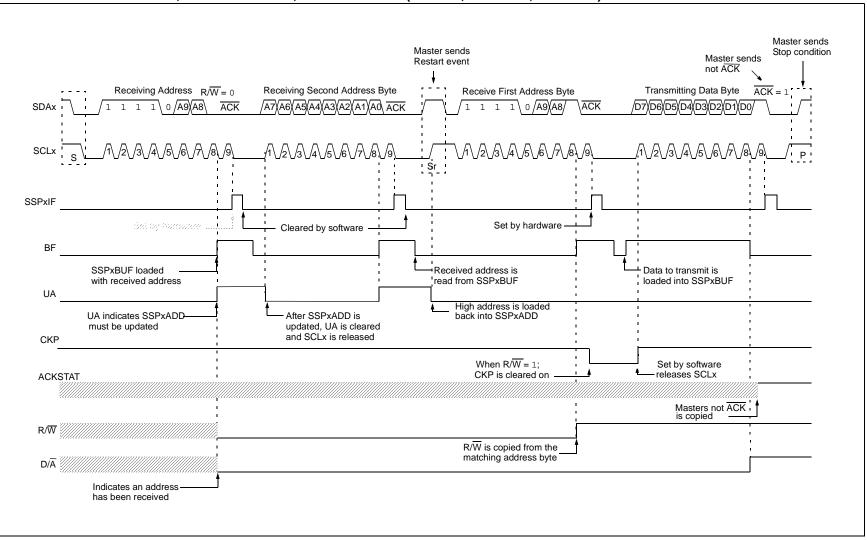

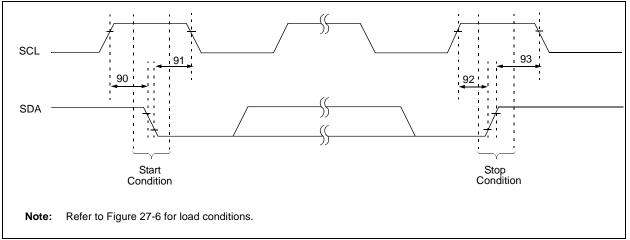

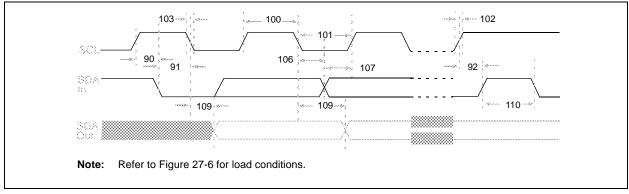

#### FIGURE 15-22: I<sup>2</sup>C SLAVE, 10-BIT ADDRESS, TRANSMISSION (SEN = 0, AHEN = 0, DHEN = 0)

PIC18(L)F2X/4XK22

# 15.6 I<sup>2</sup>C Master Mode

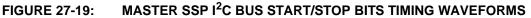

Master mode is enabled by setting and clearing the appropriate SSPxM bits in the SSPxCON1 register and by setting the SSPxEN bit. In Master mode, the SCLx and SDAx lines are set as inputs and are manipulated by the MSSPx hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSPx module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDAx and SCLx lines.

The following events will cause the SSPx Interrupt Flag bit, SSPxIF, to be set (SSPx interrupt, if enabled):

- Start condition detected

- Stop condition detected

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSPx module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

# 15.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDAx, while SCLx outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDAx, while SCLx outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCLx. See Section 15.7 "Baud Rate Generator" for more detail.

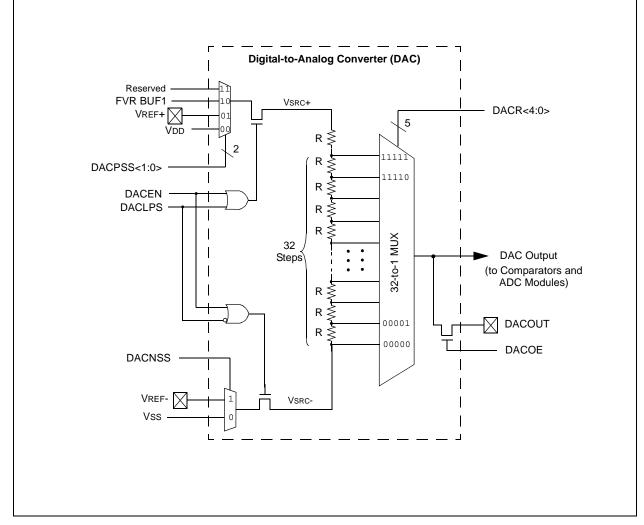

## FIGURE 22-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

| DEV<10:3> | DEV<2:0> | Part Number  |

|-----------|----------|--------------|

|           | 000      | PIC18F46K22  |

| 0101 0100 | 001      | PIC18LF46K22 |

| 0101 0100 | 010      | PIC18F26K22  |

|           | 011      | PIC18LF26K22 |

|           | 000      | PIC18F45K22  |

| 0101 0101 | 001      | PIC18LF45K22 |

|           | 010      | PIC18F25K22  |

|           | 011      | PIC18LF25K22 |

|           | 000      | PIC18F44K22  |

| 0101 0110 | 001      | PIC18LF44K22 |

| 0101 0110 | 010      | PIC18F24K22  |

|           | 011      | PIC18LF24K22 |

|           | 000      | PIC18F43K22  |

| 0101 0111 | 001      | PIC18LF43K22 |

| 0101 0111 | 010      | PIC18F23K22  |

|           | 011      | PIC18LF23K22 |

TABLE 24-2: DEVICE ID TABLE FOR THE PIC18(L)F2X/4XK22 FAMILY

| CPFSGT               | Compare           | f with W, sk                         | ip if f > W     |  |  |  |  |  |

|----------------------|-------------------|--------------------------------------|-----------------|--|--|--|--|--|

| Syntax:              | CPFSGT            | f {,a}                               |                 |  |  |  |  |  |

| Operands:            | 0 ≤ f ≤ 255       | () - y                               |                 |  |  |  |  |  |

| oporaliaol           | a ∈ [0,1]         |                                      |                 |  |  |  |  |  |

| Operation:           | (f) – (W),        |                                      |                 |  |  |  |  |  |

|                      | skip if (f) > (   |                                      |                 |  |  |  |  |  |

|                      | (unsigned c       | omparison)                           |                 |  |  |  |  |  |

| Status Affected:     | None              |                                      |                 |  |  |  |  |  |

| Encoding:            | 0110              | 010a fff                             | f fff           |  |  |  |  |  |

| Description:         | Compares t        | Compares the contents of data memory |                 |  |  |  |  |  |

|                      |                   | o the contents                       |                 |  |  |  |  |  |

|                      | 1 0               | an unsigned s                        |                 |  |  |  |  |  |

|                      |                   | nts of 'f' are gre                   |                 |  |  |  |  |  |

|                      |                   | WREG, then t<br>s discarded ar       |                 |  |  |  |  |  |

|                      |                   | stead, making                        |                 |  |  |  |  |  |

|                      | 2-cycle inst      |                                      |                 |  |  |  |  |  |

|                      | lf 'a' is '0', tl | he Access Bar                        | nk is selected. |  |  |  |  |  |

|                      | ,                 | he BSR is used                       | d to select the |  |  |  |  |  |

|                      | GPR bank.         | nd the extende                       | dinstruction    |  |  |  |  |  |

|                      |                   | ed, this instruc                     |                 |  |  |  |  |  |

|                      |                   | _iteral Offset A                     | •               |  |  |  |  |  |

|                      |                   | ever f ≤ 95 (5F                      |                 |  |  |  |  |  |

|                      |                   | .2.3 "Byte-Ori                       |                 |  |  |  |  |  |

|                      |                   | d Instruction                        |                 |  |  |  |  |  |

|                      |                   | Literal Offset Mode" for details.    |                 |  |  |  |  |  |

| Words:               | 1                 |                                      |                 |  |  |  |  |  |

| Cycles:              | 1(2)              |                                      | l felleure d    |  |  |  |  |  |

|                      | •                 | cles if skip and<br>2-word instrue   |                 |  |  |  |  |  |

| Q Cycle Activity:    | by a              |                                      |                 |  |  |  |  |  |

| Q1                   | Q2                | Q3                                   | Q4              |  |  |  |  |  |

| Decode               | Read              | Process                              | No              |  |  |  |  |  |

| Decoud               | register 'f'      | Data                                 | operation       |  |  |  |  |  |

| If skip:             | 0                 |                                      |                 |  |  |  |  |  |

| Q1                   | Q2                | Q3                                   | Q4              |  |  |  |  |  |

| No                   | No                | No                                   | No              |  |  |  |  |  |

| operation            | operation         | operation                            | operation       |  |  |  |  |  |

| If skip and followed |                   |                                      |                 |  |  |  |  |  |

| Q1                   | Q2                | Q3                                   | Q4              |  |  |  |  |  |

| No                   | No                | No                                   | No              |  |  |  |  |  |

| operation<br>No      | operation<br>No   | operation<br>No                      | operation<br>No |  |  |  |  |  |

| operation            | operation         | operation                            | operation       |  |  |  |  |  |

|                      |                   |                                      |                 |  |  |  |  |  |

| Example:             | HERE              | HERE CPFSGT REG, 0                   |                 |  |  |  |  |  |

|                      | NGREATER          |                                      |                 |  |  |  |  |  |

|                      | GREATER           | :                                    |                 |  |  |  |  |  |

| Before Instruc       |                   |                                      |                 |  |  |  |  |  |

| PC                   |                   | dress (HERE)                         | )               |  |  |  |  |  |

| W                    | = ?               |                                      |                 |  |  |  |  |  |

| After Instruction    |                   |                                      |                 |  |  |  |  |  |

| If REG               | > W;              |                                      |                 |  |  |  |  |  |

| PC<br>If REG         | = Ad              | dress (GREAT                         | LEK)            |  |  |  |  |  |

| CPFSLT                                                                    | Compare                                                                                                                            | f with W, s                                                                                                                                                                                                                                                                                                                                                                                          |                 |  |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Syntax:                                                                   | CPFSLT f                                                                                                                           | {,a}                                                                                                                                                                                                                                                                                                                                                                                                 |                 |  |  |  |  |

| Operands:                                                                 | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                      |                 |  |  |  |  |

| Operation:                                                                | (f) – (W),<br>skip if (f) < (<br>(unsigned c                                                                                       | · ·                                                                                                                                                                                                                                                                                                                                                                                                  |                 |  |  |  |  |

| Status Affected:                                                          | None                                                                                                                               | . ,                                                                                                                                                                                                                                                                                                                                                                                                  |                 |  |  |  |  |

| Encoding:                                                                 | 0110                                                                                                                               | 000a ff                                                                                                                                                                                                                                                                                                                                                                                              | ff ffff         |  |  |  |  |

| Description:                                                              | location 'f' t<br>performing<br>If the conten<br>contents of<br>instruction i<br>executed in<br>2-cycle instr<br>If 'a' is '0', tl | Compares the contents of data memory<br>location 'f' to the contents of W by<br>performing an unsigned subtraction.<br>If the contents of 'f' are less than the<br>contents of W, then the fetched<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction.<br>If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select the |                 |  |  |  |  |

| Words:                                                                    | 1                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                      |                 |  |  |  |  |

| Cycles:                                                                   |                                                                                                                                    | ycles if skip a<br>a 2-word inst                                                                                                                                                                                                                                                                                                                                                                     |                 |  |  |  |  |

| Q Cycle Activity:                                                         |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                      |                 |  |  |  |  |

| Q1                                                                        | Q2                                                                                                                                 | Q3                                                                                                                                                                                                                                                                                                                                                                                                   | Q4              |  |  |  |  |

| Decode                                                                    | Read<br>register 'f'                                                                                                               | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                      | No<br>operation |  |  |  |  |

| If skip:                                                                  | register i                                                                                                                         | Dala                                                                                                                                                                                                                                                                                                                                                                                                 | operation       |  |  |  |  |

| Q1                                                                        | Q2                                                                                                                                 | Q3                                                                                                                                                                                                                                                                                                                                                                                                   | Q4              |  |  |  |  |

| No                                                                        | No                                                                                                                                 | No                                                                                                                                                                                                                                                                                                                                                                                                   | No              |  |  |  |  |

| operation                                                                 | operation                                                                                                                          | operation                                                                                                                                                                                                                                                                                                                                                                                            | operation       |  |  |  |  |

| If skip and followed                                                      | d by 2-word in                                                                                                                     | struction:                                                                                                                                                                                                                                                                                                                                                                                           |                 |  |  |  |  |

| Q1                                                                        | Q2                                                                                                                                 | Q3                                                                                                                                                                                                                                                                                                                                                                                                   | Q4              |  |  |  |  |

| No                                                                        | No                                                                                                                                 | No                                                                                                                                                                                                                                                                                                                                                                                                   | No              |  |  |  |  |

| operation                                                                 | operation                                                                                                                          | operation                                                                                                                                                                                                                                                                                                                                                                                            | operation       |  |  |  |  |

| No                                                                        | No                                                                                                                                 | No                                                                                                                                                                                                                                                                                                                                                                                                   | No              |  |  |  |  |

|                                                                           | operation                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                      |                 |  |  |  |  |

| operation                                                                 | HERE (<br>NLESS                                                                                                                    | operation                                                                                                                                                                                                                                                                                                                                                                                            | operation       |  |  |  |  |

|                                                                           |                                                                                                                                    | CPFSLT REG                                                                                                                                                                                                                                                                                                                                                                                           | • •             |  |  |  |  |

|                                                                           | NLESS<br>LESS                                                                                                                      | CPFSLT REG                                                                                                                                                                                                                                                                                                                                                                                           | • •             |  |  |  |  |

| Example:                                                                  | NLESS ==<br>LESS ==<br>tion                                                                                                        | CPFSLT REG                                                                                                                                                                                                                                                                                                                                                                                           | , 1             |  |  |  |  |

| Example:<br>Before Instruc<br>PC                                          | NLESS =<br>LESS =<br>tion<br>= Ad<br>= ?                                                                                           | CPFSLT REG                                                                                                                                                                                                                                                                                                                                                                                           | , 1             |  |  |  |  |

| Example:<br>Before Instruc<br>PC<br>W<br>After Instructic<br>If REG       | NLESS :<br>LESS :<br>tion = Ad<br>= ?<br>on < W;                                                                                   | CPFSLT REG                                                                                                                                                                                                                                                                                                                                                                                           | , 1<br>E)       |  |  |  |  |

| Example:<br>Before Instruc<br>PC<br>W<br>After Instructic<br>If REG<br>PC | NLESS :<br>LESS :<br>tion = Ad<br>= ?<br>on < W;<br>= Ad                                                                           | CPFSLT REG                                                                                                                                                                                                                                                                                                                                                                                           | , 1<br>E)       |  |  |  |  |

| Example:<br>Before Instruc<br>PC<br>W<br>After Instructic<br>If REG       | NLESS :<br>LESS :<br>tion = Ad<br>= ?<br>on < W;<br>= Ad<br>≥ W;                                                                   | CPFSLT REG                                                                                                                                                                                                                                                                                                                                                                                           | , 1<br>E)<br>S) |  |  |  |  |

If REG

PC

≤ W;

= Address (NGREATER)

CNT Z C DC

After Instruction

CNT Z C DC

FFh 0 ? ?

00h

= = = =

= = = 1 1 1

| GOTO                                                                                                                                         | Uncondit                  | ional Bran      | ch                      |                                        | INCF                                                                                                                                                                                                                            | Incremen                                                                                                     | tf                                |                      |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------|-------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------|--|--|

| Syntax:                                                                                                                                      | GOTO k                    |                 |                         |                                        | Syntax:                                                                                                                                                                                                                         | INCF f {,d {,a}}                                                                                             |                                   |                      |  |  |

| Operands:                                                                                                                                    | $0 \le k \le 104$         | 8575            |                         |                                        | Operands:                                                                                                                                                                                                                       | $0 \leq f \leq 255$                                                                                          |                                   |                      |  |  |

| Operation:                                                                                                                                   | $k \rightarrow PC < 20$   | ):1>            |                         |                                        |                                                                                                                                                                                                                                 | d ∈ [0,1]<br>a ∈ [0,1]                                                                                       |                                   |                      |  |  |

| Status Affected:                                                                                                                             | None                      |                 |                         |                                        | Operation:                                                                                                                                                                                                                      | $a \in [0, 1]$<br>(f) + 1 $\rightarrow$ definition                                                           | • • •                             |                      |  |  |

| Encoding:                                                                                                                                    |                           |                 |                         |                                        | Status Affected:                                                                                                                                                                                                                | $(1) \neq 1 \rightarrow 0$<br>C, DC, N,                                                                      |                                   |                      |  |  |

| 1st word (k<7:0>)<br>2nd word(k<19:8>)                                                                                                       | 1110<br>) 1111            |                 | <sub>7</sub> kkk<br>kkk | kkkk <sub>0</sub><br>kkkk <sub>8</sub> | Encoding:                                                                                                                                                                                                                       | 0010                                                                                                         | 10da ff                           | ff ffff              |  |  |

| Description:                                                                                                                                 |                           | vs an uncon     |                         | Ũ                                      | Description:                                                                                                                                                                                                                    |                                                                                                              | ts of register "                  |                      |  |  |

| anywhere within entire<br>2-Mbyte memory range. The 20-bit<br>value 'k' is loaded into PC<20:1>.<br>GOTO is always a 2-cycle<br>instruction. |                           |                 |                         |                                        | incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the |                                                                                                              |                                   |                      |  |  |

| Words:                                                                                                                                       | 2                         |                 |                         |                                        |                                                                                                                                                                                                                                 | GPR bank.                                                                                                    |                                   | ! : <b>!</b>         |  |  |

| Cycles:                                                                                                                                      | 2                         |                 |                         |                                        |                                                                                                                                                                                                                                 |                                                                                                              | nd the extend<br>led, this instru |                      |  |  |

| Q Cycle Activity:                                                                                                                            |                           |                 |                         |                                        |                                                                                                                                                                                                                                 | in Indexed                                                                                                   | Literal Offset A                  | Addressing           |  |  |

| Q1                                                                                                                                           | Q2                        | Q3              |                         | Q4                                     |                                                                                                                                                                                                                                 |                                                                                                              | never f ≤ 95 (5                   |                      |  |  |

| Decode                                                                                                                                       | Read literal<br>'k'<7:0>, | No<br>operation | 'k'                     | ad literal<br><19:8>,<br>ite to PC     |                                                                                                                                                                                                                                 | Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Index<br>Literal Offset Mode" for details. |                                   |                      |  |  |

| No                                                                                                                                           | No                        | No              |                         | No                                     | Words:                                                                                                                                                                                                                          | 1                                                                                                            |                                   |                      |  |  |

| operation                                                                                                                                    | operation                 | operation       | op                      | peration                               | Cycles:                                                                                                                                                                                                                         | 1                                                                                                            |                                   |                      |  |  |

|                                                                                                                                              |                           |                 |                         |                                        | Q Cycle Activity:                                                                                                                                                                                                               |                                                                                                              |                                   |                      |  |  |

| Example:                                                                                                                                     | GOTO THE                  | RE              |                         |                                        | Q1                                                                                                                                                                                                                              | Q2                                                                                                           | Q3                                | Q4                   |  |  |

| After Instructi<br>PC =                                                                                                                      | on<br>Address (T          | HERE)           |                         |                                        | Decode                                                                                                                                                                                                                          | Read<br>register 'f'                                                                                         | Process<br>Data                   | Write to destination |  |  |

|                                                                                                                                              |                           |                 |                         |                                        | Example:                                                                                                                                                                                                                        | INCF                                                                                                         | CNT, 1, 0                         |                      |  |  |

|                                                                                                                                              |                           |                 |                         |                                        | Before Instruc                                                                                                                                                                                                                  | ction                                                                                                        |                                   |                      |  |  |

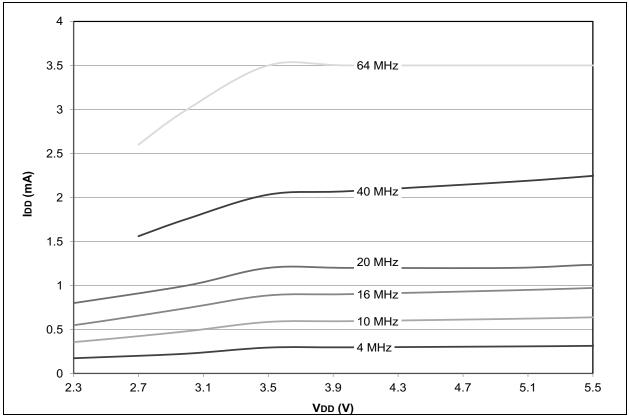

| PIC18LF      | 2X/4XK22               | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |       |                 |            | tated)                                                               |  |  |

|--------------|------------------------|----------------------------------------------------------------------------------------------------------------------|------|-------|-----------------|------------|----------------------------------------------------------------------|--|--|

| PIC18F2      | X/4XK22                | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |       |                 |            |                                                                      |  |  |

| Param<br>No. | Device Characteristics | Тур                                                                                                                  | Max  | Units |                 | Conditions |                                                                      |  |  |

| D055         |                        | 0.25                                                                                                                 | 0.40 | mA    | -40°C to +125°C | Vdd = 1.8V | Fosc = 1 MHz                                                         |  |  |

| D056         |                        | 0.35                                                                                                                 | 0.50 | mA    | -40°C to +125°C | VDD = 3.0V | ( <b>RC_IDLE</b> mode,<br>HFINTOSC source)                           |  |  |

| D057         |                        | 0.30                                                                                                                 | 0.45 | mA    | -40°C to +125°C | VDD = 2.3V | Fosc = 1 MHz                                                         |  |  |

| D058         |                        | 0.40                                                                                                                 | 0.50 | mA    | -40°C to +125°C | VDD = 3.0V | ( <b>RC_IDLE</b> mode,<br>HFINTOSC source)                           |  |  |

| D059         |                        | 0.45                                                                                                                 | 0.60 | mA    | -40°C to +125°C | VDD = 5.0V |                                                                      |  |  |