Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 30x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

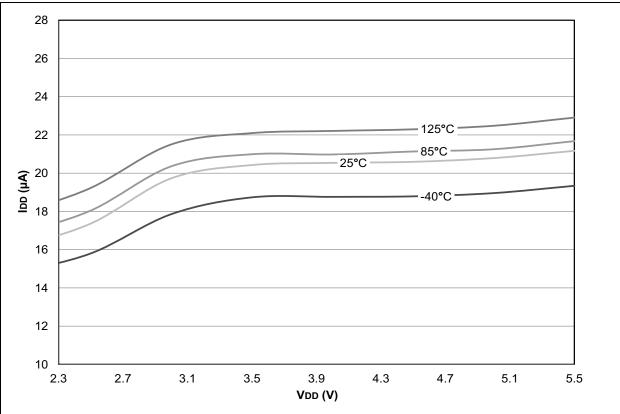

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

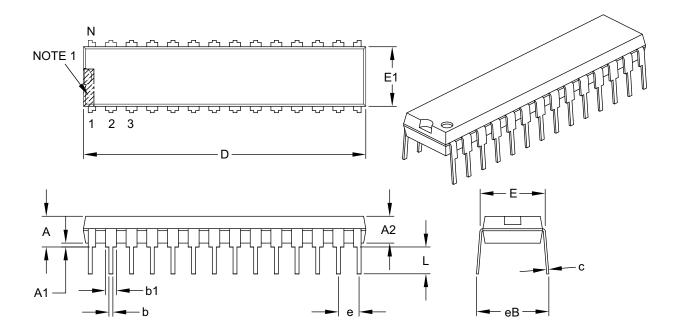

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k22-e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Nu        | ımber        |                              | <b>D</b> '  | Duffer         |                                                                                                                 |

|---------------|--------------|------------------------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------|

| PDIP,<br>SOIC | QFN,<br>UQFN | Pin Name                     | Pin<br>Type | Buffer<br>Type | Description                                                                                                     |

| 2             | 27           | RA0/C12IN0-/AN0              |             |                |                                                                                                                 |

|               |              | RA0                          | I/O         | TTL            | Digital I/O.                                                                                                    |

|               |              | C12IN0-                      | Т           | Analog         | Comparators C1 and C2 inverting input.                                                                          |

|               |              | ANO                          | I           | Analog         | Analog input 0.                                                                                                 |

| 3             | 28           | RA1/C12IN1-/AN1              |             |                |                                                                                                                 |

|               |              | RA1                          | I/O         | TTL            | Digital I/O.                                                                                                    |

|               |              | C12IN1-                      | I           | Analog         | Comparators C1 and C2 inverting input.                                                                          |

|               |              | AN1                          | Ι           | Analog         | Analog input 1.                                                                                                 |

| 4             | 1            | RA2/C2IN+/AN2/DACOUT/VREF-   |             |                |                                                                                                                 |

|               |              | RA2                          | I/O         | TTL            | Digital I/O.                                                                                                    |

|               |              | C2IN+                        | I           | Analog         | Comparator C2 non-inverting input.                                                                              |

|               |              | AN2                          | I           | Analog         | Analog input 2.                                                                                                 |

|               |              | DACOUT                       | 0           | Analog         | DAC Reference output.                                                                                           |

|               |              | VREF-                        | Ι           | Analog         | A/D reference voltage (low) input.                                                                              |

| 5             | 2            | RA3/C1IN+/AN3/VREF+          |             |                |                                                                                                                 |

|               |              | RA3                          | I/O         | TTL            | Digital I/O.                                                                                                    |

|               |              | C1IN+                        | I           | Analog         | Comparator C1 non-inverting input.                                                                              |

|               |              | AN3                          | I           | Analog         | Analog input 3.                                                                                                 |

|               |              | VREF+                        | Ι           | Analog         | A/D reference voltage (high) input.                                                                             |

| 6             | 3            | RA4/CCP5/C1OUT/SRQ/T0CKI     |             |                |                                                                                                                 |

|               |              | RA4                          | I/O         | ST             | Digital I/O.                                                                                                    |

|               |              | CCP5                         | I/O         | ST             | Capture 5 input/Compare 5 output/PWM 5 output.                                                                  |

|               |              | C1OUT                        | 0           | CMOS           | Comparator C1 output.                                                                                           |

|               |              | SRQ                          | 0           | TTL            | SR latch Q output.                                                                                              |

|               |              | ТОСКІ                        | Ι           | ST             | Timer0 external clock input.                                                                                    |

| 7             | 4            | RA5/C2OUT/SRNQ/SS1/HLVDIN/AN | 14          |                |                                                                                                                 |

|               |              | RA5                          | I/O         | TTL            | Digital I/O.                                                                                                    |

|               |              | C2OUT                        | 0           | CMOS           | Comparator C2 output.                                                                                           |

|               |              | SRNQ                         | 0           | TTL            | SR latch $\overline{Q}$ output.                                                                                 |

|               |              | SS1                          | Т           | TTL            | SPI slave select input (MSSP).                                                                                  |

|               |              | HLVDIN                       | I           | Analog         | High/Low-Voltage Detect input.                                                                                  |

|               |              | AN4                          | Ι           | Analog         | Analog input 4.                                                                                                 |

| 10            | 7            | RA6/CLKO/OSC2                |             |                |                                                                                                                 |

|               |              | RA6                          | I/O         | TTL            | Digital I/O.                                                                                                    |

|               |              | CLKO                         | 0           |                | In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate. |

|               |              | OSC2                         | 0           |                | Oscillator crystal output. Connects to crystal or resonato<br>in Crystal Oscillator mode.                       |

| TABLE 1-2: |                                        |

|------------|----------------------------------------|

| IABLE 1-2: | PIC18(L)F2XK22 PINOUT I/O DESCRIPTIONS |

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

### 5.4 Data Memory Organization

Note: The operation of some aspects of data memory are changed when the PIC18 extended instruction set is enabled. See Section 5.7 "Data Memory and the Extended Instruction Set" for more information.

The data memory in PIC18 devices is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The memory space is divided into as many as 16 banks that contain 256 bytes each. Figures 5-5 through 5-7 show the data memory organization for the PIC18(L)F2X/4XK22 devices.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this subsection.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to SFRs and the lower portion of GPR Bank 0 without using the Bank Select Register (BSR). **Section 5.4.2 "Access Bank"** provides a detailed description of the Access RAM.

#### 5.4.1 BANK SELECT REGISTER (BSR)

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 16 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an 8-bit low-order address and a 4-bit Bank Pointer.

Most instructions in the PIC18 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the 4 Most Significant bits of a location's address; the instruction itself includes the 8 Least Significant bits. Only the four lower bits of the BSR are implemented (BSR<3:0>). The upper four bits are unused; they will always read '0' and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory; the eight bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is shown in Figures 5-5 through 5-7.

Since up to 16 registers may share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an 8-bit address of F9h while the BSR is 0Fh will end up resetting the program counter.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory maps in Figures 5-5 through 5-7 indicate which banks are implemented.

In the core PIC18 instruction set, only the MOVFF instruction fully specifies the 12-bit address of the source and target registers. This instruction ignores the BSR completely when it executes. All other instructions include only the low-order address as an operand and must use either the BSR or the Access Bank to locate their target registers.

|                   | MOVLW   | D'64′            | ; number of bytes in erase block      |

|-------------------|---------|------------------|---------------------------------------|

|                   | MOVWF   | COUNTER          |                                       |

|                   | MOVLW   | BUFFER_ADDR_HIGH | ; point to buffer                     |

|                   | MOVWF   | FSR0H            |                                       |

|                   | MOVLW   | BUFFER_ADDR_LOW  |                                       |

|                   | MOVWF   | FSROL            |                                       |

|                   | MOVLW   | CODE_ADDR_UPPER  | ; Load TBLPTR with the base           |

|                   | MOVWF   | TBLPTRU          | ; address of the memory block         |

|                   | MOVLW   | CODE_ADDR_HIGH   |                                       |

|                   | MOVWF   | TBLPTRH          |                                       |

|                   | MOVLW   | CODE_ADDR_LOW    |                                       |

|                   | MOVWF   | TBLPTRL          |                                       |

| EAD_BLOCK         |         |                  |                                       |

|                   | TBLRD*+ |                  | ; read into TABLAT, and inc           |

|                   | MOVF    | TABLAT, W        | ; get data                            |

|                   | MOVWF   | POSTINC0         | ; store data                          |

|                   | DECFSZ  | COUNTER          | ; done?                               |

|                   | BRA     | READ_BLOCK       | ; repeat                              |

| ODIFY_WORD        |         |                  |                                       |

|                   | MOVLW   | BUFFER_ADDR_HIGH | ; point to buffer                     |

|                   | MOVWF   | FSROH            |                                       |

|                   | MOVLW   | BUFFER_ADDR_LOW  |                                       |

|                   | MOVWF   | FSROL            |                                       |

|                   | MOVLW   | NEW_DATA_LOW     | ; update buffer word                  |

|                   | MOVWF   | POSTINC0         |                                       |

|                   | MOVLW   | NEW_DATA_HIGH    |                                       |

|                   | MOVWF   | INDF0            |                                       |

| ERASE_BLOCK       |         |                  |                                       |

|                   | MOVLW   | CODE_ADDR_UPPER  | ; load TBLPTR with the base           |

|                   | MOVWF   | TBLPTRU          | ; address of the memory block         |

|                   | MOVLW   | CODE_ADDR_HIGH   |                                       |

|                   | MOVWF   | TBLPTRH          |                                       |

|                   | MOVLW   | CODE_ADDR_LOW    |                                       |

|                   | MOVWF   | TBLPTRL          |                                       |

|                   | BSF     | EECON1, EEPGD    | ; point to Flash program memory       |

|                   | BCF     | EECON1, CFGS     | ; access Flash program memory         |

|                   | BSF     | EECON1, WREN     | ; enable write to memory              |

|                   | BSF     | EECON1, FREE     | ; enable Erase operation              |

|                   | BCF     | INTCON, GIE      | ; disable interrupts                  |

|                   | MOVLW   | 55h              |                                       |

| Required          | MOVWF   | EECON2           | ; write 55h                           |

| Sequence          | MOVLW   | 0AAh             |                                       |

|                   | MOVWF   | EECON2           | ; write OAAh                          |

|                   | BSF     | EECON1, WR       | ; start erase (CPU stall)             |

|                   | BSF     | INTCON, GIE      | ; re-enable interrupts                |

|                   | TBLRD*- |                  | ; dummy read decrement                |

|                   | MOVLW   | BUFFER_ADDR_HIGH | ; point to buffer                     |

|                   | MOVWF   | FSR0H            |                                       |

|                   | MOVLW   | BUFFER_ADDR_LOW  |                                       |

|                   | MOVWF   | FSROL            |                                       |

| WRITE_BUFFER_BACK |         |                  |                                       |

|                   | MOVLW   | BlockSize        | ; number of bytes in holding register |

|                   | MOVWF   | COUNTER          |                                       |

|                   | MOVLW   | D'64'/BlockSize  | ; number of write blocks in 64 bytes  |

|                   | MOVWF   | COUNTER2         |                                       |

| WRITE_BYTE_TO_HRE | GS      |                  |                                       |

|                   | MOVF    | POSTINCO, W      | ; get low byte of buffer data         |

|                   | MOVWF   | TABLAT           | ; present data to table latch         |

|                   | TBLWT+* |                  | ; write data, perform a short write   |

|                   |         |                  | ; to internal TBLWT holding register. |

#### TABLE 10-1: PORTA I/O SUMMARY

| Pin Name                       | Function                 | TRIS<br>Setting | ANSEL<br>Setting | Pin<br>Type | Buffer<br>Type       | Description                                                                                                          |

|--------------------------------|--------------------------|-----------------|------------------|-------------|----------------------|----------------------------------------------------------------------------------------------------------------------|

| RA0/C12IN0-/AN0                | RA0                      | 0               | 0                | 0           | DIG                  | LATA<0> data output; not affected by analog input.                                                                   |

|                                |                          | 1               | 0                | Ι           | TTL                  | PORTA<0> data input; disabled when analog input enabled.                                                             |

|                                | C12IN0-                  | 1               | 1                | Ι           | AN                   | Comparators C1 and C2 inverting input.                                                                               |

|                                | AN0                      | 1               | 1                | I           | AN                   | Analog input 0.                                                                                                      |

| RA1/C12IN1-/AN1                | RA1                      | 0               | 0                | 0           | DIG                  | LATA<1> data output; not affected by analog input.                                                                   |

|                                |                          | 1               | 0                | I           | TTL                  | PORTA<1> data input; disabled when analog input enabled.                                                             |

|                                | C12IN1-                  | 1               | 1                | I           | AN                   | Comparators C1 and C2 inverting input.                                                                               |

|                                | AN1                      | 1               | 1                | I           | AN                   | Analog input 1.                                                                                                      |

| RA2/C2IN+/AN2/<br>DACOUT/VREF- | RA2                      | 0               | 0                | 0           | DIG                  | LATA<2> data output; not affected by analog input; disabled when DACOUT enabled.                                     |

|                                |                          | 1               | 0                | Ι           | TTL                  | PORTA<2> data input; disabled when analog input enabled;<br>disabled when DACOUT enabled.                            |

|                                | C2IN+                    | 1               | 1                | Ι           | AN                   | Comparator C2 non-inverting input.                                                                                   |

|                                | AN2                      | 1               | 1                | Ι           | AN                   | Analog output 2.                                                                                                     |

|                                | DACOUT                   | x               | 1                | 0           | AN                   | DAC Reference output.                                                                                                |

|                                | VREF-                    | 1               | 1                | Ι           | AN                   | A/D reference voltage (low) input.                                                                                   |

| RA3/C1IN+/AN3/                 | RA3                      | 0               |                  | 0           | DIG                  | LATA<3> data output; not affected by analog input.                                                                   |

| VREF+                          |                          | 1               | 0                | I           | TTL                  | PORTA<3> data input; disabled when analog input enabled.                                                             |

|                                | C1IN+                    | 1               | 1                | I           | AN                   | Comparator C1 non-inverting input.                                                                                   |

|                                | AN3                      | 1               | 1                | I           | AN                   | Analog input 3.                                                                                                      |

|                                | VREF+                    | 1               | 1                | Ι           | AN                   | A/D reference voltage (high) input.                                                                                  |

| RA4/CCP5/C1OUT/                | A4/CCP5/C1OUT/ RA4 0 — O |                 | 0                | DIG         | LATA<4> data output. |                                                                                                                      |

| SRQ/T0CKI                      |                          | 1               | _                | Ι           | ST                   | PORTA<4> data input; default configuration on POR.                                                                   |

|                                | CCP5                     | 0               | _                | 0           | DIG                  | CCP5 Compare output/PWM output, takes priority over RA4 output                                                       |

|                                |                          | 1               | —                | I           | ST                   | Capture 5 input/Compare 5 output/ PWM 5 output.                                                                      |

|                                | C1OUT                    | 0               | _                | 0           | DIG                  | Comparator C1 output.                                                                                                |

|                                | SRQ                      | 0               | _                | 0           | DIG                  | SR latch Q output; take priority over CCP 5 output.                                                                  |

|                                | TOCKI                    | 1               | _                | Ι           | ST                   | Timer0 external clock input.                                                                                         |

| RA5/C2OUT/SRNQ/                | RA5                      | 0               | 0                | 0           | DIG                  | LATA<5> data output; not affected by analog input.                                                                   |

| SS1/<br>HLVDIN/AN4             |                          | 1               | 0                | I           | TTL                  | PORTA<5> data input; disabled when analog input enabled.                                                             |

| HLVDIN/AN4                     | C2OUT                    | 0               | 0                | 0           | DIG                  | Comparator C2 output.                                                                                                |

|                                | SRNQ                     | 0               | 0                | 0           | DIG                  | SR latch $\overline{Q}$ output.                                                                                      |

|                                | SS1                      | 1               | 0                | I           | TTL                  | SPI slave select input (MSSP1).                                                                                      |

|                                | HLVDIN                   | 1               | 1                | I           | AN                   | High/Low-Voltage Detect input.                                                                                       |

|                                | AN4                      | 1               | 1                | 1           | AN                   | A/D input 4.                                                                                                         |

| RA6/CLKO/OSC2                  | RA6                      | 0               | _                | 0           | DIG                  | LATA<6> data output; enabled in INTOSC modes when CLKO is no<br>enabled.                                             |

|                                |                          | 1               | —                | Ι           | TTL                  | PORTA<6> data input; enabled in INTOSC modes when CLKO is not enabled.                                               |

|                                | CLKO                     | x               | —                | 0           | DIG                  | In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the fre-<br>quency of OSC1 and denotes the instruction cycle rate. |

|                                | OSC2                     | x               | _                | 0           | XTAL                 | Oscillator crystal output; connects to crystal or resonator in Crystal Oscillator mode.                              |

| RA7/CLKI/OSC1                  | RA7                      | 0               | _                | 0           | DIG                  | LATA<7> data output; disabled in external oscillator modes.                                                          |

|                                |                          | 1               | —                | Ι           | TTL                  | PORTA<7> data input; disabled in external oscillator modes.                                                          |

|                                | CLKI                     | x               | —                | I           | AN                   | External clock source input; always associated with pin function OSC1.                                               |

|                                | OSC1                     | x               |                  | Ι           | XTAL                 | Oscillator crystal input or external clock source input ST buffer wher<br>configured in RC mode; CMOS otherwise.     |

Legend: AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C.

| Name     | Bit 7    | Bit 6     | Bit 5   | Bit 4       | Bit 3       | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|----------|----------|-----------|---------|-------------|-------------|--------|--------|---------|---------------------|

| CCPTMRS0 | C3TSE    | L<1:0>    | _       | C2TSE       | L<1:0>      | —      | C1TS   | EL<1:0> | 201                 |

| CCPTMRS1 | _        | —         | —       | _           | C5TSE       | L<1:0> | C4TS   | EL<1:0> | 201                 |

| INTCON   | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE      | RBIE        | TMR0IF | INT0IF | RBIF    | 109                 |

| IPR1     | _        | ADIP      | RC1IP   | TX1IP       | SSP1IP      | CCP1IP | TMR2IP | TMR1IP  | 121                 |

| IPR5     | _        | _         | _       | _           | _           | TMR6IP | TMR5IP | TMR4IP  | 124                 |

| PIE1     | _        | ADIE      | RC1IE   | TX1IE       | SSP1IE      | CCP1IE | TMR2IE | TMR1IE  | 117                 |

| PIE5     | _        | _         |         | _           | _           | TMR6IE | TMR5IE | TMR4IE  | 120                 |

| PIR1     | _        | ADIF      | RC1IF   | TX1IF       | SSP1IF      | CCP1IF | TMR2IF | TMR1IF  | 112                 |

| PIR5     | _        | _         |         | _           | _           | TMR6IF | TMR5IF | TMR4IF  | 116                 |

| PMD0     | UART2MD  | UART1MD   | TMR6MD  | TMR5MD      | TMR4MD      | TMR3MD | TMR2MD | TMR1MD  | 52                  |

| PR2      |          |           | -       | Timer2 Peri | od Register |        |        |         | —                   |

| PR4      |          |           | -       | Timer4 Peri | od Register |        |        |         | —                   |

| PR6      |          |           | -       | Timer6 Peri | od Register |        |        |         | _                   |

| T2CON    | _        |           | T2OUTPS | S<3:0>      |             | TMR2ON | T2CK   | PS<1:0> | 166                 |

| T4CON    |          |           | T4OUTPS | S<3:0>      |             | TMR4ON | T4CK   | PS<1:0> | 166                 |

| T6CON    |          |           | T6OUTPS | S<3:0>      |             | TMR6ON | T6CK   | PS<1:0> | 166                 |

| TMR2     |          |           |         | Timer2      | Register    |        |        |         | _                   |

| TMR4     |          |           |         | Timer4 I    | Register    |        |        |         | —                   |

| TMR6     |          |           |         | Timer6 I    | Register    |        |        |         | —                   |

#### TABLE 13-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2/4/6

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by Timer2/4/6.

#### 14.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PRx is 255. The resolution is a function of the PRx register value as shown by Equation 14-4.

#### EQUATION 14-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PRx+1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

### TABLE 14-7: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 32 MHz)

| PWM Frequency             | 1.95 kHz | 7.81 kHz | 31.25 kHz | 125 kHz | 250 kHz | 333.3 kHz |

|---------------------------|----------|----------|-----------|---------|---------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1       | 1       | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F    | 0x1F    | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8       | 7       | 6.6       |

#### TABLE 14-8: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 14-9: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PRx Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 14.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMRx register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMRx will continue from its previous state.

#### 14.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 2.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 14.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 14.4.8 SETUP FOR ECCP PWM OPERATION USING ECCP1 AND TIMER2

The following steps should be taken when configuring the ECCP1 module for PWM operation using Timer2:

- 1. Configure the PWM pins to be used (P1A, P1B, P1C, and P1D):

- Configure PWM outputs to be used as inputs by setting the corresponding TRIS bits. This prevents spurious outputs during setup.

- Set the PSTR1CON bits for each PWM output to be used.

- Select Timer2 as the period timer by configuring CCPTMR0 register bits C1TSEL<1:0> = '00'.

- 3. Set the PWM period by loading the PR2 register.

- 4. Configure auto-shutdown as OFF or select the source with the CCP1AS<2:0> bits of the ECCP1AS register.

- 5. Configure the auto-shutdown sources as needed:

- Configure each comparator used.

- Configure the comparator inputs as analog.

- Configure the FLT0 input pin and clear ANSB0.

- 6. Force a shutdown condition (OFF included):

- Configure safe starting output levels by setting the default shutdown drive states with the PSS1AC<1:0> and PSS1BD<1:0> bits of the ECCP1AS register.

- Clear the P1RSEN bit of the PWM1CON register.

- Set the CCP1AS bit of the ECCP1AS register.

- Configure the ECCP1 module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M<1:0> bits.

- Select the polarities of the PWM output signals with the CCP1M<3:0> bits.

- 8. Set the 10-bit PWM duty cycle:

- Load the eight MSbs into the CCPR1L register.

- Load the two LSbs into the DC<1:0> bits of the CCP1CON register.

- For Half-Bridge Output mode, set the deadband delay by loading P1DC<6:0> bits of the PWM1CON register with the appropriate value.

- 10. Configure and start TMR2:

- Set the TMR2 prescale value by loading the T2CKPS bits of the T2CON register.

- Start Timer2 by setting the TMR2ON bit.

- 11. Enable the ECCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- 12. Start the PWM:

- If shutdown auto-restart is used, then set the P1RSEN bit of the PWM1CON register.

- If shutdown auto-restart is not used, then clear the CCP1ASE bit of the ECCP1AS register.

## 15.3 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit Bus (I<sup>2</sup>C) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCLx)

- Serial Data (SDAx)

Figure 15-2 shows the block diagram of the MSSPx module when operating in  $I^2C$  mode.

Both the SCLx and SDAx connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

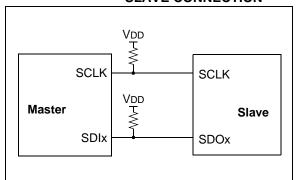

Figure 15-11 shows a typical connection between two processors configured as master and slave devices.

The I<sup>2</sup>C bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode

(master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDAx line while the SCLx line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

### FIGURE 15-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDAx line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of data bits is always performed while the SCLx line is held low. Transitions that occur while the SCLx line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an ACK bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDAx line while the SCLx line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

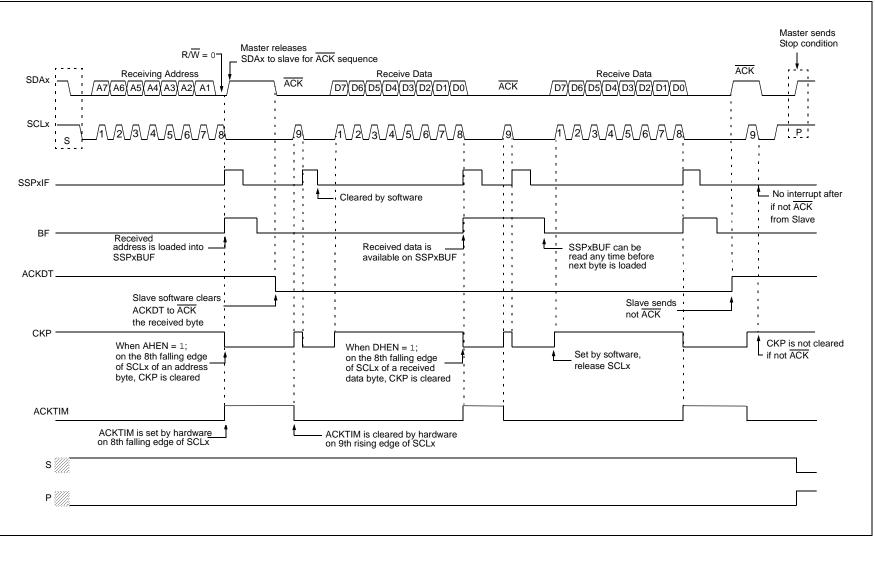

### FIGURE 15-17: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 1, AHEN = 1, DHEN = 1)

PIC18(L)F2X/4XK22

### 15.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDAx pin after the falling edge of SCLx is asserted. SCLx is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCLx is released high. When the SCLx pin is released high, it is held that way for TBRG. The data on the SDAx pin must remain stable for that duration and some hold time after the next falling edge of SCLx. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDAx. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of  $\overline{ACK}$  is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCLx low and SDAx unchanged (Figure 15-28).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCLx until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDAx pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDAx pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCLx low and allowing SDAx to float.

#### 15.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all 8 bits are shifted out.

#### 15.6.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

#### 15.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

15.6.6.4 Typical Transmit Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSPx module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- 6. Address is shifted out the SDAx pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 7. The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDAx pin until all eight bits are transmitted.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPx-CON2 register. Interrupt is generated once the Stop/Restart condition is complete.

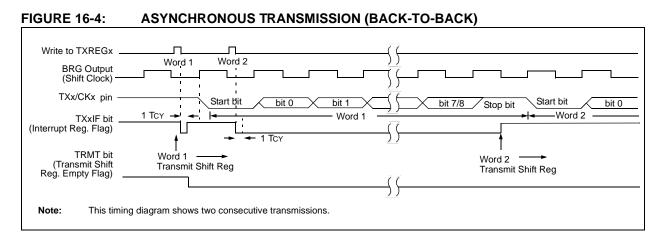

#### TABLE 16-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name     | Bit 7    | Bit 6     | Bit 5   | Bit 4       | Bit 3        | Bit 2     | Bit 1   | Bit 0   | Reset<br>Values<br>on<br>Page |

|----------|----------|-----------|---------|-------------|--------------|-----------|---------|---------|-------------------------------|

| BAUDCON1 | ABDOVF   | RCIDL     | DTRXP   | CKTXP       | BRG16        | —         | WUE     | ABDEN   | 271                           |

| BAUDCON2 | ABDOVF   | RCIDL     | DTRXP   | CKTXP       | BRG16        | —         | WUE     | ABDEN   | 271                           |

| INTCON   | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE      | RBIE         | TMR0IF    | INT0IF  | RBIF    | 109                           |

| IPR1     | —        | ADIP      | RC1IP   | TX1IP       | SSP1IP       | CCP1IP    | TMR2IP  | TMR1IP  | 121                           |

| IPR3     | SSP2IP   | BCL2IP    | RC2IP   | TX2IP       | CTMUIP       | TMR5GIP   | TMR3GIP | TMR1GIP | 123                           |

| PIE1     | —        | ADIE      | RC1IE   | TX1IE       | SSP1IE       | CCP1IE    | TMR2IE  | TMR1IE  | 117                           |

| PIE3     | SSP2IE   | BCL2IE    | RC2IE   | TX2IE       | CTMUIE       | TMR5GIE   | TMR3GIE | TMR1GIE | 119                           |

| PIR1     | _        | ADIF      | RC1IF   | TX1IF       | SSP1IF       | CCP1IF    | TMR2IF  | TMR1IF  | 112                           |

| PIR3     | SSP2IF   | BCL2IF    | RC2IF   | TX2IF       | CTMUIF       | TMR5GIF   | TMR3GIF | TMR1GIF | 114                           |

| PMD0     | UART2MD  | UART1MD   | TMR6MD  | TMR5MD      | TMR4MD       | TMR3MD    | TMR2MD  | TMR1MD  | 52                            |

| RCSTA1   | SPEN     | RX9       | SREN    | CREN        | ADDEN        | FERR      | OERR    | RX9D    | 270                           |

| RCSTA2   | SPEN     | RX9       | SREN    | CREN        | ADDEN        | FERR      | OERR    | RX9D    | 270                           |

| SPBRG1   |          |           | EUSART  | 1 Baud Rate | Generator,   | _ow Byte  |         |         | —                             |

| SPBRGH1  |          |           | EUSART  | Baud Rate   | Generator, I | ligh Byte |         |         | —                             |

| SPBRG2   |          |           | EUSART  | 2 Baud Rate | Generator,   | _ow Byte  |         |         | —                             |

| SPBRGH2  |          |           | EUSART2 | 2 Baud Rate | Generator, I | ligh Byte |         |         | —                             |

| TXREG1   |          |           | EL      | JSART1 Tra  | nsmit Regist | er        |         |         | —                             |

| TXSTA1   | CSRC     | TX9       | TXEN    | SYNC        | SENDB        | BRGH      | TRMT    | TX9D    | 269                           |

| TXREG2   |          |           | EL      | JSART2 Tra  | nsmit Regist | er        |         |         | —                             |

| TXSTA2   | CSRC     | TX9       | TXEN    | SYNC        | SENDB        | BRGH      | TRMT    | TX9D    | 269                           |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for asynchronous transmission.

| Name                  | Bit 7    | Bit 6     | Bit 5   | Bit 4      | Bit 3         | Bit 2     | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------------|----------|-----------|---------|------------|---------------|-----------|---------|---------|---------------------|

| BAUDCON1              | ABDOVF   | RCIDL     | DTRXP   | CKTXP      | BRG16         | —         | WUE     | ABDEN   | 271                 |

| BAUDCON2              | ABDOVF   | RCIDL     | DTRXP   | CKTXP      | BRG16         | _         | WUE     | ABDEN   | 271                 |

| INTCON                | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE     | RBIE          | TMR0IF    | INT0IF  | RBIF    | 109                 |

| IPR1                  | _        | ADIP      | RC1IP   | TX1IP      | SSP1IP        | CCP1IP    | TMR2IP  | TMR1IP  | 121                 |

| IPR3                  | SSP2IP   | BCL2IP    | RC2IP   | TX2IP      | CTMUIP        | TMR5GIP   | TMR3GIP | TMR1GIP | 123                 |

| PIE1                  | _        | ADIE      | RC1IE   | TX1IE      | SSP1IE        | CCP1IE    | TMR2IE  | TMR1IE  | 117                 |

| PIE3                  | SSP2IE   | BCL2IE    | RC2IE   | TX2IE      | CTMUIE        | TMR5GIE   | TMR3GIE | TMR1GIE | 119                 |

| PIR1                  | _        | ADIF      | RC1IF   | TX1IF      | SSP1IF        | CCP1IF    | TMR2IF  | TMR1IF  | 112                 |

| PIR3                  | SSP2IF   | BCL2IF    | RC2IF   | TX2IF      | CTMUIF        | TMR5GIF   | TMR3GIF | TMR1GIF | 114                 |

| PMD0                  | UART2MD  | UART1MD   | TMR6MD  | TMR5MD     | TMR4MD        | TMR3MD    | TMR2MD  | TMR1MD  | 52                  |

| RCSTA1                | SPEN     | RX9       | SREN    | CREN       | ADDEN         | FERR      | OERR    | RX9D    | 270                 |

| RCSTA2                | SPEN     | RX9       | SREN    | CREN       | ADDEN         | FERR      | OERR    | RX9D    | 270                 |

| SPBRG1                |          |           | EUSART1 | Baud Rate  | Generator, L  | ow Byte   |         |         | _                   |

| SPBRGH1               |          |           | EUSART1 | Baud Rate  | Generator, H  | ligh Byte |         |         | _                   |

| SPBRG2                |          |           | EUSART2 | Baud Rate  | Generator, L  | ow Byte   |         |         | _                   |

| SPBRGH2               |          |           | EUSART2 | Baud Rate  | Generator, H  | ligh Byte |         |         | _                   |

| TRISB <sup>(2)</sup>  | TRISB7   | TRISB6    | TRISB5  | TRISB4     | TRISB3        | TRISB2    | TRISB1  | TRISB0  | 151                 |

| TRISC                 | TRISC7   | TRISC6    | TRISC5  | TRISC4     | TRISC3        | TRISC2    | TRISC1  | TRISC0  | 151                 |

| TRISD <sup>(1)</sup>  | TRISD7   | TRISD6    | TRISD5  | TRISD4     | TRISD3        | TRISD2    | TRISD1  | TRISD0  | 151                 |

| ANSELC                | ANSC7    | ANSC6     | ANSC5   | ANSC4      | ANSC3         | ANSC2     | _       | —       | 150                 |

| ANSELD <sup>(1)</sup> | ANSD7    | ANSD6     | ANSD5   | ANSD4      | ANSD3         | ANSD2     | ANSD1   | ANSD0   | 150                 |

| TXREG1                |          | -         | EU      | SART1 Trar | smit Registe  | er        |         |         | —                   |

| TXSTA1                | CSRC     | TX9       | TXEN    | SYNC       | SENDB         | BRGH      | TRMT    | TX9D    | 269                 |

| TXREG2                |          | -         | EU      | SART2 Trar | ismit Registe | er        | -       |         | —                   |

| TXSTA2                | CSRC     | TX9       | TXEN    | SYNC       | SENDB         | BRGH      | TRMT    | TX9D    | 269                 |

### TABLE 16-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for synchronous master transmission.

Note 1: PIC18(L)F4XK22 devices.

2: PIC18(L)F2XK22 devices.

| Address | Name                  | Bit 7 | Bit 6    | Bit 5               | Bit 4  | Bit 3                | Bit 2                | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|-----------------------|-------|----------|---------------------|--------|----------------------|----------------------|--------|--------|-----------------------------------|

| 300000h | CONFIG1L              | —     | _        | —                   | —      | —                    | —                    | —      | —      | 0000 0000                         |

| 300001h | CONFIG1H              | IESO  | FCMEN    | PRICLKEN            | PLLCFG |                      | FOSC                 | <3:0>  |        | 0010 0101                         |

| 300002h | CONFIG2L              | _     | _        | _                   | BORV   | /<1:0>               | BORE                 | N<1:0> | PWRTEN | 0001 1111                         |

| 300003h | CONFIG2H              | _     | _        |                     | WDPS-  | <3:0>                |                      | WDTE   | N<1:0> | 0011 1111                         |

| 300004h | CONFIG3L              | _     | _        | _                   | _      | _                    | _                    | _      | _      | 0000 0000                         |

| 300005h | CONFIG3H              | MCLRE | _        | P2BMX               | T3CMX  | HFOFST               | CCP3MX               | PBADEN | CCP2MX | 1011 1111                         |

| 300006h | CONFIG4L              | DEBUG | XINST    | _                   | _      | _                    | LVP <sup>(1)</sup>   | _      | STRVEN | 1000 0101                         |

| 300007h | CONFIG4H              | _     | _        | _                   | _      | _                    | _                    | _      | _      | 1111 1111                         |

| 300008h | CONFIG5L              | _     | _        | _                   | _      | CP3 <sup>(2)</sup>   | CP2 <sup>(2)</sup>   | CP1    | CP0    | 0000 1111                         |

| 300009h | CONFIG5H              | CPD   | CPB      | _                   | _      | _                    | _                    | _      | _      | 1100 0000                         |

| 30000Ah | CONFIG6L              | _     | _        | _                   | _      | WRT3 <sup>(2)</sup>  | WRT2 <sup>(2)</sup>  | WRT1   | WRT0   | 0000 1111                         |

| 30000Bh | CONFIG6H              | WRTD  | WRTB     | WRTC <sup>(3)</sup> | _      | _                    | _                    | _      | _      | 1110 0000                         |

| 30000Ch | CONFIG7L              | _     | _        | _                   |        | EBTR3 <sup>(2)</sup> | EBTR2 <sup>(2)</sup> | EBTR1  | EBTR0  | 0000 1111                         |

| 30000Dh | CONFIG7H              | _     | EBTRB    | _                   | _      | _                    | _                    | _      | _      | 0100 0000                         |

| 3FFFFEh | DEVID1 <sup>(4)</sup> |       | DEV<2:0: | >                   |        |                      | REV<4:0>             |        |        | রবরর বরবর                         |

| 3FFFFFh | DEVID2 <sup>(4)</sup> |       |          |                     | DEV<1  | 0:3>                 |                      |        |        | 0101 qqqq                         |

#### TABLE 24-1: CONFIGURATION BITS AND DEVICE IDs

Legend: -= unimplemented, q = value depends on condition. Shaded bits are unimplemented, read as '0'.

Note 1: Can only be changed when in high voltage programming mode.

2: Available on PIC18(L)FX5K22 and PIC18(L)FX6K22 devices only.

3: In user mode, this bit is read-only and cannot be self-programmed.

4: See Register 24-12 and Register 24-13 for DEVID values. DEVID registers are read-only and cannot be programmed by the user.

| Mnemonic,<br>Operands   |         | Description                    | Cualas     | 16-Bit Instruction Word |      |      | Status |                   |       |

|-------------------------|---------|--------------------------------|------------|-------------------------|------|------|--------|-------------------|-------|

|                         |         | Description                    | Cycles     | MSb                     |      |      | LSb    | Affected          | Notes |

| BIT-ORIENTED OPERATIONS |         |                                |            |                         |      |      |        |                   |       |

| BCF                     | f, b, a | Bit Clear f                    | 1          | 1001                    | bbba | ffff | ffff   | None              | 1, 2  |

| BSF                     | f, b, a | Bit Set f                      | 1          | 1000                    | bbba | ffff | ffff   | None              | 1, 2  |

| BTFSC                   | f, b, a | Bit Test f, Skip if Clear      | 1 (2 or 3) | 1011                    | bbba | ffff | ffff   | None              | 3, 4  |

| BTFSS                   | f, b, a | Bit Test f, Skip if Set        | 1 (2 or 3) | 1010                    | bbba | ffff | ffff   | None              | 3, 4  |

| BTG                     | f, b, a | Bit Toggle f                   | 1          | 0111                    | bbba | ffff | ffff   | None              | 1, 2  |

| CONTROL                 | OPERA   | TIONS                          |            |                         |      |      |        | •                 | -     |

| BC                      | n       | Branch if Carry                | 1 (2)      | 1110                    | 0010 | nnnn | nnnn   | None              |       |

| BN                      | n       | Branch if Negative             | 1 (2)      | 1110                    | 0110 | nnnn | nnnn   | None              |       |

| BNC                     | n       | Branch if Not Carry            | 1 (2)      | 1110                    | 0011 | nnnn | nnnn   | None              |       |

| BNN                     | n       | Branch if Not Negative         | 1 (2)      | 1110                    | 0111 | nnnn | nnnn   | None              |       |

| BNOV                    | n       | Branch if Not Overflow         | 1 (2)      | 1110                    | 0101 | nnnn | nnnn   | None              |       |

| BNZ                     | n       | Branch if Not Zero             | 1 (2)      | 1110                    | 0001 | nnnn | nnnn   | None              |       |

| BOV                     | n       | Branch if Overflow             | 1 (2)      | 1110                    | 0100 | nnnn | nnnn   | None              |       |

| BRA                     | n       | Branch Unconditionally         | 2          | 1101                    | 0nnn | nnnn | nnnn   | None              |       |

| BZ                      | n       | Branch if Zero                 | 1 (2)      | 1110                    | 0000 | nnnn | nnnn   | None              |       |

| CALL                    | k, s    | Call subroutine 1st word       | 2          | 1110                    | 110s | kkkk | kkkk   | None              |       |

|                         |         | 2nd word                       |            | 1111                    | kkkk | kkkk | kkkk   |                   |       |

| CLRWDT                  | _       | Clear Watchdog Timer           | 1          | 0000                    | 0000 | 0000 | 0100   | TO, PD            |       |

| DAW                     | —       | Decimal Adjust WREG            | 1          | 0000                    | 0000 | 0000 | 0111   | С                 |       |

| GOTO                    | k       | Go to address 1st word         | 2          | 1110                    | 1111 | kkkk | kkkk   | None              |       |

|                         |         | 2nd word                       |            | 1111                    | kkkk | kkkk | kkkk   |                   |       |

| NOP                     | —       | No Operation                   | 1          | 0000                    | 0000 | 0000 | 0000   | None              |       |

| NOP                     | _       | No Operation                   | 1          | 1111                    | xxxx | xxxx | xxxx   | None              | 4     |

| POP                     | _       | Pop top of return stack (TOS)  | 1          | 0000                    | 0000 | 0000 | 0110   | None              |       |

| PUSH                    | _       | Push top of return stack (TOS) | 1          | 0000                    | 0000 | 0000 | 0101   | None              |       |

| RCALL                   | n       | Relative Call                  | 2          | 1101                    | 1nnn | nnnn | nnnn   | None              |       |

| RESET                   |         | Software device Reset          | 1          | 0000                    | 0000 | 1111 | 1111   | All               |       |

| RETFIE                  | S       | Return from interrupt enable   | 2          | 0000                    | 0000 | 0001 | 000s   | GIE/GIEH,         |       |

| RETLW                   | k       | Return with literal in WREG    | 2          | 0000                    | 1100 | kkkk | kkkk   | PEIE/GIEL<br>None |       |

| RETURN                  | S       | Return from Subroutine         | 2          | 0000                    | 0000 | 0001 | 001s   | None              |       |

| SLEEP                   | _       | Go into Standby mode           | 1          | 0000                    | 0000 | 0000 | 0013   | TO, PD            |       |

#### TABLE 25-2: PIC18(L)F2X/4XK22 INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| MULLW                               |                     | Multiply                                                                                                   | Multiply literal with W                                                                                                                                                                                                                                                                                                                                                                      |          |                                      |  |  |  |

|-------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------|--|--|--|

| Syntax:                             |                     | MULLW                                                                                                      | MULLW k                                                                                                                                                                                                                                                                                                                                                                                      |          |                                      |  |  |  |

| Operands:                           |                     | $0 \le k \le 25$                                                                                           | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                                                            |          |                                      |  |  |  |

| Operation:                          |                     | (W) x k →                                                                                                  | (W) x k $\rightarrow$ PRODH:PRODL                                                                                                                                                                                                                                                                                                                                                            |          |                                      |  |  |  |

| Statu                               | is Affected:        | None                                                                                                       | None                                                                                                                                                                                                                                                                                                                                                                                         |          |                                      |  |  |  |

| Encoding:                           |                     | 0000                                                                                                       | 1101                                                                                                                                                                                                                                                                                                                                                                                         | kkkk     | kkkk                                 |  |  |  |

| Description:                        |                     | out betwee<br>8-bit litera<br>placed in<br>pair. PRO<br>W is unch<br>None of th<br>Note that<br>possible i | An unsigned multiplication is carried<br>out between the contents of W and the<br>8-bit literal 'k'. The 16-bit result is<br>placed in the PRODH:PRODL register<br>pair. PRODH contains the high byte.<br>W is unchanged.<br>None of the Status flags are affected.<br>Note that neither overflow nor carry is<br>possible in this operation. A zero result<br>is possible but not detected. |          |                                      |  |  |  |

| Word                                | ds:                 | 1                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                              |          |                                      |  |  |  |

| Cycle                               | es:                 | 1                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                              |          |                                      |  |  |  |

| QC                                  | ycle Activity:      |                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                              |          |                                      |  |  |  |

|                                     | Q1                  | Q2                                                                                                         | Q3                                                                                                                                                                                                                                                                                                                                                                                           |          | Q4                                   |  |  |  |

|                                     | Decode              | Read<br>literal 'k'                                                                                        | Proce<br>Dat                                                                                                                                                                                                                                                                                                                                                                                 | a r<br>F | Write<br>egisters<br>PRODH:<br>PRODL |  |  |  |

| Example:<br>Before Instruction      |                     | MULLW                                                                                                      | 0C4h                                                                                                                                                                                                                                                                                                                                                                                         |          |                                      |  |  |  |

| W                                   |                     |                                                                                                            | 2h                                                                                                                                                                                                                                                                                                                                                                                           |          |                                      |  |  |  |

| PRODH<br>PRODL<br>After Instruction |                     | = ?                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                              |          |                                      |  |  |  |

|                                     | W<br>PRODH<br>PRODL | = A                                                                                                        | 2h<br>\Dh<br>\8h                                                                                                                                                                                                                                                                                                                                                                             |          |                                      |  |  |  |