Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 35                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 30x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k22t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

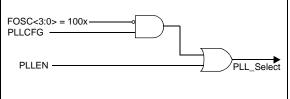

# FIGURE 2-3: PLL\_SELECT BLOCK DIAGRAM

# TABLE 2-1: PLL\_SELECT TRUTH TABLE

| Primary Clock MUX Source    | FOSC<3:0> | PLLCFG | PLLEN | PLL_Select |

|-----------------------------|-----------|--------|-------|------------|

| FOSC (any source)           | 0000-1111 | 0      | 0     | 0          |

| OSC1/OSC2 (external source) | 0000-0111 | 1      | х     | 1          |

|                             | 1010-1111 | 0      | 1     | 1          |

| INTOSC (internal source)    | 1000-1001 | x      | 0     | 0          |

|                             |           | x      | 1     | 1          |

## 6.5 Erasing Flash Program Memory

The minimum erase block is 32 words or 64 bytes. Only through the use of an external programmer, or through ICSP<sup>™</sup> control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. The TBLPTR<5:0> bits are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

The write initiate sequence for EECON2, shown as steps 4 through 6 in **Section 6.5.1** "**Flash Program Memory Erase Sequence**", is used to guard against accidental writes. This is sometimes referred to as a long write.

A long write is necessary for erasing the internal Flash. Instruction execution is halted during the long write cycle. The long write is terminated by the internal programming timer.

#### 6.5.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory is:

- 1. Load Table Pointer register with address of block being erased.

- 2. Set the EECON1 register for the erase operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN bit to enable writes;

- set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the block erase cycle.

- 7. The CPU will stall for duration of the erase (about 2 ms using internal timer).

- 8. Re-enable interrupts.

|          | MOVLW | CODE_ADDR_UPPER | ; load TBLPTR with the base     |

|----------|-------|-----------------|---------------------------------|

|          | MOVWF | TBLPTRU         | ; address of the memory block   |

|          | MOVLW | CODE_ADDR_HIGH  |                                 |

|          | MOVWF | TBLPTRH         |                                 |

|          | MOVLW | CODE_ADDR_LOW   |                                 |

|          | MOVWF | TBLPTRL         |                                 |

| ERASE_BL | ЭСК   |                 |                                 |

|          | BSF   | EECON1, EEPGD   | ; point to Flash program memory |

|          | BCF   | EECON1, CFGS    | ; access Flash program memory   |

|          | BSF   | EECON1, WREN    | ; enable write to memory        |

|          | BSF   | EECON1, FREE    | ; enable block Erase operation  |

|          | BCF   | INTCON, GIE     | ; disable interrupts            |

| Required | MOVLW | 55h             |                                 |

| Sequence | MOVWF | EECON2          | ; write 55h                     |

|          | MOVLW | 0AAh            |                                 |

|          | MOVWF | EECON2          | ; write OAAh                    |

|          | BSF   | EECON1, WR      | ; start erase (CPU stall)       |

|          | BSF   | INTCON, GIE     | ; re-enable interrupts          |

|          | BSF   | INTCON, GIE     | ; re-enable interrupts          |

#### EXAMPLE 6-2: ERASING A FLASH PROGRAM MEMORY BLOCK

| Pin Name         | Function | TRIS<br>Setting | ANSEL setting | Pin<br>Type | Buffer<br>Type | Description                                              |

|------------------|----------|-----------------|---------------|-------------|----------------|----------------------------------------------------------|

| RD6/P1C/TX2/CK2/ | RD6      | 0               | 0             | 0           | DIG            | LATD<6> data output; not affected by analog input.       |

| AN26             |          | 1               | 0             | I           | ST             | PORTD<6> data input; disabled when analog input enabled. |

|                  | P1C      | 0               | 0             | 0           | DIG            | Enhanced CCP1 PWM output 3.                              |

|                  | TX2      | 1               | 0             | 0           | DIG            | EUSART asynchronous transmit data output.                |

|                  | CK2      | 1               | 0             | 0           | DIG            | EUSART synchronous serial clock output.                  |

|                  |          | 1               | 0             | I           | ST             | EUSART synchronous serial clock input.                   |

|                  | AN26     | 1               | 1             | I           | AN             | Analog input 26.                                         |

| RD7/P1D/RX2/DT2/ | RD7      | 0               | 0             | 0           | DIG            | LATD<7> data output; not affected by analog input.       |

| AN27             |          | 1               | 0             | I           | ST             | PORTD<7> data input; disabled when analog input enabled. |

|                  | P1D      | 0               | 0             | 0           | DIG            | Enhanced CCP1 PWM output 4.                              |

|                  | RX2      | 1               | 0             | Ι           | ST             | EUSART asynchronous receive data in.                     |

|                  | DT2      | 1               | 0             | 0           | DIG            | EUSART synchronous serial data output.                   |

|                  |          | 1               | 0             | Ι           | ST             | EUSART synchronous serial data input.                    |

|                  | AN27     | 1               | 1             | Ι           | AN             | Analog input 27.                                         |

## TABLE 10-11: PORTD I/O SUMMARY (CONTINUED)

Legend:AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS =<br/>CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;  $I^2C$  = Schmitt Trigger input with  $I^2C$ .

**Note 1:** Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

| U-0                               | U-0 | U-0 | U-0                                     | R/W-1                            | R/W-1                                                                                           | R/W-1                                                                              |  |

|-----------------------------------|-----|-----|-----------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| —                                 | —   | —   | —                                       | ANSE2 <sup>(1)</sup>             | ANSE1 <sup>(1)</sup>                                                                            | ANSE0 <sup>(1)</sup>                                                               |  |

|                                   |     |     |                                         |                                  |                                                                                                 | bit 0                                                                              |  |

|                                   |     |     |                                         |                                  |                                                                                                 |                                                                                    |  |

|                                   |     |     |                                         |                                  |                                                                                                 |                                                                                    |  |

| R = Readable bit W = Writable bit |     |     | U = Unimplemented bit, read as '0'      |                                  |                                                                                                 |                                                                                    |  |

| Value at POR '1' = Bit is set     |     |     | '0' = Bit is cleared x = Bit is unknown |                                  |                                                                                                 |                                                                                    |  |

|                                   |     |     |                                         | Dit W = Writable bit U = Unimple | —     —     —     ANSE2 <sup>(1)</sup> Dit     W = Writable bit     U = Unimplemented bit, read | $ ANSE2^{(1)} ANSE1^{(1)}$ Dit W = Writable bit U = Unimplemented bit, read as '0' |  |

### REGISTER 10-7: ANSELE – PORTE ANALOG SELECT REGISTER

bit 7-3 Unimplemented: Read as '0'

bit 2-0 ANSE<2:0>: RE<2:0> Analog Select bit<sup>(1)</sup>

1 = Digital input buffer disabled

0 = Digital input buffer enabled

**Note 1:** Available on PIC18(L)F4XK22 devices only.

#### REGISTER 10-8: TRISx: PORTx TRI-STATE REGISTER<sup>(1)</sup>

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISx7 | TRISx6 | TRISx5 | TRISx4 | TRISx3 | TRISx2 | TRISx1 | TRISx0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                                                                      |                      |                    |  |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 7-0 TRISx<7:0>: PORTx Tri-State Control bit

1 = PORTx pin configured as an input (tri-stated)

0 = PORTx pin configured as an output

**Note 1:** Register description for TRISA, TRISB, TRISC and TRISD.

#### REGISTER 10-9: TRISE: PORTE TRI-STATE REGISTER

| R/W-1       | U-0 | U-0 | U-0 | U-0 | R/W-1                 | R/W-1                 | R/W-1                 |  |

|-------------|-----|-----|-----|-----|-----------------------|-----------------------|-----------------------|--|

| WPUE3       | —   | —   | —   | —   | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> |  |

| bit 7 bit 0 |     |     |     |     |                       |                       |                       |  |

| Legend:          |                           |                                                   |                       |                    |

|------------------|---------------------------|---------------------------------------------------|-----------------------|--------------------|

| R = Readable bit |                           | W = Writable bit                                  | U = Unimplemented bit | , read as '0'      |

| -n = Value       | n = Value at POR '1' = Bi |                                                   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7            | WPUE3:                    | Weak Pull-up Register bits                        |                       |                    |

|                  |                           | up enabled on PORT pin<br>up disabled on PORT pin |                       |                    |

| 1.11.0.0         |                           |                                                   |                       |                    |

bit 6-3 Unimplemented: Read as '0'

bit 2-0 TRISE<7:0>: PORTE Tri-State Control bit<sup>(1)</sup>

1 = PORTE pin configured as an input (tri-stated)

0 = PORTE pin configured as an output

Note 1: Available on PIC18(L)F4XK22 devices only.

© 2010-2016 Microchip Technology Inc.

### 15.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPxOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 15-5.

An MSSPx interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCLx will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 15.2.3 "SPI Master Mode"** for more detail.

#### 15.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSPx module configured as an  $I^2C$  slave in 7-bit Addressing mode. All decisions made by hardware or software and their effect on reception. Figure 15-14 and Figure 15-5 are used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $\mathsf{I}^2\mathsf{C}$  communication.

- 1. Start bit detected.

- S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCLx line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes Idle.

### 15.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the 8th falling edge of SCLx. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 15-16 displays a module using both address and data holding. Figure 15-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- 1. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the 8th falling edge of SCLx.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPx-CON3 register to <u>determine</u> if the SSPxIF was after or before the ACK.

- 5. Slave reads the address value from SSPxBUF, clearing the BF flag.

- Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF

**Note:** SSPxIF is still set after the 9th falling edge of SCLx even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPxIF not set.

- 11. SSPxIF set and CKP cleared after 8th falling edge of SCLx for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

#### 15.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCLx pin is held low (see **Section 15.5.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then the SCLx pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCLx input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes Idle and waits for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCLx pin must be released by setting bit CKP.

An MSSPx interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 15.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDAx line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIRx register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

#### 15.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 15-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDAx and SCLx.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit set is received by the slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCLx, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

**Note 1:** If the master ACKs the clock will be stretched.

**2:** ACKSTAT is the only bit updated on the rising edge of SCLx (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

# 15.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPxM bits in the SSPxCON1 register and by setting the SSPxEN bit. In Master mode, the SCLx and SDAx lines are set as inputs and are manipulated by the MSSPx hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSPx module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDAx and SCLx lines.

The following events will cause the SSPx Interrupt Flag bit, SSPxIF, to be set (SSPx interrupt, if enabled):

- Start condition detected

- Stop condition detected

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSPx module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

## 15.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDAx, while SCLx outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDAx, while SCLx outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCLx. See Section 15.7 "Baud Rate Generator" for more detail.

## 19.1 CTMU Operation

The CTMU works by using a fixed current source to charge a circuit. The type of circuit depends on the type of measurement being made. In the case of charge measurement, the current is fixed, and the amount of time the current is applied to the circuit is fixed. The amount of voltage read by the A/D is then a measurement of the capacitance of the circuit. In the case of time measurement, the current, as well as the capacitance of the circuit, is fixed. In this case, the voltage read by the A/D is then representative of the amount of time elapsed from the time the current source starts and stops charging the circuit.

If the CTMU is being used as a time delay, both capacitance and current source are fixed, as well as the voltage supplied to the comparator circuit. The delay of a signal is determined by the amount of time it takes the voltage to charge to the comparator threshold voltage.

#### 19.1.1 THEORY OF OPERATION

The operation of the CTMU is based on the equation for charge:

$$I = C \cdot \frac{dV}{dT}$$

More simply, the amount of charge measured in coulombs in a circuit is defined as current in amperes (*I*) multiplied by the amount of time in seconds that the current flows (t). Charge is also defined as the capacitance in farads (C) multiplied by the voltage of the circuit (V). It follows that:

$$I \cdot t = C \cdot V.$$

The CTMU module provides a constant, known current source. The A/D Converter is used to measure (V) in the equation, leaving two unknowns: capacitance (C) and time (t). The above equation can be used to calculate capacitance or time, by either the relationship using the known fixed capacitance of the circuit:

$$t = (C \cdot V) / I$$

or by:

$$C = (I \cdot t) / V$$

using a fixed time that the current source is applied to the circuit.

### 19.1.2 CURRENT SOURCE

At the heart of the CTMU is a precision current source, designed to provide a constant reference for measurements. The level of current is user-selectable across three ranges, with the ability to trim the output. The current range is selected by the IRNG<1:0> bits (CTMUICON<1:0>), with a value of '00' representing the lowest range.

Current trim is provided by the ITRIM<5:0> bits (CTMUICON<7:2>). Note that half of the range adjusts the current source positively and the other half reduces the current source. A value of '000000' is the neutral position (no change). A value of '100000' is the maximum negative adjustment, and '011111' is the maximum positive adjustment.

## 19.1.3 EDGE SELECTION AND CONTROL

CTMU measurements are controlled by edge events occurring on the module's two input channels. Each channel, referred to as Edge 1 and Edge 2, can be configured to receive input pulses from one of the edge input pins (CTED1 and CTED2) or ECCPx Special Event Triggers. The input channels are level-sensitive, responding to the instantaneous level on the channel rather than a transition between levels. The inputs are selected using the EDG1SEL and EDG2SEL bit pairs (CTMUCONL<3:2 and 6:5>).

In addition to source, each channel can be configured for event polarity using the EDGE2POL and EDGE1POL bits (CTMUCONL<7,4>). The input channels can also be filtered for an edge event sequence (Edge 1 occurring before Edge 2) by setting the EDGSEQEN bit (CTMUCONH<2>).

### 19.1.4 EDGE STATUS

The CTMUCONL register also contains two Status bits: EDG2STAT and EDG1STAT (CTMUCONL<1:0>). Their primary function is to show if an edge response has occurred on the corresponding channel. The CTMU automatically sets a particular bit when an edge response is detected on its channel. The level-sensitive nature of the input channels also means that the Status bits become set immediately if the channel's configuration is changed and is the same as the channel's current state.

|               | 19-2: CTM                                                                                                                                                                                                                                                         | UCONL. CIN                                            |                  | REGISTER          |                  |                 |          |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-------------------|------------------|-----------------|----------|

| R/W-0         | R/W-0                                                                                                                                                                                                                                                             | R/W-0                                                 | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0    |

| EDG2POL       | EDG28                                                                                                                                                                                                                                                             | SEL<1:0>                                              | EDG1POL          | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |

| bit 7         |                                                                                                                                                                                                                                                                   |                                                       |                  |                   |                  |                 | bit      |

|               |                                                                                                                                                                                                                                                                   |                                                       |                  |                   |                  |                 |          |

| Legend:       |                                                                                                                                                                                                                                                                   |                                                       |                  |                   |                  |                 |          |

| R = Readable  | e bit                                                                                                                                                                                                                                                             | W = Writable                                          | bit              | U = Unimplen      | nented bit, read | 1 as '0'        |          |

| -n = Value at | POR                                                                                                                                                                                                                                                               | '1' = Bit is set                                      |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |

| bit 7         | EDG2POL:                                                                                                                                                                                                                                                          | Edge 2 Polarity                                       | Select bit       |                   |                  |                 |          |

|               | <b>.</b> .                                                                                                                                                                                                                                                        | programmed for<br>programmed for                      |                  |                   |                  |                 |          |

| bit 6-5       | EDG2SEL<1                                                                                                                                                                                                                                                         | I:0>: Edge 2 Sc                                       | ource Select bit | S                 |                  |                 |          |

|               |                                                                                                                                                                                                                                                                   |                                                       |                  |                   |                  |                 |          |

| bit 4         | EDG1POL:                                                                                                                                                                                                                                                          | Edge 1 Polarity                                       | Select bit       |                   |                  |                 |          |

|               |                                                                                                                                                                                                                                                                   | programmed for<br>programmed for                      |                  |                   |                  |                 |          |

| bit 3-2       | <ul> <li>0 = Edge 1 programmed for a negative edge response</li> <li>EDG1SEL&lt;1:0&gt;: Edge 1 Source Select bits</li> <li>11 = CTED1 pin</li> <li>10 = CTED2 pin</li> <li>01 = ECCP1 Special Event Trigger</li> <li>00 = ECCP2 Special Event Trigger</li> </ul> |                                                       |                  |                   |                  |                 |          |

| bit 1         | <b>EDG2STAT:</b><br>1 = Edge 2 (                                                                                                                                                                                                                                  | Edge 2 Status I<br>event has occur<br>event has not o | pit<br>red       |                   |                  |                 |          |

| bit 0         | 1 = Edge 1                                                                                                                                                                                                                                                        | Edge 1 Status I<br>event has occur<br>event has not o | red              |                   |                  |                 |          |

### REGISTER 19-2: CTMUCONL: CTMU CONTROL REGISTER 1

# 22.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- ADC input channel

- DACOUT pin

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the VREFCON1 register.

# 22.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the VREFCON2 register.

The DAC output voltage is determined by the following equations:

# EQUATION 22-1: DAC OUTPUT VOLTAGE

$$VOUT = \left( (VSRC+ - VSRC-) \neq \frac{DACR < 4:0>}{2^5} \right) + VSRC-$$

$$VSRC+ = VDD, VREF+ or FVR1$$

$$VSRC- = VSS or VREF-$$

# 22.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 27.0** "**Electrical Specifications**".

## 22.3 Low-Power Voltage State

In order for the DAC module to consume the least amount of power, one of the two voltage reference input sources to the resistor ladder must be disconnected. Either the positive voltage source, (VSRC+), or the negative voltage source, (VSRC-) can be disabled. The negative voltage source is disabled by setting the DACLPS bit in the VREFCON1 register. Clearing the DACLPS bit in the VREFCON1 register disables the positive voltage source.

## 22.4 Output Clamped to Positive Voltage Source

The DAC output voltage can be set to VsRC+ with the least amount of power consumption by performing the following:

- Clearing the DACEN bit in the VREFCON1 register.

- Setting the DACLPS bit in the VREFCON1 register.

- Configuring the DACPSS bits to the proper positive source.

- Configuring the DACRx bits to '11111' in the VREFCON2 register.

This is also the method used to output the voltage level from the FVR to an output pin. See **Section 22.6 "DAC Voltage Reference Output"** for more information.

## 22.5 Output Clamped to Negative Voltage Source

The DAC output voltage can be set to VSRC- with the least amount of power consumption by performing the following:

- Clearing the DACEN bit in the VREFCON1 register.

- Clearing the DACLPS bit in the VREFCON1 register.

- Configuring the DACPSS bits to the proper negative source.

- Configuring the DACRx bits to '00000' in the VREFCON2 register.

This allows the comparator to detect a zero-crossing while not consuming additional current through the DAC module.

# 22.6 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the VREFCON1 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 22-2 shows an example buffering technique.

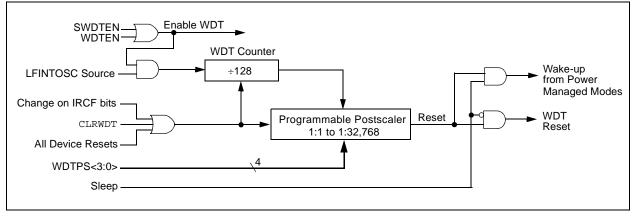

## 24.3 Watchdog Timer (WDT)

For PIC18(L)F2X/4XK22 devices, the WDT is driven by the LFINTOSC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the LFINTOSC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration Register 2H. Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: a SLEEP or CLRWDT instruction is executed, the IRCF bits of the OSCCON register are changed or a clock failure has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: Changing the setting of the IRCF bits of the OSCCON register clears the WDT and postscaler counts.

- **3:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

#### FIGURE 24-1: WDT BLOCK DIAGRAM

| BTG               | Bit Togg                                                                                                                                                                                                                                                                                                                                                                                                          | Bit Toggle f  |      |                     |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|---------------------|--|--|--|--|--|

| Syntax:           | BTG f, b {,                                                                                                                                                                                                                                                                                                                                                                                                       | BTG f, b {,a} |      |                     |  |  |  |  |  |

| Operands:         | 0 ≤ f ≤ 255<br>0 ≤ b < 7<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                             |               |      |                     |  |  |  |  |  |

| Operation:        | $(\overline{f}\!<\!b\!\!>) \to f$                                                                                                                                                                                                                                                                                                                                                                                 | <b></b>       |      |                     |  |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                                                                                                                              |               |      |                     |  |  |  |  |  |

| Encoding:         | 0111                                                                                                                                                                                                                                                                                                                                                                                                              | bbba          | ffff | ffff                |  |  |  |  |  |

|                   | inverted.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |               |      |                     |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                 |               |      |                     |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                 |               |      |                     |  |  |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                                   |               |      |                     |  |  |  |  |  |

| Q1                | Q2                                                                                                                                                                                                                                                                                                                                                                                                                | Q3            |      | Q4                  |  |  |  |  |  |

| Decode            | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                              | Proce<br>Data |      | Write<br>gister 'f' |  |  |  |  |  |

| Example:          |                                                                                                                                                                                                                                                                                                                                                                                                                   | PORTC,        | 4, 0 |                     |  |  |  |  |  |

| Before Instruction: |      |      |       |

|---------------------|------|------|-------|

| PORTC =             | 0111 | 0101 | [75h] |

| After Instruction:  |      |      |       |

| PORTC =             | 0110 | 0101 | [65h] |

| BOV                                                                                    | /                           | Branch if                                                                             | Branch if Overflow                                                                                                                                                                                                                                                                       |               |                 |  |  |  |  |  |

|----------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|--|--|--|--|--|

| Syntax:                                                                                |                             | BOV n                                                                                 | BOV n                                                                                                                                                                                                                                                                                    |               |                 |  |  |  |  |  |

| Oper                                                                                   | ands:                       | -128 ≤ n ≤ ′                                                                          | $-128 \le n \le 127$                                                                                                                                                                                                                                                                     |               |                 |  |  |  |  |  |

| Oper                                                                                   | ation:                      | -                                                                                     | if OVERFLOW bit is '1' (PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                    |               |                 |  |  |  |  |  |

| Statu                                                                                  | s Affected:                 | None                                                                                  | None                                                                                                                                                                                                                                                                                     |               |                 |  |  |  |  |  |

| Enco                                                                                   | ding:                       | 1110                                                                                  | 1110 0100 nnnn n                                                                                                                                                                                                                                                                         |               |                 |  |  |  |  |  |

| Desc                                                                                   | ription:                    | program wi<br>The 2's cor<br>added to th<br>incremente<br>instruction,<br>PC + 2 + 2t | If the OVERFLOW bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction. |               |                 |  |  |  |  |  |

| Word                                                                                   | ls:                         | 1                                                                                     | 1                                                                                                                                                                                                                                                                                        |               |                 |  |  |  |  |  |

| Cycle                                                                                  | es:                         | 1(2)                                                                                  | 1(2)                                                                                                                                                                                                                                                                                     |               |                 |  |  |  |  |  |

| Q Cycle Activity:<br>If Jump:                                                          |                             |                                                                                       |                                                                                                                                                                                                                                                                                          |               |                 |  |  |  |  |  |

| Q1                                                                                     |                             | Q2                                                                                    | Q3                                                                                                                                                                                                                                                                                       | _             | Q4              |  |  |  |  |  |

|                                                                                        | Decode                      | Read literal<br>'n'                                                                   | Process<br>Data                                                                                                                                                                                                                                                                          |               | Write to PC     |  |  |  |  |  |

|                                                                                        | No No<br>operation operatio |                                                                                       | No<br>operation                                                                                                                                                                                                                                                                          |               | No<br>operation |  |  |  |  |  |

| lf No                                                                                  | o Jump:                     |                                                                                       |                                                                                                                                                                                                                                                                                          |               |                 |  |  |  |  |  |

|                                                                                        | Q1                          | Q2                                                                                    | Q3                                                                                                                                                                                                                                                                                       |               | Q4              |  |  |  |  |  |

|                                                                                        | Decode                      | Read literal<br>'n'                                                                   | Process<br>Data                                                                                                                                                                                                                                                                          |               | No<br>operation |  |  |  |  |  |

| Example:<br>Before Instruction<br>PC<br>After Instruction                              |                             | = ad                                                                                  |                                                                                                                                                                                                                                                                                          | Jump<br>HERE) |                 |  |  |  |  |  |

| If OVERFLOW = 1;<br>PC = address (Jump)<br>If OVERFLOW = 0;<br>PC = address (HERE + 2) |                             |                                                                                       |                                                                                                                                                                                                                                                                                          |               |                 |  |  |  |  |  |

|                                                                   | Complem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ent f                                                       |         |                |  |  |  |  |  |  |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------|----------------|--|--|--|--|--|--|

| Syntax:                                                           | COMF f {                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | {,d {,a}}                                                   |         |                |  |  |  |  |  |  |

| Operands:                                                         | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\begin{array}{l} 0\leq f\leq 255\\ d\in [0,1] \end{array}$ |         |                |  |  |  |  |  |  |

| Operation:                                                        | $(\overline{f}) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |         |                |  |  |  |  |  |  |

| Status Affected:                                                  | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | N, Z                                                        |         |                |  |  |  |  |  |  |

| Encoding:                                                         | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11da f                                                      | fff     | ffff           |  |  |  |  |  |  |

| Description:                                                      | The contents of register 'f' are<br>complemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f' (default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed |                                                             |         |                |  |  |  |  |  |  |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | set Mode" fo                                                | or deta | ils.           |  |  |  |  |  |  |

| Words:                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |         |                |  |  |  |  |  |  |

| Cycles:                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |         |                |  |  |  |  |  |  |

| Q Cycle Activity:                                                 | 0.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.0                                                         |         | ~ /            |  |  |  |  |  |  |

| Q1<br>Decode                                                      | Q2<br>Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Q3<br>Process                                               | L V     | Q4<br>Vrite to |  |  |  |  |  |  |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Data                                                        |         |                |  |  |  |  |  |  |

| Decode                                                            | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Dala                                                        | de      | stination      |  |  |  |  |  |  |

| Example:<br>Before Instruc<br>REG<br>After Instructio<br>REG<br>W | COMF<br>tion<br>= 13h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | REG, 0,                                                     |         | stination      |  |  |  |  |  |  |

| 005050                           | 0                        | 6                                                                         |                 |  |  |  |  |  |  |

|----------------------------------|--------------------------|---------------------------------------------------------------------------|-----------------|--|--|--|--|--|--|

| CPFSEQ                           | -                        | f with W, sk                                                              | ID IT T = W     |  |  |  |  |  |  |

| Syntax:                          | CPFSEQ                   | f {,a}                                                                    |                 |  |  |  |  |  |  |

| Operands:                        | 0 ≤ f ≤ 255<br>a ∈ [0,1] | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                  |                 |  |  |  |  |  |  |

| Operation:                       | (f) – (W),               |                                                                           |                 |  |  |  |  |  |  |

|                                  | skip if $(f) = ($        |                                                                           |                 |  |  |  |  |  |  |

| Statua Affaatad                  |                          | (unsigned comparison)<br>None                                             |                 |  |  |  |  |  |  |

| Status Affected:                 |                          | 001- 555                                                                  |                 |  |  |  |  |  |  |

| Encoding:<br>Description:        |                          | 0110 001a ffff ffff                                                       |                 |  |  |  |  |  |  |

| Description.                     |                          | Compares the contents of data memory location 'f' to the contents of W by |                 |  |  |  |  |  |  |

|                                  | performing               | performing an unsigned subtraction.                                       |                 |  |  |  |  |  |  |

|                                  | ,                        | en the fetched<br>and a NOP is ex                                         |                 |  |  |  |  |  |  |

|                                  |                          | king this a 2-c                                                           |                 |  |  |  |  |  |  |

|                                  | instruction.             | 5                                                                         |                 |  |  |  |  |  |  |

|                                  |                          | he Access Bar                                                             |                 |  |  |  |  |  |  |

|                                  | GPR bank.                | he BSR is use                                                             | d to select the |  |  |  |  |  |  |

|                                  |                          | nd the extende                                                            | ed instruction  |  |  |  |  |  |  |

|                                  |                          | set is enabled, this instruction operates                                 |                 |  |  |  |  |  |  |

|                                  |                          | Literal Offset A<br>iever f ≤ 95 (5F                                      | 0               |  |  |  |  |  |  |

|                                  |                          | .2.3 "Byte-Ori                                                            | ,               |  |  |  |  |  |  |

|                                  |                          | d Instruction                                                             |                 |  |  |  |  |  |  |

|                                  |                          | set Mode" for                                                             | details.        |  |  |  |  |  |  |

| Words:                           | 1                        |                                                                           |                 |  |  |  |  |  |  |

| Cycles:                          | 1(2)<br>Note: 3 cv       | ycles if skip an                                                          | d followed      |  |  |  |  |  |  |

|                                  |                          | a 2-word instru                                                           |                 |  |  |  |  |  |  |

| Q Cycle Activity:                |                          |                                                                           |                 |  |  |  |  |  |  |

| Q1                               | Q2                       | Q3                                                                        | Q4              |  |  |  |  |  |  |

| Decode                           | Read                     | Process                                                                   | No              |  |  |  |  |  |  |

| lf skip:                         | register 'f'             | Data                                                                      | operation       |  |  |  |  |  |  |

| Q1                               | Q2                       | Q3                                                                        | Q4              |  |  |  |  |  |  |

| No                               | No                       | No                                                                        | No              |  |  |  |  |  |  |

| operation<br>If skip and followe | operation                | operation                                                                 | operation       |  |  |  |  |  |  |

| Q1                               | Q2                       | Q3                                                                        | Q4              |  |  |  |  |  |  |

| No                               | No                       | No                                                                        | No              |  |  |  |  |  |  |