## NXP USA Inc. - KMPC8349VVAJDB Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 533MHz                                                                 |

| Co-Processors/DSP               | - ·                                                                    |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | - ·                                                                    |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | -                                                                      |

| USB                             | USB 2.0 + PHY (2)                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 672-LBGA                                                               |

| Supplier Device Package         | 672-LBGA (35x35)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8349vvajdb |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **RESET** Initialization

## Table 9. RESET Pins DC Electrical Characteristics<sup>1</sup> (continued)

| Parameter          | Symbol          | Condition                | Min | Max | Unit |

|--------------------|-----------------|--------------------------|-----|-----|------|

| Output low voltage | V <sub>OL</sub> | l <sub>OL</sub> = 3.2 mA | _   | 0.4 | V    |

Notes:

1. This table applies for pins PORESET, HRESET, SRESET, and QUIESCE.

2. HRESET and SRESET are open drain pins, thus V<sub>OH</sub> is not relevant for those pins.

## 5.2 **RESET AC Electrical Characteristics**

Table 10 provides the reset initialization AC timing specifications of the MPC8349EA.

### Table 10. RESET Initialization Timing Specifications

| Parameter                                                                                                                                                            | Min | Max | Unit                     | Notes |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|-------|

| Required assertion time of HRESET or SRESET (input) to activate reset flow                                                                                           | 32  | —   | t <sub>PCI_SYNC_IN</sub> | 1     |

| Required assertion time of $\overrightarrow{\text{PORESET}}$ with stable clock applied to CLKIN when the MPC8349EA is in PCI host mode                               | 32  | —   | t <sub>CLKIN</sub>       | 2     |

| Required assertion time of PORESET with stable clock applied to PCI_SYNC_IN when the MPC8349EA is in PCI agent mode                                                  | 32  | _   | t <sub>PCI_SYNC_IN</sub> | 1     |

| HRESET/SRESET assertion (output)                                                                                                                                     | 512 | —   | t <sub>PCI_SYNC_IN</sub> | 1     |

| HRESET negation to SRESET negation (output)                                                                                                                          | 16  | —   | t <sub>PCI_SYNC_IN</sub> | 1     |

| Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the MPC8349EA is in PCI host mode  | 4   | —   | t <sub>CLKIN</sub>       | 2     |

| Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the MPC8349EA is in PCI agent mode | 4   | _   | <sup>t</sup> PCI_SYNC_IN | 1     |

| Input hold time for POR configuration signals with respect to negation of HRESET                                                                                     | 0   | —   | ns                       | —     |

| Time for the MPC8349EA to turn off POR configuration signals with respect to the assertion of HRESET                                                                 | —   | 4   | ns                       | 3     |

| Time for the MPC8349EA to turn on POR configuration signals with respect to the negation of $\overline{\text{HRESET}}$                                               | 1   | —   | t <sub>PCI_SYNC_IN</sub> | 1, 3  |

Notes:

1. t<sub>PCI\_SYNC\_IN</sub> is the clock period of the input clock applied to PCI\_SYNC\_IN. In PCI host mode, the primary clock is applied to the CLKIN input, and PCI\_SYNC\_IN period depends on the value of CFG\_CLKIN\_DIV. See the *MPC8349EA PowerQUICC II Pro Integrated Host Processor Family Reference Manual*.

2. t<sub>CLKIN</sub> is the clock period of the input clock applied to CLKIN. It is valid only in PCI host mode. See the MPC8349EA PowerQUICC II Pro Integrated Host Processor Family Reference Manual.

3. POR configuration signals consist of CFG\_RESET\_SOURCE[0:2] and CFG\_CLKIN\_DIV.

Table 11 lists the PLL and DLL lock times.

Table 11. PLL and DLL Lock Times

| Parameter/Condition | Min  | Мах     | Unit           | Notes |

|---------------------|------|---------|----------------|-------|

| PLL lock times      | —    | 100     | μs             |       |

| DLL lock times      | 7680 | 122,880 | csb_clk cycles | 1, 2  |

Notes:

1. DLL lock times are a function of the ratio between the output clock and the coherency system bus clock (csb\_clk). A 2:1 ratio results in the minimum and an 8:1 ratio results in the maximum.

2. The csb\_clk is determined by the CLKIN and system PLL ratio. See Section 19, "Clocking."

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR SDRAM interface of the MPC8349EA. Note that DDR SDRAM is  $GV_{DD}(typ) = 2.5$  V and DDR2 SDRAM is  $GV_{DD}(typ) = 1.8$  V. The AC electrical specifications are the same for DDR and DRR2 SDRAM.

## NOTE

The information in this document is accurate for revision 3.0 silicon and later. For information on revision 1.1 silicon and earlier versions see the *MPC8349E PowerQUICC II Pro Integrated Host Processor Hardware Specifications*. See Section 22.1, "Part Numbers Fully Addressed by This Document," for silicon revision level determination.

## 6.1 DDR and DDR2 SDRAM DC Electrical Characteristics

Table 12 provides the recommended operating conditions for the DDR2 SDRAM component(s) of the MPC8349EA when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol            | Min                       | Мах                       | Unit | Notes |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.71                      | 1.89                      | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 	imes GV_{DD}$      | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | —     |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | —     |

| Output leakage current                           | I <sub>OZ</sub>   | -9.9                      | 9.9                       | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>   | -13.4                     |                           | mA   | —     |

#### DDR and DDR2 SDRAM

### Table 20. DDR and DDR2 SDRAM Output AC Timing Specifications (continued)

At recommended operating conditions with GV<sub>DD</sub> of (1.8 or 2.5 V)  $\pm$  5%.

| Parameter         | Symbol <sup>1</sup> | Min  | Мах | Unit | Notes |

|-------------------|---------------------|------|-----|------|-------|

| MDQS epilogue end | t <sub>DDKHME</sub> | -0.6 | 0.6 | ns   | 6     |

Notes:

- The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output goes invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are set up (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/ $\overline{MCK}$  referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS. For the ADDR/CMD setup and hold specifications, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

- 4. t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register and is typically set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these two parameters are set to the same adjustment value. See the MPC8349EA PowerQUICC II Pro Integrated Host Processor Family Reference Manual for the timing modifications enabled by use of these bits.

- 5. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside the data eye at the pins of the microprocessor.

- 6. All outputs are referenced to the rising edge of MCK(n) at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

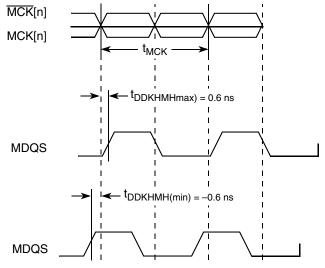

Figure 6 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

Figure 6. Timing Diagram for t<sub>DDKHMH</sub>

USB

# 9 USB

This section provides the AC and DC electrical specifications for the USB interface of the MPC8349EA.

## 9.1 USB DC Electrical Characteristics

Table 35 provides the DC electrical characteristics for the USB interface.

| Table 35 | . USB | DC | Electrical | Characteristics |

|----------|-------|----|------------|-----------------|

|----------|-------|----|------------|-----------------|

| Parameter                                          | Symbol          | Min                    | Max                    | Unit |

|----------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                           | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                            | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| Input current                                      | I <sub>IN</sub> | —                      | ±5                     | μA   |

| High-level output voltage, $I_{OH} = -100 \ \mu A$ | V <sub>OH</sub> | OV <sub>DD</sub> - 0.2 | _                      | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$   | V <sub>OL</sub> | —                      | 0.2                    | V    |

## 9.2 USB AC Electrical Specifications

Table 36 describes the general timing parameters of the USB interface of the MPC8349EA.

Table 36. USB General Timing Parameters (ULPI Mode Only)

| Parameter                              | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|----------------------------------------|---------------------|-----|-----|------|-------|

| USB clock cycle time                   | t <sub>USCK</sub>   | 15  | —   | ns   | 2–5   |

| Input setup to USB clock—all inputs    | t <sub>USIVKH</sub> | 4   | —   | ns   | 2–5   |

| Input hold to USB clock—all inputs     | t <sub>USIXKH</sub> | 1   | —   | ns   | 2–5   |

| USB clock to output valid—all outputs  | t <sub>USKHOV</sub> | —   | 7   | ns   | 2–5   |

| Output hold from USB clock—all outputs | t <sub>USKHOX</sub> | 2   | —   | ns   | 2–5   |

Notes:

The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>USIXKH</sub> symbolizes USB timing (US) for the input (I) to go invalid (X) with respect to the time the USB clock reference (K) goes high (H). Also, t<sub>USKHOX</sub> symbolizes USB timing (US) for the USB clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

2. All timings are in reference to USB clock.

3. All signals are measured from  $OV_{DD}/2$  of the rising edge of the USB clock to  $0.4 \times OV_{DD}$  of the signal in question for 3.3 V signaling levels.

4. Input timings are measured at the pin.

5. For active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to that of the leakage current specification.

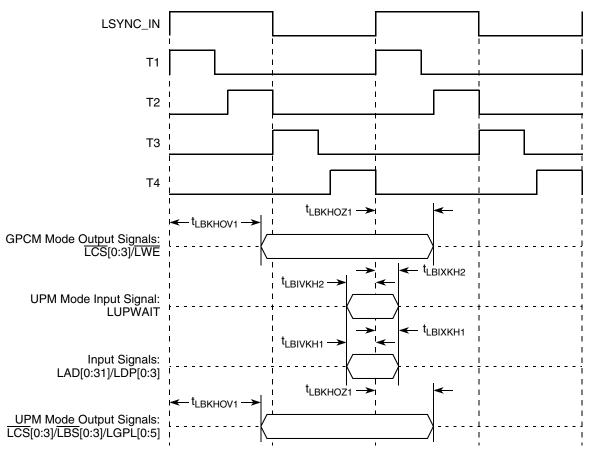

## 10.2 Local Bus AC Electrical Specification

Table 38 and Table 39 describe the general timing parameters of the local bus interface of the MPC8349EA.

| Parameter                                                   | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|-------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus cycle time                                        | t <sub>LBK</sub>     | 7.5 | —   | ns   | 2     |

| Input setup to local bus clock (except LUPWAIT)             | t <sub>LBIVKH1</sub> | 1.5 | —   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                      | t <sub>LBIVKH2</sub> | 2.2 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)            | t <sub>LBIXKH1</sub> | 1.0 | —   | ns   | 3, 4  |

| LUPWAIT Input hold from local bus clock                     | t <sub>LBIXKH2</sub> | 1.0 | —   | ns   | 3, 4  |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT1</sub> | 1.5 | —   | ns   | 5     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT2</sub> | 3   | —   | ns   | 6     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT3</sub> | 2.5 | —   | ns   | 7     |

| Local bus clock to LALE rise                                | t <sub>LBKHLR</sub>  | —   | 4.5 | ns   | _     |

| Local bus clock to output valid (except LAD/LDP and LALE)   | t <sub>LBKHOV1</sub> | —   | 4.5 | ns   | _     |

| Local bus clock to data valid for LAD/LDP                   | t <sub>LBKHOV2</sub> | —   | 4.5 | ns   | 3     |

| Local bus clock to address valid for LAD                    | t <sub>LBKHOV3</sub> | —   | 4.5 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)  | t <sub>LBKHOX1</sub> | 1   | —   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                | t <sub>LBKHOX2</sub> | 1   | —   | ns   | 3     |

| Local bus clock to output high impedance for LAD/LDP        | t <sub>LBKHOZ</sub>  | —   | 3.8 | ns   | 8     |

#### Notes:

The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to the rising edge of LSYNC\_IN.

- 3. All signals are measured from  $OV_{DD}/2$  of the rising edge of LSYNC\_IN to  $0.4 \times OV_{DD}$  of the signal in question for 3.3 V signaling levels.

- 4. Input timings are measured at the pin.

- 5. t<sub>LBOTOT1</sub> should be used when RCWH[LALE] is not set and when the load on the LALE output pin is at least 10 pF less than the load on the LAD output pins.

- 6. t<sub>LBOTOT2</sub> should be used when RCWH[LALE] is set and when the load on the LALE output pin is at least 10 pF less than the load on the LAD output pins.

- 7. t<sub>LBOTOT3</sub> should be used when RCWH[LALE] is set and when the load on the LALE output pin equals the load on the LAD output pins.

- 8. For active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to that of the leakage current specification.

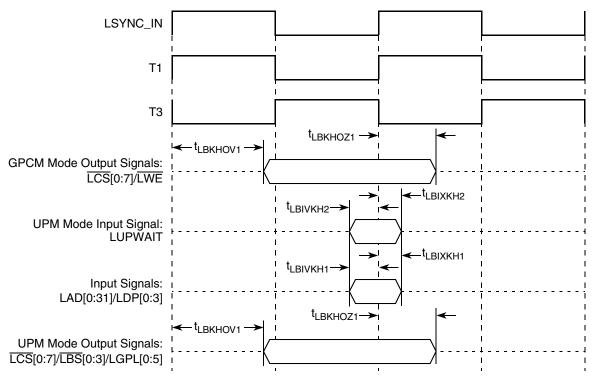

Figure 23. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 2 (DLL Enabled)

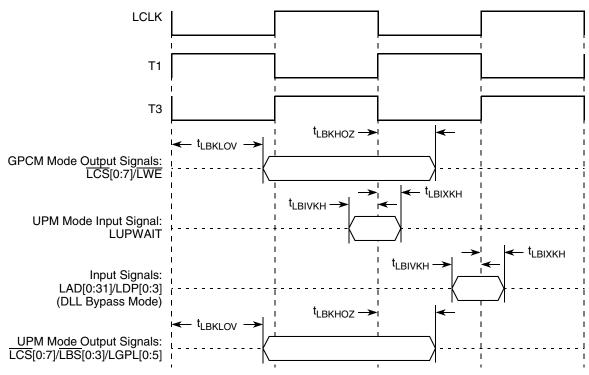

Figure 24. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 2 (DLL Bypass Mode)

Local Bus

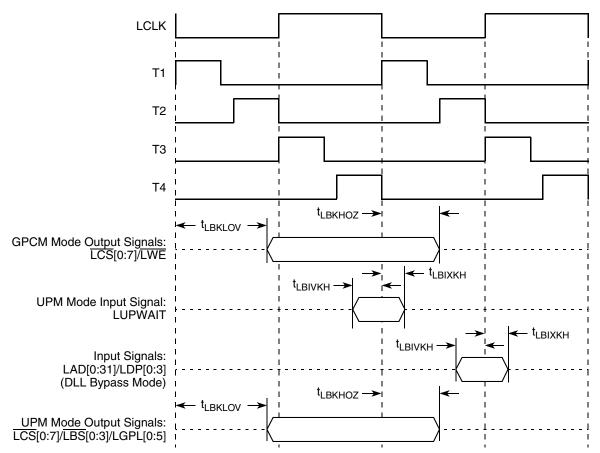

Figure 25. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (DLL Bypass Mode)

Figure 26. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (DLL Enabled)

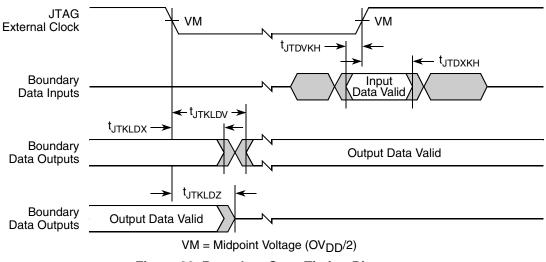

# 11 JTAG

This section describes the DC and AC electrical specifications for the IEEE Std. 1149.1 (JTAG) interface of the MPC8349EA.

## **11.1 JTAG DC Electrical Characteristics**

Table 40 provides the DC electrical characteristics for the IEEE Std. 1149.1 (JTAG) interface of the MPC8349EA.

| Table 40. JTAG Interface DC Electrical Characteristic | s |

|-------------------------------------------------------|---|

|-------------------------------------------------------|---|

| Parameter           | Symbol          | Condition                 | Min                    | Max                    | Unit |

|---------------------|-----------------|---------------------------|------------------------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> | —                         | OV <sub>DD</sub> - 0.3 | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                         | -0.3                   | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | —                         | —                      | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4                    | —                      | V    |

#### JTAG

| Parameter          | Symbol          | Condition                | Min | Мах | Unit |

|--------------------|-----------------|--------------------------|-----|-----|------|

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA | —   | 0.5 | V    |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA | —   | 0.4 | V    |

### Table 40. JTAG Interface DC Electrical Characteristics (continued)

## **11.2 JTAG AC Timing Specifications**

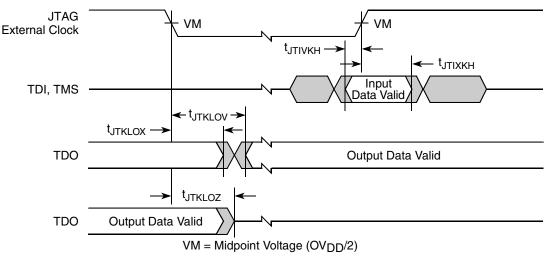

This section describes the AC electrical specifications for the IEEE Std. 1149.1 (JTAG) interface of the MPC8349EA. Table 41 provides the JTAG AC timing specifications as defined in Figure 28 through Figure 31.

## Table 41. JTAG AC Timing Specifications (Independent of CLKIN)<sup>1</sup>

At recommended operating conditions (see Table 2).

| Parameter                              |                                | Symbol <sup>2</sup>                        | Min      | Мах      | Unit | Notes |

|----------------------------------------|--------------------------------|--------------------------------------------|----------|----------|------|-------|

| JTAG external clock frequency of op    | eration                        | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  | —     |

| JTAG external clock cycle time         |                                | t <sub>JTG</sub>                           | 30       | —        | ns   | —     |

| JTAG external clock pulse width mea    | asured at 1.4 V                | t <sub>JTKHKL</sub>                        | 15       | _        | ns   | —     |

| JTAG external clock rise and fall time | es                             | t <sub>JTGR</sub> , t <sub>JTGF</sub>      | 0        | 2        | ns   | —     |

| TRST assert time                       |                                | t <sub>TRST</sub>                          | 25       | _        | ns   | 3     |

| Input setup times:                     | Boundary-scan data<br>TMS, TDI | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>4   | _<br>_   | ns   | 4     |

| Input hold times:                      | Boundary-scan data<br>TMS, TDI | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 10<br>10 |          | ns   | 4     |

| Valid times:                           | Boundary-scan data<br>TDO      | t <sub>jtkldv</sub><br>t <sub>jtklov</sub> | 2<br>2   | 11<br>11 | ns   | 5     |

| Output hold times:                     | Boundary-scan data<br>TDO      | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 2<br>2   |          | ns   | 5     |

JTAG

Figure 30 provides the boundary-scan timing diagram.

| Table 45. PCI AC Timing Specifications at 66 MHz <sup>1</sup> ( | (continued) |

|-----------------------------------------------------------------|-------------|

|-----------------------------------------------------------------|-------------|

| Parameter                  | Symbol <sup>2</sup> | Min | Max | Unit | Notes |

|----------------------------|---------------------|-----|-----|------|-------|

| PORESET to REQ64 hold time | t <sub>PCRHRX</sub> | 0   | 50  | ns   | 6     |

Notes:

- 1. PCI timing depends on M66EN and the ratio between PCI1/PCI2. Refer to the PCI chapter of the reference manual for a description of M66EN.

- 2. The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.</sub>

- 3. See the timing measurement conditions in the PCI 2.3 Local Bus Specifications.

- 4. For active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Input timings are measured at the pin.

- 6. The setup and hold time is with respect to the rising edge of PORESET.

### Table 46 provides the PCI AC timing specifications at 33 MHz.

#### Table 46. PCI AC Timing Specifications at 33 MHz

| Parameter                      | Symbol <sup>1</sup> | Min | Мах | Unit   | Notes |

|--------------------------------|---------------------|-----|-----|--------|-------|

| Clock to output valid          | <sup>t</sup> PCKHOV | —   | 11  | ns     | 2     |

| Output hold from clock         | <sup>t</sup> РСКНОХ | 2   | -   | ns     | 2     |

| Clock to output high impedance | <sup>t</sup> рскноz | —   | 14  | ns     | 2, 3  |

| Input setup to clock           | t <sub>PCIVKH</sub> | 3.0 | _   | ns     | 2, 4  |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0   | _   | ns     | 2, 4  |

| REQ64 to PORESET setup time    | t <sub>PCRVRH</sub> | 5   | _   | clocks | 5     |

| PORESET to REQ64 hold time     | t <sub>PCRHRX</sub> | 0   | 50  | ns     | 5     |

Notes:

2. See the timing measurement conditions in the PCI 2.3 Local Bus Specifications.

3. For active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

4. Input timings are measured at the pin.

5. The setup and hold time is with respect to the rising edge of PORESET.

The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

</sub>

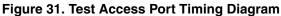

Figure 34 provides the AC test load for PCI.

Figure 34. PCI AC Test Load

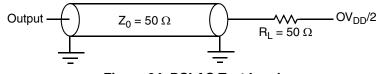

Figure 35 shows the PCI input AC timing diagram.

Figure 35. PCI Input AC Timing Diagram

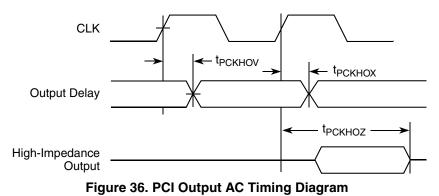

Figure 36 shows the PCI output AC timing diagram.

# 14 Timers

This section describes the DC and AC electrical specifications for the timers.

## 14.1 Timer DC Electrical Characteristics

Table 47 provides the DC electrical characteristics for the MPC8349EA timer pins, including TIN, TOUT, TGATE, and RTC\_CLK.

**Table 47. Timer DC Electrical Characteristics**

| Parameter           | Symbol          | Condition                 | Min  | Max                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> | —                         | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                         | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | —                         | _    | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | _                      | V    |

Package and Pin Listings

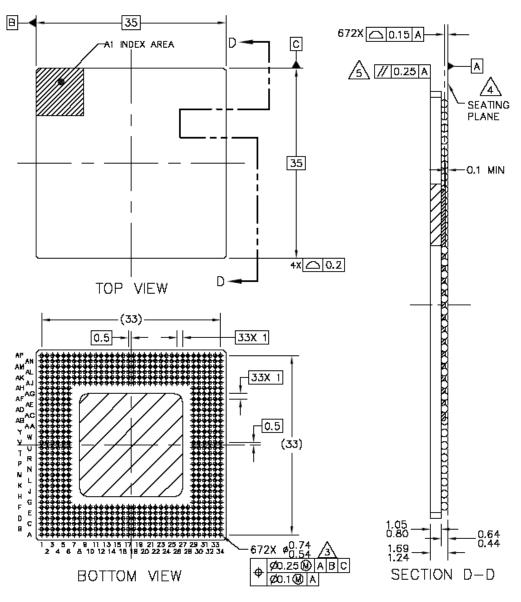

## 18.2 Mechanical Dimensions for the MPC8349EA TBGA

Figure 40 shows the mechanical dimensions and bottom surface nomenclature for the MPC8349EA, 672-TBGA package.

#### Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensions and tolerances per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement must exclude any effect of mark on top surface of package.

### Figure 40. Mechanical Dimensions and Bottom Surface Nomenclature for the MPC8349EA TBGA

Package and Pin Listings

|                    |                          | .g (,                                                            |                    | 1     |

|--------------------|--------------------------|------------------------------------------------------------------|--------------------|-------|

| Signal             | Package Pin Number       | Pin Type                                                         | Power<br>Supply    | Notes |

| TDO                | B20                      | 0                                                                | $OV_{DD}$          | 3     |

| TMS                | A20                      | I                                                                | $OV_{DD}$          | 4     |

| TRST               | B19                      | I                                                                | $OV_{DD}$          | 4     |

|                    | Test                     |                                                                  |                    |       |

| TEST               | D22                      | I                                                                | $OV_{DD}$          | 6     |

| TEST_SEL           | AL13                     | I                                                                | $OV_{DD}$          | 6     |

|                    | РМС                      |                                                                  |                    |       |

| QUIESCE            | A18                      | 0                                                                | $OV_{DD}$          | _     |

|                    | System Control           |                                                                  |                    | •     |

| PORESET            | C18                      | I                                                                | $OV_{DD}$          | _     |

| HRESET             | B18                      | I/O                                                              | $OV_{DD}$          | 1     |

| SRESET             | D18                      | I/O                                                              | $OV_{DD}$          | 2     |

|                    | Thermal Management       |                                                                  |                    | •     |

| THERM0             | K32                      | I                                                                | _                  | 8     |

|                    | Power and Ground Signals |                                                                  |                    |       |

| AV <sub>DD</sub> 1 | L31                      | Power for e300<br>PLL (1.2 V<br>nominal, 1.3 V<br>for 667 MHz)   | AV <sub>DD</sub> 1 | —     |

| AV <sub>DD</sub> 2 | AP12                     | Power for<br>system PLL (1.2<br>V nominal, 1.3 V<br>for 667 MHz) | AV <sub>DD</sub> 2 | _     |

| AV <sub>DD</sub> 3 | AE1                      | Power for DDR<br>DLL (1.2 V<br>nominal, 1.3 V<br>for 667 MHz)    | _                  | _     |

| AV <sub>DD</sub> 4 | AJ13                     | Power for LBIU<br>DLL (1.2 V<br>nominal, 1.3 V<br>for 667 MHz)   | AV <sub>DD</sub> 4 | —     |

## Table 55. MPC8349EA (TBGA) Pinout Listing (continued)

Clocking

# **19 Clocking**

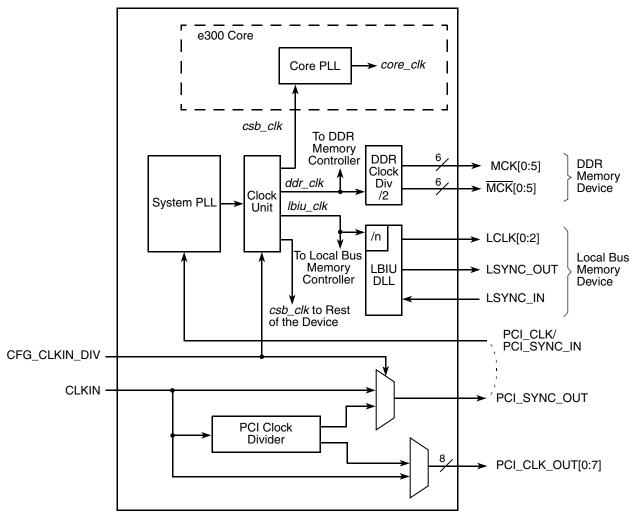

Figure 41 shows the internal distribution of the clocks.

Figure 41. MPC8349EA Clock Subsystem

The primary clock source can be one of two inputs, CLKIN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. When the MPC8349EA is configured as a PCI host device, CLKIN is its primary input clock. CLKIN feeds the PCI clock divider (÷2) and the multiplexors for PCI\_SYNC\_OUT and PCI\_CLK\_OUT. The CFG\_CLKIN\_DIV configuration input selects whether CLKIN or CLKIN/2 is driven out on the PCI\_SYNC\_OUT signal. The OCCR[PCICD*n*] parameters select whether CLKIN or CLKIN/2 is driven out on the PCI\_CLK\_OUT signal.

PCI\_SYNC\_OUT is connected externally to PCI\_SYNC\_IN to allow the internal clock subsystem to synchronize to the system PCI clocks. PCI\_SYNC\_OUT must be connected properly to PCI\_SYNC\_IN, with equal delay to all PCI agent devices in the system, to allow the MPC8349EA to function. When the device is configured as a PCI agent device, PCI\_CLK is the primary input clock and the CLKIN signal should be tied to GND.

## 22.1 Part Numbers Fully Addressed by This Document

Table 66 shows an analysis of the Freescale part numbering nomenclature for the MPC8349EA. The individual part numbers correspond to a maximum processor core frequency. Each part number also contains a revision code that refers to the die mask revision number. For available frequency configuration parts including extended temperatures, refer to the device product summary page on our website listed on the back cover of this document or, contact your local Freescale sales office.

| MPC             | nnnn               | е                                       | t                                                        | рр                            | aa                                                     | а                               | r                 |

|-----------------|--------------------|-----------------------------------------|----------------------------------------------------------|-------------------------------|--------------------------------------------------------|---------------------------------|-------------------|

| Product<br>Code | Part<br>Identifier | Encryption<br>Acceleration              | Temperature <sup>1</sup><br>Range                        | Package <sup>2</sup>          | Processor<br>Frequency <sup>3</sup>                    | Platform<br>Frequency           | Revision<br>Level |

| MPC             | 8349               | Blank = Not<br>included<br>E = included | Blank = 0 to $105^{\circ}C$<br>C = -40 to $105^{\circ}C$ | ZU =TBGA<br>VV = PB free TBGA | e300 core<br>speed<br>AG = 400<br>AJ = 533<br>AL = 667 | D = 266<br>F = 333 <sup>4</sup> | B = 3.1           |

### Table 66. Part Numbering Nomenclature

Notes:

1. For temperature range = C, processor frequency is limited to with a platform frequency of 266 and up to 533 with a platform frequency of 333

2. See Section 18, "Package and Pin Listings," for more information on available package types.

- Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by Part Number Specifications may support other maximum core frequencies.

- 4. ALF marked parts support DDR1 data rate up to 333 MHz (at 333 MHz CSB as the 'F' marking implies) and DDR2 data rate up to 400 MHz (at 200 MHz CSB). AJF marked parts support DDR1 and DDR2 data rate up to 333 MHz (at a CSB of 333 MHz).

Table 67 shows the SVR settings by device and package type.

#### Table 67. SVR Settings

| Device    | Package | SVR (Rev. 3.0) |

|-----------|---------|----------------|

| MPC8349EA | TBGA    | 8050_0030      |

| MPC8349A  | TBGA    | 8051_0030      |

**Document Revision History**

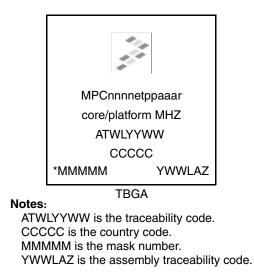

## 22.2 Part Marking

Parts are marked as in the example shown in Figure 44.

Figure 44. Freescale Part Marking for TBGA Devices

# 23 Document Revision History

This table provides a revision history of this document.

| Table 68. Docume | nt Revision History |

|------------------|---------------------|

|------------------|---------------------|

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13             | 09/2011 | <ul> <li>In Section 2.2, "Power Sequencing," added Section 2.2.1, "Power-Up Sequencing" and Figure 4.</li> <li>In Table 25, Table 29 and Table 31, removed the GTX_CLK125.</li> <li>In Table 34, updated t<sub>MDKHDX</sub> Max value from 170ns to 70ns.</li> </ul>                                                                                                                                                 |

| 12             | 11/2010 | <ul> <li>In Table 55 added note for pin LGPL4.</li> <li>In Section 21.7, "Pull-Up Resistor Requirements, updated the list of open drain type pins.</li> </ul>                                                                                                                                                                                                                                                        |

| 11             | 05/2010 | <ul> <li>In Table 25 through Table 30, changed V<sub>IL</sub>(min) to V<sub>IH</sub>(max) to (20%–80%).</li> <li>Added Table 8, "EC_GTX_CLK125 AC Timing Specifications."</li> </ul>                                                                                                                                                                                                                                 |

| 10             | 5/2009  | <ul> <li>In Table 57, updated frequency for max csb_clk to 333 MHz and DDR2, from 100-200 to 100-133 at core frequency = 533MHz.</li> <li>In Section 18.1, "Package Parameters for the MPC8349EA TBGA, changed solder ball for TBGA and PBGA from 95.5 Sn/0.5 Cu/4 Ag to 96.5 Sn/3.5 Ag.</li> <li>In Table 66, footnote 1, changed 667(TBGA) to 533(TBGA). footnote 4, added data rate for DDR1 and DDR2.</li> </ul> |

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9              | 2/2009  | <ul> <li>Added footnote 6 to Table 7.</li> <li>In Section 9.2, "USB AC Electrical Specifications," clarified that AC table is for ULPI only.</li> <li>In Table 39, corrected t<sub>LBKHOV</sub> parameter to t<sub>LBKLOV</sub> (output data is driven on falling edge of clock in DLL bypass mode). Similarly, made the same correction to Figure 22, Figure 24, and Figure 25 for output signals.</li> <li>Added footnote 11 to Table 55.</li> <li>Added footnote 4 to Table 66.</li> <li>In Section 21.1, "System Clocking," removed "(AVDD1)" and "(AVDD2") from bulleted list.</li> <li>In Section 21.2, "PLL Power Supply Filtering," in the second paragraph, changed "provide five independent filter circuits," and "the five AVDD pins" to provide four independent filter circuits," and "the four AVDD pins."</li> <li>In Table 57, corrected the max csb_clk to 266 MHz.</li> <li>In Table 62, added PLL configurations 903, 923, A03, A23, and 503 for 533 MHz</li> <li>In Table 66, updated note 1 to say the following: "For temperature range = C, processor frequency is limited to 533 with a platform frequency of 266."</li> </ul> |

| 8              | 4/2007  | <ul> <li>In Table 3, "Output Drive Capability," changed the values in the Output Impedance column and added USB to the seventh row.</li> <li>In Section 21.7, "Pull-Up Resistor Requirements,"deleted last two paragraphs and after first paragraph, added a new paragraph.</li> <li>Deleted Section 21.8, "JTAG Configuration Signals," and Figure 43, "JTAG Interface Connection."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7              | 3/2007  | <ul> <li>In Table 57, "Operating Frequencies for TBGA," in the 'Coherent system bus frequency (<i>csb_clk</i>)' row, changed the value in the 533 MHz column to 100-333.</li> <li>In Table 63, "Suggested PLL Configurations," under the subhead, '33 MHz CLKIN/PCI_CLK Options,' added row A03 between Ref. No. 724 and 804. Under the subhead '66 MHz CLKIN/PCI_CLK Options,' added row 503 between Ref. No. 305 and 404. For Ref. No. 306, changed the CORE PLL value to 0000110.</li> <li>In Section 23, "Ordering Information," replaced first paragraph and added a note.</li> <li>In Section 23.1, "Part Numbers Fully Addressed by this Document," replaced first paragraph.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6              | 2/2007  | <ul> <li>Page 1, updated first paragraph to reflect PowerQUICC II Pro information.</li> <li>In Table 18, "DDR and DDR2 SDRAM Input AC Timing Specifications," added note 2 to t<sub>CISKEW</sub> and deleted original note 3; renumbered the remaining notes.</li> <li>In Figure 41, "JTAG Interface Connection," updated with new figure.</li> <li>In Section 23.1, "Part Numbers Fully Addressed by This Document," replaced third sentence of first paragraph directing customer to product summary page for available frequency configuration parts.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5              | 1/2007  | <ul> <li>In Table 1, "Absolute Maximum Ratings," added (1.36 max for 667-MHz core frequency) to max V<sub>DD</sub> and Av<sub>DD</sub> values.</li> <li>In Table 2, "Recommended Operating Conditions," added a row showing nominal core supply voltage and PLL supply voltage of 1.3 V for 667-MHz parts.</li> <li>In Table 4, "MPC8349EA Power Dissipation," added two footnotes to 667-MHz row showing nominal core supply voltage and PLL supply voltage of 1.3 V for 667-MHz parts.</li> <li>In Table 54, "MPC83479EA (TBGA) Pinout Listing," updated V<sub>DD</sub> nd AV<sub>DD</sub> rows to show nominal core supply voltage and PLL supply voltage of 1.3 V for 667-MHz parts.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4              | 12/2006 | Table 19, "DDR and DDR2 SDRAM Output AC Timing Specifications," modified $T_{ddkhds}$ for 333 MHz from 900 ps to 775 ps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3              | 11/2006 | <ul> <li>Updated note in introduction.</li> <li>In the features list in Section 1, "Overview," updated DDR data rate to show 400 MHz for DDR2 for TBGA parts for silicon 3.x and 400 MHz for DDR2 for TBGA parts for silicon 3.x.</li> <li>In Section 23, "Ordering Information," replicated note from document introduction.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2              | 8/2006  | <ul> <li>Changed all references to revision 2.0 silicon to revision 3.0 silicon.</li> <li>Changed VIH minimum value in Table 40, "JTAG Interface DC Electrical Characteristics," to OV<sub>DD</sub> - 0.3.</li> <li>In Table 44, "PCI DC Electrical Characteristics," changed high-level input voltage values to min = 2 and max = OV<sub>DD</sub> + 0.3; changed low-level input voltage values to min = (-0.3) and max = 0.8.</li> <li>Updated DDR2 I/O power values in Table 5, "MPC8347EA Typical I/O Power Dissipation."</li> <li>In Table 66, "Suggested PLL Configurations," deleted reference-number rows 902 and 703.</li> </ul>                                                                                                                                                 |

| 1              | 4/2006  | <ul> <li>Removed Table 20, "Timing Parameters for DDR2-400."</li> <li>Changed ADDR/CMD to ADDR/CMD/MODT in Table 9, "DDR and DDR2 SDRAM Output AC Timing Specifications," rows 2 and 3, and in Figure 2, "DDR SDRAM Output Timing Diagram.</li> <li>Changed Min and Max values for V<sub>IH</sub> and VIL in Table 40Table 44,"PCI DC Electrical Characteristics."</li> <li>In Table 55, "MPC8349EA (TBGA) Pinout Listing," and Table 52, "MPC8347EA (PBGA) Pinout Listing," modified rows for MDICO and MDIC1 signals and added note 'It is recommended that MDICO be tied to GRD using an 18 Ω resistor and MCIC1 be tied to DDR power using an 18 Ω resistor.'</li> <li>Table 55, "MPC8349EA (TBGA) Pinout Listing," in row AVDD3 changed power supply from "AVDD3" to '—.'</li> </ul> |

| 0              | 3/2006  | Initial public release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

### Table 68. Document Revision History (continued)

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo and PowerQUICC are trademarks of Freescale Semiconductor, Inc. Reg. U.S. Pat. & Tm. Off. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2006–2011 Freescale Semiconductor, Inc.

Document Number: MPC8349EAEC Rev. 13 09/2011