#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Number of Cores/Bus Width Speed | 1 Core, 32-Bit                                                         |

|---------------------------------|------------------------------------------------------------------------|

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | -                                                                      |

| USB                             | USB 2.0 + PHY (2)                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 672-LBGA                                                               |

| Supplier Device Package         | 672-LBGA (35x35)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8349zuajfb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Double data rate, DDR1/DDR2 SDRAM memory controller

- Programmable timing supporting DDR1 and DDR2 SDRAM

- 32- or 64-bit data interface, up to 400 MHz data rate

- Up to four physical banks (chip selects), each bank up to 1 Gbyte independently addressable

- DRAM chip configurations from 64 Mbits to 1 Gbit with  $\times 8/\times 16$  data ports

- Full error checking and correction (ECC) support

- Support for up to 16 simultaneous open pages (up to 32 pages for DDR2)

- Contiguous or discontiguous memory mapping

- Read-modify-write support

- Sleep-mode support for SDRAM self refresh

- Auto refresh

- On-the-fly power management using CKE

- Registered DIMM support

- 2.5-V SSTL2 compatible I/O for DDR1, 1.8-V SSTL2 compatible I/O for DDR2

- Dual three-speed (10/100/1000) Ethernet controllers (TSECs)

- Dual controllers designed to comply with IEEE 802.3<sup>TM</sup>, 802.3u<sup>TM</sup>, 820.3x<sup>TM</sup>, 802.3z<sup>TM</sup>, 802.3ac<sup>TM</sup> standards

- Ethernet physical interfaces:

- 1000 Mbps IEEE Std. 802.3 GMII/RGMII, IEEE Std. 802.3z TBI/RTBI, full-duplex

- 10/100 Mbps IEEE Std. 802.3 MII full- and half-duplex

- Buffer descriptors are backward-compatible with MPC8260 and MPC860T 10/100 programming models

- 9.6-Kbyte jumbo frame support

- RMON statistics support

- Internal 2-Kbyte transmit and 2-Kbyte receive FIFOs per TSEC module

- MII management interface for control and status

- Programmable CRC generation and checking

- Dual PCI interfaces

- Designed to comply with PCI Specification Revision 2.3

- Data bus width options:

- Dual 32-bit data PCI interfaces operating at up to 66 MHz

- Single 64-bit data PCI interface operating at up to 66 MHz

- PCI 3.3-V compatible

- PCI host bridge capabilities on both interfaces

- PCI agent mode on PCI1 interface

- PCI-to-memory and memory-to-PCI streaming

- Memory prefetching of PCI read accesses and support for delayed read transactions

- Posting of processor-to-PCI and PCI-to-memory writes

### **Electrical Characteristics**

- Dual industry-standard I<sup>2</sup>C interfaces

- Two-wire interface

- Multiple master support

- Master or slave I<sup>2</sup>C mode support

- On-chip digital filtering rejects spikes on the bus

- System initialization data optionally loaded from I<sup>2</sup>C-1 EPROM by boot sequencer embedded hardware

- DMA controller

- Four independent virtual channels

- Concurrent execution across multiple channels with programmable bandwidth control

- Handshaking (external control) signals for all channels: DMA\_DREQ[0:3],

DMA\_DACK[0:3], DMA\_DDONE[0:3]

- All channels accessible to local core and remote PCI masters

- Misaligned transfer capability

- Data chaining and direct mode

- Interrupt on completed segment and chain

- DUART

- Two 4-wire interfaces (RxD, TxD, RTS, CTS)

- Programming model compatible with the original 16450 UART and the PC16550D

- Serial peripheral interface (SPI) for master or slave

- General-purpose parallel I/O (GPIO)

- 64 parallel I/O pins multiplexed on various chip interfaces

- System timers

- Periodic interrupt timer

- Real-time clock

- Software watchdog timer

- Eight general-purpose timers

- Designed to comply with IEEE Std. 1149.1<sup>TM</sup>, JTAG boundary scan

- Integrated PCI bus and SDRAM clock generation

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8349EA. The device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

# 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

## 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

| Table 1. Absolute Maximum Ratings | s <sup>1</sup> |

|-----------------------------------|----------------|

|-----------------------------------|----------------|

|                                                  | Parameter                                                                                        | Symbol            | Max Value                                                | Unit | Notes |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------|------|-------|

| Core supply voltage                              |                                                                                                  | V <sub>DD</sub>   | –0.3 to 1.32 (1.36 max<br>for 667-MHz core<br>frequency) | V    | _     |

| PLL supply voltage                               | y voltage                                                                                        |                   | -0.3 to 1.32 (1.36 max<br>for 667-MHz core<br>frequency) | V    | —     |

| DDR and DDR2 DRAM I/O voltage                    |                                                                                                  | GV <sub>DD</sub>  | -0.3 to 2.75<br>-0.3 to 1.98                             | V    | —     |

| Three-speed Ethernet I/O, MII management voltage |                                                                                                  | LV <sub>DD</sub>  | -0.3 to 3.63                                             | V    | —     |

| PCI, local bus, DUA and JTAG I/O voltag          | RT, system control and power management, I <sup>2</sup> C, le                                    | OV <sub>DD</sub>  | -0.3 to 3.63                                             | V    | —     |

| Input voltage                                    | DDR DRAM signals                                                                                 | MV <sub>IN</sub>  | –0.3 to (GV <sub>DD</sub> + 0.3)                         | V    | 2, 5  |

|                                                  | DDR DRAM reference                                                                               | MV <sub>REF</sub> | –0.3 to (GV <sub>DD</sub> + 0.3)                         | V    | 2, 5  |

|                                                  | Three-speed Ethernet signals                                                                     | LV <sub>IN</sub>  | -0.3 to (LV <sub>DD</sub> + 0.3)                         | V    | 4, 5  |

|                                                  | Local bus, DUART, CLKIN, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>  | -0.3 to (OV <sub>DD</sub> + 0.3)                         | V    | 3, 5  |

|                                                  | PCI                                                                                              | OV <sub>IN</sub>  | -0.3 to (OV <sub>DD</sub> + 0.3)                         | V    | 6     |

| Storage temperature range                        |                                                                                                  | T <sub>STG</sub>  | -55 to 150                                               | °C   | —     |

Notes:

<sup>1</sup> Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- <sup>2</sup> Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit can be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- <sup>3</sup> **Caution:** OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit can be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- <sup>4</sup> **Caution:** LV<sub>IN</sub> must not exceed LV<sub>DD</sub> by more than 0.3 V. This limit can be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

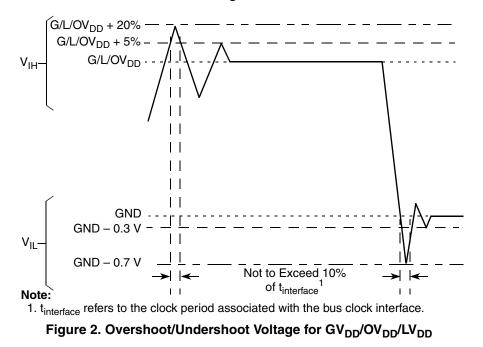

- <sup>5</sup> (M,L,O)V<sub>IN</sub> and MV<sub>REF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

- 6 OVIN on the PCI interface can overshoot/undershoot according to the PCI Electrical Specification for 3.3-V operation, as shown in Figure 3.

Electrical Characteristics

## 2.1.2 Power Supply Voltage Specification

Table 2 provides the recommended operating conditions for the MPC8349EA. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

| Parameter                                                                                          | Symbol            | Recommended<br>Value             | Unit | Notes |

|----------------------------------------------------------------------------------------------------|-------------------|----------------------------------|------|-------|

| Core supply voltage for 667-MHz core frequency                                                     | V <sub>DD</sub>   | 1.3 V ± 60 mV                    | V    | 1     |

| Core supply voltage                                                                                | V <sub>DD</sub>   | 1.2 V ± 60 mV                    | V    | 1     |

| PLL supply voltage for 667-MHz core frequency                                                      | AV <sub>DD</sub>  | 1.3 V ± 60 mV                    | V    | 1     |

| PLL supply voltage                                                                                 | AV <sub>DD</sub>  | 1.2 V ± 60 mV                    | V    | 1     |

| DDR and DDR2 DRAM I/O voltage                                                                      | GV <sub>DD</sub>  | 2.5 V ± 125 mV<br>1.8 V ± 90 mV  | V    | _     |

| Three-speed Ethernet I/O supply voltage                                                            | LV <sub>DD1</sub> | 3.3 V ± 330 mV<br>2.5 V ± 125 mV | V    | _     |

| Three-speed Ethernet I/O supply voltage                                                            | LV <sub>DD2</sub> | 3.3 V ± 330 mV<br>2.5 V ± 125 mV | V    | _     |

| PCI, local bus, DUART, system control and power management, I <sup>2</sup> C, and JTAG I/O voltage | OV <sub>DD</sub>  | 3.3 V ± 330 mV                   | V    | _     |

| Table 2. Recommended | Operating Conditions |

|----------------------|----------------------|

|----------------------|----------------------|

Note:

<sup>1</sup> GV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8349EA.

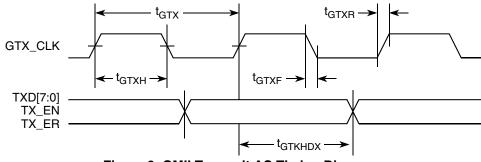

## 8.2.1.1 GMII Transmit AC Timing Specifications

Table 25 provides the GMII transmit AC timing specifications.

### Table 25. GMII Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                               | Symbol <sup>1</sup>                 | Min   | Тур | Max   | Unit |

|---------------------------------------------------|-------------------------------------|-------|-----|-------|------|

| GTX_CLK clock period                              | t <sub>GTX</sub>                    | _     | 8.0 | _     | ns   |

| GTX_CLK duty cycle                                | t <sub>GTXH</sub> /t <sub>GTX</sub> | 43.75 |     | 56.25 | %    |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay | t <sub>GTKHDX</sub>                 | 0.5   |     | 5.0   | ns   |

| GTX_CLK clock rise time (20%-80%)                 | t <sub>GTXR</sub>                   | _     |     | 1.0   | ns   |

| GTX_CLK clock fall time (80%–20%)                 | t <sub>GTXF</sub>                   | _     |     | 1.0   | ns   |

### Notes:

1. The symbols for timing specifications follow the pattern t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the high state (H) relative to the time date input signals (D) reaching the clock reference (K) going to the high state (H) relative to the time date input signals (D) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. In general, the clock reference symbol is based on three letters representing the clock of a particular function. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

### Figure 9 shows the GMII transmit AC timing diagram.

Figure 9. GMII Transmit AC Timing Diagram

## 8.2.1.2 GMII Receive AC Timing Specifications

Table 26 provides the GMII receive AC timing specifications.

### Table 26. GMII Receive AC Timing Specifications

At recommended operating conditions with LV\_DD/OV\_DD of 3.3 V  $\pm$  10%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | _   | 8.0 | _   | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | _   | 60  | %    |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | _   | _   | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0.5 | _   | _   | ns   |

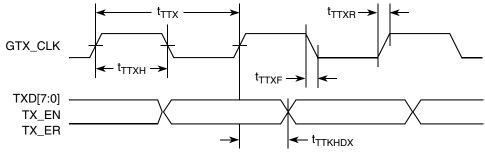

## 8.2.3.1 TBI Transmit AC Timing Specifications

Table 29 provides the TBI transmit AC timing specifications.

### Table 29. TBI Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                              | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|--------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| GTX_CLK clock period                             | t <sub>TTX</sub>                    | —   | 8.0 | —   | ns   |

| GTX_CLK duty cycle                               | t <sub>TTXH</sub> /t <sub>TTX</sub> | 40  | _   | 60  | %    |

| GTX_CLK to TBI data TXD[7:0], TX_ER, TX_EN delay | t <sub>TTKHDX</sub>                 | 1.0 | _   | 5.0 | ns   |

| GTX_CLK clock rise (20%–80%)                     | t <sub>TTXR</sub>                   | _   | _   | 1.0 | ns   |

| GTX_CLK clock fall time (80%–20%)                | t <sub>TTXF</sub>                   | —   |     | 1.0 | ns   |

### Notes:

1. The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the invalid state (X) or hold time. In general, the clock reference symbol is based on three letters representing the clock of a particular function. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

### Figure 14 shows the TBI transmit AC timing diagram.

Figure 14. TBI Transmit AC Timing Diagram

## 8.2.3.2 TBI Receive AC Timing Specifications

Table 30 provides the TBI receive AC timing specifications.

### Table 30. TBI Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition     | Symbol <sup>1</sup>                 | Min | Тур  | Max | Unit |

|-------------------------|-------------------------------------|-----|------|-----|------|

| PMA_RX_CLK clock period | t <sub>TRX</sub>                    |     | 16.0 |     | ns   |

| PMA_RX_CLK skew         | t <sub>SKTRX</sub>                  | 7.5 |      | 8.5 | ns   |

| RX_CLK duty cycle       | t <sub>TRXH</sub> /t <sub>TRX</sub> | 40  |      | 60  | %    |

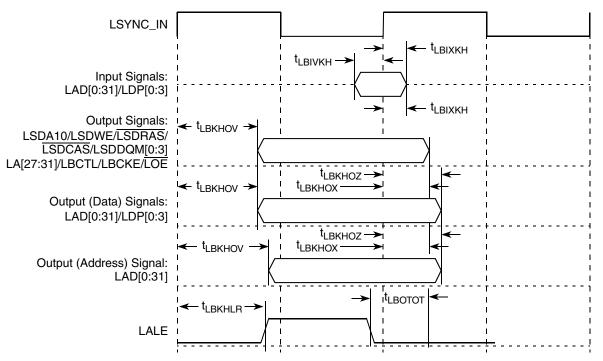

#### Local Bus

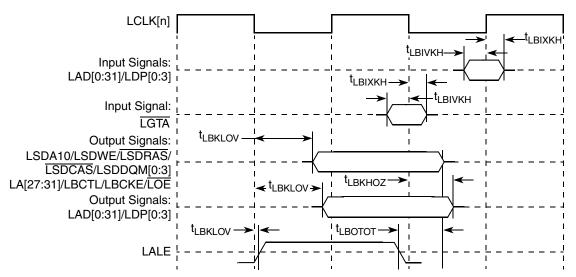

Figure 21 through Figure 26 show the local bus signals.

Figure 21. Local Bus Signals, Nonspecial Signals Only (DLL Enabled)

Figure 22. Local Bus Signals, Nonspecial Signals Only (DLL Bypass Mode)

### Table 41. JTAG AC Timing Specifications (Independent of CLKIN)<sup>1</sup> (continued)

At recommended operating conditions (see Table 2).

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min    | Мах     | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|--------|---------|------|-------|

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 2<br>2 | 19<br>9 | ns   | 5, 6  |

Notes:

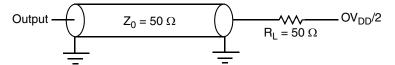

1. All outputs are measured from the midpoint voltage of the falling/rising edge of  $t_{TCLK}$  to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50  $\Omega$  load (see Figure 18). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

2. The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. In general, the clock reference symbol is based on three letters representing the clock of a particular function. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

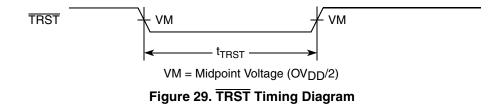

3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

6. Guaranteed by design and characterization.

Figure 27 provides the AC test load for TDO and the boundary-scan outputs of the MPC8349EA.

Figure 27. AC Test Load for the JTAG Interface

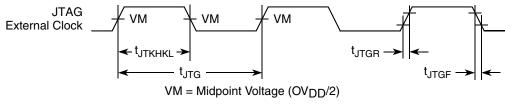

Figure 28 provides the JTAG clock input timing diagram.

Figure 28. JTAG Clock Input Timing Diagram

Figure 29 provides the  $\overline{\text{TRST}}$  timing diagram.

# 13 PCI

This section describes the DC and AC electrical specifications for the PCI bus of the MPC8349EA.

# **13.1 PCI DC Electrical Characteristics**

Table 44 provides the DC electrical characteristics for the PCI interface of the MPC8349EA.

| Parameter                 | Symbol          | Test Condition                                       | Min                    | Мах                    | Unit |

|---------------------------|-----------------|------------------------------------------------------|------------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or                        | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage   | V <sub>IL</sub> | $V_{OUT} \le V_{OL}$ (max)                           | -0.3                   | 0.8                    | V    |

| Input current             | I <sub>IN</sub> | $V_{IN}^{1} = 0 V \text{ or } V_{IN} = OV_{DD}$      | _                      | ±5                     | μA   |

| High-level output voltage | V <sub>OH</sub> | OV <sub>DD</sub> = min,<br>I <sub>OH</sub> = −100 μA | OV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage  | V <sub>OL</sub> | OV <sub>DD</sub> = min,<br>I <sub>OL</sub> = 100 μA  |                        | 0.2                    | V    |

**Table 44. PCI DC Electrical Characteristics**

Note:

1. The symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1.

# 13.2 PCI AC Electrical Specifications

This section describes the general AC timing parameters of the PCI bus of the MPC8349EA. Note that the PCI\_CLK or PCI\_SYNC\_IN signal is used as the PCI input clock depending on whether the device is configured as a host or agent device. Table 45 provides the PCI AC timing specifications at 66 MHz.

| Parameter                      | Symbol <sup>2</sup> | Min | Max | Unit   | Notes |

|--------------------------------|---------------------|-----|-----|--------|-------|

| Clock to output valid          | <sup>t</sup> PCKHOV | —   | 6.0 | ns     | 3     |

| Output hold from clock         | <sup>t</sup> РСКНОХ | 1   | _   | ns     | 3     |

| Clock to output high impedance | t <sub>PCKHOZ</sub> | —   | 14  | ns     | 3, 4  |

| Input setup to clock           | t <sub>PCIVKH</sub> | 3.0 | _   | ns     | 3, 5  |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0   | _   | ns     | 3, 5  |

| REQ64 to PORESET setup time    | t <sub>PCRVRH</sub> | 5   | —   | clocks | 6     |

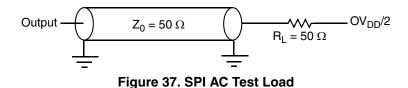

Figure 37 provides the AC test load for the SPI.

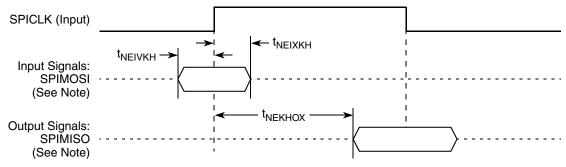

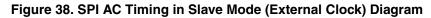

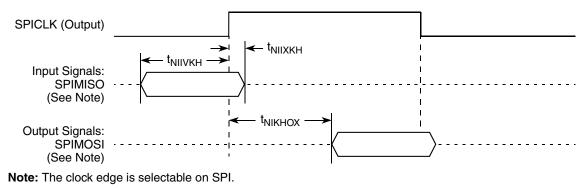

Figure 38 and Figure 39 represent the AC timings from Table 54. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

Figure 38 shows the SPI timings in slave mode (external clock).

Note: The clock edge is selectable on SPI.

Figure 39 shows the SPI timings in master mode (internal clock).

Figure 39. SPI AC Timing in Master Mode (Internal Clock) Diagram

# **18 Package and Pin Listings**

This section details package parameters, pin assignments, and dimensions. The MPC8349EA is available in a tape ball grid array (TBGA). See Section 18.1, "Package Parameters for the MPC8349EA TBGA" and Section 18.2, "Mechanical Dimensions for the MPC8349EA TBGA.

Package and Pin Listings

| Signal                    | Package Pin Number                                                                                                                                                                                                                                                                                                  | Pin Type | Power<br>Supply      | Notes |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|-------|

| PCI2_FRAME/GPIO2[1]       | AE33                                                                                                                                                                                                                                                                                                                | I/O      | I/O OV <sub>DD</sub> |       |

| PCI2_TRDY/GPIO2[2]        | AF32                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub>     | 5     |

| PCI2_IRDY/GPIO2[3]        | AE34                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub>     | 5     |

| PCI2_STOP/GPIO2[4]        | AF34                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub>     | 5     |

| PCI2_DEVSEL/GPIO2[5]      | AF33                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub>     | 5     |

| PCI2_SERR/PCI1_ACK64      | AG33                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub>     | 5     |

| PCI2_PERR/PCI1_REQ64      | AG32                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub>     | 5     |

| PCI2_REQ[0:2]/GPIO2[6:8]  | Y32, Y34, AA32                                                                                                                                                                                                                                                                                                      | I/O      | OV <sub>DD</sub>     |       |

| PCI2_GNT[0:2]/GPIO2[9:11] | Y31, Y33, AA31                                                                                                                                                                                                                                                                                                      | I/O      | OV <sub>DD</sub>     | —     |

| M66EN                     | A19                                                                                                                                                                                                                                                                                                                 | I        | OV <sub>DD</sub>     | —     |

|                           | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                          |          |                      |       |

| MDQ[0:63]                 | D5, A3, C3, D3, C4, B3, C2, D4, D2, E5,<br>G2, H6, E4, F3, G4, G3, H1, J2, L6, M6,<br>H2, K6, L2, M4, N2, P4, R2, T4, P6, P3,<br>R1, T2, AB5, AA3, AD6, AE4, AB4, AC2,<br>AD3, AE6, AE3, AG4, AK5, AK4, AE2,<br>AG6, AK3, AK2, AL2, AL1, AM5, AP5,<br>AM2, AN1, AP4, AN5, AJ7, AN7, AM8,<br>AJ9, AP6, AL7, AL9, AN8 | I/O      | GV <sub>DD</sub>     | _     |

| MECC[0:4]/MSRCID[0:4]     | W4, W3, Y3, AA6, T1                                                                                                                                                                                                                                                                                                 | I/O      | GV <sub>DD</sub>     | —     |

| MECC[5]/MDVAL             | U1                                                                                                                                                                                                                                                                                                                  | I/O      | GV <sub>DD</sub>     | —     |

| MECC[6:7]                 | Y1, Y6                                                                                                                                                                                                                                                                                                              | I/O      | GV <sub>DD</sub>     | —     |

| MDM[0:8]                  | B1, F1, K1, R4, AD4, AJ1, AP3, AP7, Y4                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>     | —     |

| MDQS[0:8]                 | B2, F5, J1, P2, AC1, AJ2, AN4, AL8, W2                                                                                                                                                                                                                                                                              | I/O      | GV <sub>DD</sub>     | —     |

| MBA[0:1]                  | AD1, AA5                                                                                                                                                                                                                                                                                                            | 0        | GV <sub>DD</sub>     | —     |

| MA[0:14]                  | W1, U4, T3, R3, P1, M1, N1, L3, L1, K2,<br>Y2, K3, J3, AP2, AN6                                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub>     | —     |

| MWE                       | AF1                                                                                                                                                                                                                                                                                                                 | 0        | GV <sub>DD</sub>     | —     |

| MRAS                      | AF4                                                                                                                                                                                                                                                                                                                 | 0        | GV <sub>DD</sub>     | —     |

| MCAS                      | AG3                                                                                                                                                                                                                                                                                                                 | 0        | GV <sub>DD</sub>     | —     |

| MCS[0:3]                  | AG2, AG1, AK1, AL4                                                                                                                                                                                                                                                                                                  | 0        | GV <sub>DD</sub>     | _     |

| MCKE[0:1]                 | H3, G1                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>     | 3     |

| MCK[0:5]                  | U2, F4, AM3, V3, F2, AN3                                                                                                                                                                                                                                                                                            | 0        | GV <sub>DD</sub>     | _     |

| MCK[0:5]                  | U3, E3, AN2, V4, E1, AM4                                                                                                                                                                                                                                                                                            | 0        | GV <sub>DD</sub>     | _     |

| MODT[0:3]                 | AH3, AJ5, AH1, AJ4                                                                                                                                                                                                                                                                                                  | 0        | GV <sub>DD</sub>     |       |

### Table 55. MPC8349EA (TBGA) Pinout Listing (continued)

| Signal                                         | Package Pin Number                                                                                                                                                                                            | Pin Type | Power<br>Supply  | Notes |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| MBA[2]                                         | H4                                                                                                                                                                                                            | 0        | GV <sub>DD</sub> |       |

| MDICO                                          | AB1                                                                                                                                                                                                           | I/O      | —                | 9     |

| MDIC1                                          | AA1                                                                                                                                                                                                           | I/O      | —                | 9     |

|                                                | Local Bus Controller Interface                                                                                                                                                                                |          |                  |       |

| LAD[0:31]                                      | AM13, AP13, AL14, AM14, AN14, AP14,<br>AK15, AJ15, AM15, AN15, AP15, AM16,<br>AL16, AN16, AP16, AL17, AM17, AP17,<br>AK17, AP18, AL18, AM18, AN18, AP19,<br>AN19, AM19, AP20, AK19, AN20, AL20,<br>AP21, AN21 | I/O      | OV <sub>DD</sub> | _     |

| LDP[0]/CKSTOP_OUT                              | AM21                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | —     |

| LDP[1]/CKSTOP_IN                               | AP22                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | —     |

| LDP[2]/LCS[4]                                  | AN22                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | —     |

| LDP[3]/LCS[5]                                  | AM22                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | —     |

| LA[27:31]                                      | AK21, AP23, AN23, AP24, AK22                                                                                                                                                                                  | 0        | OV <sub>DD</sub> | —     |

| LCS[0:3]                                       | AN24, AL23, AP25, AN25                                                                                                                                                                                        | 0        | OV <sub>DD</sub> | _     |

| LWE[0:3]/LSDDQM[0:3]/LBS[0:3]                  | AK23, AP26, AL24, AM25                                                                                                                                                                                        | 0        | OV <sub>DD</sub> | _     |

| LBCTL                                          | AN26                                                                                                                                                                                                          | 0        | OV <sub>DD</sub> | _     |

| LALE                                           | AK24                                                                                                                                                                                                          | 0        | OV <sub>DD</sub> | _     |

| LGPL0/LSDA10/cfg_reset_source0                 | AP27                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | —     |

| LGPL1/LSDWE/cfg_reset_source1                  | AL25                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | —     |

| LGPL2/LSDRAS/LOE                               | AJ24                                                                                                                                                                                                          | 0        | OV <sub>DD</sub> | —     |

| LGPL3/LSDCAS/cfg_reset_source2                 | AN27                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | _     |

| LGPL4/LGTA/LUPWAIT/LPBSE                       | AP28                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 12    |

| LGPL5/cfg_clkin_div                            | AL26                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | —     |

| LCKE                                           | AM27                                                                                                                                                                                                          | 0        | OV <sub>DD</sub> | —     |

| LCLK[0:2]                                      | AN28, AK26, AP29                                                                                                                                                                                              | 0        | OV <sub>DD</sub> | _     |

| LSYNC_OUT                                      | AM12                                                                                                                                                                                                          | 0        | OV <sub>DD</sub> | _     |

| LSYNC_IN                                       | AJ10                                                                                                                                                                                                          | I        | OV <sub>DD</sub> |       |

|                                                | General Purpose I/O Timers                                                                                                                                                                                    |          |                  | 1     |

| GPIO1[0]/DMA_DREQ0/GTM1_TIN1/<br>GTM2_TIN2     | F24                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | -     |

| GPIO1[1]/DMA_DACK0/<br>GTM1_TGATE1/GTM2_TGATE2 | E24                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | —     |

### Table 55. MPC8349EA (TBGA) Pinout Listing (continued)

| Signal                                     | Package Pin Number         | Pin Type | Power<br>Supply   | Notes |

|--------------------------------------------|----------------------------|----------|-------------------|-------|

| TSEC2_TX_ER/GPIO1[24]                      | F14                        | I/O      | OV <sub>DD</sub>  | —     |

| TSEC2_TX_EN/GPIO1[12]                      | C5                         | I/O      | LV <sub>DD2</sub> | —     |

| TSEC2_TX_CLK/GPIO1[30]                     | E14                        | I/O      | OV <sub>DD</sub>  | —     |

|                                            | DUART                      |          |                   |       |

| UART_SOUT[1:2]/MSRCID[0:1]/<br>LSRCID[0:1] | AK27, AN29                 | 0        | OV <sub>DD</sub>  | —     |

| UART_SIN[1:2]/MSRCID[2:3]/<br>LSRCID[2:3]  | AL28, AM29                 | I/O      | OV <sub>DD</sub>  | —     |

| UART_CTS[1]/MSRCID4/LSRCID4                | AP30                       | I/O      | OV <sub>DD</sub>  | —     |

| UART_CTS[2]/MDVAL/ LDVAL                   | AN30                       | I/O      | OV <sub>DD</sub>  | —     |

| UART_RTS[1:2]                              | AP31, AM30                 | 0        | OV <sub>DD</sub>  | —     |

|                                            | I <sup>2</sup> C interface |          | •                 |       |

| IIC1_SDA                                   | AK29                       | I/O      | OV <sub>DD</sub>  | 2     |

| IIC1_SCL                                   | AP32                       | I/O      | OV <sub>DD</sub>  | 2     |

| IIC2_SDA                                   | AN31                       | I/O      | OV <sub>DD</sub>  | 2     |

| IIC2_SCL                                   | AM31                       | I/O      | OV <sub>DD</sub>  | 2     |

|                                            | SPI                        |          |                   |       |

| SPIMOSI/LCS[6]                             | AN32                       | I/O      | OV <sub>DD</sub>  | _     |

| SPIMISO/LCS[7]                             | AP33                       | I/O      | OV <sub>DD</sub>  | —     |

| SPICLK                                     | AK30                       | I/O      | OV <sub>DD</sub>  | —     |

| SPISEL                                     | AL31                       | I        | OV <sub>DD</sub>  | —     |

|                                            | Clocks                     |          |                   |       |

| PCI_CLK_OUT[0:2]                           | AN9, AP9, AM10,            | 0        | OV <sub>DD</sub>  | _     |

| PCI_CLK_OUT[3]/LCS[6]                      | AN10                       | 0        | OV <sub>DD</sub>  | —     |

| PCI_CLK_OUT[4]/LCS[7]                      | AJ11                       | 0        | OV <sub>DD</sub>  | —     |

| PCI_CLK_OUT[5:7]                           | AP10, AL11, AM11           | 0        | OV <sub>DD</sub>  | —     |

| PCI_SYNC_IN/PCI_CLOCK                      | AK12                       | I        | OV <sub>DD</sub>  | —     |

| PCI_SYNC_OUT                               | AP11                       | 0        | OV <sub>DD</sub>  | 3     |

| RTC/PIT_CLOCK                              | AM32                       | I        | OV <sub>DD</sub>  | —     |

| CLKIN                                      | AM9                        | I        | OV <sub>DD</sub>  | —     |

|                                            | JTAG                       |          | •                 |       |

| ТСК                                        | E20                        | I        | OV <sub>DD</sub>  |       |

| TDI                                        | F20                        | I        | OV <sub>DD</sub>  | 4     |

Clocking

# **19 Clocking**

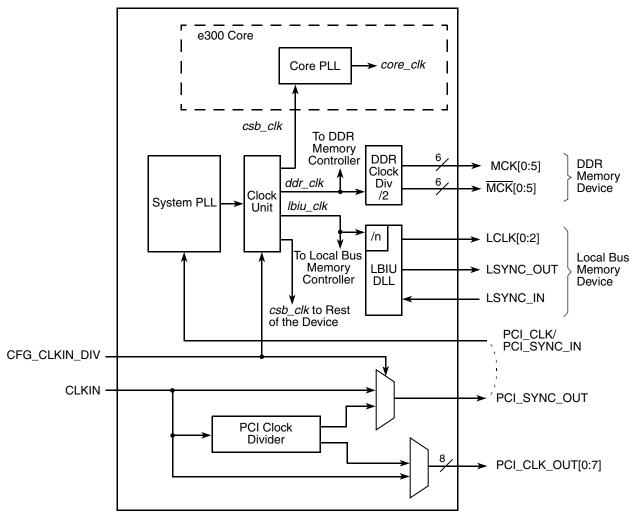

Figure 41 shows the internal distribution of the clocks.

Figure 41. MPC8349EA Clock Subsystem

The primary clock source can be one of two inputs, CLKIN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. When the MPC8349EA is configured as a PCI host device, CLKIN is its primary input clock. CLKIN feeds the PCI clock divider (÷2) and the multiplexors for PCI\_SYNC\_OUT and PCI\_CLK\_OUT. The CFG\_CLKIN\_DIV configuration input selects whether CLKIN or CLKIN/2 is driven out on the PCI\_SYNC\_OUT signal. The OCCR[PCICD*n*] parameters select whether CLKIN or CLKIN/2 is driven out on the PCI\_CLK\_OUT signal.

PCI\_SYNC\_OUT is connected externally to PCI\_SYNC\_IN to allow the internal clock subsystem to synchronize to the system PCI clocks. PCI\_SYNC\_OUT must be connected properly to PCI\_SYNC\_IN, with equal delay to all PCI agent devices in the system, to allow the MPC8349EA to function. When the device is configured as a PCI agent device, PCI\_CLK is the primary input clock and the CLKIN signal should be tied to GND.

| RCWL[SPMF] | System PLL Multiplication Factor |

|------------|----------------------------------|

| 0111       | × 7                              |

| 1000       | × 8                              |

| 1001       | × 9                              |

| 1010       | × 10                             |

| 1011       | × 11                             |

| 1100       | × 12                             |

| 1101       | × 13                             |

| 1110       | × 14                             |

| 1111       | × 15                             |

| Table 58. System | <b>PLL Multiplication</b> | Factors (continued) |

|------------------|---------------------------|---------------------|

|------------------|---------------------------|---------------------|

As described in Section 19, "Clocking," the LBIUCM, DDRCM, and SPMF parameters in the reset configuration word low and the CFG\_CLKIN\_DIV configuration input signal select the ratio between the primary clock input (CLKIN or PCI\_CLK) and the internal coherent system bus clock (*csb\_clk*). Table 59 and Table 60 show the expected frequency values for the CSB frequency for select *csb\_clk* to CLKIN/PCI\_SYNC\_IN ratios.

|                                             |                                                    |                                                                 | In | ) <sup>2</sup>          |       |     |  |  |

|---------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------|----|-------------------------|-------|-----|--|--|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> SPMF | <i>csb_clk</i> :<br>Input Clock Ratio <sup>2</sup> | <i>csb_clk</i> :<br>put Clock Ratio <sup>2</sup> 16.67 25 33.33 |    | 33.33                   | 66.67 |     |  |  |

|                                             |                                                    |                                                                 |    | csb_clk Frequency (MHz) |       |     |  |  |

| Low                                         | 0010                                               | 2 : 1                                                           |    |                         |       | 133 |  |  |

| Low                                         | 0011                                               | 3 : 1                                                           |    |                         | 100   | 200 |  |  |

| Low                                         | 0100                                               | 4 : 1                                                           |    | 100                     | 133   | 266 |  |  |

| Low                                         | 0101                                               | 5 : 1                                                           |    | 125                     | 166   | 333 |  |  |

Table 59. CSB Frequency Options for Host Mode

|                                        |      |                                                    | li    | nput Clock Fre      | equency (MHz | ) <sup>2</sup> |

|----------------------------------------|------|----------------------------------------------------|-------|---------------------|--------------|----------------|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> | SPMF | <i>csb_clk</i> :<br>Input Clock Ratio <sup>2</sup> | 16.67 | 25                  | 33.33        | 66.67          |

|                                        |      |                                                    |       | <i>csb_clk</i> Freq | uency (MHz)  |                |

| Low                                    | 0110 | 6 : 1                                              | 100   | 150                 | 200          |                |

| Low                                    | 0111 | 7 : 1                                              | 116   | 175                 | 233          |                |

| Low                                    | 1000 | 8 : 1                                              | 133   | 200                 | 266          |                |

| Low                                    | 1001 | 9 : 1                                              | 150   | 225                 | 300          |                |

| Low                                    | 1010 | 10 : 1                                             | 166   | 250                 | 333          |                |

| Low                                    | 1011 | 11 : 1                                             | 183   | 275                 |              |                |

| Low                                    | 1100 | 12 : 1                                             | 200   | 300                 |              |                |

| Low                                    | 1101 | 13 : 1                                             | 216   | 325                 |              |                |

| Low                                    | 1110 | 14 : 1                                             | 233   |                     |              |                |

| Low                                    | 1111 | 15 : 1                                             | 250   |                     |              |                |

| Low                                    | 0000 | 16 : 1                                             | 266   |                     |              |                |

| High                                   | 0010 | 4 : 1                                              |       | 100                 | 133          | 266            |

| High                                   | 0011 | 6 : 1                                              | 100   | 150                 | 200          |                |

| High                                   | 0100 | 8 : 1                                              | 133   | 200                 | 266          |                |

| High                                   | 0101 | 10 : 1                                             | 166   | 250                 | 333          |                |

| High                                   | 0110 | 12 : 1                                             | 200   | 300                 |              |                |

| High                                   | 0111 | 14 : 1                                             | 233   |                     |              |                |

| High                                   | 1000 | 16 : 1                                             | 266   |                     |              |                |

Table 60. CSB Frequency Options for Agent Mode (continued)

<sup>1</sup> CFG\_CLKIN\_DIV doubles csb\_clk if set high.

<sup>2</sup> CLKIN is the input clock in host mode; PCI\_CLK is the input clock in agent mode.

# 19.2 Core PLL Configuration

RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (*csb\_clk*) and the e300 core clock (*core\_clk*). Table 61 shows the encodings for RCWL[COREPLL]. COREPLL values that are not listed in Table 61 should be considered as reserved.

### NOTE

Core VCO frequency = core frequency × VCO divider

VCO divider must be set properly so that the core VCO frequency is in the range of 800–1800 MHz.

### Table 63. Package Thermal Characteristics for TBGA (continued)

| Characteristic                                | Symbol | Value | Unit | Notes |

|-----------------------------------------------|--------|-------|------|-------|

| Junction-to-package natural convection on top | ΨJT    | 1     | °C/W | 6     |

Notes:

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal, 1 m/s is approximately equal to 200 linear feet per minute (LFM).

- 4. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

## 20.2 Thermal Management Information

For the following sections,  $P_D = (V_{DD} \times I_{DD}) + P_{I/O}$  where  $P_{I/O}$  is the power dissipation of the I/O drivers. See Table 5 for I/O power dissipation values.

## 20.2.1 Estimation of Junction Temperature with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from the equation:

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

where:

$T_J$  = junction temperature (°C)

$T_A$  = ambient temperature for the package (°C)

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The junction-to-ambient thermal resistance is an industry-standard value that provides a quick and easy estimation of thermal performance. Generally, the value obtained on a single-layer board is appropriate for a tightly packed printed-circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated. Test cases have demonstrated that errors of a factor of two (in the quantity  $T_J - T_A$ ) are possible.

## 20.2.2 Estimation of Junction Temperature with Junction-to-Board Thermal Resistance

The thermal performance of a device cannot be adequately predicted from the junction-to-ambient thermal resistance. The thermal performance of any component is strongly dependent on the power dissipation of surrounding components. In addition, the ambient temperature varies widely within the application. For many natural convection and especially closed box applications, the board temperature at the perimeter

### Thermal

| Heat sink vendors include the following list:                                                                                         |              |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Aavid Thermalloy<br>80 Commercial St.<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                                       | 603-224-9988 |

| Alpha Novatech<br>473 Sapena Ct. #12<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                                      | 408-567-8082 |

| International Electronic Research Corporation (IERC)<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com          | 818-842-7277 |

| Millennium Electronics (MEI)<br>Loroco Sites<br>671 East Brokaw Road<br>San Jose, CA 95112<br>Internet: www.mei-thermal.com           | 408-436-8770 |

| Tyco Electronics<br>Chip Coolers <sup>™</sup><br>P.O. Box 3668<br>Harrisburg, PA 17105-3668<br>Internet: www.chipcoolers.com          | 800-522-2800 |

| Wakefield Engineering<br>33 Bridge St.<br>Pelham, NH 03076<br>Internet: www.wakefield.com                                             | 603-635-5102 |

| Interface material vendors include the following:                                                                                     |              |

| Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01801<br>Internet: www.chomerics.com                                                   | 781-935-4850 |

| Dow-Corning Corporation<br>Dow-Corning Electronic Materials<br>P.O. Box 994<br>Midland, MI 48686-0997<br>Internet: www.dowcorning.com | 800-248-2481 |

| Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                                        | 888-642-7674 |

### **Ordering Information**

$V_2 = (1 \div (1/R_1 + 1/R_2)) \times I_{source}$ . Solving for the output impedance gives  $R_{source} = R_{term} \times (V_1 \div V_2 - 1)$ . The drive current is then  $I_{source} = V_1 \div R_{source}$ .

Table 65 summarizes the signal impedance targets. The driver impedance are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | Local Bus, Ethernet,<br>DUART, Control,<br>Configuration, Power<br>Management | PCI Signals<br>(Not Including PCI<br>Output Clocks) | PCI Output Clocks<br>(Including<br>PCI_SYNC_OUT) | DDR DRAM  | Symbol            | Unit |

|----------------|-------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|-----------|-------------------|------|

| R <sub>N</sub> | 42 Target                                                                     | 25 Target                                           | 42 Target                                        | 20 Target | Z <sub>0</sub>    | W    |

| R <sub>P</sub> | 42 Target                                                                     | 25 Target                                           | 42 Target                                        | 20 Target | Z <sub>0</sub>    | W    |

| Differential   | NA                                                                            | NA                                                  | NA                                               | NA        | Z <sub>DIFF</sub> | W    |

Table 65. Impedance Characteristics

**Note:** Nominal supply voltages. See Table 1,  $T_j = 105^{\circ}C$ .

# 21.6 Configuration Pin Multiplexing

The MPC8349EA power-on configuration options can be set through external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see the customer-visible configuration pins). These pins are used as output only pins in normal operation.

However, while HRESET is asserted, these pins are treated as inputs, and the value on these pins is latched when PORESET deasserts. Then the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with the large value of the pull-up/pull-down resistor should minimize the disruption of signal quality or speed for the output pins.

# 21.7 Pull-Up Resistor Requirements

The MPC8349EA requires high resistance pull-up resistors (10 k $\Omega$  is recommended) on open-drain pins, including I<sup>2</sup>C pins, and IPIC interrupt pins.

For more information on required pull-up resistors and the connections required for the JTAG interface, refer to application note AN2931, "PowerQUICC Design Checklist."

# 22 Ordering Information

This section presents ordering information for the device discussed in this document, and it shows an example of how the parts are marked.

## NOTE

The information in this document is accurate for revision 3.x silicon and later (in other words, for orderable part numbers ending in A or B). For information on revision 1.1 silicon and earlier versions, see the *MPC8349E PowerQUICC II Pro Integrated Host Processor Hardware Specifications* (Document Order No. MPC8349EEC).

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo and PowerQUICC are trademarks of Freescale Semiconductor, Inc. Reg. U.S. Pat. & Tm. Off. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2006–2011 Freescale Semiconductor, Inc.

Document Number: MPC8349EAEC Rev. 13 09/2011