# E·XFL

## NXP USA Inc. - MPC8349CVVAGDB Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 400MHz                                                                 |

| Co-Processors/DSP               | ·                                                                      |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | ·                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | ·                                                                      |

| USB                             | USB 2.0 + PHY (2)                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                     |

| Security Features               | -                                                                      |

| Package / Case                  | 672-LBGA                                                               |

| Supplier Device Package         | 672-LBGA (35x35)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8349cvvagdb |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Double data rate, DDR1/DDR2 SDRAM memory controller

- Programmable timing supporting DDR1 and DDR2 SDRAM

- 32- or 64-bit data interface, up to 400 MHz data rate

- Up to four physical banks (chip selects), each bank up to 1 Gbyte independently addressable

- DRAM chip configurations from 64 Mbits to 1 Gbit with  $\times 8/\times 16$  data ports

- Full error checking and correction (ECC) support

- Support for up to 16 simultaneous open pages (up to 32 pages for DDR2)

- Contiguous or discontiguous memory mapping

- Read-modify-write support

- Sleep-mode support for SDRAM self refresh

- Auto refresh

- On-the-fly power management using CKE

- Registered DIMM support

- 2.5-V SSTL2 compatible I/O for DDR1, 1.8-V SSTL2 compatible I/O for DDR2

- Dual three-speed (10/100/1000) Ethernet controllers (TSECs)

- Dual controllers designed to comply with IEEE 802.3<sup>TM</sup>, 802.3u<sup>TM</sup>, 820.3x<sup>TM</sup>, 802.3z<sup>TM</sup>, 802.3ac<sup>TM</sup> standards

- Ethernet physical interfaces:

- 1000 Mbps IEEE Std. 802.3 GMII/RGMII, IEEE Std. 802.3z TBI/RTBI, full-duplex

- 10/100 Mbps IEEE Std. 802.3 MII full- and half-duplex

- Buffer descriptors are backward-compatible with MPC8260 and MPC860T 10/100 programming models

- 9.6-Kbyte jumbo frame support

- RMON statistics support

- Internal 2-Kbyte transmit and 2-Kbyte receive FIFOs per TSEC module

- MII management interface for control and status

- Programmable CRC generation and checking

- Dual PCI interfaces

- Designed to comply with PCI Specification Revision 2.3

- Data bus width options:

- Dual 32-bit data PCI interfaces operating at up to 66 MHz

- Single 64-bit data PCI interface operating at up to 66 MHz

- PCI 3.3-V compatible

- PCI host bridge capabilities on both interfaces

- PCI agent mode on PCI1 interface

- PCI-to-memory and memory-to-PCI streaming

- Memory prefetching of PCI read accesses and support for delayed read transactions

- Posting of processor-to-PCI and PCI-to-memory writes

## 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

| Table 1. Absolute Maximum Ratings | s <sup>1</sup> |

|-----------------------------------|----------------|

|-----------------------------------|----------------|

|                                         | Parameter                                                                                        | Symbol            | Max Value                                                | Unit | Notes |

|-----------------------------------------|--------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------|------|-------|

| Core supply voltage                     |                                                                                                  | V <sub>DD</sub>   | –0.3 to 1.32 (1.36 max<br>for 667-MHz core<br>frequency) | V    | _     |

| PLL supply voltage                      |                                                                                                  | AV <sub>DD</sub>  | -0.3 to 1.32 (1.36 max<br>for 667-MHz core<br>frequency) | V    | —     |

| DDR and DDR2 DR                         | AM I/O voltage                                                                                   | GV <sub>DD</sub>  | -0.3 to 2.75 V<br>-0.3 to 1.98                           |      | —     |

| Three-speed Etherr                      | hree-speed Ethernet I/O, MII management voltage                                                  |                   | -0.3 to 3.63                                             | V    | —     |

| PCI, local bus, DUA and JTAG I/O voltag | RT, system control and power management, I <sup>2</sup> C, le                                    | OV <sub>DD</sub>  | -0.3 to 3.63                                             | V    | —     |

| Input voltage                           | DDR DRAM signals                                                                                 | MV <sub>IN</sub>  | –0.3 to (GV <sub>DD</sub> + 0.3)                         | V    | 2, 5  |

|                                         | DDR DRAM reference                                                                               | MV <sub>REF</sub> | –0.3 to (GV <sub>DD</sub> + 0.3)                         | V    | 2, 5  |

|                                         | Three-speed Ethernet signals                                                                     | LV <sub>IN</sub>  | -0.3 to (LV <sub>DD</sub> + 0.3)                         | V    | 4, 5  |

|                                         | Local bus, DUART, CLKIN, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>  | -0.3 to (OV <sub>DD</sub> + 0.3)                         | V    | 3, 5  |

|                                         | PCI                                                                                              | OV <sub>IN</sub>  | -0.3 to (OV <sub>DD</sub> + 0.3)                         | V    | 6     |

| Storage temperature                     | e range                                                                                          | T <sub>STG</sub>  | -55 to 150                                               | °C   | —     |

Notes:

<sup>1</sup> Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- <sup>2</sup> Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit can be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- <sup>3</sup> **Caution:** OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit can be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- <sup>4</sup> **Caution:** LV<sub>IN</sub> must not exceed LV<sub>DD</sub> by more than 0.3 V. This limit can be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- <sup>5</sup> (M,L,O)V<sub>IN</sub> and MV<sub>REF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

- 6 OVIN on the PCI interface can overshoot/undershoot according to the PCI Electrical Specification for 3.3-V operation, as shown in Figure 3.

**RESET Initialization**

# 4.3 TSEC Gigabit Reference Clock Timing

Table 8 provides the TSEC gigabit reference clocks (EC\_GTX\_CLK125) AC timing specifications.

## Table 8. EC\_GTX\_CLK125 AC Timing Specifications

At recommended operating conditions with LV  $_{DD}$  = 2.5  $\pm$  0.125 mV/ 3.3 V  $\pm$  165 mV

| Parameter                                                                                 | Symbol                                 | Min      | Typical | Max         | Unit | Notes |

|-------------------------------------------------------------------------------------------|----------------------------------------|----------|---------|-------------|------|-------|

| EC_GTX_CLK125 frequency                                                                   | t <sub>G125</sub>                      | —        | 125     | _           | MHz  | _     |

| EC_GTX_CLK125 cycle time                                                                  | t <sub>G125</sub>                      | —        | 8       |             | ns   | _     |

| EC_GTX_CLK125 rise and fall time $\label{eq:LVDD} LV_{DD} = 2.5 \ V \\ LV_{DD} = 3.3 \ V$ | <sup>t</sup> G125R <sup>/t</sup> G125F | _        |         | 0.75<br>1.0 | ns   | 1     |

| EC_GTX_CLK125 duty cycle<br>GMII, TBI<br>1000Base-T for RGMII, RTBI                       |                                        | 45<br>47 | _       | 55<br>53    | %    | 2     |

| EC_GTX_CLK125 jitter                                                                      | —                                      | _        |         | ±150        | ps   | 2     |

### Notes:

1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5 and 2.0 V for  $LV_{DD}$  = 2.5 V and from 0.6 and 2.7 V for  $LV_{DD}$  = 3.3 V.

2. EC\_GTX\_CLK125 is used to generate the GTX clock for the eTSEC transmitter with 2% degradation. The EC\_GTX\_CLK125 duty cycle can be loosened from 47%/53% as long as the PHY device can tolerate the duty cycle generated by the eTSEC GTX\_CLK. See Section 8.2.4, "RGMII and RTBI AC Timing Specifications for the duty cycle for 10Base-T and 100Base-T reference clock.

# 5 **RESET Initialization**

This section describes the DC and AC electrical specifications for the reset initialization timing and electrical requirements of the MPC8349EA.

# 5.1 **RESET DC Electrical Characteristics**

Table 9 provides the DC electrical characteristics for the RESET pins of the MPC8349EA.

| Parameter                        | Symbol          | Condition                 | Min  | Мах                    | Unit |

|----------------------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage               | V <sub>IH</sub> | —                         | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage                | V <sub>IL</sub> | —                         | -0.3 | 0.8                    | V    |

| Input current                    | I <sub>IN</sub> | —                         | _    | ±5                     | μA   |

| Output high voltage <sup>2</sup> | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —                      | V    |

| Output low voltage               | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | _    | 0.5                    | V    |

Table 9. RESET Pins DC Electrical Characteristics<sup>1</sup>

Table 11 lists the PLL and DLL lock times.

Table 11. PLL and DLL Lock Times

| Parameter/Condition | Min  | Мах     | Unit           | Notes |

|---------------------|------|---------|----------------|-------|

| PLL lock times      | —    | 100     | μs             |       |

| DLL lock times      | 7680 | 122,880 | csb_clk cycles | 1, 2  |

Notes:

1. DLL lock times are a function of the ratio between the output clock and the coherency system bus clock (csb\_clk). A 2:1 ratio results in the minimum and an 8:1 ratio results in the maximum.

2. The csb\_clk is determined by the CLKIN and system PLL ratio. See Section 19, "Clocking."

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR SDRAM interface of the MPC8349EA. Note that DDR SDRAM is  $GV_{DD}(typ) = 2.5$  V and DDR2 SDRAM is  $GV_{DD}(typ) = 1.8$  V. The AC electrical specifications are the same for DDR and DRR2 SDRAM.

## NOTE

The information in this document is accurate for revision 3.0 silicon and later. For information on revision 1.1 silicon and earlier versions see the *MPC8349E PowerQUICC II Pro Integrated Host Processor Hardware Specifications*. See Section 22.1, "Part Numbers Fully Addressed by This Document," for silicon revision level determination.

## 6.1 DDR and DDR2 SDRAM DC Electrical Characteristics

Table 12 provides the recommended operating conditions for the DDR2 SDRAM component(s) of the MPC8349EA when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol            | Min                       | Мах                       | Unit | Notes |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.71                      | 1.89                      | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 	imes GV_{DD}$      | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | —     |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | —     |

| Output leakage current                           | I <sub>OZ</sub>   | -9.9                      | 9.9                       | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>   | -13.4                     |                           | mA   | —     |

Table 15 provides the DDR capacitance when  $GV_{DD}(typ) = 2.5$  V.

Table 15. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Max | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1     |

Note:

1. This parameter is sampled.  $GV_{DD} = 2.5 V \pm 0.125 V$ , f = 1 MHz,  $T_A = 25^{\circ}C$ ,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

## Table 16 provides the current draw characteristics for MV<sub>REF</sub>.

Table 16. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter/Condition                | Symbol             | Min | Max | Unit | Note |

|------------------------------------|--------------------|-----|-----|------|------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> | _   | 500 | μA   | 1    |

### Note:

1. The voltage regulator for  $\text{MV}_{\text{REF}}$  must supply up to 500  $\mu\text{A}$  current.

## 6.2 DDR and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR and DDR2 SDRAM interface.

## 6.2.1 DDR and DDR2 SDRAM Input AC Timing Specifications

Table 17 provides the input AC timing specifications for the DDR2 SDRAM when  $GV_{DD}(typ) = 1.8 \text{ V}$ .

## Table 17. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

At recommended operating conditions with  $GV_{DD}$  of 1.8 ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.25 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 | _                        | V    | —     |

Table 18 provides the input AC timing specifications for the DDR SDRAM when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

### Table 18. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

At recommended operating conditions with  $GV_{DD}$  of 2.5 ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.31 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | _                        | V    | —     |

## 8.1.1 **TSEC DC Electrical Characteristics**

GMII, MII, TBI, RGMII, and RTBI drivers and receivers comply with the DC parametric attributes specified in Table 23 and Table 24. The RGMII and RTBI signals in Table 24 are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

| Parameter            | Symbol                        | Conditions                     |                 | Min  | Max                    | Unit |

|----------------------|-------------------------------|--------------------------------|-----------------|------|------------------------|------|

| Supply voltage 3.3 V | LV <sub>DD</sub> <sup>2</sup> | —                              |                 | 2.97 | 3.63                   | V    |

| Output high voltage  | V <sub>OH</sub>               | I <sub>OH</sub> = -4.0 mA      | $LV_{DD} = Min$ | 2.40 | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>               | I <sub>OL</sub> = 4.0 mA       | $LV_{DD} = Min$ | GND  | 0.50                   | V    |

| Input high voltage   | V <sub>IH</sub>               | —                              | —               | 2.0  | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>               | —                              | —               | -0.3 | 0.90                   | V    |

| Input high current   | I <sub>IH</sub>               | $V_{IN}^{1} = LV_{DD}$         |                 | _    | 40                     | μA   |

| Input low current    | ۱ <sub>IL</sub>               | V <sub>IN</sub> <sup>1</sup> = | GND             | -600 | —                      | μA   |

## Table 23. GMII/TBI and MII DC Electrical Characteristics

Notes:

1. The symbol  $V_{IN}$ , in this case, represents the LV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

2. GMII/MII pins not needed for RGMII or RTBI operation are powered by the OV<sub>DD</sub> supply.

## Table 24. RGMII/RTBI (When Operating at 2.5 V) DC Electrical Characteristics

| Parameters           | Symbol           | Conditions                     |                        | Min       | Max                    | Unit |

|----------------------|------------------|--------------------------------|------------------------|-----------|------------------------|------|

| Supply voltage 2.5 V | LV <sub>DD</sub> | —                              |                        | 2.37      | 2.63                   | V    |

| Output high voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0 mA      | $LV_{DD} = Min$        | 2.00      | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA       | LV <sub>DD</sub> = Min | GND – 0.3 | 0.40                   | V    |

| Input high voltage   | V <sub>IH</sub>  | —                              | LV <sub>DD</sub> = Min | 1.7       | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>  | —                              | LV <sub>DD</sub> = Min | -0.3      | 0.70                   | V    |

| Input high current   | I <sub>IH</sub>  | $V_{IN}^{1} = LV_{DD}$         |                        | —         | 10                     | μA   |

| Input low current    | Ι <sub>IL</sub>  | V <sub>IN</sub> <sup>1</sup> = | GND                    | -15       | —                      | μA   |

### Note:

1. The symbol  $V_{IN}$ , in this case, represents the LV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

# 8.2 GMII, MII, TBI, RGMII, and RTBI AC Timing Specifications

The AC timing specifications for GMII, MII, TBI, RGMII, and RTBI are presented in this section.

## 8.2.1 GMII Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

# 8.2.4 RGMII and RTBI AC Timing Specifications

Table 31 presents the RGMII and RTBI AC timing specifications.

## Table 31. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> of 2.5 V  $\pm$  5%.

| Parameter/Condition                                    | Symbol <sup>1</sup>                 | Min  | Тур | Max  | Unit |

|--------------------------------------------------------|-------------------------------------|------|-----|------|------|

| Data to clock output skew (at transmitter)             | t <sub>SKRGT</sub>                  | -0.5 | —   | 0.5  | ns   |

| Data to clock input skew (at receiver) <sup>2</sup>    | t <sub>SKRGT</sub>                  | 1.0  | —   | 2.8  | ns   |

| Clock cycle duration <sup>3</sup>                      | t <sub>RGT</sub>                    | 7.2  | 8.0 | 8.8  | ns   |

| Duty cycle for 1000Base-T <sup>4, 5</sup>              | t <sub>RGTH</sub> /t <sub>RGT</sub> | 45   | 50  | 55   | %    |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3, 5</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub> | 40   | 50  | 60   | %    |

| Rise time (20%–80%)                                    | t <sub>RGTR</sub>                   | —    | —   | 0.75 | ns   |

| Fall time (80%–20%)                                    | t <sub>RGTF</sub>                   | _    | —   | 0.75 | ns   |

Notes:

1. In general, the clock reference symbol for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (RX) clock. Also, the notation for rise (R) and fall (F) times follows the clock symbol. For symbols representing skews, the subscript is SK followed by the clock being skewed (RGT).

2. This implies that PC board design requires clocks to be routed so that an additional trace delay of greater than 1.5 ns is added to the associated clock signal.

3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns  $\pm$  40 ns and 40 ns  $\pm$  4 ns, respectively.

4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned.

5. Duty cycle reference is  $LV_{DD}/2$ .

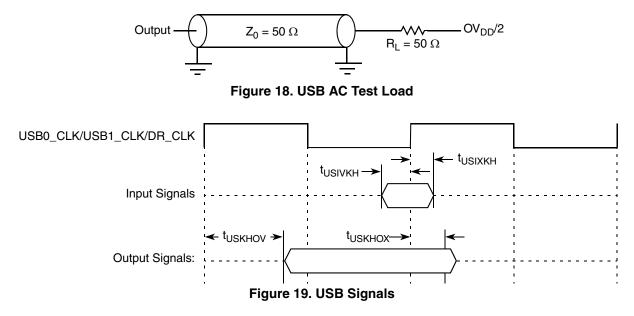

Figure 18 and Figure 19 provide the AC test load and signals for the USB, respectively.

# 10 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8349EA.

## **10.1 Local Bus DC Electrical Characteristics**

Table 37 provides the DC electrical characteristics for the local bus interface.

Table 37. Local Bus DC Electrical Characteristics

| Parameter                                          | Symbol          | Min                    | Мах                    | Unit |

|----------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                           | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                            | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| Input current                                      | I <sub>IN</sub> | —                      | ±5                     | μA   |

| High-level output voltage, $I_{OH} = -100 \ \mu A$ | V <sub>OH</sub> | OV <sub>DD</sub> - 0.2 | _                      | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$   | V <sub>OL</sub> | —                      | 0.2                    | V    |

### JTAG

| Parameter          | Symbol          | Condition                | Min | Мах | Unit |

|--------------------|-----------------|--------------------------|-----|-----|------|

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA | —   | 0.5 | V    |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA | —   | 0.4 | V    |

## Table 40. JTAG Interface DC Electrical Characteristics (continued)

# **11.2 JTAG AC Timing Specifications**

This section describes the AC electrical specifications for the IEEE Std. 1149.1 (JTAG) interface of the MPC8349EA. Table 41 provides the JTAG AC timing specifications as defined in Figure 28 through Figure 31.

## Table 41. JTAG AC Timing Specifications (Independent of CLKIN)<sup>1</sup>

At recommended operating conditions (see Table 2).

| Parameter                                  |                                | Symbol <sup>2</sup>                        | Min      | Мах      | Unit | Notes |

|--------------------------------------------|--------------------------------|--------------------------------------------|----------|----------|------|-------|

| JTAG external clock frequency of operation |                                | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  | —     |

| JTAG external clock cycle time             |                                | t <sub>JTG</sub>                           | 30       | —        | ns   | —     |

| JTAG external clock pulse width mea        | asured at 1.4 V                | t <sub>JTKHKL</sub>                        | 15       | _        | ns   | —     |

| JTAG external clock rise and fall times    |                                | t <sub>JTGR</sub> , t <sub>JTGF</sub>      | 0        | 2        | ns   | —     |

| TRST assert time                           |                                | t <sub>TRST</sub>                          | 25       | _        | ns   | 3     |

| Input setup times:                         | Boundary-scan data<br>TMS, TDI | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>4   | _<br>_   | ns   | 4     |

| Input hold times:                          | Boundary-scan data<br>TMS, TDI | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 10<br>10 |          | ns   | 4     |

| Valid times:                               | Boundary-scan data<br>TDO      | t <sub>jtkldv</sub><br>t <sub>jtklov</sub> | 2<br>2   | 11<br>11 | ns   | 5     |

| Output hold times:                         | Boundary-scan data<br>TDO      | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 2<br>2   |          | ns   | 5     |

# 13 PCI

This section describes the DC and AC electrical specifications for the PCI bus of the MPC8349EA.

# **13.1 PCI DC Electrical Characteristics**

Table 44 provides the DC electrical characteristics for the PCI interface of the MPC8349EA.

| Parameter                 | Symbol          | Test Condition                                       | Min                    | Мах                    | Unit |

|---------------------------|-----------------|------------------------------------------------------|------------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or                        | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage   | V <sub>IL</sub> | $V_{OUT} \le V_{OL}$ (max)                           | -0.3                   | 0.8                    | V    |

| Input current             | I <sub>IN</sub> | $V_{IN}^{1} = 0 V \text{ or } V_{IN} = OV_{DD}$      | _                      | ±5                     | μA   |

| High-level output voltage | V <sub>OH</sub> | OV <sub>DD</sub> = min,<br>I <sub>OH</sub> = −100 μA | OV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage  | V <sub>OL</sub> | OV <sub>DD</sub> = min,<br>I <sub>OL</sub> = 100 μA  |                        | 0.2                    | V    |

**Table 44. PCI DC Electrical Characteristics**

Note:

1. The symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1.

# 13.2 PCI AC Electrical Specifications

This section describes the general AC timing parameters of the PCI bus of the MPC8349EA. Note that the PCI\_CLK or PCI\_SYNC\_IN signal is used as the PCI input clock depending on whether the device is configured as a host or agent device. Table 45 provides the PCI AC timing specifications at 66 MHz.

| Parameter                      | Symbol <sup>2</sup> | Min | Max | Unit   | Notes |

|--------------------------------|---------------------|-----|-----|--------|-------|

| Clock to output valid          | <sup>t</sup> PCKHOV | —   | 6.0 | ns     | 3     |

| Output hold from clock         | <sup>t</sup> РСКНОХ | 1   | _   | ns     | 3     |

| Clock to output high impedance | t <sub>PCKHOZ</sub> | —   | 14  | ns     | 3, 4  |

| Input setup to clock           | t <sub>PCIVKH</sub> | 3.0 | _   | ns     | 3, 5  |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0   | _   | ns     | 3, 5  |

| REQ64 to PORESET setup time    | t <sub>PCRVRH</sub> | 5   | —   | clocks | 6     |

# **15.2 GPIO AC Timing Specifications**

Table 50 provides the GPIO input and output AC timing specifications.

| Table 50 | . GPIO Inpu | t AC Timing | Specifications <sup>1</sup> |

|----------|-------------|-------------|-----------------------------|

|----------|-------------|-------------|-----------------------------|

| Parameter                       | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

### Notes:

1. Input specifications are measured from the 50 percent level of the signal to the 50 percent level of the rising edge of CLKIN. Timings are measured at the pin.

2. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by external synchronous logic. GPIO inputs must be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

# 16 IPIC

This section describes the DC and AC electrical specifications for the external interrupt pins.

## 16.1 IPIC DC Electrical Characteristics

Table 51 provides the DC electrical characteristics for the external interrupt pins.

| Table 51. | IPIC DC | Electrical | Characteristics <sup>1</sup> |

|-----------|---------|------------|------------------------------|

|-----------|---------|------------|------------------------------|

| Parameter          | Symbol          | Condition                | Min  | Мах                    | Unit | Notes |

|--------------------|-----------------|--------------------------|------|------------------------|------|-------|

| Input high voltage | V <sub>IH</sub> | —                        | 2.0  | OV <sub>DD</sub> + 0.3 | V    | —     |

| Input low voltage  | V <sub>IL</sub> | _                        | -0.3 | 0.8                    | V    | —     |

| Input current      | I <sub>IN</sub> | _                        | —    | ±5                     | μA   | —     |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA | —    | 0.5                    | V    | 2     |

| Output low voltage | V <sub>OL</sub> | l <sub>OL</sub> = 3.2 mA | —    | 0.4                    | V    | 2     |

### Notes:

1. This table applies for pins  $\overline{IRQ}$ [0:7],  $\overline{IRQ}$ \_OUT, and  $\overline{MCP}$ \_OUT.

2. IRQ\_OUT and MCP\_OUT are open-drain pins; thus VOH is not relevant for those pins.

# **16.2 IPIC AC Timing Specifications**

Table 52 provides the IPIC input and output AC timing specifications.

## Table 52. IPIC Input AC Timing Specifications<sup>1</sup>

| Parameter                       | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| IPIC inputs—minimum pulse width | t <sub>PICWID</sub> | 20  | ns   |

### Notes:

1. Input specifications are measured at the 50 percent level of the IPIC input signals. Timings are measured at the pin.

IPIC inputs and outputs are asynchronous to any visible clock. IPIC outputs should be synchronized before use by external synchronous logic. IPIC inputs must be valid for at least t<sub>PICWID</sub> ns to ensure proper operation in edge triggered mode.

Package and Pin Listings

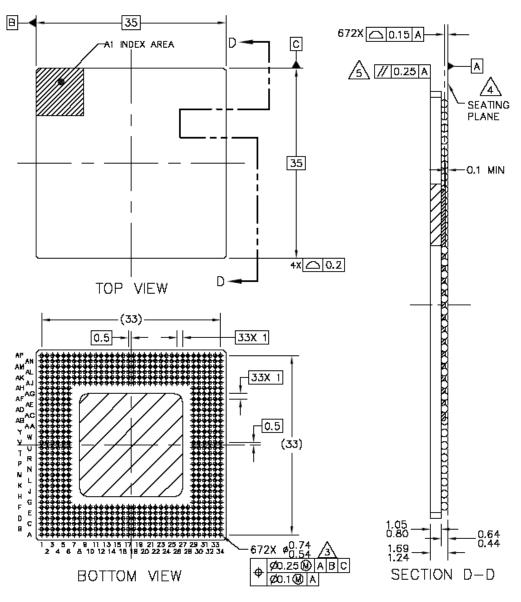

## 18.2 Mechanical Dimensions for the MPC8349EA TBGA

Figure 40 shows the mechanical dimensions and bottom surface nomenclature for the MPC8349EA, 672-TBGA package.

### Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensions and tolerances per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement must exclude any effect of mark on top surface of package.

### Figure 40. Mechanical Dimensions and Bottom Surface Nomenclature for the MPC8349EA TBGA

# 18.3 Pinout Listings

Table 55 provides the pin-out listing for the MPC8349EA, 672 TBGA package.

## Table 55. MPC8349EA (TBGA) Pinout Listing

| Signal                        | Package Pin Number                                                                                                                                                                                            | Pin Type Power<br>Supply |                  |   |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------|---|--|

|                               | PCI1 and PCI2 (One 64-Bit or Two 32-Bit)                                                                                                                                                                      |                          |                  |   |  |

| PCI1_INTA/IRQ_OUT             | B34                                                                                                                                                                                                           | 0                        | OV <sub>DD</sub> | 2 |  |

| PCI1_RESET_OUT                | C33                                                                                                                                                                                                           | 0                        | OV <sub>DD</sub> | — |  |

| PCI1_AD[31:0]                 | G30, G32, G34, H31, H32, H33, H34, J29,<br>J32, J33, L30, K31, K33, K34, L33, L34,<br>P34, R29, R30, R33, R34, T31, T32, T33,<br>U31, U34, V31, V32, V33, V34, W33, W34                                       | I/O                      | OV <sub>DD</sub> | _ |  |

| PCI1_C/BE[3:0]                | J30, M31, P33, T34                                                                                                                                                                                            | I/O                      | OV <sub>DD</sub> | — |  |

| PCI1_PAR                      | P32                                                                                                                                                                                                           | I/O                      | OV <sub>DD</sub> | — |  |

| PCI1_FRAME                    | M32                                                                                                                                                                                                           | I/O                      | OV <sub>DD</sub> | 5 |  |

| PCI1_TRDY                     | N29                                                                                                                                                                                                           | I/O                      | OV <sub>DD</sub> | 5 |  |

| PCI1_IRDY                     | M34                                                                                                                                                                                                           | I/O                      | OV <sub>DD</sub> | 5 |  |

| PCI1_STOP                     | N31                                                                                                                                                                                                           | I/O                      | OV <sub>DD</sub> | 5 |  |

| PCI1_DEVSEL                   | N30                                                                                                                                                                                                           | I/O                      | OV <sub>DD</sub> | 5 |  |

| PCI1_IDSEL                    | J31                                                                                                                                                                                                           | I                        | OV <sub>DD</sub> | — |  |

| PCI1_SERR                     | N34                                                                                                                                                                                                           | I/O                      | OV <sub>DD</sub> | 5 |  |

| PCI1_PERR                     | N33                                                                                                                                                                                                           | I/O                      | OV <sub>DD</sub> | 5 |  |

| PCI1_REQ[0]                   | D32                                                                                                                                                                                                           | I/O                      | OV <sub>DD</sub> | — |  |

| PCI1_REQ[1]/CPCI1_HS_ES       | D34                                                                                                                                                                                                           | I                        | OV <sub>DD</sub> | — |  |

| PCI1_REQ[2:4]                 | E34, F32, G29                                                                                                                                                                                                 | I                        | OV <sub>DD</sub> | — |  |

| PCI1_GNT0                     | C34                                                                                                                                                                                                           | I/O                      | OV <sub>DD</sub> | — |  |

| PCI1_GNT1/CPCI1_HS_LED        | D33                                                                                                                                                                                                           | 0                        | OV <sub>DD</sub> | — |  |

| PCI1_GNT2/CPCI1_HS_ENUM       | E33                                                                                                                                                                                                           | 0                        | OV <sub>DD</sub> | — |  |

| PCI1_GNT[3:4]                 | F31, F33                                                                                                                                                                                                      | 0                        | OV <sub>DD</sub> | — |  |

| PCI2_RESET_OUT/GPIO2[0]       | W32                                                                                                                                                                                                           | I/O                      | OV <sub>DD</sub> | — |  |

| PCI2_AD[31:0]/PCI1[63:32]     | AA33, AA34, AB31, AB32, AB33, AB34,<br>AC29, AC31, AC33, AC34, AD30, AD32,<br>AD33, AD34, AE29, AE30, AH32, AH33,<br>AH34, AM33, AJ31, AJ32, AJ33, AJ34,<br>AK32, AK33, AK34, AM34, AL33, AL34,<br>AK31, AH30 | I/O                      | OV <sub>DD</sub> | _ |  |

| PCI2_C/BE[3:0]/PCI1_C/BE[7:4] | AC32, AE32, AH31, AL32                                                                                                                                                                                        | I/O                      | OV <sub>DD</sub> | _ |  |

| PCI2_PAR/PCI1_PAR64           | AG34                                                                                                                                                                                                          | I/O                      | OV <sub>DD</sub> | — |  |

Package and Pin Listings

| Signal                    | Package Pin Number                                                                                                                                                                                                                                                                                                  | Pin Type | Power<br>Supply  | Notes |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| PCI2_FRAME/GPIO2[1]       | AE33                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | 5     |

| PCI2_TRDY/GPIO2[2]        | AF32                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | 5     |

| PCI2_IRDY/GPIO2[3]        | AE34                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | 5     |

| PCI2_STOP/GPIO2[4]        | AF34                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | 5     |

| PCI2_DEVSEL/GPIO2[5]      | AF33                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | 5     |

| PCI2_SERR/PCI1_ACK64      | AG33                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | 5     |

| PCI2_PERR/PCI1_REQ64      | AG32                                                                                                                                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | 5     |

| PCI2_REQ[0:2]/GPIO2[6:8]  | Y32, Y34, AA32                                                                                                                                                                                                                                                                                                      | I/O      | OV <sub>DD</sub> |       |

| PCI2_GNT[0:2]/GPIO2[9:11] | Y31, Y33, AA31                                                                                                                                                                                                                                                                                                      | I/O      | OV <sub>DD</sub> |       |

| M66EN                     | A19                                                                                                                                                                                                                                                                                                                 | I        | OV <sub>DD</sub> |       |

|                           | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                          |          |                  | I     |

| MDQ[0:63]                 | D5, A3, C3, D3, C4, B3, C2, D4, D2, E5,<br>G2, H6, E4, F3, G4, G3, H1, J2, L6, M6,<br>H2, K6, L2, M4, N2, P4, R2, T4, P6, P3,<br>R1, T2, AB5, AA3, AD6, AE4, AB4, AC2,<br>AD3, AE6, AE3, AG4, AK5, AK4, AE2,<br>AG6, AK3, AK2, AL2, AL1, AM5, AP5,<br>AM2, AN1, AP4, AN5, AJ7, AN7, AM8,<br>AJ9, AP6, AL7, AL9, AN8 | I/O      | GV <sub>DD</sub> | _     |

| MECC[0:4]/MSRCID[0:4]     | W4, W3, Y3, AA6, T1                                                                                                                                                                                                                                                                                                 | I/O      | GV <sub>DD</sub> | —     |

| MECC[5]/MDVAL             | U1                                                                                                                                                                                                                                                                                                                  | I/O      | GV <sub>DD</sub> | —     |

| MECC[6:7]                 | Y1, Y6                                                                                                                                                                                                                                                                                                              | I/O      | GV <sub>DD</sub> | —     |

| MDM[0:8]                  | B1, F1, K1, R4, AD4, AJ1, AP3, AP7, Y4                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> | —     |

| MDQS[0:8]                 | B2, F5, J1, P2, AC1, AJ2, AN4, AL8, W2                                                                                                                                                                                                                                                                              | I/O      | GV <sub>DD</sub> | —     |

| MBA[0:1]                  | AD1, AA5                                                                                                                                                                                                                                                                                                            | 0        | GV <sub>DD</sub> | —     |

| MA[0:14]                  | W1, U4, T3, R3, P1, M1, N1, L3, L1, K2,<br>Y2, K3, J3, AP2, AN6                                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | —     |

| MWE                       | AF1                                                                                                                                                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | —     |

| MRAS                      | AF4                                                                                                                                                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | —     |

| MCAS                      | AG3                                                                                                                                                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | —     |

| MCS[0:3]                  | AG2, AG1, AK1, AL4                                                                                                                                                                                                                                                                                                  | 0        | GV <sub>DD</sub> | —     |

| MCKE[0:1]                 | H3, G1                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> | 3     |

| MCK[0:5]                  | U2, F4, AM3, V3, F2, AN3                                                                                                                                                                                                                                                                                            | 0        | GV <sub>DD</sub> | —     |

| MCK[0:5]                  | U3, E3, AN2, V4, E1, AM4                                                                                                                                                                                                                                                                                            | 0        | GV <sub>DD</sub> | —     |

| MODT[0:3]                 | AH3, AJ5, AH1, AJ4                                                                                                                                                                                                                                                                                                  | 0        | GV <sub>DD</sub> | —     |

Package and Pin Listings

| Table 55. MPC8349EA | (TBGA) Pinout Listing (cor | itinued) |

|---------------------|----------------------------|----------|

|---------------------|----------------------------|----------|

| Signal                                          | Package Pin Number | Pin Type | Power<br>Supply  | Notes |

|-------------------------------------------------|--------------------|----------|------------------|-------|

| GPIO1[2]/DMA_DDONE0/<br>GTM1_TOUT1              | B25                | I/O      | OV <sub>DD</sub> | —     |

| GPIO1[3]/DMA_DREQ1/GTM1_TIN2/<br>GTM2_TIN1      | D24                | I/O      | OV <sub>DD</sub> | —     |

| GPIO1[4]/DMA_DACK1/<br>GTM1_TGATE2/GTM2_TGATE1  | A25                | I/O      | OV <sub>DD</sub> | —     |

| GPIO1[5]/DMA_DDONE1/<br>GTM1_TOUT2/GTM2_TOUT1   | B24                | I/O      | OV <sub>DD</sub> | —     |

| GPIO1[6]/DMA_DREQ2/GTM1_TIN3/<br>GTM2_TIN4      | A24                | I/O      | OV <sub>DD</sub> | —     |

| GPIO1[7]/DMA_DACK2/<br>GTM1_TGATE3/GTM2_TGATE4  | D23                | I/O      | OV <sub>DD</sub> | —     |

| GPIO1[8]/DMA_DDONE2/<br>GTM1_TOUT3              | B23                | I/O      | OV <sub>DD</sub> | —     |

| GPIO1[9]/DMA_DREQ3/GTM1_TIN4/<br>GTM2_TIN3      | A23                | I/O      | OV <sub>DD</sub> | —     |

| GPIO1[10]/DMA_DACK3/<br>GTM1_TGATE4/GTM2_TGATE3 | F22                | I/O      | OV <sub>DD</sub> | —     |

| GPIO1[11]/DMA_DDONE3/<br>GTM1_TOUT4/GTM2_TOUT3  | E22                | I/O      | OV <sub>DD</sub> | —     |

|                                                 | USB Port 1         |          |                  |       |

| MPH1_D0_ENABLEN/<br>DR_D0_ENABLEN               | A26                | I/O      | OV <sub>DD</sub> | —     |

| MPH1_D1_SER_TXD/<br>DR_D1_SER_TXD               | B26                | I/O      | OV <sub>DD</sub> | —     |

| MPH1_D2_VMO_SE0/<br>DR_D2_VMO_SE0               | D25                | I/O      | OV <sub>DD</sub> | —     |

| MPH1_D3_SPEED/DR_D3_SPEED                       | A27                | I/O      | OV <sub>DD</sub> | —     |

| MPH1_D4_DP/DR_D4_DP                             | B27                | I/O      | OV <sub>DD</sub> | —     |

| MPH1_D5_DM/DR_D5_DM                             | C27                | I/O      | OV <sub>DD</sub> | —     |

| MPH1_D6_SER_RCV/<br>DR_D6_SER_RCV               | D26                | I/O      | OV <sub>DD</sub> | —     |

| MPH1_D7_DRVVBUS/<br>DR_D7_DRVVBUS               | E26                | I/O      | OV <sub>DD</sub> | —     |

| MPH1_NXT/DR_SESS_VLD_NXT                        | D27                | I        | OV <sub>DD</sub> | _     |

| MPH1_DIR_DPPULLUP/<br>DR_XCVR_SEL_DPPULLUP      | A28                | I/O      | OV <sub>DD</sub> | —     |

| MPH1_STP_SUSPEND/<br>DR_STP_SUSPEND             | F26                | 0        | OV <sub>DD</sub> | —     |

### Table 55. MPC8349EA (TBGA) Pinout Listing (continued)

| Signal                                     | Package Pin Number         | Pin Type | Power<br>Supply   | Notes |

|--------------------------------------------|----------------------------|----------|-------------------|-------|

| TSEC2_TX_ER/GPIO1[24]                      | F14                        | I/O      | OV <sub>DD</sub>  | —     |

| TSEC2_TX_EN/GPIO1[12]                      | C5                         | I/O      | LV <sub>DD2</sub> | —     |

| TSEC2_TX_CLK/GPIO1[30]                     | E14                        | I/O      | OV <sub>DD</sub>  | —     |

|                                            | DUART                      |          |                   |       |

| UART_SOUT[1:2]/MSRCID[0:1]/<br>LSRCID[0:1] | AK27, AN29                 | 0        | OV <sub>DD</sub>  | —     |

| UART_SIN[1:2]/MSRCID[2:3]/<br>LSRCID[2:3]  | AL28, AM29                 | I/O      | OV <sub>DD</sub>  | —     |

| UART_CTS[1]/MSRCID4/LSRCID4                | AP30                       | I/O      | OV <sub>DD</sub>  | —     |

| UART_CTS[2]/MDVAL/ LDVAL                   | AN30                       | I/O      | OV <sub>DD</sub>  | —     |

| UART_RTS[1:2]                              | AP31, AM30                 | 0        | OV <sub>DD</sub>  | —     |

|                                            | I <sup>2</sup> C interface |          | •                 |       |

| IIC1_SDA                                   | AK29                       | I/O      | OV <sub>DD</sub>  | 2     |

| IIC1_SCL                                   | AP32                       | I/O      | OV <sub>DD</sub>  | 2     |

| IIC2_SDA                                   | AN31                       | I/O      | OV <sub>DD</sub>  | 2     |

| IIC2_SCL                                   | AM31                       | I/O      | OV <sub>DD</sub>  | 2     |

|                                            | SPI                        |          |                   |       |

| SPIMOSI/LCS[6]                             | AN32                       | I/O      | OV <sub>DD</sub>  | _     |

| SPIMISO/LCS[7]                             | AP33                       | I/O      | OV <sub>DD</sub>  | —     |

| SPICLK                                     | AK30                       | I/O      | OV <sub>DD</sub>  | —     |

| SPISEL                                     | AL31                       | I        | OV <sub>DD</sub>  | —     |

|                                            | Clocks                     |          |                   |       |

| PCI_CLK_OUT[0:2]                           | AN9, AP9, AM10,            | 0        | OV <sub>DD</sub>  | _     |

| PCI_CLK_OUT[3]/LCS[6]                      | AN10                       | 0        | OV <sub>DD</sub>  | —     |

| PCI_CLK_OUT[4]/LCS[7]                      | AJ11                       | 0        | OV <sub>DD</sub>  | —     |

| PCI_CLK_OUT[5:7]                           | AP10, AL11, AM11           | 0        | OV <sub>DD</sub>  | —     |

| PCI_SYNC_IN/PCI_CLOCK                      | AK12                       | I        | OV <sub>DD</sub>  | —     |

| PCI_SYNC_OUT                               | AP11                       | 0        | OV <sub>DD</sub>  | 3     |

| RTC/PIT_CLOCK                              | AM32                       | I        | OV <sub>DD</sub>  | —     |

| CLKIN                                      | AM9                        | I        | OV <sub>DD</sub>  | —     |

|                                            | JTAG                       |          | •                 |       |

| ТСК                                        | E20                        | I        | OV <sub>DD</sub>  |       |

| TDI                                        | F20                        | I        | OV <sub>DD</sub>  | 4     |

#### Clocking

Table 57 provides the operating frequencies for the MPC8349EA TBGA under recommended operating conditions (see Table 2).

| Characteristic <sup>1</sup>                          | 400 MHz   | 533 MHz   | 667 MHz    | Unit |

|------------------------------------------------------|-----------|-----------|------------|------|

| e300 core frequency ( <i>core_clk</i> )              | 266–400   | 266–533   | 266–667    | MHz  |

| Coherent system bus frequency ( <i>csb_clk</i> )     | 100–266   | 100–333   | 100–333    | MHz  |

| DDR1 memory bus frequency (MCK) <sup>2</sup>         | 100–133   | 100–133   | 100–166.67 | MHz  |

| DDR2 memory bus frequency (MCK) <sup>3</sup>         | 100–133   | 100–133   | 100–200    | MHz  |

| Local bus frequency (LCLKn) <sup>4</sup>             | 16.67–133 | 16.67–133 | 16.67–133  | MHz  |

| PCI input frequency (CLKIN or PCI_CLK)               | 25–66     | 25–66     | 25–66      | MHz  |

| Security core maximum internal operating frequency   | 133       | 133       | 166        | MHz  |

| USB_DR, USB_MPH maximum internal operating frequency | 133       | 133       | 166        | MHz  |

Table 57. Operating Frequencies for TBGA

<sup>1</sup> The CLKIN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be chosen so that the resulting *csb\_clk*, MCK, LCLK[0:2], and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies. The value of SCCR[ENCCM], SCCR[USBDRCM] and SCCR[USBMPHCM] must be programmed so that the maximum internal operating frequency of the security core and USB modules does not exceed the respective values listed in this table.

<sup>2</sup> The DDR data rate is 2x the DDR memory bus frequency.

<sup>3</sup> The DDR data rate is 2x the DDR memory bus frequency.

<sup>4</sup> The local bus frequency is 1/2, 1/4, or 1/8 of the *lbiu\_clk* frequency (depending on LCCR[CLKDIV]) which is in turn 1x or 2x the *csb\_clk* frequency (depending on RCWL[LBIUCM]).

All frequency combinations shown in the table below may not be available. Maximum operating frequencies depend on the part ordered, see Section 22.1, "Part Numbers Fully Addressed by This Document," for part ordering details and contact your Freescale Sales Representative or authorized distributor for more information.

# **19.1 System PLL Configuration**

The system PLL is controlled by the RCWL[SPMF] parameter. Table 58 shows the multiplication factor encodings for the system PLL.

| RCWL[SPMF] | System PLL Multiplication Factor |

|------------|----------------------------------|

| 0000       | × 16                             |

| 0001       | Reserved                         |

| 0010       | × 2                              |

| 0011       | × 3                              |

| 0100       | × 4                              |

| 0101       | × 5                              |

| 0110       | × 6                              |

Table 58. System PLL Multiplication Factors

# **19.3 Suggested PLL Configurations**

Table 62 shows suggested PLL configurations for 33 and 66 MHz input clocks.

| Table 62. Sug | gested PLL | Configurations |

|---------------|------------|----------------|

|---------------|------------|----------------|

|                         | RC   | WL          | 40                                           | 0 MHz Dev            | ice                   | 533                                          | 3 MHz Dev            | ice                   | 667                                          | 7 MHz Dev            | ice                   |

|-------------------------|------|-------------|----------------------------------------------|----------------------|-----------------------|----------------------------------------------|----------------------|-----------------------|----------------------------------------------|----------------------|-----------------------|

| Ref<br>No. <sup>1</sup> | SPMF | CORE<br>PLL | Input<br>Clock<br>Freq<br>(MHz) <sup>2</sup> | CSB<br>Freq<br>(MHz) | Core<br>Freq<br>(MHz) | Input<br>Clock<br>Freq<br>(MHz) <sup>2</sup> | CSB<br>Freq<br>(MHz) | Core<br>Freq<br>(MHz) | Input<br>Clock<br>Freq<br>(MHz) <sup>2</sup> | CSB<br>Freq<br>(MHz) | Core<br>Freq<br>(MHz) |

|                         |      |             |                                              | 33 N                 | MHz CLKIN             | /PCI_CLK                                     | Options              |                       |                                              |                      |                       |

| 922                     | 1001 | 0100010     | —                                            | —                    | —                     | _                                            | —                    | f300                  | 33                                           | 300                  | 300                   |

| 723                     | 0111 | 0100011     | 33                                           | 233                  | 350                   | 33                                           | 233                  | 350                   | 33                                           | 233                  | 350                   |

| 604                     | 0110 | 0000100     | 33                                           | 200                  | 400                   | 33                                           | 200                  | 400                   | 33                                           | 200                  | 400                   |

| 624                     | 0110 | 0100100     | 33                                           | 200                  | 400                   | 33                                           | 200                  | 400                   | 33                                           | 200                  | 400                   |

| 803                     | 1000 | 0000011     | 33                                           | 266                  | 400                   | 33                                           | 266                  | 400                   | 33                                           | 266                  | 400                   |

| 823                     | 1000 | 0100011     | 33                                           | 266                  | 400                   | 33                                           | 266                  | 400                   | 33                                           | 266                  | 400                   |

| 903                     | 1001 | 0000011     |                                              | _                    |                       | 33                                           | 300                  | 450                   | 33                                           | 300                  | 450                   |

| 923                     | 1001 | 0100011     |                                              | _                    |                       | 33                                           | 300                  | 450                   | 33                                           | 300                  | 450                   |

| 704                     | 0111 | 0000011     |                                              | _                    |                       |                                              | 233                  | 466                   | 33                                           | 233                  | 466                   |

| 724                     | 0111 | 0100011     |                                              | _                    |                       | 33                                           | 233                  | 466                   | 33                                           | 233                  | 466                   |

| A03                     | 1010 | 0000011     |                                              | _                    |                       | 33                                           | 333                  | 500                   | 33                                           | 333                  | 500                   |

| 804                     | 1000 | 0000100     |                                              | _                    |                       | 33                                           | 266                  | 533                   | 33                                           | 266                  | 533                   |

| 705                     | 0111 | 0000101     |                                              | _                    |                       |                                              | _                    |                       | 33                                           | 233                  | 583                   |

| 606                     | 0110 | 0000110     |                                              | _                    |                       |                                              | _                    |                       | 33                                           | 200                  | 600                   |

| 904                     | 1001 | 0000100     |                                              | _                    |                       |                                              | —                    |                       | 33                                           | 300                  | 600                   |

| 805                     | 1000 | 0000101     |                                              | _                    |                       |                                              | _                    |                       | 33                                           | 266                  | 667                   |

| A04                     | 1010 | 0000100     |                                              | _                    |                       |                                              | _                    |                       | 33                                           | 333                  | 667                   |

|                         |      |             |                                              | 66 N                 | MHz CLKIN             | /PCI_CLK                                     | Options              |                       |                                              |                      |                       |

| 304                     | 0011 | 0000100     | 66                                           | 200                  | 400                   | 66                                           | 200                  | 400                   | 66                                           | 200                  | 400                   |

| 324                     | 0011 | 0100100     | 66                                           | 200                  | 400                   | 66                                           | 200                  | 400                   | 66                                           | 200                  | 400                   |

| 403                     | 0100 | 0000011     | 66                                           | 266                  | 400                   | 66                                           | 266                  | 400                   | 66                                           | 266                  | 400                   |

| 423                     | 0100 | 0100011     | 66                                           | 266                  | 400                   | 66                                           | 266                  | 400                   | 66                                           | 266                  | 400                   |

| 305                     | 0011 | 0000101     |                                              |                      |                       | 66                                           | 200                  | 500                   | 66                                           | 200                  | 500                   |

| 503                     | 0101 | 0000011     |                                              | _                    |                       | 66                                           | 333                  | 500                   | 66                                           | 333                  | 500                   |

| 404                     | 0100 | 0000100     |                                              | _                    |                       | 66                                           | 266                  | 533                   | 66                                           | 266                  | 533                   |

### System Design Information

2. The e300 core PLL generates the core clock as a slave to the platform clock. The frequency ratio between the e300 core clock and the platform clock is selected using the e300 PLL ratio configuration bits as described in Section 19.2, "Core PLL Configuration."

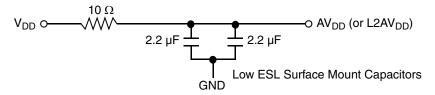

# 21.2 PLL Power Supply Filtering

Each PLL gets power through independent power supply pins ( $AV_{DD}1$ ,  $AV_{DD}2$ , respectively). The  $AV_{DD}$  level should always equal to  $V_{DD}$ , and preferably these voltages are derived directly from  $V_{DD}$  through a low frequency filter scheme.

There are a number of ways to provide power reliably to the PLLs, but the recommended solution is to provide four independent filter circuits as illustrated in Figure 42, one to each of the four  $AV_{DD}$  pins. Independent filters to each PLL reduce the opportunity to cause noise injection from one PLL to the other.

The circuit filters noise in the PLL resonant frequency range from 500 kHz to 10 MHz. It should be built with surface mount capacitors with minimum effective series inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

To minimize noise coupled from nearby circuits, each circuit should be placed as closely as possible to the specific  $AV_{DD}$  pin being supplied. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of package, without the inductance of vias.

Figure 42 shows the PLL power supply filter circuit.

Figure 42. PLL Power Supply Filter Circuit

## 21.3 Decoupling Recommendations

Due to large address and data buses and high operating frequencies, the MPC8349EA can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8349EA system, and the device itself requires a clean, tightly regulated source of power. Therefore, the system designer should place at least one decoupling capacitor at each  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pin of the device. These capacitors should receive their power from separate  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ , and GND power planes in the PCB, with short traces to minimize inductance. Capacitors can be placed directly under the device using a standard escape pattern. Others can surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, distribute several bulk storage capacitors around the PCB, feeding the  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should

## 22.1 Part Numbers Fully Addressed by This Document

Table 66 shows an analysis of the Freescale part numbering nomenclature for the MPC8349EA. The individual part numbers correspond to a maximum processor core frequency. Each part number also contains a revision code that refers to the die mask revision number. For available frequency configuration parts including extended temperatures, refer to the device product summary page on our website listed on the back cover of this document or, contact your local Freescale sales office.