# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                               |

|---------------------------------|--------------------------------------------------------|

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 16MHz                                                  |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                        |

| Security Features               | -                                                      |

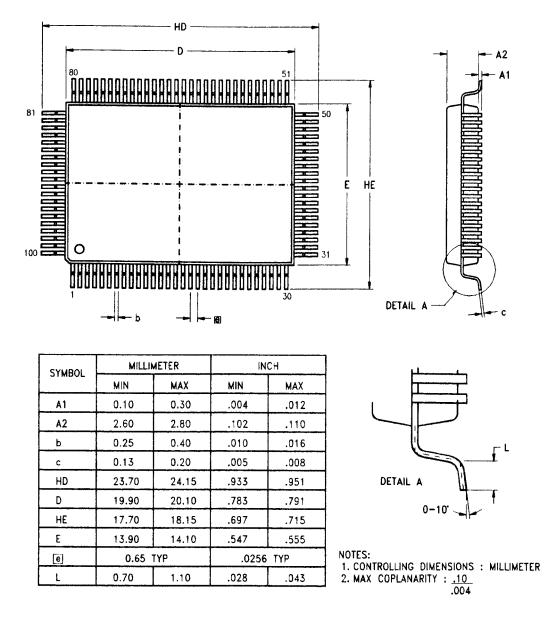

| Package / Case                  | 100-LQFP                                               |

| Supplier Device Package         | 100-VQFP (14x14)                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018216asc |

|                                 |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z80182/Z8L182 FUNCTIONAL DESCRIPTION

Functionally, the on-chip Z182 MPU and ESCC<sup>m</sup> are the same as the discrete devices (Figure 1). Therefore, for a detailed description of each individual unit, refer to the

Product Specification/Technical Manuals of each discrete product. The following subsections describe each of the individual units of the Z182.

## **Z182 MPU FUNCTIONAL DESCRIPTION**

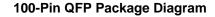

This unit provides all the capabilities and pins of the Zilog Z8S180 MPU (Static Z80180 MPU). Figure 4 shows the S180 MPU Block Diagram of the Z182. This allows 100%

software compatibility with existing  $Z180^{\text{M}}$  (and  $Z80^{\text{B}}$ ) software. The following is an overview of the major functional units of the Z182.

Figure 4. S180 MPU Block Diagram of Z182

## Z85230 ESCC<sup>™</sup> FUNCTIONAL DESCRIPTION

The Zilog Enhanced Serial Communication Controller ESCC<sup>™</sup> is a dual channel, multiprotocol data communication peripheral. The ESCC functions as a serial-to-parallel, parallel-to-serial converter/controller. The ESCC can be software-configured to satisfy a wide variety of serial communications applications. The device contains a variety of new, sophisticated internal functions including on-chip baud rate generators, digital phase-lock loops, and crystal oscillators, which dramatically reduce the need for external logic.

The ESCC handles asynchronous formats, synchronous byte-oriented protocols such as IBM<sup>®</sup> Bisync, and synchronous bit-oriented protocols such as HDLC and IBM SDLC. This versatile device supports virtually any serial data transfer application (telecommunication, LAN, etc.)

The device can generate and check CRC codes in any synchronous mode and can be programmed to check data integrity in various modes. The ESCC also has facilities for modem control in both channels in applications where these controls are not needed, the modem controls can be used for general-purpose I/O.

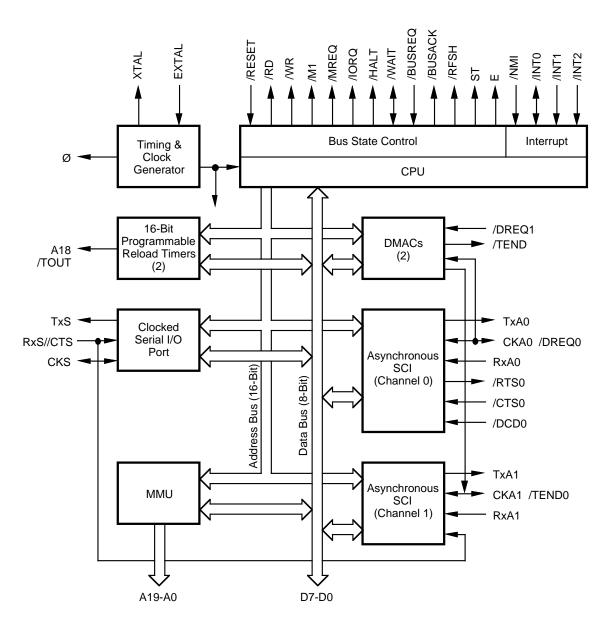

With access to 14 Write registers and 7 Read registers per channel (number of the registers varies depending on the version), the user can configure the ESCC to handle all synchronous formats regardless of data size, number of stop bits, or parity requirements. The ESCC also accommodates all synchronous formats including character, byte, and bit-oriented protocols.

Within each operating mode, the ESCC also allows for protocol variations by checking odd or even parity bits, character insertion or deletion, CRC generation, checking break and abort generation and detection, and many other protocol-dependent features. The ESCC (Enhanced SCC) is pin and software compatible to the CMOS SCC version. The following enhancements were made to the CMOS SCC:

- Deeper Transmit FIFO (4 bytes)

- Deeper Receive FIFO (8 bytes)

- Programmable FIFO interrupt and DMA request level

- Seven enhancements to improve SDLC link layer supports:

- Automatic transmission of the opening flag

- Automatic reset of Tx Underrun/EOM latch

- Deactivation of /RTS pin after closing flag

- Automatic CRC generator preset

- Complete CRC reception

- TxD pin automatically forced High with NRZI encoding when using mark idle

- Status FIFO handles better frames with an ABORT

- Receive FIFO automatically unlocked for special receive interrupts when using the SDLC status FIFO

- Delayed bus latching for easier microprocessor interface

- New programmable features added with Write Register 7' (WR seven prime)

- Write registers, 3, 4, 5 and 10 are now readable

- Read register 0 latched during access

- DPLL counter output available as jitter-free transmitter clock source

- Enhanced /DTR, /RTS deactivation timing

## PARALLEL PORTS FUNCTIONAL DESCRIPTION

The Z80182/Z8L182 has three 8-bit bi-directional Ports. Each bit is individually programmable for input or output (with the exception of PC6 and PC7 which are inputs only).

The Ports are controlled through two registers: the Port Direction Control Register and the Port Data Register. (Please see register description for Ports A, B and C).

## PROGRAMMING

The following subsections explain and define the parameters for I/O Address assignments. The three tables in this section describe the mapping of the common registers shared by the MPU and the 16550 MIMIC. The MPU address refers to the I/O address as accessed from the MPU side (the Z180<sup>™</sup> MPU interface side of the 16550 MIMIC). Note that only the lowest eight address lines are decoded for Z182 peripheral access. The full sixteen

address lines are decoded for on-chip Z180 MPU access. The PC address (coined because the UART is common in PCs) is the address needed to access the MIMIC registers through the MIMIC interface signals. The MIMIC interface signals are multiplexed with the ESCC channel B and the Port A signals, and must be activated through the System Configuration Register and the Interrupt Edge/Pin MUX Register.

#### Table 7. Z80182/Z8L182 MPU Registers

| Register Name                       | MPU Addr                                                                | PC Addr |

|-------------------------------------|-------------------------------------------------------------------------|---------|

| Z80182/Z8L182 MPU Control Registers | 0000H to 00x3FH<br>(Relocatable to 0040H to 007FH<br>or 0080H to 00BFH) | None    |

#### Note:

"x" indicates don't care condition

| Register Name                       | MPU Add | r/Access | PC Add | PC Addr/Access |  |  |

|-------------------------------------|---------|----------|--------|----------------|--|--|

| MMC MIMIC Master Control Register   | xxFFH   | R/W      | None   |                |  |  |

| IUS/IP Interrupt Pending            | xxFEH   | R/Wb7    | None   |                |  |  |

| IE Interrupt Enable                 | xxFDH   | R/W      | None   |                |  |  |

| IVEC Interrupt Vector               | xxFCH   | R/W      | None   |                |  |  |

| TTCR Transmit Time Constant         | xxFAH   | R/W      | None   |                |  |  |

| RTCR Receive Time Constant          | xxFBH   | R/W      | None   |                |  |  |

| FSCR FIFO Status and Control        | XXECH   | R/W7-4   | None   |                |  |  |

| RTTC Receive Timeout Time Constant  | xxEAH   | R/W      | None   |                |  |  |

| TTTC Transmit Timeout Time Constant | xxEBH   | R/W      | None   |                |  |  |

| RBR Receive Buffer Register         | xxF0H   | Wonly    | 00H    | DLAB=0 R only  |  |  |

| THR Transmit Holding Register       | xxF0H   | Ronly    | 00H    | DLAB=0 W only  |  |  |

| IER Interrupt Enable Register       | xxF1H   | Ronly    | 01H    | DLAB=0 R/W     |  |  |

| IIR Interrupt Identification        | None    | 2        | 02H    | R only         |  |  |

| FCR FIFO Control Register           | xxE9H   | R only   | 02H    | W only         |  |  |

| MM REGISTER                         | XXE9H   | Wonly    | None   |                |  |  |

| LCR Line Control Register           | xxF3H   | Ronly    | 03H    | R/W            |  |  |

| MCR Modem Control Register          | xxF4H   | Ronly    | 04H    | R/W            |  |  |

| LSR Line Status Register            | xxF5H   | R/Wb6432 | 05H    | R only         |  |  |

| MSR Modem Status Register           | xxF6H   | R/Wb7-4  | 06H    | Ronly          |  |  |

| SCR Scratch Register                | xxF7H   | R only   | 07H    | R/W            |  |  |

| DLL Divisor Latch (LSByte)          | xxF8H   | Ronly    | 00H    | DLAB=1 R/W     |  |  |

| DLM Divisor Latch (MSByte)          | xxF9H   | R only   | 01H    | DLAB=1 R/W     |  |  |

#### Table 8. Z80182/Z8L182 MIMIC Register MAP

|            | CNTLB   | 0   |             |     |     |     | A   | ddr 02H |                                                                                                                                                                                                  |

|------------|---------|-----|-------------|-----|-----|-----|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit        | MPBT    | MP  | /CTS/<br>PS | PE0 | DR  | SS2 | SS1 | SS0     |                                                                                                                                                                                                  |

| Upon Reset | Invalid | 0   | †           | 0   | 0   | 1   | 1   | 1       |                                                                                                                                                                                                  |

| R/W        | R/W     | R/W | R/W         | R/W | R/W | R/W | R/W | R/W     |                                                                                                                                                                                                  |

|            |         |     |             |     |     |     |     |         | <ul> <li>Clock Source and Speed Select</li> <li>Divide Ratio</li> <li>Parity Even or Odd</li> <li>Clear To Send/Prescale</li> <li>Multiprocessor</li> <li>Multiprocessor Bit Transmit</li> </ul> |

$\ensuremath{^+}$  /CTS - Depending on the condition of /CTS pin. PS - Cleared to 0.

| General<br>Divide Ratio | PS = 0<br>(Divide Ratio = 10) |              | PS = 1<br>(Divide Ratio = 30) |              |

|-------------------------|-------------------------------|--------------|-------------------------------|--------------|

| SS, 2, 1, 0             | DR = 0 (x16)                  | DR = 1 (x64) | DR = 0 (x16)                  | DR = 1 (x64) |

| 000                     | Ø÷160                         | Ø ÷ 640      | Ø÷ 480                        | Ø÷ 1920      |

| 001                     | Ø ÷ 320                       | Ø÷1280       | Ø÷960                         | Ø÷ 3840      |

| 010                     | Ø÷640                         | Ø÷2580       | Ø÷1920                        | Ø÷7680       |

| 011                     | Ø÷ 1280                       | Ø÷5120       | Ø÷3840                        | Ø÷ 15360     |

| 100                     | Ø÷2560                        | Ø÷10240      | Ø÷7680                        | Ø÷ 30720     |

| 101                     | Ø÷5120                        | Ø÷20480      | Ø÷ 15360                      | Ø÷61440      |

| 110                     | Ø÷ 10240                      | Ø÷40960      | Ø÷ 30720                      | Ø÷ 122880    |

| 111                     | External Clock (Frequer       | cy < Ø ÷ 40) |                               |              |

Figure 11. ASCI Control Register B (Ch. 0)

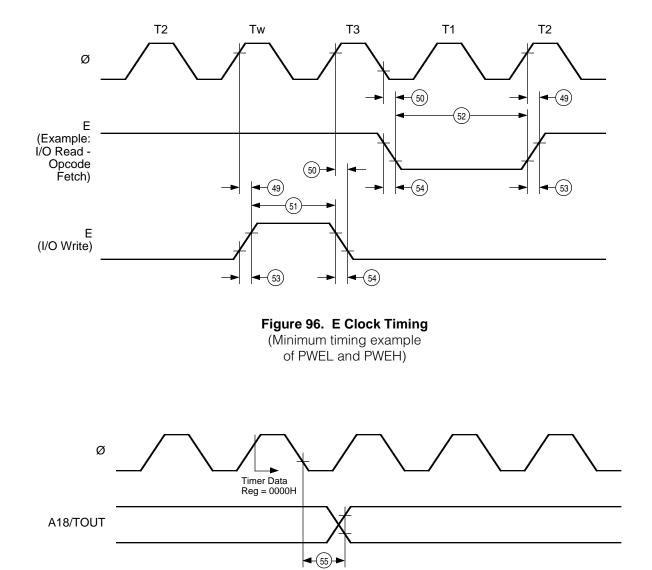

## TIMER DATA REGISTERS

|   | TMDR0L<br>Read/Write |  |   |  |   | Addr 0CH |   |   |  |

|---|----------------------|--|---|--|---|----------|---|---|--|

| ſ | 7                    |  | 5 |  | 3 | 2        | 1 | 0 |  |

#### Figure 23. Timer 0 Data Register L

| TM<br>Re |   | A | ddr | 14H |   |   |   |

|----------|---|---|-----|-----|---|---|---|

| 7        | 6 | 5 | 4   | 3   | 2 | 1 | 0 |

Figure 24. Timer 1 Data Register L

|    | IDR<br>ad/ |    |    | Addr 0DH |    |   |   |

|----|------------|----|----|----------|----|---|---|

| 15 | 14         | 13 | 12 | 11       | 10 | 9 | 8 |

When Read, read Data Register L before reading Data Register H.

#### Figure 25. Timer 0 Data Register H

| TMDR1H<br>Read/Write |    |    |    |    |    | ddr | 15H | 4 |

|----------------------|----|----|----|----|----|-----|-----|---|

| 15                   | 14 | 13 | 12 | 11 | 10 | 9   | 8   |   |

When Read, read Data Register L before reading Data Register H.

#### Figure 26. Timer 1 Data Register H

## TIMER RELOAD REGISTERS

| RLDR0L<br>Read/Write |   |   |   |   | Ac | ldr ( | DEH | I |  |

|----------------------|---|---|---|---|----|-------|-----|---|--|

|                      | 7 | 6 | 5 | 4 | 3  | 2     | 1   | 0 |  |

#### Figure 27. Timer 0 Reload Register L

| RLI<br>Rea |   | L<br>Vrite | • |   | Ad | ddr | 16H |  |

|------------|---|------------|---|---|----|-----|-----|--|

| 7          | 6 | 5          | 4 | 3 | 2  | 1   | 0   |  |

Figure 28. Timer 1 Reload Register L

| RL  | DR0  | H     |    |          |    |   |   |  |

|-----|------|-------|----|----------|----|---|---|--|

| Rea | ad/V | Vrite | )  | Addr 0FH |    |   |   |  |

| 15  | 14   | 13    | 12 | 11       | 10 | 9 | 8 |  |

#### Figure 29. Timer 0 Reload Register H

| RL  |    | ••• |    |    |    |       |   |  |

|-----|----|-----|----|----|----|-------|---|--|

| Rea |    |     | -  |    |    | ldr ' |   |  |

| 15  | 14 | 13  | 12 | 11 | 10 | 9     | 8 |  |

Figure 30. Timer 1 Reload Register H

|            | DCNTL                |      |                                    |           |     |                                          | A         | ddr 32H                                  |                                                                                                                                                     |

|------------|----------------------|------|------------------------------------|-----------|-----|------------------------------------------|-----------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit        | MWI1                 | MWI0 | IWI1                               | IWI0      | DMS | 1 DMS0                                   | DIM1      | DIM0                                     |                                                                                                                                                     |

| Upon Reset | 1                    | 1    | 1                                  | 1         | 0   | 0                                        | 0         | 0                                        |                                                                                                                                                     |

| R/W        | R/W                  | R/W  | R/W                                | R/W       | R/W | R/W                                      | R/W       | R/W                                      |                                                                                                                                                     |

|            |                      |      |                                    |           |     |                                          |           |                                          | <ul> <li>DMA Ch 1 I/O Memory<br/>Mode Select</li> <li>/DREQi Select, i = 1, 0</li> <li>I/0 Wait Insertion</li> <li>Memory Wait Insertion</li> </ul> |

| *          | MWI1,                | 0 Nc | o. of Wa                           | it States | ר ר | IWI1, 0                                  | No. o     | f Wait S                                 |                                                                                                                                                     |

|            | 00<br>01<br>10<br>11 |      | 0<br>1<br>2<br>3                   |           |     | 00<br>01<br>10<br>11                     |           | 1<br>2<br>3<br>4                         |                                                                                                                                                     |

|            |                      |      |                                    |           |     |                                          |           |                                          |                                                                                                                                                     |

|            | DMSi                 |      | Sens                               | se        |     |                                          |           |                                          |                                                                                                                                                     |

|            | 1<br>0               |      | Edge S<br>Level S                  |           |     |                                          |           |                                          |                                                                                                                                                     |

|            | DM1,                 | 0 -  | Fransfer                           | Mode      | A   | ddress In                                | crement   | /Decrem                                  | ent                                                                                                                                                 |

|            | 00<br>01<br>10<br>11 |      | M - I,<br>M - I,<br>I/O -<br>I/O - | /O<br>M   |     | MAR1+1<br>MAR1-1<br>AR1 Fixe<br>AR1 Fixe | A۱<br>d I | AR1 Fixe<br>AR1 Fixe<br>MAR1+1<br>MAR1-1 | d                                                                                                                                                   |

|            | Note:                |      |                                    |           |     |                                          |           |                                          |                                                                                                                                                     |

Note: \* If using ROM/RAM Chip Select wait state generators, the Z180 wait state generator should be set to 0.

## Figure 42. DMA/WAIT Control Register

## STANDBY Mode Exit with BUS REQUEST

Optionally, if the BREXT bit (D5 of CPU Control Register) is set to 1, the Z8S180 exits STANDBY mode when the /BUSREQ input is asserted; the crystal oscillator is then restarted. An internal counter automatically provides time for the oscillator to stabilize, before the internal clocking and the system clock output of the Z8S180 are resumed.

The Z8S180 relinquishes the system bus after the clocking is resumed by:

- Tri-State the address outputs A19 through A0.

- Tri-State the bus control outputs /MREQ, /IORQ, /RD and /WR.

- Asserting /BUSACK

The Z8S180 regains the system bus when /BUSREQ is deactivated. The address outputs and the bus control outputs are then driven High; the STANDBY mode is exited.

If the BREXT bit of the CPU Control Register (CCR) is cleared, asserting the /BUSREQ would not cause the Z8S180 to exit STANDBY mode.

If STANDBY mode is exited due to a reset or an external interrupt, the Z8S180 remains relinquished from the system bus as long as /BUSREQ is active.

## STANDBY Mode Exit with External Interrupts

STANDBY mode can be exited by asserting input /NMI. The STANDBY mode may also exit by asserting /INT0, /INT1 or /INT2, depending on the conditions specified in the following paragraphs.

/INTO wake-up requires assertion throughout duration of clock stabilization time (2<sup>17</sup> clocks).

If exit conditions are met, the internal counter provides time for the crystal oscillator to stabilize, before the internal clocking and the system clock output within the Z8S180 are resumed.

1. Exit with Non-Maskable Interrupts

If /NMI is asserted, the CPU begins a normal NMI interrupt acknowledge sequence after clocking resumes.

2. Exit with External Maskable Interrupts

If an External Maskable Interrupt input is asserted, the CPU responds according to the status of the Global Interrupt Enable Flag IEF1 (determined by the ITE1 bit) and the settings of the corresponding interrupt enable bit in the Interrupt/Trap Control Register (ITC: I/O Address = 34H):

- **a.** If an interrupt source is disabled in the ITC, asserting the corresponding interrupt input would not cause the Z8S180 to exit STANDBY mode. This is true regardless of the state of the Global Interrupt Enable Flag IEF1.

- **b.** If the Global Interrupt Flag IEF1 is set to 1, and if an interrupt source is enabled in the ITC, asserting the corresponding interrupt input causes the Z8S180 to exit STANDBY mode. The CPU performs an interrupt acknowledge sequence appropriate to the input being asserted when clocking is resumed if:

- The interrupt input follows the normal interrupt daisy chain protocol.

- The interrupt source is active until the acknowledge cycle is completed.

- c. If the Global Interrupt Flag IEF1 is disabled, i.e., reset to 0, and if an interrupt source is enabled in the ITC, asserting the corresponding interrupt input will still cause the Z8S180 to exit STANDBY mode. The CPU will proceed to fetch and execute instructions that follow the SLEEP instruction when clocking is resumed.

If the External Maskable Interrupt input is not active until clocking resumes, the Z8S180 will not exit STANDBY mode. If the Non-Maskable Interrupt (/NMI) is not active until clocking resumes, the Z8S180 still exits the STANDBY mode even if the interrupt sources go away before the timer times out, because /NMI is edge-triggered. The condition is latched internally once /NMI is asserted Low.

## **IDLE Mode**

IDLE mode is another power-down mode offered by the Z8S180. To enter IDLE mode:

- 1. Set D6 and D3 to 0 and 1, respectively.

- 2. Set the I/O STOP bit (D5 of ICR, I/O Address = 3FH) to 1.

- **3.** Execute the SLEEP instruction.

## **CPU Control Register**

**Bit 7.** *Clock Divide Select.* Bit 7 of the CCR allows the programmer to set the internal clock to divide the external clock by 2 if the bit is 0 and divide-by-one if the bit is 1. Upon reset, this bit is set to 0 and the part is in divide-by-two mode. Since the on-board oscillator is not guaranteed to operate above 20 MHz, an external source must be used to achieve the maximum 33 MHz operation of the part, i.e., an external clock at 66 MHz with 50% duty cycle.

If an external oscillator is used in divide-by-one mode, the minimum pulse width requirement must be satisfied.

**Bits 6 and 3.** *STANDBY/IDLE Enable.* These two bits are used for enabling/disabling the IDLE and STANDBY mode.

Setting D6, D3 to 0 and 1, respectively, enables the IDLE mode. In the IDLE mode, the clock oscillator is kept oscillating but the clock to the rest of the internal circuit, including the CLKOUT, is stopped. The Z8S180 enters IDLE mode after fetching the second opcode of a SLEEP instruction, if the I/O STOP bit is set.

Setting D6, D3 to 1 and 0, respectively, enables the STANDBY mode. In the STANDBY mode, the clock oscillator is stopped completely. The Z8S180 enters STANDBY after fetching the second opcode of a SLEEP instruction, if the I/O STOP bit is set.

Setting D6, D3 to 1 and 1, respectively, enables the STANDBY-QUICK RECOVERY mode. In this mode, its operations are identical to STANDBY except that the clock

recovery is reduced to 64 clock cycles after the exit conditions are gathered. Similarly, in STANDBY mode, the Z8S180 enters STANDBY after fetching the second opcode of a SLEEP instruction, if the I/O STOP bit is set.

**Bit 5.** *BREXT.* This bit controls the ability of the Z8S180 to honor a bus request during STANDBY mode. If this bit is set to 1 and the part is in STANDBY mode, a BUSREQ is honored after the clock stabilization timer is timed out.

**Bit 4.** *LNPHI.* This bit controls the drive capability on the PHI Clock output. If this bit is set to 1, the PHI Clock output is reduced to 25% of its drive capability.

Bit 2. Reserved

**Bit 1.** *LNCPUCTL*. This bit controls the drive capability of the CPU Control pins. When this bit is set to 1, the output drive capability of the following pins is reduced to 25% of the original drive capability:

| - /BUSACK | - /MREQ  |

|-----------|----------|

| - /RD     | - /IORQ  |

| - /WR     | - /RFSH  |

| - /M1     | - /HALT  |

| - E       | - /TEND1 |

**Bit 0.** *LNAD/DATA*. This bit controls the drive capability of the Address/Data bus output drivers. If this bit is set to 1, the output drive capability of the Address and Data bus output is reduced to 25% of its original drive capability.

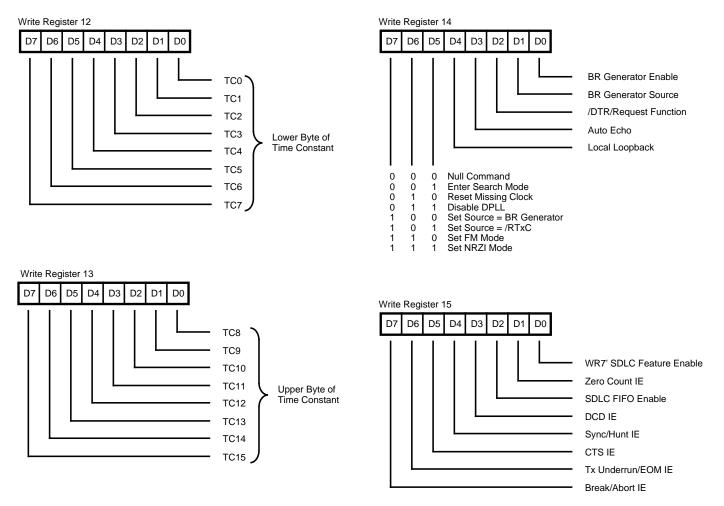

Figure 52. Write Register Bit Functions (Continued)

## CONTROL REGISTERS (Continued)

Figure 52. Write Register Bit Functions (Continued)

## **Z182 MISCELLANEOUS CONTROL AND INTERFACE REGISTERS**

Table 12b. Data Bus Direction (Z182 Bus Master)

| Interrupt Acknowledge Transaction                   |                                             |                                              |  |  |  |

|-----------------------------------------------------|---------------------------------------------|----------------------------------------------|--|--|--|

|                                                     | Intack For<br>On-Chip<br>Peripheral (IEI=1) | Intack For<br>Off-Chip<br>Peripheral (IEI=0) |  |  |  |

| Z80182/Z8L182<br>Data Bus<br>(DD <sub>ουτ</sub> =0) | Z                                           | In                                           |  |  |  |

| Z80182/Z8L182<br>Data Bus<br>(DD <sub>out</sub> =1) | Out                                         | In                                           |  |  |  |

### Table 13a. Data Bus Direction (Z80182/Z8L182 is not Bus Master)

#### I/O And Memory Transactions

| _                                                      | I/O Write<br>to On-Chip<br>Peripherals | I/O Read<br>From On-Chip<br>Peripherals | I/O Write<br>to Off-Chip<br>Peripherals | I/O Read<br>From Off-Chip<br>Peripherals | Write<br>To<br>Memory | Read<br>From<br>Mode | Refresh | Z80182<br>Idle Mode |

|--------------------------------------------------------|----------------------------------------|-----------------------------------------|-----------------------------------------|------------------------------------------|-----------------------|----------------------|---------|---------------------|

| Z80182<br>/Z8L182<br>Data Bus<br>DD <sub>out</sub> =0) |                                        | Out                                     | Z                                       | Z                                        | Z                     | In                   | Z       | Z                   |

| Z80182<br>/Z8L182<br>Data Bus<br>(DD <sub>OUT</sub> =1 |                                        | Out                                     | Z                                       | Z                                        | Z                     | In                   | Z       | Z                   |

#### Table 13b. Data Bus Direction (Z80182/Z8L182 *is not* Bus Master)

| Interrupt Acknowledge Transaction                   |                                     |                                      |  |  |

|-----------------------------------------------------|-------------------------------------|--------------------------------------|--|--|

|                                                     | Intack For<br>On-Chip<br>Peripheral | Intack For<br>Off-Chip<br>Peripheral |  |  |

| Z80182/Z8L182<br>Data Bus<br>(DD <sub>out</sub> =0) | Out                                 | In                                   |  |  |

| Z80182/Z8L182<br>Data Bus<br>(DD <sub>OUT</sub> =1) | Out                                 | In                                   |  |  |

#### Bit 0 16450 MIMIC Mode Enable

(Reset value=0) This bit = 1 will force the mimic into 16450 mode. Bit 0 in the FCR reg is forced to zero as well as the mimic internal FIFO enable. When used, this bit should be programmed at MIMIC initialization and not modified afterwards.

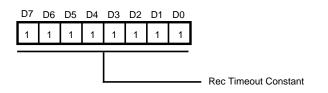

### Figure 65. Receive Timeout Timer Constant

(Z180 MPU Read/Write, Address xxEAH)

This register contains an 8-bit constant for emulation of the 16550 four character timeout feature. Software must determine the value to load into this register based on the bit rate and word length specified by the MIMIC interface with the PC. This timer receives its input from the /TRxCB Clock of the ESCC. This timer is enabled to down count when the enable bit in the FSR register is set and the trigger level interrupt has not been activated on the RCVR FIFO. The counter reloads and counts down each time there is a read or write to the RCVR FIFO.

The receive timeout timer is enhanced to emulate the actual 16550 when bit 1 of the FIFO status and control register is enabled. Under most circumstances, this register should be programmed for four character timers (40d, 8-N-1).

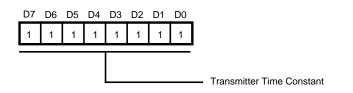

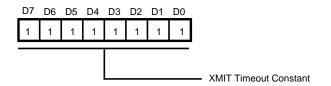

This register contains an 8-bit constant for determining the interval for the Transmit Timeout Timer. If allowed to decrement to zero, this timer interrupts the MPU by setting the THR bit in the IUS/IP register. This timer receives its input from the /TRxCB Clock of the SCC. The timer is enabled to down count when the enable bit in the FSR register is set and the trigger level has not been reached on the XMIT FIFO. The counter reloads each time there is a read or write to the XMIT FIFO.

## **Transmit And Receive Timers**

Because of the speed at which data transfers can take place between the Z180<sup>™</sup> MPU and the PC/XT/AT, two timers have been added to alleviate any software problems that a high speed parallel data transfer might cause. These timers allow the programmer to slow down the data transfer just as if the 16550 MIMIC interface had to shift the data in and out serially. The Timers receive their input from the /TRxCB Clock since, in 16550 MIMIC mode, the ESCC channel B is disabled. For example, the clock source for the 8-bit registers: RTTC (Receive Timeout Time Constant, xxEAH), TTTC (Transmit Timeout Time Constant, xxEBH), TTCR (Transmit Time Constant Register, xxFAH) and RTCR (Receive Time Constant Register, xxFBH) uses the /TRxCB Clock output. The /TRxCB Clock output needs to be generated by the ESCC's channel B's 16-bit BRG as its clock source, thus allowing the programmer to access a total of 24 bits as a timer to slow down the data transfer.

In most cases, ESCC Ch. B BRG should be programmed to output at a frequency equivalent to the desired serial transfer rate. The output of the BRG should be routed to the /TRxCB pin.

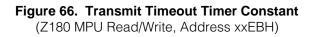

Figure 67. Transmitter Time Constant Register (Z180 MPU Read/Write, Address xxFAH)

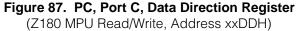

## PARALLEL PORTS REGISTERS

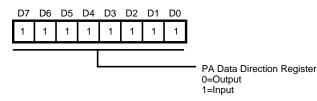

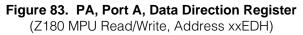

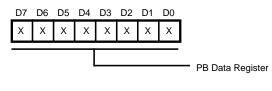

The Z80182/Z8L182 has three 8-bit bi-directional Ports. Each bit is individually programmable for input or output. The Ports consist of two registers the Port Direction Control Register and the Port Data Register. The Port and direction register can be accessed in any page of I/O space since only the lowest eight address lines are decoded. Bits PC7 and PC6 are input only bits and have the special function of reading the external value of the /INT2 and /INT1 pins. Writing '1' to these bits will clear the edge detect interrupt logic when operating /INT2 and/or /INT1 in edge detect mode.

When Port B and Port C bits 5-0 are deselected in the System Configuration Register, the Data and Data Direction Registers are still available as read/write scratch registers. If a Port is deselected and if the DDR bit is a '0', then the written value to that bit will be latched and this value can be read back. If a Port is deselected and if the DDR bit is a '1', then you could read only the external pin value; any write to that bit is latched but can be read back only with DDR=0.

The data direction register determines which are inputs and outputs in the PA Data Register. When a bit is set to 1 the corresponding bit in the PA Data Register is an input. If the bit is 0, then the corresponding bit is an output.

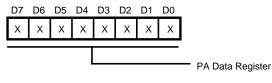

**Figure 84. PA, Port A, Data Register** (Z180 MPU Read/Write, Address xxEEH)

When the Z180 MPU writes to the PA Data Register the

data is stored in the internal buffer. The values of the PA Data Register are undefined after reset. Any bits that are output are then sent on to the output buffers.

When the Z180 MPU reads the PA Data Register the data on the external pins is returned.

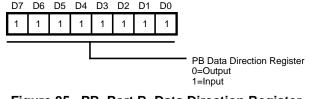

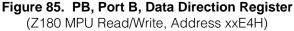

The data direction register determines which are inputs and outputs in the PB Data Register. When a bit is set to 1 the corresponding bit in the PB Data Register is an input. If the bit is 0 then the corresponding bit is an output.

Figure 86. PB, Port B, Data Register

(Z180 MPU, Address xxE5H)

When the Z180 MPU writes to the PB Data Register the data is stored in the internal buffer. The values of Port B data register are undefined after reset. Any bits that are output are then sent on to the output buffers.

When the Z180 MPU reads the PB Data Register, the data on the external pins is returned.

## **EMULATION MODES** (Continued)

#### Table 21. Emulation Mode 1

| Signal                   | Normal<br>Mode 0 | Emulation Adaptor<br>Mode 1 |

|--------------------------|------------------|-----------------------------|

| PHI                      | Output           | Input                       |

| /M1                      | Output           | Input                       |

| /MREQ,/MRD               | Output           | Input                       |

| /IORQ                    | Output           | Input                       |

| /RD                      | Output           | Input                       |

| /WR                      | Output           | Input                       |

| /RFSH                    | Output           | Input                       |

| /HALT                    | Output           | Input                       |

| ST                       | Output           | Input                       |

| E                        | Output           | Tri-state                   |

| /BUSACK                  | Output           | Input                       |

| /WAIT                    | Input            | Output                      |

| A19,A18/T <sub>out</sub> | Output           | Input                       |

| A17-A0                   | Output           | Input                       |

| D7-D0                    | Input/Output     | Input/Output                |

| TxA0                     | Output           | Tri-state                   |

| /RTS0                    | Output           | Tri-state                   |

| TxA1                     | Output           | Tri-state                   |

| /INTO                    | Input            | Output, Open-Drain          |

## Mode 2 Emulation Probe Mode

In the Emulator Probe Mode all of the Z182 output signals are tri-state. This scheme allows a Z182 emulator probe to grab on to the Z182 package leads on the target system.

### Mode 3 RESERVED (for test purposes only)

This mode is reserved for test purpose only, do not use.

#### Notes:

Z182 has two branches of reset. /RESET controls the Z182 overall configuration, RAM and ROM boundaries, plus the ESCC, Port and the 16550 MIMIC interface. In Normal Mode, a "one shot" circuit samples the input of the /RESET pin to assert the internal reset to its proper duration. In Adapter Mode, this "one shot" circuit is bypassed. Note also that the Z180's crystal oscillator is disabled in Mode 1 and Mode 2.

In Mode 1 the emulator must provide /MREQ on the (/MREQ,/MRD) Z80182/Z8L182 pin (not /MRD); and A18 (not  $T_{out}$ ) on the A18/T<sub>out</sub> pin.

## SLEEP, HALT EFFECT ON MIMIC AND 182 SIGNALS

The following Z80182/Z8L182 signals are driven High when Z180<sup>™</sup> MPU enters a SLEEP or HALT state:

- /MRD when selected in the Interrupt Edge/Pin MUX Register.

- /MWR when selected in the Interrupt Edge/Pin MUX Register.

- /ROMCS,/RAMCS always High in SLEEP or HALT.

The following signals are High-Z during SLEEP and HALT:

- /IOCS when so selected in the Interrupt Edge/Pin MUX Register.

- /RD and /WR.

A0-A19 (A18 if selected) always High-Z in power down.

D0-D7 always High-Z in power down modes.

The MIMIC logic of the 182 is disabled during power down modes of the Z180.

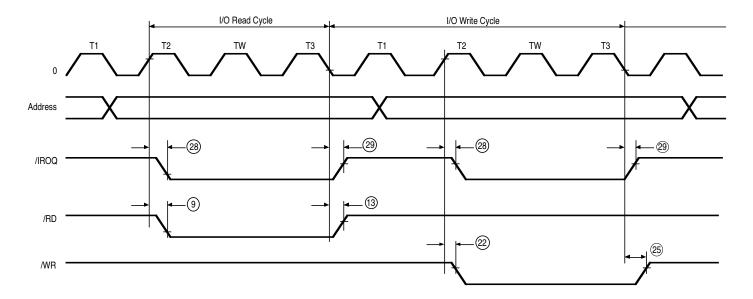

DMA Control Signals [1] tDRQS and tDRQH are specified for the rising edge of clock followed by T3.

[2] tDRQS and tDRQH are specified for the rising edge of clock.[3] DMA cycle starts.

[4] CPU cycle starts.

#### Figure 93. DMA Control Signals

## PS009801-0301

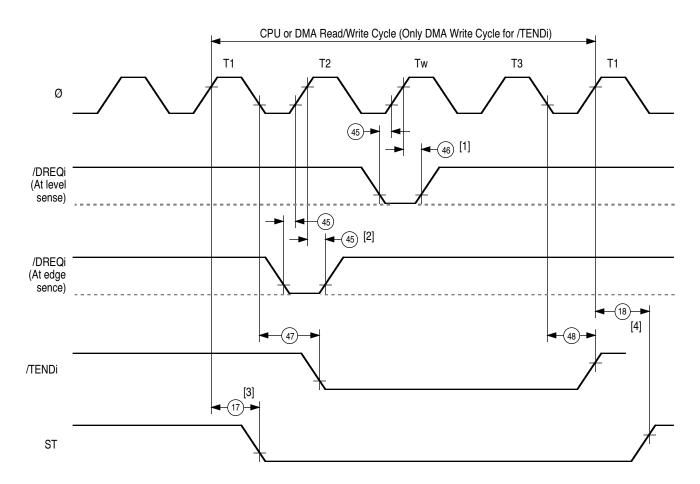

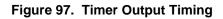

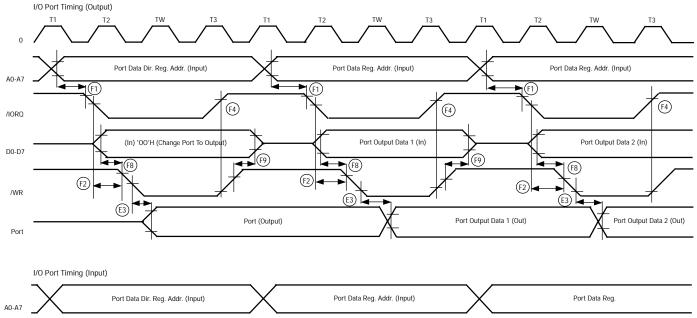

## General-Purpose I/O Port Timing

This figure shows the timing for the Ports A, B and C. Parameters referred to in this figure appear in Tables D and E.

Figure 107. PORT Timing

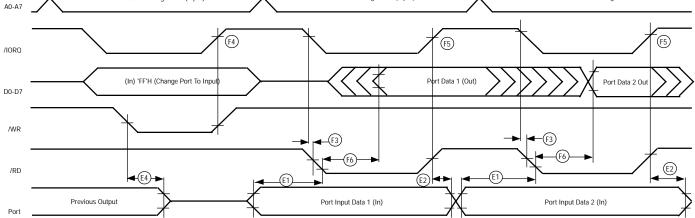

## **Read Write External Bus Master Timing**

Figure 108. Read/Write External Bus Master Timing

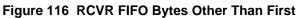

| Table L. | Interrupt | Timing | Transmitter | FIFO |

|----------|-----------|--------|-------------|------|

|----------|-----------|--------|-------------|------|

|     |      |                                                          | Z8L<br>20 N           |                         | Z80182<br>33 MHz     |                         |  |

|-----|------|----------------------------------------------------------|-----------------------|-------------------------|----------------------|-------------------------|--|

| No. | Sym  | Parameter                                                | Min                   | Max                     | Min                  | Max                     |  |

| 16  | tHR  | Delay from /WR<br>(WR THR) to Reset<br>Interrupt         |                       | 2.5 MPU<br>Clock Cycles |                      | 2.5 MPU<br>Clock Cycles |  |

| 17  | TSTI | Delay from Stop to<br>Interrupt (THRE)                   | 2 MPU<br>Clock Cycles |                         | 2 MPU<br>Clock Cycle | es                      |  |

| 18  | TIR  | Delay from /RD<br>(RD IIR) to Reset<br>Interrupt (THRIE) |                       | 75                      |                      | 75                      |  |

PS009801-0301

## **PACKAGE INFORMATION** (Continued)