# E·XFL

#### AMD Xilinx - XC5204-6VQ100C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                   |

|--------------------------------|------------------------------------------------------------|

| Number of LABs/CLBs            | 120                                                        |

| Number of Logic Elements/Cells | 480                                                        |

| Total RAM Bits                 | -                                                          |

| Number of I/O                  | 81                                                         |

| Number of Gates                | 6000                                                       |

| Voltage - Supply               | 4.75V ~ 5.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 100-TQFP                                                   |

| Supplier Device Package        | 100-VQFP (14x14)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc5204-6vq100c |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

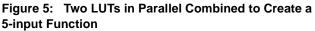

single-length lines, double-length lines, and Longlines all routed through the GRM. The direct connects, LIM, and logic-cell feedthrough are contained within each Versa-Block. Throughout the XC5200 interconnect, an efficient multiplexing scheme, in combination with three layer metal (TLM), was used to improve the overall efficiency of silicon usage.

#### **Performance Overview**

The XC5200 family has been benchmarked with many designs running synchronous clock rates beyond 66 MHz. The performance of any design depends on the circuit to be implemented, and the delay through the combinatorial and sequential logic elements, plus the delay in the interconnect routing. A rough estimate of timing can be made by assuming 3-6 ns per logic level, which includes direct-connect routing delays, depending on speed grade. More accurate estimations can be made using the information in the Switching Characteristic Guideline section.

#### Taking Advantage of Reconfiguration

FPGA devices can be reconfigured to change logic function while resident in the system. This capability gives the system designer a new degree of freedom not available with any other type of logic.

Hardware can be changed as easily as software. Design updates or modifications are easy, and can be made to products already in the field. An FPGA can even be reconfigured dynamically to perform different functions at different times.

Reconfigurable logic can be used to implement system self-diagnostics, create systems capable of being reconfigured for different environments or operations, or implement multi-purpose hardware for a given application. As an added benefit, using reconfigurable FPGA devices simplifies hardware design and debugging and shortens product time-to-market.

### **Detailed Functional Description**

#### **Configurable Logic Blocks (CLBs)**

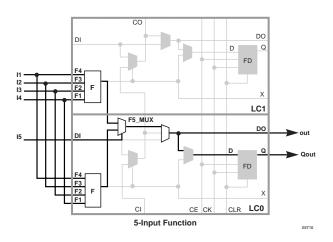

Figure 4 shows the logic in the XC5200 CLB, which consists of four Logic Cells (LC[3:0]). Each Logic Cell consists of an independent 4-input Lookup Table (LUT), and a D-Type flip-flop or latch with common clock, clock enable, and clear, but individually selectable clock polarity. Additional logic features provided in the CLB are:

- An independent 5-input LUT by combining two 4-input LUTs.

- High-speed carry propagate logic.

- High-speed pattern decoding.

- High-speed direct connection to flip-flop D-inputs.

- Individual selection of either a transparent, level-sensitive latch or a D flip-flop.

- Four 3-state buffers with a shared Output Enable.

#### **5-Input Functions**

Figure 5 illustrates how the outputs from the LUTs from LC0 and LC1 can be combined with a 2:1 multiplexer (F5\_MUX) to provide a 5-input function. The outputs from the LUTs of LC2 and LC3 can be similarly combined.

**∑**XILINX<sup>®</sup>

Figure 17: Detail of Programmable Interconnect Associated with XC5200 Series CLB

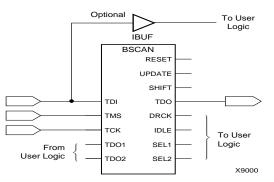

Figure 20: Boundary Scan Schematic Example

Even if the boundary scan symbol is used in a schematic, the input pins TMS, TCK, and TDI can still be used as inputs to be routed to internal logic. Care must be taken not to force the chip into an undesired boundary scan state by inadvertently applying boundary scan input patterns to these pins. The simplest way to prevent this is to keep TMS High, and then apply whatever signal is desired to TDI and TCK.

#### **Avoiding Inadvertent Boundary Scan**

If TMS or TCK is used as user I/O, care must be taken to ensure that at least one of these pins is held constant during configuration. In some applications, a situation may occur where TMS or TCK is driven during configuration. This may cause the device to go into boundary scan mode and disrupt the configuration process.

To prevent activation of boundary scan during configuration, do either of the following:

- TMS: Tie High to put the Test Access Port controller in a benign RESET state

- TCK: Tie High or Low—do not toggle this clock input.

For more information regarding boundary scan, refer to the Xilinx Application Note XAPP 017, "*Boundary Scan in XC4000 and XC5200 Devices.*"

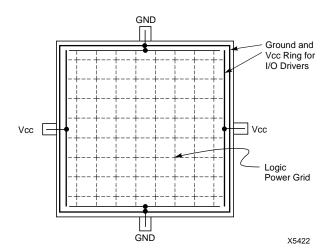

### **Power Distribution**

Power for the FPGA is distributed through a grid to achieve high noise immunity and isolation between logic and I/O. Inside the FPGA, a dedicated Vcc and Ground ring surrounding the logic array provides power to the I/O drivers, as shown in Figure 21. An independent matrix of Vcc and Ground lines supplies the interior logic of the device.

This power distribution grid provides a stable supply and ground for all internal logic, providing the external package power pins are all connected and appropriately decoupled.

#### **XC5200 Series Field Programmable Gate Arrays**

Typically, a 0.1  $\mu\text{F}$  capacitor connected near the Vcc and Ground pins of the package will provide adequate decoupling.

Output buffers capable of driving/sinking the specified 8 mA loads under specified worst-case conditions may be capable of driving/sinking up to 10 times as much current under best case conditions.

Noise can be reduced by minimizing external load capacitance and reducing simultaneous output transitions in the same direction. It may also be beneficial to locate heavily loaded output buffers near the Ground pads. The I/O Block output buffers have a slew-rate limited mode (default) which should be used where output rise and fall times are not speed-critical.

Figure 21: XC5200-Series Power Distribution

### **Pin Descriptions**

There are three types of pins in the XC5200-Series devices:

- · Permanently dedicated pins

- User I/O pins that can have special functions

- Unrestricted user-programmable I/O pins.

Before and during configuration, all outputs not used for the configuration process are 3-stated and pulled high with a 20 k $\Omega$  - 100 k $\Omega$  pull-up resistor.

After configuration, if an IOB is unused it is configured as an input with a 20 k $\Omega$  - 100 k $\Omega$  pull-up resistor.

Device pins for XC5200-Series devices are described in Table 9. Pin functions during configuration for each of the seven configuration modes are summarized in "Pin Func-

tions During Configuration" on page 124, in the "Configuration Timing" section.

**Table 9: Pin Descriptions**

| Pin Name<br>Permanently I | I/O<br>During<br>Config.<br>Dedicated | I/O<br>After<br>Config.<br>I Pins | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------|---------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC                       | I                                     | 1                                 | Five or more (depending on package) connections to the nominal +5 V supply voltage. All must be connected, and each must be decoupled with a 0.01 - 0.1 $\mu$ F capacitor to Ground.                                                                                                                                                                                                                                                                                                                                                            |

| GND                       | I                                     | I                                 | Four or more (depending on package type) connections to Ground. All must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CCLK                      | l or O                                | I                                 | During configuration, Configuration Clock (CCLK) is an output in Master modes or Asyn-<br>chronous Peripheral mode, but is an input in Slave mode, Synchronous Peripheral<br>mode, and Express mode. After configuration, CCLK has a weak pull-up resistor and<br>can be selected as the Readback Clock. There is no CCLK High time restriction on<br>XC5200-Series devices, except during Readback. See "Violating the Maximum High<br>and Low Time Specification for the Readback Clock" on page 113 for an explanation of<br>this exception. |

| DONE                      | I/O                                   | 0                                 | DONE is a bidirectional signal with an optional internal pull-up resistor. As an output, it indicates the completion of the configuration process. As an input, a Low level on DONE can be configured to delay the global logic initialization and the enabling of outputs.<br>The exact timing, the clock source for the Low-to-High transition, and the optional pull-up resistor are selected as options in the program that creates the configuration bit-stream. The resistor is included by default.                                      |

| PROGRAM                   | I                                     | I                                 | PROGRAM is an active Low input that forces the FPGA to clear its configuration mem-<br>ory. It is used to initiate a configuration cycle. When PROGRAM goes High, the FPGA<br>executes a complete clear cycle, before it goes into a WAIT state and releases INIT.<br>The PROGRAM pin has an optional weak pull-up after configuration.                                                                                                                                                                                                         |

| User I/O Pins             | That Can                              | Have Sp                           | ecial Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RDY/BUSY                  | 0                                     | I/O                               | During Peripheral mode configuration, this pin indicates when it is appropriate to write<br>another byte of data into the FPGA. The same status is also available on D7 in Asyn-<br>chronous Peripheral mode, if a read operation is performed when the device is selected.<br>After configuration, RDY/BUSY is a user-programmable I/O pin.<br>RDY/BUSY is pulled High with a high-impedance pull-up prior to INIT going High.                                                                                                                 |

| RCLK                      | 0                                     | I/O                               | During Master Parallel configuration, each change on the A0-A17 outputs is preceded<br>by a rising edge on RCLK, a redundant output signal. RCLK is useful for clocked<br>PROMs. It is rarely used during configuration. After configuration, RCLK is a user-pro-<br>grammable I/O pin.                                                                                                                                                                                                                                                         |

| M0, M1, M2                | I                                     | I/O                               | As Mode inputs, these pins are sampled before the start of configuration to determine the configuration mode to be used. After configuration, M0, M1, and M2 become user-programmable I/O. During configuration, these pins have weak pull-up resistors. For the most popular configuration mode, Slave Serial, the mode pins can thus be left unconnected. A pull-down resistor value of 3.3 k $\Omega$ is recommended for other modes.                                                                                                        |

| TDO                       | 0                                     | 0                                 | If boundary scan is used, this pin is the Test Data Output. If boundary scan is not used, this pin is a 3-state output, after configuration is completed.<br>This pin can be user output only when called out by special schematic definitions. To use this pin, place the library component TDO instead of the usual pad symbol. An output buffer must still be used.                                                                                                                                                                          |

**∑**XILINX<sup>®</sup>

### XC5200 Series Field Programmable Gate Arrays

#### Table 9: Pin Descriptions (Continued)

|                                   | l/O<br>During   | I/O<br>After          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------|-----------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                          | Config.         | Config.               | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TDI, TCK,<br>TMS                  | I               | I/O<br>or I<br>(JTAG) | If boundary scan is used, these pins are Test Data In, Test Clock, and Test Mode Select<br>inputs respectively. They come directly from the pads, bypassing the IOBs. These pins<br>can also be used as inputs to the CLB logic after configuration is completed.<br>If the BSCAN symbol is not placed in the design, all boundary scan functions are inhib<br>ited once configuration is completed, and these pins become user-programmable I/O.<br>In this case, they must be called out by special schematic definitions. To use these pins<br>place the library components TDI, TCK, and TMS instead of the usual pad symbols. In<br>put or output buffers must still be used. |

| HDC                               | Ο               | I/O                   | High During Configuration (HDC) is driven High until the I/O go active. It is available as a control output indicating that configuration is not yet completed. After configuration, HDC is a user-programmable I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LDC                               | 0               | I/O                   | Low During Configuration (LDC) is driven Low until the I/O go active. It is available as a<br>control output indicating that configuration is not yet completed. After configuration, LDC is a user-programmable I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ĪNĪT                              | I/O             | I/O                   | Before and during configuration, INIT is a bidirectional signal. A 1 k $\Omega$ - 10 k $\Omega$ externational pull-up resistor is recommended.<br>As an active-Low open-drain output, INIT is held Low during the power stabilization and internal clearing of the configuration memory. As an active-Low input, it can be used to hold the FPGA in the internal WAIT state before the start of configuration. Master mode devices stay in a WAIT state an additional 50 to 250 µs after INIT has gone High. During configuration, a Low on this output indicates that a configuration data error has occurred. After the I/O go active, INIT is a user-programmable I/O pin.      |

| GCK1 -<br>GCK4                    | Weak<br>Pull-up | l or I/O              | Four Global inputs each drive a dedicated internal global net with short delay and mir<br>imal skew. These internal global nets can also be driven from internal logic. If not used<br>to drive a global net, any of these pins is a user-programmable I/O pin.<br>The GCK1-GCK4 pins provide the shortest path to the four Global Buffers. Any input<br>pad symbol connected directly to the input of a BUFG symbol is automatically placed or<br>one of these pins.                                                                                                                                                                                                              |

| <u>CS0,</u> <u>CS1,</u><br>WS, RS | I               | I/O                   | These four inputs are used in Asynchronous Peripheral mode. The chip is selected when CS0 is Low and CS1 is High. While the chip is selected, a Low on Write Strobe (WS) loads the data present on the D0 - D7 inputs into the internal data buffer. A Low on Read Strobe (RS) changes D7 into a status output — High if Ready, Low if Busy – and drives D0 - D6 High.<br>In Express mode, CS1 is used as a serial-enable signal for daisy-chaining.<br>WS and RS should be mutually exclusive, but if both are Low simultaneously, the Writ Strobe overrides. After configuration, these are user-programmable I/O pins.                                                          |

| A0 - A17                          | 0               | I/O                   | During Master Parallel configuration, these 18 output pins address the configuration EPROM. After configuration, they are user-programmable I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D0 - D7                           | I               | I/O                   | During Master Parallel, Peripheral, and Express configuration, these eight input pins receive configuration data. After configuration, they are user-programmable I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DIN                               | I               | I/O                   | During Slave Serial or Master Serial configuration, DIN is the serial configuration data input receiving data on the rising edge of CCLK. During Parallel configuration, DIN is the D0 input. After configuration, DIN is a user-programmable I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DOUT                              | 0               | I/O                   | During configuration in any mode but Express mode, DOUT is the serial configuration data output that can drive the DIN of daisy-chained slave FPGAs. DOUT data change on the falling edge of CCLK.<br>In Express mode, DOUT is the status output that can drive the CS1 of daisy-chained FPGAs, to enable and disable downstream devices.<br>After configuration, DOUT is a user-programmable I/O pin.                                                                                                                                                                                                                                                                             |

#### **Master Serial Mode**

In Master Serial mode, the CCLK output of the lead FPGA drives a Xilinx Serial PROM that feeds the FPGA DIN input. Each rising edge of the CCLK output increments the Serial PROM internal address counter. The next data bit is put on the SPROM data output, connected to the FPGA DIN pin. The lead FPGA accepts this data on the subsequent rising CCLK edge.

The lead FPGA then presents the preamble data—and all data that overflows the lead device—on its DOUT pin. There is an internal pipeline delay of 1.5 CCLK periods, which means that DOUT changes on the falling CCLK edge, and the next FPGA in the daisy chain accepts data on the subsequent rising CCLK edge.

In the bitstream generation software, the user can specify Fast ConfigRate, which, starting several bits into the first frame, increases the CCLK frequency by a factor of twelve. The value increases from a nominal 1 MHz, to a nominal 12 MHz. Be sure that the serial PROM and slaves are fast enough to support this data rate. The Medium ConfigRate option changes the frequency to a nominal 6 MHz. XC2000, XC3000/A, and XC3100A devices do not support the Fast or Medium ConfigRate options.

The SPROM CE input can be driven from either LDC or DONE. Using LDC avoids potential contention on the DIN pin, if this pin is configured as user-I/O, but LDC is then restricted to be a permanently High user output after configuration. Using DONE can also avoid contention on DIN, provided the DONE before I/O enable option is invoked.

Figure 28 on page 114 shows a full master/slave system. The leftmost device is in Master Serial mode.

Master Serial mode is selected by a <000> on the mode pins (M2, M1, M0).

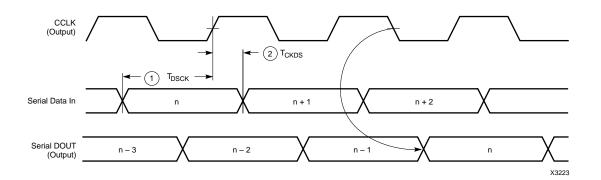

|      | Description | \$ | Symbol            | Min | Max | Units |

|------|-------------|----|-------------------|-----|-----|-------|

| CCLK | DIN setup   | 1  | т <sub>рск</sub>  | 20  |     | ns    |

| COLK | DIN hold    | 2  | T <sub>CKDS</sub> | 0   |     | ns    |

Notes: 1. At power-up, Vcc must rise from 2.0 V to Vcc min in less than 25 ms, otherwise delay configuration by pulling PROGRAM Low until Vcc is valid.

2. Master Serial mode timing is based on testing in slave mode.

#### Figure 30: Master Serial Mode Programming Switching Characteristics

In the two Master Parallel modes, the lead FPGA directly addresses an industry-standard byte-wide EPROM, and accepts eight data bits just before incrementing or decrementing the address outputs.

The eight data bits are serialized in the lead FPGA, which then presents the preamble data—and all data that overflows the lead device—on its DOUT pin. There is an internal delay of 1.5 CCLK periods, after the rising CCLK edge that accepts a byte of data (and also changes the EPROM address) until the falling CCLK edge that makes the LSB (D0) of this byte appear at DOUT. This means that DOUT changes on the falling CCLK edge, and the next FPGA in the daisy chain accepts data on the subsequent rising CCLK edge. The PROM address pins can be incremented or decremented, depending on the mode pin settings. This option allows the FPGA to share the PROM with a wide variety of microprocessors and microcontrollers. Some processors must boot from the bottom of memory (all zeros) while others must boot from the top. The FPGA is flexible and can load its configuration bitstream from either end of the memory.

Master Parallel Up mode is selected by a <100> on the mode pins (M2, M1, M0). The EPROM addresses start at 00000 and increment.

Master Parallel Down mode is selected by a <110> on the mode pins. The EPROM addresses start at 3FFFF and decrement.

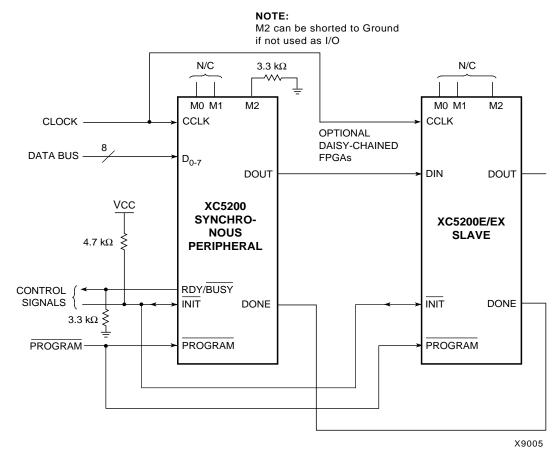

#### Synchronous Peripheral Mode

Synchronous Peripheral mode can also be considered Slave Parallel mode. An external signal drives the CCLK input(s) of the FPGA(s). The first byte of parallel configuration data must be available at the Data inputs of the lead FPGA a short setup time before the rising CCLK edge. Subsequent data bytes are clocked in on every eighth consecutive rising CCLK edge.

The same CCLK edge that accepts data, also causes the RDY/BUSY output to go High for one CCLK period. The pin name is a misnomer. In Synchronous Peripheral mode it is really an ACKNOWLEDGE signal. Synchronous operation does not require this response, but it is a meaningful signal

for test purposes. Note that RDY/BUSY is pulled High with a high-impedance pullup prior to INIT going High.

The lead FPGA serializes the data and presents the preamble data (and all data that overflows the lead device) on its DOUT pin. There is an internal delay of 1.5 CCLK periods, which means that DOUT changes on the falling CCLK edge, and the next FPGA in the daisy chain accepts data on the subsequent rising CCLK edge.

In order to complete the serial shift operation, 10 additional CCLK rising edges are required after the last data byte has been loaded, plus one more CCLK cycle for each daisy-chained device.

Synchronous Peripheral mode is selected by a <011> on the mode pins (M2, M1, M0).

Figure 33: Synchronous Peripheral Mode Circuit Diagram

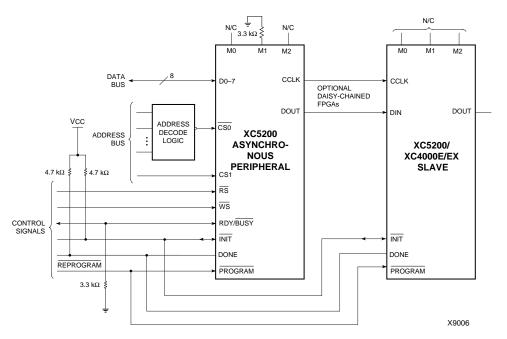

#### **Asynchronous Peripheral Mode**

#### Write to FPGA

Asynchronous Peripheral mode uses the trailing edge of the logic AND condition of WS and CS0 being Low and RS and CS1 being High to accept byte-wide data from a microprocessor bus. In the lead FPGA, this data is loaded into a double-buffered UART-like parallel-to-serial converter and is serially shifted into the internal logic.

The lead FPGA presents the preamble data (and all data that overflows the lead device) on its DOUT pin. The RDY/BUSY output from the lead FPGA acts as a hand-shake signal to the microprocessor. RDY/BUSY goes Low when a byte has been received, and goes High again when the byte-wide input buffer has transferred its information into the shift register, and the buffer is ready to receive new data. A new write may be started immediately, as soon as the RDY/BUSY output has gone Low, acknowledging receipt of the previous data. Write may not be terminated until RDY/BUSY is High again for one CCLK period. Note that RDY/BUSY is pulled High with a high-impedance pull-up prior to INIT going High.

The length of the BUSY signal depends on the activity in the UART. If the shift register was empty when the new byte was received, the BUSY signal lasts for only two CCLK periods. If the shift register was still full when the new byte was received, the BUSY signal can be as long as nine CCLK periods.

Note that after the last byte has been entered, only seven of its bits are shifted out. CCLK remains High with DOUT equal to bit 6 (the next-to-last bit) of the last byte entered. The READY/BUSY handshake can be ignored if the delay from any one Write to the end of the next Write is guaranteed to be longer than 10 CCLK periods.

#### Status Read

The logic AND condition of the  $\overline{CS0}$ , CS1 and  $\overline{RS}$  inputs puts the device status on the Data bus.

- D7 High indicates Ready

- D7 Low indicates Busy

- D0 through D6 go unconditionally High

It is mandatory that the whole start-up sequence be started and completed by one byte-wide input. Otherwise, the pins used as Write Strobe or Chip Enable might become active outputs and interfere with the final byte transfer. If this transfer does not occur, the start-up sequence is not completed all the way to the finish (point F in Figure 25 on page 109).

In this case, at worst, the internal reset is not released. At best, Readback and Boundary Scan are inhibited. The length-count value, as generated by the software, ensures that these problems never occur.

Although RDY/BUSY is brought out as a separate signal, microprocessors can more easily read this information on one of the data lines. For this purpose, D7 represents the RDY/BUSY status when RS is Low, WS is High, and the two chip select lines are both active.

Asynchronous Peripheral mode is selected by a <101> on the mode pins (M2, M1, M0).

Figure 35: Asynchronous Peripheral Mode Circuit Diagram

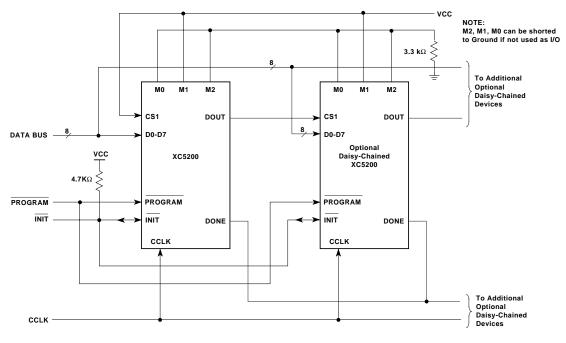

#### **Express Mode**

Express mode is similar to Slave Serial mode, except that data is processed one byte per CCLK cycle instead of one bit per CCLK cycle. An external source is used to drive CCLK, while byte-wide data is loaded directly into the configuration data shift registers. A CCLK frequency of 10 MHz is equivalent to an 80 MHz serial rate, because eight bits of configuration data are loaded per CCLK cycle. Express mode does not support CRC error checking, but does support constant-field error checking.

In Express mode, an external signal drives the CCLK input of the FPGA device. The first byte of parallel configuration data must be available at the D inputs of the FPGA a short setup time before the second rising CCLK edge. Subsequent data bytes are clocked in on each consecutive rising CCLK edge.

If the first device is configured in Express mode, additional devices may be daisy-chained only if every device in the chain is also configured in Express mode. CCLK pins are tied together and D0-D7 pins are tied together for all devices along the chain. A status signal is passed from DOUT to CS1 of successive devices along the chain. The lead device in the chain has its CS1 input tied High (or floating, since there is an internal pullup). Frame data is accepted only when CS1 is High and the device's configu-

ration memory is not already full. The status <u>pin</u> DOUT is pulled Low two internal-oscillator cycles after INIT is recognized as High, and remains Low until the device's configuration memory is full. DOUT is then pulled High to signal the next device in the chain to accept the configuration data on the D0-D7 bus.

The DONE pins of all devices in the chain should be tied together, with one or more active internal pull-ups. If a large number of devices are included in the chain, deactivate some of the internal pull-ups, since the Low-driving DONE pin of the last device in the chain must sink the current from all pull-ups in the chain. The DONE pull-up is activated by default. It can be deactivated using an option in the bitstream generation software.

XC5200 devices in Express mode are always synchronized to DONE. The device becomes active after DONE goes High. DONE is an open-drain output. With the DONE pins tied together, therefore, the external DONE signal stays low until all devices are configured, then all devices in the daisy chain become active simultaneously. If the DONE pin of a device is left unconnected, the device becomes active as soon as that device has been configured.

Express mode is selected by a <010> on the mode pins (M2, M1, M0).

X6611\_01

Figure 37: Express Mode Circuit Diagram

#### **Pin Functions During Configuration** Table 13.

|                  | 1                     |                       |                        | <m2:m1:m0></m2:m1:m0>  |                       | [                  | USER      |

|------------------|-----------------------|-----------------------|------------------------|------------------------|-----------------------|--------------------|-----------|

| SLAVE<br><1:1:1> | MASTER-SER<br><0:0:0> | SYN.PERIPH<br><0:1:1> | ASYN.PERIPH<br><1:0:1> | MASTER-HIGH<br><1:1:0> | MASTER-LOW<br><1:0:0> | EXPRESS<br><0:1:0> | OPERATION |

|                  |                       |                       |                        | A16                    | A16                   |                    | GCK1-I/O  |

|                  |                       |                       |                        | A17                    | A17                   |                    | I/O       |

| TDI              | TDI                   | TDI                   | TDI                    | TDI                    | TDI                   | TDI                | TDI-I/O   |

| TCK              | TCK                   | TCK                   | TCK                    | TCK                    | TCK                   | TCK                | TCK-I/O   |

| TMS              | TMS                   | TMS                   | TMS                    | TMS                    | TMS                   | TMS                | TMS-I/O   |

|                  |                       |                       |                        |                        |                       |                    | I/O       |

| M1 (HIGH) (I)    | M1 (LOW) (I)          | M1 (HIGH) (I)         | M1 (LOW) (I)           | M1 (HIGH) (I)          | M1 (LOW) (I)          | M1 (HIGH) (I)      | I/O       |

| M0 (HIGH) (I)    | M0 (LOW) (I)          | M0 (HIGH) (I)         | M0 (HIGH) (I)          | M0 (LOW) (I)           | M0 (LOW) (I)          | M0 (LOW) (I)       | I/O       |

| M2 (HIGH) (I)    | M2 (LOW) (I)          | M2 (LOW) (I)          | M2 (HIGH) (I)          | M2 (HIGH) (I)          | M2 (HIGH) (I)         | M2 (LOW) (I)       | I/O       |

|                  |                       |                       |                        |                        |                       |                    | GCK2-I/O  |

| HDC (HIGH)       | HDC (HIGH)            | HDC (HIGH)            | HDC (HIGH)             | HDC (HIGH)             | HDC (HIGH)            | HDC (HIGH)         | I/O       |

| LDC (LOW)        | LDC (LOW)             | LDC (LOW)             | LDC (LOW)              | LDC (LOW)              | LDC (LOW)             | LDC (LOW)          | I/O       |

| INIT-ERROR       | INIT-ERROR            | INIT-ERROR            | INIT-ERROR             | INIT-ERROR             | INIT-ERROR            | INIT-ERROR         | I/O       |

|                  |                       |                       |                        |                        |                       |                    | I/O       |

| DONE             | DONE                  | DONE                  | DONE                   | DONE                   | DONE                  | DONE               | DONE      |

| PROGRAM (I)      | PROGRAM (I)           | PROGRAM (I)           | PROGRAM (I)            | PROGRAM (I)            | PROGRAM (I)           | PROGRAM (I)        | PROGRAM   |

|                  |                       | DATA 7 (I)            | DATA 7 (I)             | DATA 7 (I)             | DATA 7 (I)            | DATA 7 (I)         | I/O       |

|                  |                       |                       |                        |                        |                       |                    | GCK3-I/O  |

|                  |                       | DATA 6 (I)            | DATA 6 (I)             | DATA 6 (I)             | DATA 6 (I)            | DATA 6 (I)         | I/O       |

|                  |                       | DATA 5 (I)            | DATA 5 (I)             | DATA 5 (I)             | DATA 5 (I)            | DATA 5 (I)         | I/O       |

|                  |                       |                       | CSO (I)                |                        |                       |                    | I/O       |

|                  |                       | DATA 4 (I)            | DATA 4 (I)             | DATA 4 (I)             | DATA 4 (I)            | DATA 4 (I)         | I/O       |

|                  |                       | DATA 3 (I)            | DATA 3 (I)             | DATA 3 (I)             | DATA 3 (I)            | DATA 3 (I)         | I/O       |

|                  |                       |                       | RS (I)                 |                        |                       |                    | I/O       |

|                  |                       | DATA 2 (I)            | DATA 2 (I)             | DATA 2 (I)             | DATA 2 (I)            | DATA 2 (I)         | I/O       |

|                  |                       | DATA 1 (I)            | DATA 1 (I)             | DATA 1 (I)             | DATA 1 (I)            | DATA 1 (I)         | I/O       |

|                  |                       | RDY/BUSY              | RDY/BUSY               | RCLK                   | RCLK                  |                    | I/O       |

| DIN (I)          | DIN (I)               | DATA 0 (I)            | DATA 0 (I)             | DATA 0 (I)             | DATA 0 (I)            | DATA 0 (I)         | I/O       |

| DOUT             | DOUT                  | DOUT                  | DOUT                   | DOUT                   | DOUT                  | DOUT               | I/O       |

| CCLK (I)         | CCLK (O)              | CCLK (I)              | CCLK (O)               | CCLK (O)               | CCLK (O)              | CCLK (I)           | CCLK (I)  |

| TDO              | TDO                   | TDO                   | TDO                    | TDO                    | TDO                   | TDO                | TDO-I/O   |

|                  |                       |                       | WS (I)                 | A0                     | A0                    |                    | I/O       |

|                  |                       |                       | 1                      | A1                     | A1                    |                    | GCK4-I/O  |

|                  |                       |                       | CS1 (I)                | A2                     | A2                    | CS1 (I)            | I/O       |

|                  |                       |                       |                        | A3                     | A3                    |                    | I/O       |

|                  |                       |                       |                        | A4                     | A4                    |                    | I/O       |

|                  |                       |                       |                        | A5                     | A5                    |                    | I/O       |

|                  |                       |                       |                        | A6                     | A6                    |                    | I/O       |

|                  |                       |                       |                        | A7                     | A7                    |                    | I/O       |

|                  |                       |                       |                        | A8                     | A8                    |                    | I/O       |

|                  |                       |                       |                        | A9                     | A9                    |                    | I/O       |

|                  |                       |                       |                        | A10                    | A10                   |                    | I/O       |

|                  |                       |                       |                        | A11                    | A11                   |                    | I/O       |

|                  |                       |                       |                        | A12                    | A12                   |                    | I/O       |

|                  |                       |                       |                        | A13                    | A13                   |                    | I/O       |

|                  |                       |                       |                        | A14                    | A14                   |                    | I/O       |

|                  |                       |                       |                        | A15                    | A15                   |                    | I/O       |

|                  |                       |                       |                        |                        |                       |                    | ALL OTHER |

Notes: 1. A shaded table cell represents a 20-kΩ to 100-kΩ pull-up resistor before and during configuration.

2. (I) represents an input (O) represents an output.

3. INIT is an open-drain output during configuration.

#### **XC5200 CLB Switching Characteristic Guidelines**

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark timing patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more detailed, more precise, and more up-to-date timing information, use the values provided by the timing calculator and used in the simulator.

| Speed                                       | d Grade            | -           | ·6          | -           | -5          |             | 4           | -:          | 3           |

|---------------------------------------------|--------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Description                                 | Symbol             | Min<br>(ns) | Max<br>(ns) | Min<br>(ns) | Max<br>(ns) | Min<br>(ns) | Max<br>(ns) | Min<br>(ns) | Max<br>(ns) |

| Combinatorial Delays                        |                    |             |             |             |             |             |             |             |             |

| F inputs to X output                        | T <sub>ILO</sub>   |             | 5.6         |             | 4.6         |             | 3.8         |             | 3.0         |

| F inputs via transparent latch to Q         | T <sub>ITO</sub>   |             | 8.0         |             | 6.6         |             | 5.4         |             | 4.3         |

| DI inputs to DO output (Logic-Cell          | T <sub>IDO</sub>   |             | 4.3         |             | 3.5         |             | 2.8         |             | 2.4         |

| Feedthrough)                                |                    |             |             |             |             |             |             |             |             |

| F inputs via F5_MUX to DO output            | T <sub>IMO</sub>   |             | 7.2         |             | 5.8         |             | 5.0         |             | 4.3         |

| Carry Delays                                |                    |             |             |             |             |             |             |             |             |

| Incremental delay per bit                   | T <sub>CY</sub>    |             | 0.7         |             | 0.6         |             | 0.5         |             | 0.5         |

| Carry-in overhead from DI                   | T <sub>CYDI</sub>  |             | 1.8         |             | 1.6         |             | 1.5         |             | 1.4         |

| Carry-in overhead from F                    | T <sub>CYL</sub>   |             | 3.7         |             | 3.2         |             | 2.9         |             | 2.4         |

| Carry-out overhead to DO                    | T <sub>CYO</sub>   |             | 4.0         |             | 3.2         |             | 2.5         |             | 2.1         |

| Sequential Delays                           |                    |             |             |             |             |             |             |             |             |

| Clock (CK) to out (Q) (Flip-Flop)           | Т <sub>ско</sub>   |             | 5.8         |             | 4.9         |             | 4.0         |             | 4.0         |

| Gate (Latch enable) going active to out (Q) | T <sub>GO</sub>    |             | 9.2         |             | 7.4         |             | 5.9         |             | 5.5         |

| Set-up Time Before Clock (CK)               |                    |             |             |             |             |             |             |             |             |

| F inputs                                    | Т <sub>ICK</sub>   | 2.3         |             | 1.8         |             | 1.4         |             | 1.3         |             |

| F inputs via F5_MUX                         | T <sub>MICK</sub>  | 3.8         |             | 3.0         |             | 2.5         |             | 2.4         |             |

| DI input                                    | T <sub>DICK</sub>  | 0.8         |             | 0.5         |             | 0.4         |             | 0.4         |             |

| CE input                                    | T <sub>EICK</sub>  | 1.6         |             | 1.2         |             | 0.9         |             | 0.9         |             |

| Hold Times After Clock (CK)                 |                    |             |             |             |             |             |             |             |             |

| F inputs                                    | Тскі               | 0           |             | 0           |             | 0           |             | 0           |             |

| F inputs via F5_MUX                         | Тскмі              | 0           |             | 0           |             | 0           |             | 0           |             |

| DI input                                    | T <sub>CKDI</sub>  | 0           |             | 0           |             | 0           |             | 0           |             |

| CE input                                    | T <sub>CKEI</sub>  | 0           |             | 0           |             | 0           |             | 0           |             |

| Clock Widths                                |                    |             |             |             |             |             |             |             |             |

| Clock High Time                             | Т <sub>сн</sub>    | 6.0         |             | 6.0         |             | 6.0         |             | 6.0         |             |

| Clock Low Time                              | T <sub>CL</sub>    | 6.0         |             | 6.0         |             | 6.0         |             | 6.0         |             |

| Toggle Frequency (MHz) (Note 3)             | F <sub>TOG</sub>   |             | 83          |             | 83          |             | 83          |             | 83          |

| Reset Delays                                |                    |             |             |             |             |             |             |             |             |

| Width (High)                                | T <sub>CLRW</sub>  | 6.0         |             | 6.0         |             | 6.0         |             | 6.0         |             |

| Delay from CLR to Q (Flip-Flop)             | T <sub>CLR</sub>   |             | 7.7         |             | 6.3         |             | 5.1         |             | 4.0         |

| Delay from CLR to Q (Latch)                 | T <sub>CLRL</sub>  |             | 6.5         |             | 5.2         |             | 4.2         |             | 3.0         |

| Global Reset Delays                         |                    |             |             |             |             |             |             |             |             |

| Width (High)                                | T <sub>GCLRW</sub> | 6.0         |             | 6.0         |             | 6.0         | 1           | 6.0         |             |

| Delay from internal GR to Q                 | T <sub>GCLR</sub>  |             | 14.7        |             | 12.1        |             | 9.1         |             | 8.0         |

Note: 1. The CLB K to Q output delay (T<sub>CKO</sub>) of any CLB, plus the shortest possible interconnect delay, is always longer than the Data In hold-time requirement (T<sub>CKDI</sub>) of any CLB on the same die.

2. Timing is based upon the XC5215 device. For other devices, see Timing Calculator.

3. Maximum flip-flop toggle rate for export control purposes.

#### XC5200 Guaranteed Input and Output Parameters (Pin-to-Pin)

All values listed below are tested directly, and guaranteed over the operating conditions. The same parameters can also be derived indirectly from the Global Buffer specifications. The delay calculator uses this indirect method, and may overestimate because of worst-case assumptions. When there is a discrepancy between these two methods, the values listed below should be used, and the derived values should be considered conservative overestimates.

|                                                                                                  | Spee                     | d Grade | -6          | -5          | -4          | -3          |

|--------------------------------------------------------------------------------------------------|--------------------------|---------|-------------|-------------|-------------|-------------|

| Description                                                                                      | Symbol                   | Device  | Max<br>(ns) | Max<br>(ns) | Max<br>(ns) | Max<br>(ns) |

| Global Clock to Output Pad (fast)                                                                | T <sub>ICKOF</sub>       | XC5202  | 16.9        | 15.1        | 10.9        | 9.8         |

| CLB Direct IOB                                                                                   |                          | XC5204  | 17.1        | 15.3        | 11.3        | 9.9         |

|                                                                                                  | (Max)                    | XC5206  | 17.2        | 15.4        | 11.9        | 10.8        |

|                                                                                                  |                          | XC5210  | 17.2        | 15.4        | 12.8        | 11.2        |

| Global Clock-to-Output Delay                                                                     |                          | XC5215  | 19.0        | 17.0        | 12.8        | 11.7        |

| Global Clock to Output Pad (slew-limited)                                                        | Т <sub>IСКО</sub>        | XC5202  | 21.4        | 18.7        | 12.6        | 11.5        |

| CLB _Direct IOB                                                                                  |                          | XC5204  | 21.6        | 18.9        | 13.3        | 11.9        |

| BUFG Q Connect                                                                                   | (Max)                    | XC5206  | 21.7        | 19.0        | 13.6        | 12.5        |

|                                                                                                  |                          | XC5210  | 21.7        | 19.0        | 15.0        | 12.9        |

| Global Clock-to-Output Delay                                                                     |                          | XC5215  | 24.3        | 21.2        | 15.0        | 13.1        |

| Input Set-up Time (no delay) to CLB Flip-Flop                                                    | T <sub>PSUF</sub>        | XC5202  | 2.5         | 2.0         | 1.9         | 1.9         |

|                                                                                                  |                          | XC5204  | 2.3         | 1.9         | 1.9         | 1.9         |

| Set-up<br>& Hold                                                                                 | (Min)                    | XC5206  | 2.2         | 1.9         | 1.9         | 1.9         |

|                                                                                                  |                          | XC5210  | 2.2         | 1.9         | 1.9         | 1.8         |

| BUFG                                                                                             |                          | XC5215  | 2.0         | 1.8         | 1.7         | 1.7         |

| Input Hold Time (no delay) to CLB Flip-Flop                                                      | T <sub>PHF</sub>         | XC5202  | 3.8         | 3.8         | 3.5         | 3.5         |

| IOB(NODELAY) Direct CLB                                                                          | <b>(1 (</b> )            | XC5204  | 3.9         | 3.9         | 3.8         | 3.6         |

| Input Connoct F,DI                                                                               | (Min)                    | XC5206  | 4.4         | 4.4         | 4.4         | 4.3         |

|                                                                                                  |                          | XC5210  | 5.1         | 5.1         | 4.9         | 4.8         |

| BUFG                                                                                             |                          | XC5215  | 5.8         | 5.8         | 5.7         | 5.6         |

| Input Set-up Time (with delay) to CLB Flip-Flop DI Input                                         | T <sub>PSU</sub>         | XC5202  | 7.3         | 6.6         | 6.6         | 6.6         |

|                                                                                                  |                          | XC5204  | 7.3         | 6.6         | 6.6         | 6.6         |

|                                                                                                  |                          | XC5206  | 7.2         | 6.5         | 6.4         | 6.3         |

|                                                                                                  |                          | XC5210  | 7.2         | 6.5         | 6.0         | 6.0         |

| BUFG                                                                                             |                          | XC5215  | 6.8         | 5.7         | 5.7         | 5.7         |

| Input Set-up Time (with delay) to CLB Flip-Flop F Input                                          | T <sub>PSUL</sub>        | XC5202  | 8.8         | 7.7         | 7.5         | 7.5         |

|                                                                                                  | (14:                     | XC5204  | 8.6         | 7.5         | 7.5         | 7.5         |

|                                                                                                  | (Min)                    | XC5206  | 8.5         | 7.4         | 7.4         | 7.4         |

|                                                                                                  |                          | XC5210  | 8.5         | 7.4         | 7.4         | 7.3         |

| BUFG                                                                                             | <u> </u>                 | XC5215  | 8.5         | 7.4         | 7.4         | 7.2         |

| Input Hold Time (with delay) to CLB Flip-Flop<br>IOB Direct CLB<br>Set-up<br>& Hold<br>Time BUFG | Т <sub>РН</sub><br>(Min) | XC52xx  | 0           | 0           | 0           | 0           |

**Note:** 1. These measurements assume that the CLB flip-flop uses a direct interconnect to or from the IOB. The INREG/ OUTREG properties, or XACT-Performance, can be used to assure that direct connects are used. t<sub>PSU</sub> applies only to the CLB input DI that bypasses the look-up table, which only offers direct connects to IOBs on the left and right edges of the die. t<sub>PSUL</sub> applies to the CLB inputs F that feed the look-up table, which offers direct connect to IOBs on all four edges, as do the CLB Q outputs.

2. When testing outputs (fast or slew-limited), half of the outputs on one side of the device are switching.

### XC5200 Series Field Programmable Gate Arrays

# **∑**XILINX<sup>®</sup>

| Pin        | Description     | PC84 | PQ100 | VQ100 | TQ144    | PG156      | PQ160    | Boundary Scan Order |

|------------|-----------------|------|-------|-------|----------|------------|----------|---------------------|

| 14.        | I/O             | -    | -     | -     | 141      | D3         | 157      | 129                 |

| 15.        | I/O (A14)       | 9    | 1     | 98    | 142      | B1         | 158      | 138                 |

| 16.        | I/O (A15)       | 10   | 2     | 99    | 143      | B2         | 159      | 141                 |

|            | VCC             | 11   | 3     | 100   | 144      | C3         | 160      | -                   |

|            | GND             | 12   | 4     | 1     | 1        | C4         | 1        | -                   |

| 17.        | GCK1 (A16, I/O) | 13   | 5     | 2     | 2        | B3         | 2        | 150                 |

| 18.        | I/O (A17)       | 14   | 6     | 3     | 3        | A1         | 3        | 153                 |

| 19.        | I/O             | -    | -     | -     | 4        | A2         | 4        | 159                 |

| 20.        | I/O             | -    | -     | -     | 5        | C5         | 5        | 162                 |

| 21.        | I/O (TDI)       | 15   | 7     | 4     | 6        | B4         | 6        | 165                 |

| 22.        | I/O (TCK)       | 16   | 8     | 5     | 7        | A3         | 7        | 171                 |

|            | GND             | -    | -     | -     | 8        | C6         | 10       | -                   |

| 23.        | I/O             | -    | -     | -     | 9        | B5         | 11       | 174                 |

| 24.        | I/O             | -    | -     | -     | 10       | B6         | 12       | 177                 |

| 25.        | I/O (TMS)       | 17   | 9     | 6     | 11       | A5         | 13       | 180                 |

| 26.        | I/O             | 18   | 10    | 7     | 12       | C7         | 14       | 183                 |

| 27.        | I/O             | -    | -     | -     | 13       | B7         | 15       | 186                 |

| 28.        | I/O             |      | 11    | 8     | 10       | A6         | 16       | 189                 |

| 29.        | I/O             | 19   | 12    | 9     | 15       | A7         | 17       | 195                 |

| 30.        | I/O             | 20   | 12    | 10    | 16       | A8         | 18       | 198                 |

| 30.        | GND             | 20   | 13    | 10    | 10       | C8         | 18       |                     |

|            |                 |      |       |       |          |            |          | -                   |

| 24         | VCC             | 22   | 15    | 12    | 18       | B8         | 20       | -                   |

| 31.        | I/O             | 23   | 16    | 13    | 19       | C9         | 21       | 201                 |

| 32.        | I/O             | 24   | 17    | 14    | 20       | B9         | 22       | 207                 |

| 33.        | I/O             | -    | 18    | 15    | 21       | A9         | 23       | 210                 |

| 34.        | I/O             | -    | -     | -     | 22       | B10        | 24       | 213                 |

| 35.        | I/O             | 25   | 19    | 16    | 23       | C10        | 25       | 219                 |

| 36.        | I/O             | 26   | 20    | 17    | 24       | A10        | 26       | 222                 |

| 37.        | I/O             | -    | -     | -     | 25       | A11        | 27       | 225                 |

| 38.        | I/O             | -    | -     | -     | 26       | B11        | 28       | 231                 |

|            | GND             | -    | -     | -     | 27       | C11        | 29       | -                   |

| 39.        | I/O             | 27   | 21    | 18    | 28       | B12        | 32       | 234                 |

| 40.        | I/O             | -    | 22    | 19    | 29       | A13        | 33       | 237                 |

| 41.        | I/O             | -    | -     | -     | 30       | A14        | 34       | 240                 |

| 42.        | I/O             | -    | -     | -     | 31       | C12        | 35       | 243                 |

| 43.        | I/O             | 28   | 23    | 20    | 32       | B13        | 36       | 246                 |

| 44.        | I/O             | 29   | 24    | 21    | 33       | B14        | 37       | 249                 |

| 45.        | M1 (I/O)        | 30   | 25    | 22    | 34       | A15        | 38       | 258                 |

|            | GND             | 31   | 26    | 23    | 35       | C13        | 39       | -                   |

| 46.        | M0 (I/O)        | 32   | 27    | 24    | 36       | A16        | 40       | 261                 |

|            | VCC             | 33   | 28    | 25    | 37       | C14        | 41       | -                   |

| 47.        | M2 (I/O)        | 34   | 29    | 26    | 38       | B15        | 42       | 264                 |

| 48.        | GCK2 (I/O)      | 35   | 30    | 27    | 39       | B16        | 43       | 267                 |

| 49.        | I/O (HDC)       | 36   | 31    | 28    | 40       | D14        | 44       | 276                 |

| 50.        | I/O             | -    | -     | -     | 41       | C15        | 45       | 279                 |

| 51.        | I/O             | -    | -     | -     | 42       | D15        | 46       | 282                 |

| 52.        | I/O             |      | 32    | 29    | 43       | E14        | 47       | 288                 |

| 53.        | I/O (LDC)       | 37   | 33    | 30    | 44       | C16        | 48       | 200                 |

| 53.<br>54. | I/O             | -    | -     | -     | -        | E15        | 48       | 291                 |

|            | I/O             |      |       |       |          |            |          | 300                 |

| 55.        |                 | -    | -     | -     | -        | D16        | 50       |                     |

|            | GND<br>I/O      | -    | -     | -     | 45<br>46 | F14<br>F15 | 51<br>52 | - 303               |

| Pin | Description        | PC84 | PQ100 | VQ100    | TQ144 | PG156 | PQ160 | Boundary Scan Order |

|-----|--------------------|------|-------|----------|-------|-------|-------|---------------------|

| 57. | I/O                | -    | -     | -        | 47    | E16   | 53    | 306                 |

| 58. | I/O                | 38   | 34    | 31       | 48    | F16   | 54    | 312                 |

| 59. | I/O                | 39   | 35    | 32       | 49    | G14   | 55    | 315                 |

| 60. | I/O                | -    | 36    | 33       | 50    | G15   | 56    | 318                 |

| 61. | I/O                | -    | 37    | 34       | 51    | G16   | 57    | 324                 |

| 62. | I/O                | 40   | 38    | 35       | 52    | H16   | 58    | 327                 |

| 63. | I/O (ERR, INIT)    | 41   | 39    | 36       | 53    | H15   | 59    | 330                 |

|     | VCC                | 42   | 40    | 37       | 54    | H14   | 60    | -                   |

|     | GND                | 43   | 41    | 38       | 55    | J14   | 61    | -                   |

| 64. | I/O                | 44   | 42    | 39       | 56    | J15   | 62    | 336                 |

| 65. | I/O                | 45   | 43    | 40       | 57    | J16   | 63    | 339                 |

| 66. | I/O                | -    | 44    | 41       | 58    | K16   | 64    | 348                 |

| 67. | I/O                | -    | 45    | 42       | 59    | K15   | 65    | 351                 |

| 68. | I/O                | 46   | 46    | 43       | 60    | K14   | 66    | 354                 |

| 69. | I/O                | 47   | 47    | 44       | 61    | L16   | 67    | 360                 |

| 70. | I/O                | -    | -     | -        | 62    | M16   | 68    | 363                 |

| 71. | I/O                | -    | -     | -        | 63    | L15   | 69    | 366                 |

| -   | GND                | -    | -     | -        | 64    | L14   | 70    | -                   |

| 72. | 1/0                |      | -     | -        | -     | N16   | 71    | 372                 |

| 73. | I/O                | -    | -     | -        | -     | M15   | 72    | 375                 |

| 74. | I/O                | 48   | 48    | 45       | 65    | P16   | 72    | 378                 |

| 75. | I/O                | 40   | 49    | 46       | 66    | M14   | 70    | 384                 |

| 76. | I/O                | -    | -     | -        | 67    | N15   | 75    | 387                 |

| 77. | I/O                |      | -     | -        | 68    | P15   | 76    | 390                 |

| 78. | I/O                | 50   | 50    | 47       | 69    | N14   | 70    | 396                 |

| 79. | I/O                | 51   | 51    | 47       | 70    | R16   | 78    | 390                 |

| 79. | GND                | 52   | 52    | 40       | 70    | P14   | 78    |                     |

|     | DONE               | 53   | 53    | 49<br>50 | 71    | R15   |       | -                   |

|     |                    |      |       |          |       |       | 80    | -                   |

|     | VCC                | 54   | 54    | 51       | 73    | P13   | 81    |                     |

|     | PROG               | 55   | 55    | 52       | 74    | R14   | 82    | -                   |

| 80. | I/O (D7)           | 56   | 56    | 53       | 75    | T16   | 83    | 408                 |

| 81. | GCK3 (I/O)         | 57   | 57    | 54       | 76    | T15   | 84    | 411                 |

| 82. | I/O                | -    | -     | -        | 77    | R13   | 85    | 420                 |

| 83. | I/O                | -    | -     | -        | 78    | P12   | 86    | 423                 |

| 84. | I/O (D6)           | 58   | 58    | 55       | 79    | T14   | 87    | 426                 |

| 85. | I/O                | -    | 59    | 56       | 80    | T13   | 88    | 432                 |

|     | GND                | -    | -     | -        | 81    | P11   | 91    | -                   |

| 86. | I/O                | -    | -     | -        | 82    | R11   | 92    | 435                 |

| 87. | I/O                | -    | -     | -        | 83    | T11   | 93    | 438                 |

| 88. | I/O (D5)           | 59   | 60    | 57       | 84    | T10   | 94    | 444                 |

| 89. | I/O ( <u>CS0</u> ) | 60   | 61    | 58       | 85    | P10   | 95    | 447                 |

| 90. | I/O                | -    | 62    | 59       | 86    | R10   | 96    | 450                 |

| 91. | I/O                | -    | 63    | 60       | 87    | Т9    | 97    | 456                 |

| 92. | I/O (D4)           | 61   | 64    | 61       | 88    | R9    | 98    | 459                 |

| 93. | I/O                | 62   | 65    | 62       | 89    | P9    | 99    | 462                 |

|     | VCC                | 63   | 66    | 63       | 90    | R8    | 100   | -                   |

|     | GND                | 64   | 67    | 64       | 91    | P8    | 101   | -                   |

| 94. | I/O (D3)           | 65   | 68    | 65       | 92    | Т8    | 102   | 468                 |

| 95. | I/O (RS)           | 66   | 69    | 66       | 93    | T7    | 103   | 471                 |

| 96. | I/O                | -    | 70    | 67       | 94    | T6    | 104   | 474                 |

| 97. | I/O                | -    | -     | -        | 95    | R7    | 101   | 480                 |

| 98. | I/O (D2)           | 67   | 71    | 68       | 96    | P7    | 106   | 483                 |

#### Pin Locations for XC5206 Devices

The following table may contain pinout information for unsupported device/package combinations. Please see the availability charts elsewhere in the XC5200 Series data sheet for availability information.

| Pin | Description     | PC84 | PQ100 | VQ100 | TQ144 | PQ160 | TQ176 | PG191     | PQ208 | Boundary Scan Order |

|-----|-----------------|------|-------|-------|-------|-------|-------|-----------|-------|---------------------|

|     | VCC             | 2    | 92    | 89    | 128   | 142   | 155   | J4        | 183   | -                   |

| 1.  | I/O (A8)        | 3    | 93    | 90    | 129   | 143   | 156   | J3        | 184   | 87                  |

| 2.  | I/O (A9)        | 4    | 94    | 91    | 130   | 144   | 157   | J2        | 185   | 90                  |

| 3.  | I/O             | -    | 95    | 92    | 131   | 145   | 158   | J1        | 186   | 93                  |

| 4.  | I/O             | -    | 96    | 93    | 132   | 146   | 159   | H1        | 187   | 99                  |

| 5.  | I/O             | -    | -     | -     | -     | -     | 160   | H2        | 188   | 102                 |

| 6.  | I/O             | -    | -     | -     | -     | -     | 161   | H3        | 189   | 105                 |

| 7.  | I/O (A10)       | 5    | 97    | 94    | 133   | 147   | 162   | G1        | 190   | 111                 |

| 8.  | I/O (A11)       | 6    | 98    | 95    | 134   | 148   | 163   | G2        | 191   | 114                 |

| 9.  | I/O             | -    | -     | -     | 135   | 149   | 164   | F1        | 192   | 117                 |

| 10. | I/O             | -    | -     | -     | 136   | 150   | 165   | E1        | 193   | 123                 |

|     | GND             | -    | -     | -     | 137   | 151   | 166   | G3        | 194   | -                   |

| 11. | I/O             | -    | -     | -     | -     | 152   | 168   | C1        | 197   | 126                 |

| 12. | I/O             | -    | -     | -     | -     | 153   | 169   | E2        | 198   | 129                 |

| 13. | I/O (A12)       | 7    | 99    | 96    | 138   | 154   | 170   | F3        | 199   | 138                 |

| 14. | I/O (A13)       | 8    | 100   | 97    | 139   | 155   | 171   | D2        | 200   | 141                 |

| 15. | I/O             | -    | -     | -     | 140   | 156   | 172   | B1        | 201   | 150                 |

| 16. | I/O             | -    | -     | -     | 141   | 157   | 173   | E3        | 202   | 153                 |

| 17. | I/O (A14)       | 9    | 1     | 98    | 142   | 158   | 174   | C2        | 203   | 162                 |

| 18. | I/O (A15)       | 10   | 2     | 99    | 143   | 159   | 175   | B2        | 204   | 165                 |

|     | VCC             | 11   | 3     | 100   | 144   | 160   | 176   | D3        | 205   | -                   |

|     | GND             | 12   | 4     | 1     | 1     | 1     | 1     | D4        | 2     | -                   |

| 19. | GCK1 (A16, I/O) | 13   | 5     | 2     | 2     | 2     | 2     | C3        | 4     | 174                 |

| 20. | I/O (A17)       | 14   | 6     | 3     | 3     | 3     | 3     | C4        | 5     | 177                 |

| 21. | I/O             | -    | -     | -     | 4     | 4     | 4     | B3        | 6     | 183                 |

| 22. | I/O             | -    | -     | -     | 5     | 5     | 5     | C5        | 7     | 186                 |

| 23. | I/O (TDI)       | 15   | 7     | 4     | 6     | 6     | 6     | A2        | 8     | 189                 |

| 24. | I/O (TCK)       | 16   | 8     | 5     | 7     | 7     | 7     | B4        | 9     | 195                 |

| 25. | I/O             | -    | -     | -     | -     | 8     | 8     | C6        | 10    | 198                 |

| 26. | I/O             | -    | -     | -     | -     | 9     | 9     | A3        | 11    | 201                 |

| -   | GND             | _    | -     | -     | 8     | 10    | 10    | C7        | 14    | -                   |

| 27. | I/O             | -    | -     | -     | 9     | 11    | 11    | A4        | 15    | 207                 |

| 28. | I/O             | -    | -     | -     | 10    | 12    | 12    | A5        | 16    | 210                 |

| 29. | I/O (TMS)       | 17   | 9     | 6     | 11    | 13    | 13    | B7        | 17    | 213                 |