# E·XFL

#### AMD Xilinx - XC5206-5PC84C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 196                                                       |

| Number of Logic Elements/Cells | 784                                                       |

| Total RAM Bits                 | -                                                         |

| Number of I/O                  | 65                                                        |

| Number of Gates                | 10000                                                     |

| Voltage - Supply               | 4.75V ~ 5.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 84-LCC (J-Lead)                                           |

| Supplier Device Package        | 84-PLCC (29.31x29.31)                                     |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc5206-5pc84c |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **XILINX**<sup>®</sup>

#### **XC5200 Series Field Programmable Gate Arrays**

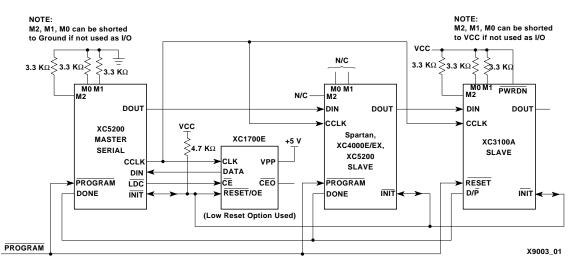

*XC3000 family:* XC5200 devices support an additional programming mode: Peripheral Synchronous.

*XC3000 family:* The XC5200 family does not support Power-down, but offers a Global 3-state input that does not reset any flip-flops.

*XC3000 family:* The XC5200 family does not provide an on-chip crystal oscillator amplifier, but it does provide an internal oscillator from which a variety of frequencies up to 12 MHz are available.

# **Architectural Overview**

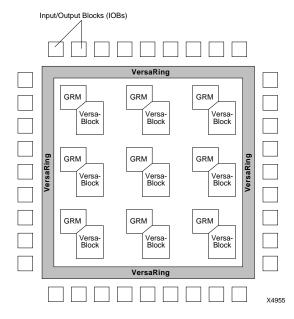

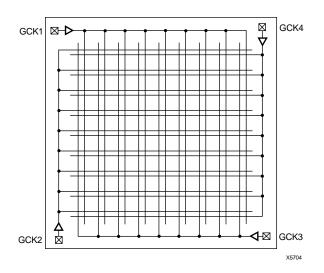

Figure 1 presents a simplified, conceptual overview of the XC5200 architecture. Similar to conventional FPGAs, the XC5200 family consists of programmable IOBs, programmable logic blocks, and programmable interconnect. Unlike other FPGAs, however, the logic and local routing resources of the XC5200 family are combined in flexible VersaBlocks (Figure 2). General-purpose routing connects to the VersaBlock through the General Routing Matrix (GRM).

#### VersaBlock: Abundant Local Routing Plus Versatile Logic

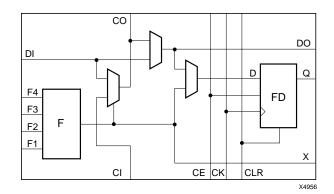

The basic logic element in each VersaBlock structure is the Logic Cell, shown in Figure 3. Each LC contains a 4-input function generator (F), a storage device (FD), and control logic. There are five independent inputs and three outputs to each LC. The independence of the inputs and outputs allows the software to maximize the resource utilization within each LC. Each Logic Cell also contains a direct feedthrough path that does not sacrifice the use of either the function generator or the register; this feature is a first for FPGAs. The storage device is configurable as either a D flip-flop or a latch. The control logic consists of carry logic for fast implementation of arithmetic functions, which can also be configured as a cascade chain allowing decode of very wide input functions.

Figure 1: XC5200 Architectural Overview

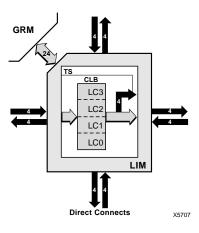

Figure 2: VersaBlock

Figure 3: XC5200 Logic Cell (Four LCs per CLB)

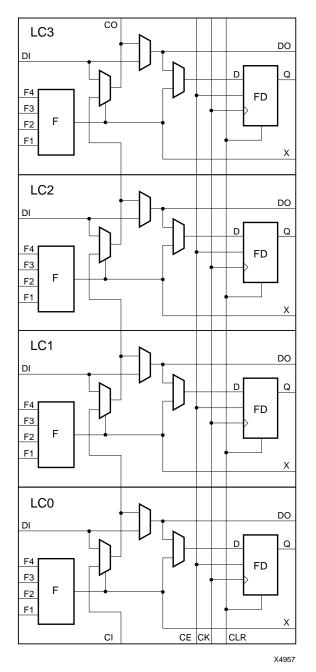

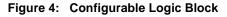

The XC5200 CLB consists of four LCs, as shown in Figure 4. Each CLB has 20 independent inputs and 12 independent outputs. The top and bottom pairs of LCs can be configured to implement 5-input functions. The challenge of FPGA implementation software has always been to maximize the usage of logic resources. The XC5200 family addresses this issue by surrounding each CLB with two types of local interconnect — the Local Interconnect Matrix (LIM) and direct connects. These two interconnect resources, combined with the CLB, form the VersaBlock, represented in Figure 2.

The LIM provides 100% connectivity of the inputs and outputs of each LC in a given CLB. The benefit of the LIM is that no general routing resources are required to connect feedback paths within a CLB. The LIM connects to the GRM via 24 bidirectional nodes.

The direct connects allow immediate connections to neighboring CLBs, once again without using any of the general interconnect. These two layers of local routing resource improve the granularity of the architecture, effectively making the XC5200 family a "sea of logic cells." Each Versa-Block has four 3-state buffers that share a common enable line and directly drive horizontal and vertical Lonalines, creating robust on-chip bussing capability. The VersaBlock allows fast, local implementation of logic functions, effectively implementing user designs in a hierarchical fashion. These resources also minimize local routing congestion and improve the efficiency of the general interconnect, which is used for connecting larger groups of logic. It is this combination of both fine-grain and coarse-grain architecture attributes that maximize logic utilization in the XC5200 family. This symmetrical structure takes full advantage of the third metal layer, freeing the placement software to pack user logic optimally with minimal routing restrictions.

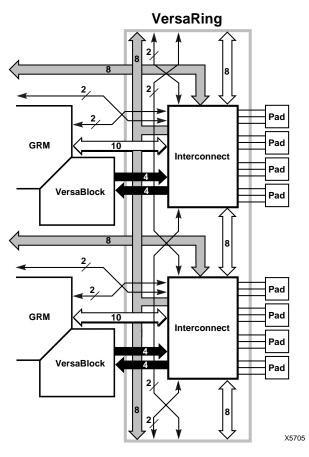

## VersaRing I/O Interface

The interface between the IOBs and core logic has been redesigned in the XC5200 family. The IOBs are completely decoupled from the core logic. The XC5200 IOBs contain dedicated boundary-scan logic for added board-level testability, but do not include input or output registers. This approach allows a maximum number of IOBs to be placed around the device, improving the I/O-to-gate ratio and decreasing the cost per I/O. A "freeway" of interconnect cells surrounding the device forms the VersaRing, which provides connections from the IOBs to the internal logic. These incremental routing resources provide abundant connections from each IOB to the nearest VersaBlock, in addition to Longline connections surrounding the device. The VersaRing eliminates the historic trade-off between high logic utilization and pin placement flexibility. These incremental edge resources give users increased flexibility in preassigning (i.e., locking) I/O pins before completing their logic designs. This ability accelerates time-to-market, since PCBs and other system components can be manufactured concurrent with the logic design.

## **General Routing Matrix**

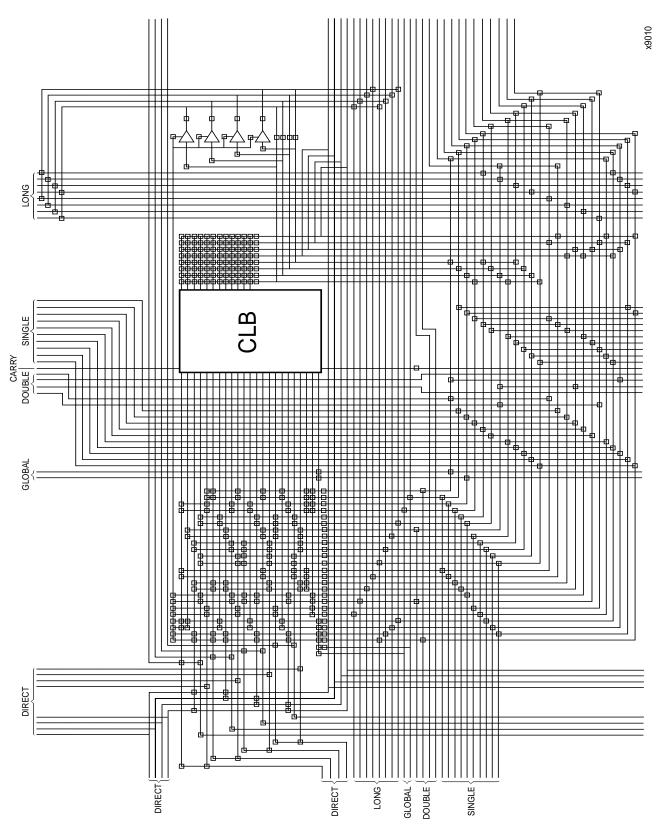

The GRM is functionally similar to the switch matrices found in other architectures, but it is novel in its tight coupling to the logic resources contained in the VersaBlocks. Advanced simulation tools were used during the development of the XC5200 architecture to determine the optimal level of routing resources required. The XC5200 family contains six levels of interconnect hierarchy — a series of

single-length lines, double-length lines, and Longlines all routed through the GRM. The direct connects, LIM, and logic-cell feedthrough are contained within each Versa-Block. Throughout the XC5200 interconnect, an efficient multiplexing scheme, in combination with three layer metal (TLM), was used to improve the overall efficiency of silicon usage.

### **Performance Overview**

The XC5200 family has been benchmarked with many designs running synchronous clock rates beyond 66 MHz. The performance of any design depends on the circuit to be implemented, and the delay through the combinatorial and sequential logic elements, plus the delay in the interconnect routing. A rough estimate of timing can be made by assuming 3-6 ns per logic level, which includes direct-connect routing delays, depending on speed grade. More accurate estimations can be made using the information in the Switching Characteristic Guideline section.

## Taking Advantage of Reconfiguration

FPGA devices can be reconfigured to change logic function while resident in the system. This capability gives the system designer a new degree of freedom not available with any other type of logic.

Hardware can be changed as easily as software. Design updates or modifications are easy, and can be made to products already in the field. An FPGA can even be reconfigured dynamically to perform different functions at different times.

Reconfigurable logic can be used to implement system self-diagnostics, create systems capable of being reconfigured for different environments or operations, or implement multi-purpose hardware for a given application. As an added benefit, using reconfigurable FPGA devices simplifies hardware design and debugging and shortens product time-to-market.

# **Detailed Functional Description**

## **Configurable Logic Blocks (CLBs)**

Figure 4 shows the logic in the XC5200 CLB, which consists of four Logic Cells (LC[3:0]). Each Logic Cell consists of an independent 4-input Lookup Table (LUT), and a D-Type flip-flop or latch with common clock, clock enable, and clear, but individually selectable clock polarity. Additional logic features provided in the CLB are:

- An independent 5-input LUT by combining two 4-input LUTs.

- High-speed carry propagate logic.

- High-speed pattern decoding.

- High-speed direct connection to flip-flop D-inputs.

- Individual selection of either a transparent, level-sensitive latch or a D flip-flop.

- Four 3-state buffers with a shared Output Enable.

### **5-Input Functions**

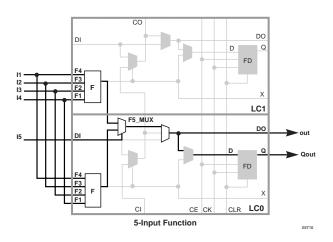

Figure 5 illustrates how the outputs from the LUTs from LC0 and LC1 can be combined with a 2:1 multiplexer (F5\_MUX) to provide a 5-input function. The outputs from the LUTs of LC2 and LC3 can be similarly combined.

non-zero hold, attach a NODELAY attribute or property to the flip-flop or input buffer.

#### **IOB Output Signals**

Output signals can be optionally inverted within the IOB, and pass directly to the pad. As with the inputs, a CLB flip-flop or latch can be used to store the output signal.

An active-High 3-state signal can be used to place the output buffer in a high-impedance state, implementing 3-state outputs or bidirectional I/O. Under configuration control, the output (OUT) and output 3-state (T) signals can be inverted. The polarity of these signals is independently configured for each IOB.

The XC5200 devices provide a guaranteed output sink current of 8 mA.

Supported destinations for XC5200-Series device outputs are shown in Table 6.(For a detailed discussion of how to interface between 5 V and 3.3 V devices, see the 3V Products section of *The Programmable Logic Data Book*.)

An output can be configured as open-drain (open-collector) by placing an OBUFT symbol in a schematic or HDL code, then tying the 3-state pin (T) to the output signal, and the input pin (I) to Ground. (See Figure 12.)

# Table 6: Supported Destinations for XC5200-SeriesOutputs

|                                                                 | XC5200 Output Mode |

|-----------------------------------------------------------------|--------------------|

| Destination                                                     | 5 V,<br>CMOS       |

| XC5200 device, V <sub>CC</sub> =3.3 V,<br>CMOS-threshold inputs | $\checkmark$       |

| Any typical device, $V_{CC} = 3.3 V$ , CMOS-threshold inputs    | some <sup>1</sup>  |

| Any device, V <sub>CC</sub> = 5 V,<br>TTL-threshold inputs      | $\checkmark$       |

| Any device, V <sub>CC</sub> = 5 V,<br>CMOS-threshold inputs     | $\checkmark$       |

1. Only if destination device has 5-V tolerant inputs

Figure 12: Open-Drain Output

#### **Output Slew Rate**

The slew rate of each output buffer is, by default, reduced, to minimize power bus transients when switching non-critical signals. For critical signals, attach a FAST attribute or property to the output buffer or flip-flop. For XC5200 devices, maximum total capacitive load for simultaneous fast mode switching in the same direction is 200 pF for all package pins between each Power/Ground pin pair. For some XC5200 devices, additional internal Power/Ground pin pairs are connected to special Power and Ground planes within the packages, to reduce ground bounce.

For slew-rate limited outputs this total is two times larger for each device type: 400 pF for XC5200 devices. This maximum capacitive load should not be exceeded, as it can result in ground bounce of greater than 1.5 V amplitude and more than 5 ns duration. This level of ground bounce may cause undesired transient behavior on an output, or in the internal logic. This restriction is common to all high-speed digital ICs, and is not particular to Xilinx or the XC5200 Series.

XC5200-Series devices have a feature called "Soft Start-up," designed to reduce ground bounce when all outputs are turned on simultaneously at the end of configuration. When the configuration process is finished and the device starts up, the first activation of the outputs is automatically slew-rate limited. Immediately following the initial activation of the I/O, the slew rate of the individual outputs is determined by the individual configuration option for each IOB.

#### **Global Three-State**

A separate Global 3-State line (not shown in Figure 11) forces all FPGA outputs to the high-impedance state, unless boundary scan is enabled and is executing an EXTEST instruction. This global net (GTS) does not compete with other routing resources; it uses a dedicated distribution network.

GTS can be driven from any user-programmable pin as a global 3-state input. To use this global net, place an input pad and input buffer in the schematic or HDL code, driving the GTS pin of the STARTUP symbol. A specific pin location can be assigned to this input using a LOC attribute or property, just as with any other user-programmable pad. An inverter can optionally be inserted after the input buffer to invert the sense of the Global 3-State signal. Using GTS is similar to Global Reset. See Figure 8 on page 90 for details. Alternatively, GTS can be driven from any internal node.

### Other IOB Options

There are a number of other programmable options in the XC5200-Series IOB.

#### Pull-up and Pull-down Resistors

Programmable IOB pull-up and pull-down resistors are useful for tying unused pins to Vcc or Ground to minimize power consumption and reduce noise sensitivity. The configurable pull-up resistor is a p-channel transistor that pulls

segments span the width and height of the chip, respectively.

Two low-skew horizontal and vertical unidirectional global-line segments span each row and column of the chip, respectively.

#### Single- and Double-Length Lines

The single- and double-length bidirectional line segments make up the bulk of the routing channels. The double-length lines hop across every other CLB to reduce the propagation delays in speed-critical nets. Regenerating the signal strength is recommended after traversing three or four such segments. Xilinx place-and-route software automatically connects buffers in the path of the signal as necessary. Single- and double-length lines cannot drive onto Longlines and global lines; Longlines and global lines can, however, drive onto single- and double-length lines. As a general rule, Longline and global-line connections to the general routing matrix are unidirectional, with the signal direction from these lines toward the routing matrix.

#### Longlines

Longlines are used for high-fan-out signals, 3-state busses, low-skew nets, and faraway destinations. Row and column splitter PIPs in the middle of the array effectively double the total number of Longlines by electrically dividing them into two separated half-lines. Longlines are driven by the 3-state buffers in each CLB, and are driven by similar buffers at the periphery of the array from the VersaRing I/O Interface.

Bus-oriented designs are easily implemented by using Longlines in conjunction with the 3-state buffers in the CLB and in the VersaRing. Additionally, weak keeper cells at the periphery retain the last valid logic level on the Longlines when all buffers are in 3-state mode.

Longlines connect to the single-length or double-length lines, or to the logic inside the CLB, through the General Routing Matrix. The only manner in which a Longline can be driven is through the four 3-state buffers; therefore, a Longline-to-Longline or single-line-to-Longline connection through PIPs in the General Routing Matrix is not possible. Again, as a general rule, long- and global-line connections to the General Routing Matrix are unidirectional, with the signal direction from these lines toward the routing matrix.

The XC5200 family has no pull-ups on the ends of the Longlines sourced by TBUFs, unlike the XC4000 Series. Consequently, wired functions (i.e., WAND and WORAND) and wide multiplexing functions requiring pull-ups for undefined states (i.e., bus applications) must be implemented in a different way. In the case of the wired functions, the same functionality can be achieved by taking advantage of the carry/cascade logic described above, implementing a wide logic function in place of the wired function. In the case of 3-state bus applications, the user must insure that all states of the multiplexing function are defined. This process is as simple as adding an additional TBUF to drive the bus High when the previously undefined states are activated.

#### **Global Lines**

Global buffers in Xilinx FPGAs are special buffers that drive a dedicated routing network called Global Lines, as shown in Figure 16. This network is intended for high-fanout clocks or other control signals, to maximize speed and minimize skewing while distributing the signal to many loads.

The XC5200 family has a total of four global buffers (BUFG symbol in the library), each with its own dedicated routing channel. Two are distributed vertically and two horizontally throughout the FPGA.

The global lines provide direct input only to the CLB clock pins. The global lines also connect to the General Routing Matrix to provide access from these lines to the function generators and other control signals.

Four clock input pads at the corners of the chip, as shown in Figure 16, provide a high-speed, low-skew clock network to each of the four global-line buffers. In addition to the dedicated pad, the global lines can be sourced by internal logic. PIPs from several routing channels within the VersaRing can also be configured to drive the global-line buffers.

Details of all the programmable interconnect for a CLB is shown in Figure 17.

Figure 16: Global Lines

**∑**XILINX<sup>®</sup>

XC5200 Series Field Programmable Gate Arrays

Figure 17: Detail of Programmable Interconnect Associated with XC5200 Series CLB

#### VersaRing Input/Output Interface

The VersaRing, shown in Figure 18, is positioned between the core logic and the pad ring; it has all the routing resources of a VersaBlock without the CLB logic. The VersaRing decouples the core logic from the I/O pads. Each VersaRing Cell provides up to four pad-cell connections on one side, and connects directly to the CLB ports on the other side.

Figure 18: VersaRing I/O Interface

# **Boundary Scan**

The "bed of nails" has been the traditional method of testing electronic assemblies. This approach has become less appropriate, due to closer pin spacing and more sophisticated assembly methods like surface-mount technology and multi-layer boards. The IEEE boundary scan standard 1149.1 was developed to facilitate board-level testing of electronic assemblies. Design and test engineers can imbed a standard test logic structure in their device to achieve high fault coverage for I/O and internal logic. This structure is easily implemented with a four-pin interface on any boundary scan-compatible IC. IEEE 1149.1-compatible devices may be serial daisy-chained together, connected in parallel, or a combination of the two. XC5200 devices support all the mandatory boundary-scan instructions specified in the IEEE standard 1149.1. A Test Access Port (TAP) and registers are provided that implement the EXTEST, SAMPLE/PRELOAD, and BYPASS instructions. The TAP can also support two USERCODE instructions. When the boundary scan configuration option is selected, three normal user I/O pins become dedicated inputs for these functions. Another user output pin becomes the dedicated boundary scan output.

Boundary-scan operation is independent of individual IOB configuration and package type. All IOBs are treated as independently controlled bidirectional pins, including any unbonded IOBs. Retaining the bidirectional test capability after configuration provides flexibility for interconnect testing.

Also, internal signals can be captured during EXTEST by connecting them to unbonded IOBs, or to the unused outputs in IOBs used as unidirectional input pins. This technique partially compensates for the lack of INTEST support.

The user can serially load commands and data into these devices to control the driving of their outputs and to examine their inputs. This method is an improvement over bed-of-nails testing. It avoids the need to over-drive device outputs, and it reduces the user interface to four pins. An optional fifth pin, a reset for the control logic, is described in the standard but is not implemented in Xilinx devices.

The dedicated on-chip logic implementing the IEEE 1149.1 functions includes a 16-state machine, an instruction register and a number of data registers. The functional details can be found in the IEEE 1149.1 specification and are also discussed in the Xilinx application note XAPP 017: *"Boundary Scan in XC4000 and XC5200 Series devices"*

Figure 19 on page 99 is a diagram of the XC5200-Series boundary scan logic. It includes three bits of Data Register per IOB, the IEEE 1149.1 Test Access Port controller, and the Instruction Register with decodes.

The public boundary-scan instructions are always available prior to configuration. After configuration, the public instructions and any USERCODE instructions are only available if specified in the design. While SAMPLE and BYPASS are available during configuration, it is recommended that boundary-scan operations not be performed during this transitory period.

In addition to the test instructions outlined above, the boundary-scan circuitry can be used to configure the FPGA device, and to read back the configuration data.

All of the XC4000 boundary-scan modes are supported in the XC5200 family. Three additional outputs for the User-Register are provided (Reset, Update, and Shift), repre-

#### Table 9: Pin Descriptions (Continued)

| Pin Name       | I/O<br>During<br>Config. | I/O<br>After<br>Config. | Pin Description                                                                                                                                                                                                                                                          |

|----------------|--------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unrestricted U | lser-Prog                | rammabl                 | e I/O Pins                                                                                                                                                                                                                                                               |

| I/O            | Weak<br>Pull-up          | I/O                     | These pins can be configured to be input and/or output after configuration is completed. Before configuration is completed, these pins have an internal high-value pull-up resistor ( $20 \text{ k}\Omega - 100 \text{ k}\Omega$ ) that defines the logic level as High. |

# Configuration

Configuration is the process of loading design-specific programming data into one or more FPGAs to define the functional operation of the internal blocks and their interconnections. This is somewhat like loading the command registers of a programmable peripheral chip. XC5200-Series devices use several hundred bits of configuration data per CLB and its associated interconnects. Each configuration bit defines the state of a static memory cell that controls either a function look-up table bit, a multiplexer input, or an interconnect pass transistor. The development system translates the design into a netlist file. It automatically partitions, places and routes the logic and generates the configuration data in PROM format.

### **Special Purpose Pins**

Three configuration mode pins (M2, M1, M0) are sampled prior to configuration to determine the configuration mode. After configuration, these pins can be used as auxiliary I/O connections. The development system does not use these resources unless they are explicitly specified in the design entry. This is done by placing a special pad symbol called MD2, MD1, or MD0 instead of the input or output pad symbol.

In XC5200-Series devices, the mode pins have weak pull-up resistors during configuration. With all three mode pins High, Slave Serial mode is selected, which is the most popular configuration mode. Therefore, for the most common configuration mode, the mode pins can be left unconnected. (Note, however, that the internal pull-up resistor value can be as high as 100 k $\Omega$ .) After configuration, these pins can individually have weak pull-up or pull-down resistors, as specified in the design. A pull-down resistor value of  $3.3k\Omega$  is recommended.

These pins are located in the lower left chip corner and are near the readback nets. This location allows convenient routing if compatibility with the XC2000 and XC3000 family conventions of M0/RT, M1/RD is desired.

## **Configuration Modes**

XC5200 devices have seven configuration modes. These modes are selected by a 3-bit input code applied to the M2,

M1, and M0 inputs. There are three self-loading Master modes, two Peripheral modes, and a Serial Slave mode,

#### **Table 10: Configuration Modes**

| Mode                       | M2 | M1 | MO | CCLK   | Data                                  |

|----------------------------|----|----|----|--------|---------------------------------------|

| Master Serial              | 0  | 0  | 0  | output | Bit-Serial                            |

| Slave Serial               | 1  | 1  | 1  | input  | Bit-Serial                            |

| Master<br>Parallel Up      | 1  | 0  | 0  | output | Byte-Wide,<br>increment<br>from 00000 |

| Master<br>Parallel Down    | 1  | 1  | 0  | output | Byte-Wide,<br>decrement<br>from 3FFFF |

| Peripheral<br>Synchronous* | 0  | 1  | 1  | input  | Byte-Wide                             |

| Peripheral<br>Asynchronous | 1  | 0  | 1  | output | Byte-Wide                             |

| Express                    | 0  | 1  | 0  | input  | Byte-Wide                             |

| Reserved                   | 0  | 0  | 1  |        |                                       |

Note :\*Peripheral Synchronous can be considered byte-wide Slave Parallel

which is used primarily for daisy-chained devices. The seventh mode, called Express mode, is an additional slave mode that allows high-speed parallel configuration. The coding for mode selection is shown in Table 10.

Note that the smallest package, VQ64, only supports the Master Serial, Slave Serial, and Express modes. A detailed description of each configuration mode, with timing information, is included later in this data sheet. During configuration, some of the I/O pins are used temporarily for the configuration process. All pins used during configuration are shown in Table 13 on page 124.

#### Master Modes

The three Master modes use an internal oscillator to generate a Configuration Clock (CCLK) for driving potential slave devices. They also generate address and timing for external PROM(s) containing the configuration data.

Master Parallel (Up or Down) modes generate the CCLK signal and PROM addresses and receive byte parallel data. The data is internally serialized into the FPGA data-frame format. The up and down selection generates starting addresses at either zero or 3FFFF, for compatibility with different microprocessor addressing conventions. The

# **Configuration Timing**

The seven configuration modes are discussed in detail in this section. Timing specifications are included.

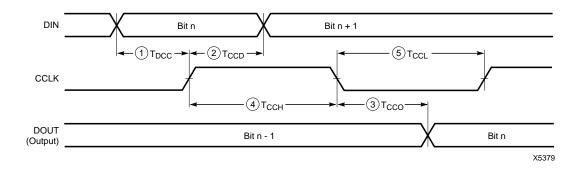

### Slave Serial Mode

In Slave Serial mode, an external signal drives the CCLK input of the FPGA. The serial configuration bitstream must be available at the DIN input of the lead FPGA a short setup time before each rising CCLK edge.

The lead FPGA then presents the preamble data—and all data that overflows the lead device—on its DOUT pin.

There is an internal delay of 0.5 CCLK periods, which means that DOUT changes on the falling CCLK edge, and the next FPGA in the daisy chain accepts data on the subsequent rising CCLK edge.

Figure 28 shows a full master/slave system. An XC5200-Series device in Slave Serial mode should be connected as shown in the third device from the left.

Slave Serial mode is selected by a <111> on the mode pins (M2, M1, M0). Slave Serial is the default mode if the mode pins are left unconnected, as they have weak pull-up resistors during configuration.

Figure 28: Master/Slave Serial Mode Circuit Diagram

|      | Description | Symbol |                  | Min | Max | Units |

|------|-------------|--------|------------------|-----|-----|-------|

|      | DIN setup   | 1      | T <sub>DCC</sub> | 20  |     | ns    |

|      | DIN hold    | 2      | T <sub>CCD</sub> | 0   |     | ns    |

| CCLK | DIN to DOUT | 3      | T <sub>CCO</sub> |     | 30  | ns    |

| COLK | High time   | 4      | Т <sub>ССН</sub> | 45  |     | ns    |

|      | Low time    | 5      | T <sub>CCL</sub> | 45  |     | ns    |

|      | Frequency   |        | F <sub>CC</sub>  |     | 10  | MHz   |

**Note:** Configuration must be delayed until the INIT pins of all daisy-chained FPGAs are High. **Figure 29:** Slave Serial Mode Programming Switching Characteristics

## **XC5200 Series Field Programmable Gate Arrays**

TO DIN OF OPTIONAL HIGH DAISY-CHAINED FPGAS or LOW 3.3 K N/C  $\sim$ N/C M1 M2 M0 TO CCLK OF OPTIONAL DAISY-CHAINED FPGAS CCLK DOUT NOTE:M0 can be shorted to Ground if not used as I/O. MO M1 M2 A17 XC5200 A16 DOUT DIN VCC Master EPROM Parallel A15 (8K x 8) (OR LARGER) CCLK ≶ X 4.7K A14 XC5200/ USER CONTROL OF HIGHER INIT A13 ORDER PROM ADDRESS BITS XC4000E/EX/ Spartan SLAVE CAN BE USED TO SELECT BETWEEN A12 A12 ALTERNATIVE CONFIGURATIONS A11 A11 PROGRAM A10 A10 PROGRAM A9 A9 DONE INIT  $\leftrightarrow$ D7 A8 A8 D6 A7 A7 D7 D5 A6 A6 D6 D4 A5 D5 A5 . D3 A4 > A4 D4 D2 A3 D3 A3 D1 A2 D2 A2 D0 A1 A1 D1 A0 D0 A0 ŌE DONE > CE DATA BUS / 8 PROGRAM

Figure 31: Master Parallel Mode Circuit Diagram

X9004\_01

**XILINX<sup>®</sup>**

#### **XC5200 Series Field Programmable Gate Arrays**

X6097

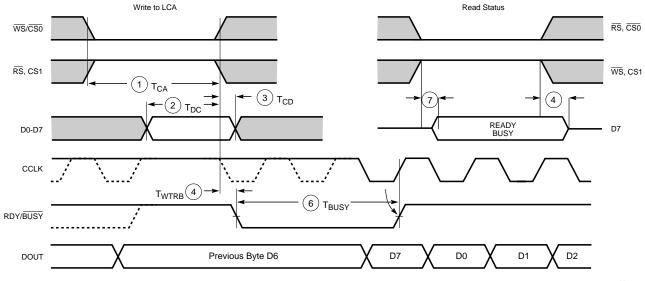

|          | Description                                        | 9 | Symbol            | Min | Max | Units           |

|----------|----------------------------------------------------|---|-------------------|-----|-----|-----------------|

| \\/-:\+- | Effective Write time<br>(CSO, WS=Low; RS, CS1=High | 1 | T <sub>CA</sub>   | 100 |     | ns              |

| Write    | DIN setup time                                     | 2 | T <sub>DC</sub>   | 60  |     | ns              |

|          | DIN hold time                                      | 3 | T <sub>CD</sub>   | 0   |     | ns              |

|          | RDY/BUSY delay after end of Write or Read          | 4 | T <sub>WTRB</sub> |     | 60  | ns              |

| RDY      | RDY/BUSY active after beginning<br>of Read         | 7 |                   |     | 60  | ns              |

|          | RDY/BUSY Low output (Note 4)                       | 6 | T <sub>BUSY</sub> | 2   | 9   | CCLK<br>periods |

Notes: 1. Configuration must be delayed until INIT pins of all daisy-chained FPGAs are high.

2. The time from the end of WS to CCLK cycle for the new byte of data depends on the completion of previous byte processing and the phase of internal timing generator for CCLK.

3. CCLK and DOUT timing is tested in slave mode.

4. T<sub>BUSY</sub> indicates that the double-buffered parallel-to-serial converter is not yet ready to receive new data. The shortest T<sub>BUSY</sub> occurs when a byte is loaded into an empty parallel-to-serial converter. The longest T<sub>BUSY</sub> occurs when a new word is loaded into the input register before the second-level buffer has started shifting out data.

This timing diagram shows very relaxed requirements. Data need not be held beyond the rising edge of  $\overline{WS}$ . RDY/ $\overline{BUSY}$  will go active within 60 ns after the end of  $\overline{WS}$ . A new write may be asserted immediately after RDY/ $\overline{BUSY}$  goes Low, but write may not be terminated until RDY/ $\overline{BUSY}$  has been High for one CCLK period.

#### Figure 36: Asynchronous Peripheral Mode Programming Switching Characteristics

**XILINX**<sup>®</sup>

## **XC5200 Series Field Programmable Gate Arrays**

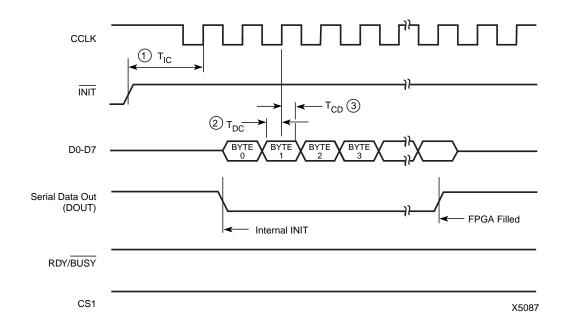

|      | Description                     | Sy | Symbol           |    | Max | Units |

|------|---------------------------------|----|------------------|----|-----|-------|

|      | INIT (High) Setup time required | 1  | T <sub>IC</sub>  | 5  |     | μs    |

|      | DIN Setup time required         | 2  | T <sub>DC</sub>  | 30 |     | ns    |

| CCLK | DIN hold time required          | 3  | T <sub>CD</sub>  | 0  |     | ns    |

| COLK | CCLK High time                  |    | T <sub>CCH</sub> | 30 |     | ns    |

|      | CCLK Low time                   |    | T <sub>CCL</sub> | 30 |     | ns    |

|      | CCLK frequency                  |    | F <sub>CC</sub>  |    | 10  | MHz   |

Note: If not driven by the preceding DOUT, CS1 must remain high until the device is fully configured.

Figure 38: Express Mode Programming Switching Characteristics

### XC5200 Guaranteed Input and Output Parameters (Pin-to-Pin)

All values listed below are tested directly, and guaranteed over the operating conditions. The same parameters can also be derived indirectly from the Global Buffer specifications. The delay calculator uses this indirect method, and may overestimate because of worst-case assumptions. When there is a discrepancy between these two methods, the values listed below should be used, and the derived values should be considered conservative overestimates.

|                                                                                                  | Spee                     | d Grade | -6          | -5          | -4          | -3          |

|--------------------------------------------------------------------------------------------------|--------------------------|---------|-------------|-------------|-------------|-------------|

| Description                                                                                      | Symbol                   | Device  | Max<br>(ns) | Max<br>(ns) | Max<br>(ns) | Max<br>(ns) |

| Global Clock to Output Pad (fast)                                                                | T <sub>ICKOF</sub>       | XC5202  | 16.9        | 15.1        | 10.9        | 9.8         |

| CLB Direct IOB                                                                                   |                          | XC5204  | 17.1        | 15.3        | 11.3        | 9.9         |

|                                                                                                  | (Max)                    | XC5206  | 17.2        | 15.4        | 11.9        | 10.8        |

|                                                                                                  |                          | XC5210  | 17.2        | 15.4        | 12.8        | 11.2        |

| Global Clock-to-Output Delay                                                                     |                          | XC5215  | 19.0        | 17.0        | 12.8        | 11.7        |

| Global Clock to Output Pad (slew-limited)                                                        | Т <sub>IСКО</sub>        | XC5202  | 21.4        | 18.7        | 12.6        | 11.5        |

| CLB _Direct IOB                                                                                  |                          | XC5204  | 21.6        | 18.9        | 13.3        | 11.9        |

| BUFG Q Connect                                                                                   | (Max)                    | XC5206  | 21.7        | 19.0        | 13.6        | 12.5        |

|                                                                                                  |                          | XC5210  | 21.7        | 19.0        | 15.0        | 12.9        |

| Global Clock-to-Output Delay                                                                     |                          | XC5215  | 24.3        | 21.2        | 15.0        | 13.1        |

| Input Set-up Time (no delay) to CLB Flip-Flop                                                    | T <sub>PSUF</sub>        | XC5202  | 2.5         | 2.0         | 1.9         | 1.9         |

|                                                                                                  |                          | XC5204  | 2.3         | 1.9         | 1.9         | 1.9         |

| Set-up<br>& Hold                                                                                 | (Min)                    | XC5206  | 2.2         | 1.9         | 1.9         | 1.9         |

|                                                                                                  |                          | XC5210  | 2.2         | 1.9         | 1.9         | 1.8         |

| BUFG                                                                                             |                          | XC5215  | 2.0         | 1.8         | 1.7         | 1.7         |

| Input Hold Time (no delay) to CLB Flip-Flop                                                      | T <sub>PHF</sub>         | XC5202  | 3.8         | 3.8         | 3.5         | 3.5         |

| IOB(NODELAY) Direct CLB                                                                          | <b>(1 (</b> )            | XC5204  | 3.9         | 3.9         | 3.8         | 3.6         |

| Input A D F,DI                                                                                   | (Min)                    | XC5206  | 4.4         | 4.4         | 4.4         | 4.3         |

|                                                                                                  |                          | XC5210  | 5.1         | 5.1         | 4.9         | 4.8         |

| BUFG                                                                                             |                          | XC5215  | 5.8         | 5.8         | 5.7         | 5.6         |

| Input Set-up Time (with delay) to CLB Flip-Flop DI Input                                         | T <sub>PSU</sub>         | XC5202  | 7.3         | 6.6         | 6.6         | 6.6         |

|                                                                                                  |                          | XC5204  | 7.3         | 6.6         | 6.6         | 6.6         |

|                                                                                                  |                          | XC5206  | 7.2         | 6.5         | 6.4         | 6.3         |

|                                                                                                  |                          | XC5210  | 7.2         | 6.5         | 6.0         | 6.0         |

| BUFG                                                                                             |                          | XC5215  | 6.8         | 5.7         | 5.7         | 5.7         |

| Input Set-up Time (with delay) to CLB Flip-Flop F Input                                          | T <sub>PSUL</sub>        | XC5202  | 8.8         | 7.7         | 7.5         | 7.5         |

|                                                                                                  | (14:                     | XC5204  | 8.6         | 7.5         | 7.5         | 7.5         |

|                                                                                                  | (Min)                    | XC5206  | 8.5         | 7.4         | 7.4         | 7.4         |

|                                                                                                  |                          | XC5210  | 8.5         | 7.4         | 7.4         | 7.3         |

| BUFG                                                                                             | <u> </u>                 | XC5215  | 8.5         | 7.4         | 7.4         | 7.2         |

| Input Hold Time (with delay) to CLB Flip-Flop<br>IOB Direct CLB<br>Set-up<br>& Hold<br>Time BUFG | Т <sub>РН</sub><br>(Min) | XC52xx  | 0           | 0           | 0           | 0           |

**Note:** 1. These measurements assume that the CLB flip-flop uses a direct interconnect to or from the IOB. The INREG/ OUTREG properties, or XACT-Performance, can be used to assure that direct connects are used. t<sub>PSU</sub> applies only to the CLB input DI that bypasses the look-up table, which only offers direct connects to IOBs on the left and right edges of the die. t<sub>PSUL</sub> applies to the CLB inputs F that feed the look-up table, which offers direct connect to IOBs on all four edges, as do the CLB Q outputs.

2. When testing outputs (fast or slew-limited), half of the outputs on one side of the device are switching.

#### **XC5200 Series Field Programmable Gate Arrays**

| Pin | Description    | VQ64* | PC84 | PQ100 | VQ100 | TQ144 | PG156 | Boundary Scan Order |

|-----|----------------|-------|------|-------|-------|-------|-------|---------------------|

|     | CCLK           | 48    | 73   | 77    | 74    | 107   | R2    | -                   |

|     | VCC            | -     | 74   | 78    | 75    | 108   | P3    | -                   |

| 74. | I/O (TDO)      | 49    | 75   | 79    | 76    | 109   | T1    | 0                   |

|     | GND            | -     | 76   | 80    | 77    | 110   | N3    | -                   |

| 75. | I/O (A0, WS)   | 50    | 77   | 81    | 78    | 111   | R1    | 9                   |

| 76. | GCK4 (A1, I/O) | 51    | 78   | 82    | 79    | 112   | P2    | 15                  |

| 77. | I/O (A2, CS1)  | 52    | 79   | 83    | 80    | 115   | P1    | 18                  |

| 78. | I/O (A3)       | -     | 80   | 84    | 81    | 116   | N1    | 21                  |

|     | GND            | -     | -    | -     | -     | 118   | L3    | -                   |

| 79. | I/O (A4)       | -     | 81   | 85    | 82    | 121   | K3    | 27                  |

| 80. | I/O (A5)       | 53    | 82   | 86    | 83    | 122   | K2    | 30                  |

| 81. | I/O            | -     | -    | 87    | 84    | 123   | K1    | 33                  |

| 82. | I/O            | -     | -    | 88    | 85    | 124   | J1    | 39                  |

| 83. | I/O (A6)       | 54    | 83   | 89    | 86    | 125   | J2    | 42                  |

| 84. | I/O (A7)       | 55    | 84   | 90    | 87    | 126   | J3    | 45                  |

|     | GND            | 56    | 1    | 91    | 88    | 127   | H2    | -                   |

\* VQ64 package supports Master Serial, Slave Serial, and Express configuration modes only.

# Additional No Connect (N.C.) Connections on TQ144 Package

|     | TQ144 |    |    |     |     |  |  |  |  |  |  |

|-----|-------|----|----|-----|-----|--|--|--|--|--|--|

| 135 | 9     | 41 | 67 | 98  | 117 |  |  |  |  |  |  |

| 136 | 10    | 42 | 68 | 99  | 119 |  |  |  |  |  |  |

| 140 | 25    | 46 | 77 | 103 | 120 |  |  |  |  |  |  |

| 141 | 26    | 47 | 78 | 104 |     |  |  |  |  |  |  |

| 4   | 30    | 62 | 82 | 113 |     |  |  |  |  |  |  |

| 5   | 31    | 63 | 83 | 114 |     |  |  |  |  |  |  |

**Notes:** Boundary Scan Bit 0 = TDO.T Boundary Scan Bit 1 = TDO.O

Boundary Scan Bit 1056 = BSCAN.UPD

## Pin Locations for XC5204 Devices

The following table may contain pinout information for unsupported device/package combinations. Please see the availability charts elsewhere in the XC5200 Series data sheet for availability information.

| Pin | Description | PC84 | PQ100 | VQ100 | TQ144 | PG156 | PQ160 | Boundary Scan Order |

|-----|-------------|------|-------|-------|-------|-------|-------|---------------------|

|     | VCC         | 2    | 92    | 89    | 128   | H3    | 142   | -                   |

| 1.  | I/O (A8)    | 3    | 93    | 90    | 129   | H1    | 143   | 78                  |

| 2.  | I/O (A9)    | 4    | 94    | 91    | 130   | G1    | 144   | 81                  |

| 3.  | I/O         | -    | 95    | 92    | 131   | G2    | 145   | 87                  |

| 4.  | I/O         | -    | 96    | 93    | 132   | G3    | 146   | 90                  |

| 5.  | I/O (A10)   | 5    | 97    | 94    | 133   | F1    | 147   | 93                  |

| 6.  | I/O (A11)   | 6    | 98    | 95    | 134   | F2    | 148   | 99                  |

| 7.  | I/O         | -    | -     | -     | 135   | E1    | 149   | 102                 |

| 8.  | I/O         | -    | -     | -     | 136   | E2    | 150   | 105                 |

|     | GND         | -    | -     | -     | 137   | F3    | 151   | -                   |

| 9.  | I/O         | -    | -     | -     | -     | D1    | 152   | 111                 |

| 10. | I/O         | -    | -     | -     | -     | D2    | 153   | 114                 |

| 11. | I/O (A12)   | 7    | 99    | 96    | 138   | E3    | 154   | 117                 |

| 12. | I/O (A13)   | 8    | 100   | 97    | 139   | C1    | 155   | 123                 |

| 13. | I/O         | -    | -     | -     | 140   | C2    | 156   | 126                 |

## Pin Locations for XC5206 Devices

The following table may contain pinout information for unsupported device/package combinations. Please see the availability charts elsewhere in the XC5200 Series data sheet for availability information.

| Pin | Description     | PC84 | PQ100 | VQ100 | TQ144 | PQ160 | TQ176 | PG191     | PQ208 | Boundary Scan Order |

|-----|-----------------|------|-------|-------|-------|-------|-------|-----------|-------|---------------------|

|     | VCC             | 2    | 92    | 89    | 128   | 142   | 155   | J4        | 183   | -                   |

| 1.  | I/O (A8)        | 3    | 93    | 90    | 129   | 143   | 156   | J3        | 184   | 87                  |

| 2.  | I/O (A9)        | 4    | 94    | 91    | 130   | 144   | 157   | J2        | 185   | 90                  |

| 3.  | I/O             | -    | 95    | 92    | 131   | 145   | 158   | J1        | 186   | 93                  |

| 4.  | I/O             | -    | 96    | 93    | 132   | 146   | 159   | H1        | 187   | 99                  |

| 5.  | I/O             | -    | -     | -     | -     | -     | 160   | H2        | 188   | 102                 |

| 6.  | I/O             | -    | -     | -     | -     | -     | 161   | H3        | 189   | 105                 |

| 7.  | I/O (A10)       | 5    | 97    | 94    | 133   | 147   | 162   | G1        | 190   | 111                 |

| 8.  | I/O (A11)       | 6    | 98    | 95    | 134   | 148   | 163   | G2        | 191   | 114                 |

| 9.  | I/O             | -    | -     | -     | 135   | 149   | 164   | F1        | 192   | 117                 |

| 10. | I/O             | -    | -     | -     | 136   | 150   | 165   | E1        | 193   | 123                 |

|     | GND             | -    | -     | -     | 137   | 151   | 166   | G3        | 194   | -                   |

| 11. | I/O             | -    | -     | -     | -     | 152   | 168   | C1        | 197   | 126                 |

| 12. | I/O             | -    | -     | -     | -     | 153   | 169   | E2        | 198   | 129                 |

| 13. | I/O (A12)       | 7    | 99    | 96    | 138   | 154   | 170   | F3        | 199   | 138                 |

| 14. | I/O (A13)       | 8    | 100   | 97    | 139   | 155   | 171   | D2        | 200   | 141                 |

| 15. | I/O             | -    | -     | -     | 140   | 156   | 172   | B1        | 201   | 150                 |

| 16. | I/O             | -    | -     | -     | 141   | 157   | 173   | E3        | 202   | 153                 |

| 17. | I/O (A14)       | 9    | 1     | 98    | 142   | 158   | 174   | C2        | 203   | 162                 |

| 18. | I/O (A15)       | 10   | 2     | 99    | 143   | 159   | 175   | B2        | 204   | 165                 |

|     | VCC             | 11   | 3     | 100   | 144   | 160   | 176   | D3        | 205   | -                   |

|     | GND             | 12   | 4     | 1     | 1     | 1     | 1     | D4        | 2     | -                   |

| 19. | GCK1 (A16, I/O) | 13   | 5     | 2     | 2     | 2     | 2     | C3        | 4     | 174                 |

| 20. | I/O (A17)       | 14   | 6     | 3     | 3     | 3     | 3     | C4        | 5     | 177                 |

| 21. | I/O             | -    | -     | -     | 4     | 4     | 4     | B3        | 6     | 183                 |

| 22. | I/O             | -    | -     | -     | 5     | 5     | 5     | C5        | 7     | 186                 |

| 23. | I/O (TDI)       | 15   | 7     | 4     | 6     | 6     | 6     | A2        | 8     | 189                 |

| 24. | I/O (TCK)       | 16   | 8     | 5     | 7     | 7     | 7     | B4        | 9     | 195                 |

| 25. | I/O             | -    | -     | -     | -     | 8     | 8     | C6        | 10    | 198                 |

| 26. | I/O             | -    | -     | -     | -     | 9     | 9     | A3        | 11    | 201                 |

| -   | GND             | _    | -     | -     | 8     | 10    | 10    | C7        | 14    | -                   |

| 27. | I/O             | -    | -     | -     | 9     | 11    | 11    | A4        | 15    | 207                 |

| 28. | I/O             | -    | -     | -     | 10    | 12    | 12    | A5        | 16    | 210                 |

| 29. | I/O (TMS)       | 17   | 9     | 6     | 11    | 13    | 13    | B7        | 17    | 213                 |

| 30. | I/O             | 18   | 10    | 7     | 12    | 14    | 14    | A6        | 18    | 219                 |

| 31. | I/O             | -    | -     | -     | -     | -     | 15    | C8        | 19    | 222                 |

| 32. | I/O             | -    | -     | -     | -     | -     | 16    | A7        | 20    | 225                 |

| 33. | I/O             | -    | -     | -     | 13    | 15    | 17    | B8        | 21    | 234                 |

| 34. | 1/O             | -    | 11    | 8     | 10    | 16    | 18    | A8        | 22    | 237                 |

| 35. | 1/O             | 19   | 12    | 9     | 15    | 10    | 19    | B9        | 23    | 246                 |

| 36. | 1/O             | 20   | 12    | 10    | 16    | 18    | 20    | C9        | 24    | 249                 |

|     | GND             | 20   | 10    | 10    | 10    | 19    | 20    | D9        | 25    | -                   |

|     | VCC             | 22   | 15    | 12    | 18    | 20    | 21    | D10       | 26    | -                   |

| 37. | 1/O             | 23   | 16    | 12    | 10    | 20    | 22    | C10       | 20    | 255                 |

| 38. | 1/O             | 23   | 10    | 13    | 20    | 21    | 23    | B10       | 28    | 258                 |

| 39. | 1/O             | -    | 17    | 14    | 20    | 22    | 24    | A9        | 28    | 258                 |

| 40. | 1/O             | -    | -     | -     | 21    | 23    | 25    | A9<br>A10 | 30    | 267                 |

| 40. | 1/O             |      |       |       |       |       | 20    |           | 31    | 207                 |

| 41. | 1/0             | -    | -     | -     | -     | -     | 21    | A11       | 31    | 270                 |

# XC5200 Series Field Programmable Gate Arrays

| Pin  | Description     | PC84 | TQ144 | PQ160 | TQ176    | PQ208 | PG223   | BG225 | PQ240 | Boundary Scan<br>Order |

|------|-----------------|------|-------|-------|----------|-------|---------|-------|-------|------------------------|

| 95.  | I/O             | -    | -     | -     | -        | -     | H15     | P7    | 85    | 519                    |

| 96.  | I/O             | -    | 50    | 56    | 62       | 74    | H18     | R7    | 86    | 522                    |

| 97.  | I/O             | -    | 51    | 57    | 63       | 75    | J18     | L7    | 87    | 528                    |

| 98.  | I/O             | 40   | 52    | 58    | 64       | 76    | J17     | N8    | 88    | 531                    |

| 99.  | I/O (ERR, INIT) | 41   | 53    | 59    | 65       | 77    | J16     | P8    | 89    | 534                    |

|      | VCC             | 42   | 54    | 60    | 66       | 78    | J15     | VCC*  | 90    | -                      |

|      | GND             | 43   | 55    | 61    | 67       | 79    | K15     | GND*  | 91    | -                      |

| 100. | I/O             | 44   | 56    | 62    | 68       | 80    | K16     | L8    | 92    | 540                    |

| 101. | I/O             | 45   | 57    | 63    | 69       | 81    | K17     | P9    | 93    | 543                    |

| 102. | I/O             | -    | 58    | 64    | 70       | 82    | K18     | R9    | 94    | 546                    |

| 103. | I/O             | -    | 59    | 65    | 71       | 83    | L18     | N9    | 95    | 552                    |

| 104. | I/O             | -    | -     | -     | 72       | 84    | L17     | M9    | 96    | 555                    |

| 105. | I/O             | -    | -     | -     | 73       | 85    | L16     | L9    | 97    | 558                    |

| 106. | I/O             | -    | -     | -     | -        | -     | L15     | R10   | 99    | 564                    |

| 100. | I/O             |      | -     | -     | -        | -     | M15     | P10   | 100   | 567                    |

| 107. | VCC             |      | -     | -     | _        | -     | INITO - | VCC*  | 100   | -                      |

| 108. | 1/O             | 46   | 60    | 66    | 74       | 86    | M18     | N10   | 101   | 570                    |

| 108. | I/O             | 40   | 61    | 67    | 74       | 87    | M17     | K9    | 102   | 576                    |

|      | 1/O             |      |       |       | 75       |       |         |       |       |                        |

| 110. |                 | -    | 62    | 68    |          | 88    | N18     | R11   | 104   | 579                    |

| 111. | 1/0             | -    | 63    | 69    | 77       | 89    | P18     | P11   | 105   | 588                    |

|      | GND             | -    | 64    | 70    | 78       | 90    | M16     | GND*  | 106   | -                      |

| 112. | I/O             | -    | -     | -     | -        | -     | N15     | M10   | 107   | 591                    |

| 113. | I/O             | -    | -     | -     | -        | -     | P15     | N11   | 108   | 600                    |

| 114. | I/O             | -    | -     | -     | -        | 91    | N17     | R12   | 109   | 603                    |

| 115. | I/O             | -    | -     | -     | -        | 92    | R18     | L10   | 110   | 606                    |

| 116. | I/O             | -    | -     | 71    | 79       | 93    | T18     | P12   | 111   | 612                    |

| 117. | I/O             | -    | -     | 72    | 80       | 94    | P17     | M11   | 112   | 615                    |

| 118. | I/O             | 48   | 65    | 73    | 81       | 95    | N16     | R13   | 113   | 618                    |

| 119. | I/O             | 49   | 66    | 74    | 82       | 96    | T17     | N12   | 114   | 624                    |

| 120. | I/O             | -    | 67    | 75    | 83       | 97    | R17     | P13   | 115   | 627                    |

| 121. | I/O             | -    | 68    | 76    | 84       | 98    | P16     | K10   | 116   | 630                    |

| 122. | I/O             | 50   | 69    | 77    | 85       | 99    | U18     | R14   | 117   | 636                    |

| 123. | I/O             | 51   | 70    | 78    | 86       | 100   | T16     | N13   | 118   | 639                    |

|      | GND             | 52   | 71    | 79    | 87       | 101   | R16     | GND*  | 119   | -                      |

|      | DONE            | 53   | 72    | 80    | 88       | 103   | U17     | P14   | 120   | _                      |

|      | VCC             | 54   | 73    | 81    | 89       | 106   | R15     | VCC*  | 121   | _                      |

|      | PROG            | 55   | 74    | 82    | 90       | 108   | V18     | M12   | 122   |                        |

| 124. | I/O (D7)        | 56   | 75    | 83    | 91       | 100   | T15     | P15   | 122   | 648                    |

| 125. | GCK3 (I/O)      | 57   | 76    | 84    | 92       | 110   | U16     | N14   | 123   | 651                    |

| 125. | I/O             |      | 70    | 85    | 93       | 111   | T14     | L11   | 124   | 660                    |

| 126. | 1/O             |      | 78    |       | 93<br>94 |       |         |       |       |                        |

|      |                 | -    |       | 86    | 94       | 112   | U15     | M13   | 126   | 663                    |

| 128. | I/O             | -    | -     | -     | -        | -     | R14     | N15   | 127   | 666                    |

| 129. | I/O             | -    | -     | -     | -        | -     | R13     | M14   | 128   | 672                    |

| 130. | I/O (D6)        | 58   | 79    | 87    | 95       | 113   | V17     | J10   | 129   | 675                    |

| 131. | I/O             | -    | 80    | 88    | 96       | 114   | V16     | L12   | 130   | 678                    |

| 132. | I/O             | -    | -     | 89    | 97       | 115   | T13     | M15   | 131   | 684                    |

| 133. | I/O             | -    | -     | 90    | 98       | 116   | U14     | L13   | 132   | 687                    |

| 134. | I/O             | -    | -     | -     | -        | 117   | V15     | L14   | 133   | 690                    |

| 135. | I/O             |      | -     | -     | -        | 118   | V14     | K11   | 134   | 696                    |

|      | GND             | -    | 81    | 91    | 99       | 119   | T12     | GND*  | 135   | -                      |

| 136. | I/O             | -    | -     | -     | -        | -     | R12     | L15   | 136   | 699                    |

# XC5200 Series Field Programmable Gate Arrays

| Pin  | Description         | PC84 | TQ144 | PQ160 | TQ176 | PQ208 | PG223 | BG225 | PQ240 | Boundary Scan<br>Order |

|------|---------------------|------|-------|-------|-------|-------|-------|-------|-------|------------------------|

| 137. | I/O                 | -    | -     | -     | -     | -     | R11   | K12   | 137   | 708                    |

| 138. | I/O                 | -    | 82    | 92    | 100   | 120   | U13   | K13   | 138   | 711                    |

| 139. | I/O                 | -    | 83    | 93    | 101   | 121   | V13   | K14   | 139   | 714                    |

|      | VCC                 | -    | -     | -     | -     | -     | -     | VCC*  | 140   | -                      |

| 140. | I/O (D5)            | 59   | 84    | 94    | 102   | 122   | U12   | K15   | 141   | 720                    |

| 141. | I/O ( <u>CS0</u> )  | 60   | 85    | 95    | 103   | 123   | V12   | J12   | 142   | 723                    |

| 142. | I/O                 | -    | -     | -     | 104   | 124   | T11   | J13   | 144   | 726                    |

| 143. | I/O                 | -    | -     | -     | 105   | 125   | U11   | J14   | 145   | 732                    |

| 144. | I/O                 | -    | 86    | 96    | 106   | 126   | V11   | J15   | 146   | 735                    |

| 145. | I/O                 | -    | 87    | 97    | 107   | 127   | V10   | J11   | 147   | 738                    |

| 146. | I/O (D4)            | 61   | 88    | 98    | 108   | 128   | U10   | H13   | 148   | 744                    |

| 147. | I/O                 | 62   | 89    | 99    | 109   | 129   | T10   | H14   | 149   | 747                    |

|      | VCC                 | 63   | 90    | 100   | 110   | 130   | R10   | VCC*  | 150   | -                      |

|      | GND                 | 64   | 91    | 101   | 111   | 131   | R9    | GND*  | 151   | -                      |

| 148. | I/O (D3)            | 65   | 92    | 102   | 112   | 132   | Т9    | H12   | 152   | 756                    |

| 149. | I/O (RS)            | 66   | 93    | 103   | 113   | 133   | U9    | H11   | 153   | 759                    |

| 150. | I/O                 | -    | 94    | 104   | 114   | 134   | V9    | G14   | 154   | 768                    |

| 151. | I/O                 | -    | 95    | 105   | 115   | 135   | V8    | G15   | 155   | 771                    |

| 152. | I/O                 | -    | -     | -     | 116   | 136   | U8    | G13   | 156   | 780                    |

| 153. | I/O                 | -    | -     | -     | 117   | 137   | T8    | G12   | 157   | 783                    |

| 154. | I/O (D2)            | 67   | 96    | 106   | 118   | 138   | V7    | G11   | 159   | 786                    |

| 155. | I/O                 | 68   | 97    | 107   | 119   | 139   | U7    | F15   | 160   | 792                    |

|      | VCC                 | -    | -     | -     | -     | -     | -     | VCC*  | 161   | -                      |

| 156. | I/O                 | -    | 98    | 108   | 120   | 140   | V6    | F14   | 162   | 795                    |

| 157. | I/O                 | -    | 99    | 109   | 121   | 141   | U6    | F13   | 163   | 798                    |

| 158. | I/O                 | -    | -     | -     | -     | -     | R8    | G10   | 164   | 804                    |

| 159. | I/O                 | -    | -     | -     | -     | -     | R7    | E15   | 165   | 807                    |

|      | GND                 | -    | 100   | 110   | 122   | 142   | T7    | GND*  | 166   | -                      |

| 160. | I/O                 | -    | -     | -     | -     | -     | R6    | E14   | 167   | 810                    |

| 161. | I/O                 | -    | -     | -     | -     | -     | R5    | F12   | 168   | 816                    |

| 162. | I/O                 | -    | -     | -     | -     | 143   | V5    | E13   | 169   | 819                    |

| 163. | I/O                 | -    | -     | -     | -     | 144   | V4    | D15   | 170   | 822                    |

| 164. | I/O                 | -    | -     | 111   | 123   | 145   | U5    | F11   | 171   | 828                    |

| 165. | I/O                 | -    | -     | 112   | 124   | 146   | T6    | D14   | 172   | 831                    |

| 166. | I/O (D1)            | 69   | 101   | 113   | 125   | 147   | V3    | E12   | 173   | 834                    |

| 167. | I/O (RCLK-BUSY/RDY) | 70   | 102   | 114   | 126   | 148   | V2    | C15   | 174   | 840                    |

| 168. | I/O                 | -    | 103   | 115   | 127   | 149   | U4    | D13   | 175   | 843                    |

| 169. | I/O                 | -    | 104   | 116   | 128   | 150   | T5    | C14   | 176   | 846                    |

| 170. | I/O (D0, DIN)       | 71   | 105   | 117   | 129   | 151   | U3    | F10   | 177   | 855                    |

| 171. | I/O (DOUT)          | 72   | 106   | 118   | 130   | 152   | T4    | B15   | 178   | 858                    |

|      | CCLK                | 73   | 107   | 119   | 131   | 153   | V1    | C13   | 179   | -                      |

|      | VCC                 | 74   | 108   | 120   | 132   | 154   | R4    | VCC*  | 180   | -                      |

| 172. | I/O (TDO)           | 75   | 109   | 121   | 133   | 159   | U2    | A15   | 181   | -                      |

|      | GND                 | 76   | 110   | 122   | 134   | 160   | R3    | GND*  | 182   | -                      |

| 173. | I/O (A0, WS)        | 77   | 111   | 123   | 135   | 161   | Т3    | A14   | 183   | 9                      |

| 174. | GCK4 (A1, I/O)      | 78   | 112   | 124   | 136   | 162   | U1    | B13   | 184   | 15                     |

| 175. | I/O                 | -    | 113   | 125   | 137   | 163   | P3    | E11   | 185   | 18                     |

| 176. | I/O                 | -    | 114   | 126   | 138   | 164   | R2    | C12   | 186   | 21                     |

| 177. | I/O (CS1, A2)       | 79   | 115   | 127   | 139   | 165   | T2    | A13   | 187   | 27                     |

| 178. | I/O (A3)            | 80   | 116   | 128   | 140   | 166   | N3    | B12   | 188   | 30                     |

| 179. | I/O                 | -    | -     | -     | -     | -     | P4    | F9    | 189   | 33                     |

#### **XC5200 Series Field Programmable Gate Arrays**

| Pin  | Description | PC84 | TQ144 | PQ160 | TQ176 | PQ208 | PG223 | BG225 | PQ240 | Boundary Scan<br>Order |

|------|-------------|------|-------|-------|-------|-------|-------|-------|-------|------------------------|

| 180. | I/O         | -    | -     | -     | -     | -     | N4    | D11   | 190   | 39                     |

| 181. | I/O         | -    | 117   | 129   | 141   | 167   | P2    | A12   | 191   | 42                     |

| 182. | I/O         | -    | -     | 130   | 142   | 168   | T1    | C11   | 192   | 45                     |

| 183. | I/O         | -    | -     | -     | -     | 169   | R1    | B11   | 193   | 51                     |

| 184. | I/O         | -    | -     | -     | -     | 170   | N2    | E10   | 194   | 54                     |

|      | -           | -    | -     | -     | -     | -     | -     | GND*  |       | -                      |

|      | GND         | -    | 118   | 131   | 143   | 171   | M3    | -     | 196   | -                      |

| 185. | I/O         | -    | 119   | 132   | 144   | 172   | P1    | A11   | 197   | 57                     |

| 186. | I/O         | -    | 120   | 133   | 145   | 173   | N1    | D10   | 198   | 66                     |

| 187. | I/O         | -    | -     | -     | -     | -     | M4    | C10   | 199   | 69                     |

| 188. | I/O         | -    | -     | -     | -     | -     | L4    | B10   | 200   | 75                     |

|      | VCC         | -    | -     | -     | -     | -     | -     | VCC*  | 201   | -                      |

| 189. | I/O (A4)    | 81   | 121   | 134   | 146   | 174   | M2    | A10   | 202   | 78                     |

| 190. | I/O (A5)    | 82   | 122   | 135   | 147   | 175   | M1    | D9    | 203   | 81                     |

| 191. | I/O         | -    | -     | -     | 148   | 176   | L3    | C9    | 205   | 87                     |

| 192. | I/O         | -    | -     | 136   | 149   | 177   | L2    | B9    | 206   | 90                     |

| 193. | I/O         | -    | 123   | 137   | 150   | 178   | L1    | A9    | 207   | 93                     |

| 194. | I/O         | -    | 124   | 138   | 151   | 179   | K1    | E9    | 208   | 99                     |

| 195. | I/O (A6)    | 83   | 125   | 139   | 152   | 180   | K2    | C8    | 209   | 102                    |

| 196. | I/O (A7)    | 84   | 126   | 140   | 153   | 181   | K3    | B8    | 210   | 105                    |

|      | GND         | 1    | 127   | 141   | 154   | 182   | K4    | GND*  | 211   | -                      |

#### Additional No Connect (N.C.) Connections for PQ208 and PQ240 Packages

|    |     | PQ208 | PQ240 |     |    |     |     |  |

|----|-----|-------|-------|-----|----|-----|-----|--|

| 1  | 53  | 105   | 157   | 208 | 22 | 143 | 219 |  |

| 3  | 54  | 107   | 158   |     | 37 | 158 |     |  |

| 51 | 102 | 155   | 206   |     | 83 | 195 |     |  |

| 52 | 104 | 156   | 207   |     | 98 | 204 |     |  |

**Notes:** \* Pins labeled VCC\* are internally bonded to a VCC plane within the BG225 package. The external pins are: B2, D8, H15, R8, B14, R1, H1, and R15.

Pins labeled GND\* are internally bonded to a ground plane within the BG225 package. The external pins are: A1, D12, G7, G9, H6, H8, H10, J8, K8, A8, F8, G8, H2, H7, H9, J7, J9, M8.

Boundary Scan Bit 0 = TDO.T Boundary Scan Bit 1 = TDO.O

Boundary Scan Bit 1056 = BSCAN.UPD

#### **Pin Locations for XC5215 Devices**

The following table may contain pinout information for unsupported device/package combinations. Please see the availability charts elsewhere in the XC5200 Series data sheet for availability information.

| Pin | Description | PQ160 | HQ208 | HQ240 | PG299 | BG225 | BG352 | Boundary Scan Order |

|-----|-------------|-------|-------|-------|-------|-------|-------|---------------------|

|     | VCC         | 142   | 183   | 212   | K1    | VCC*  | VCC*  | -                   |

| 1.  | I/O (A8)    | 143   | 184   | 213   | K2    | E8    | D14   | 138                 |

| 2.  | I/O (A9)    | 144   | 185   | 214   | K3    | B7    | C14   | 141                 |

| 3.  | I/O         | 145   | 186   | 215   | K5    | A7    | A15   | 147                 |

| 4.  | I/O         | 146   | 187   | 216   | K4    | C7    | B15   | 150                 |

| 5.  | I/O         | -     | 188   | 217   | J1    | D7    | C15   | 153                 |

| 6.  | I/O         | -     | 189   | 218   | J2    | E7    | D15   | 159                 |

| 7.  | I/O (A10)   | 147   | 190   | 220   | H1    | A6    | A16   | 162                 |

## **XC5200 Series Field Programmable Gate Arrays**

# **∑**XILINX<sup>®</sup>

# **Product Availability**

|        | PINS | 64             | 84             | 100            | 100            | 144            | 156           | 160            | 176            | 191           | 208               | 208            | 223           | 225           | 240               | 240            | 299           | 352           |

|--------|------|----------------|----------------|----------------|----------------|----------------|---------------|----------------|----------------|---------------|-------------------|----------------|---------------|---------------|-------------------|----------------|---------------|---------------|

|        | TYPE | Plast.<br>VQFP | Plast.<br>PLCC | Plast.<br>PQFP | Plast.<br>VQFP | Plast.<br>TQFP | Ceram.<br>PGA | Plast.<br>PQFP | Plast.<br>TQFP | Ceram.<br>PGA | High-Perf.<br>QFP | Plast.<br>PQFP | Ceram.<br>PGA | Plast.<br>BGA | High-Perf.<br>QFP | Plast.<br>PQFP | Ceram.<br>PGA | Plast.<br>BGA |

|        | CODE | VQ64*          | PC84           | PQ100          | VQ100          | TQ144          | PG156         | PQ160          | т0176          | PG191         | HQ208             | PQ208          | PG223         | BG225         | HQ240             | PQ240          | PG299         | BG352         |

|        | -6   | CI             | CI             | CI             | CI             | CI             | CI            |                |                |               |                   |                |               |               |                   |                |               |               |

| XC5202 | -5   | CI             | CI             | CI             | CI             | CI             | CI            |                |                |               |                   |                |               |               |                   |                |               |               |

| 703202 | -4   | С              | С              | С              | С              | С              | С             |                |                |               |                   |                |               |               |                   |                |               |               |

|        | -3   | С              | С              | С              | С              | С              | С             |                |                |               |                   |                |               |               |                   |                |               |               |

|        | -6   |                | CI             | CI             | CI             | CI             | CI            | CI             |                |               |                   |                |               |               |                   |                |               |               |

| XC5204 | -5   |                | CI             | CI             | CI             | CI             | CI            | CI             |                |               |                   |                |               |               |                   |                |               |               |

| 700204 | -4   |                | С              | С              | С              | С              | С             | С              |                |               |                   |                |               |               |                   |                |               |               |

|        | -3   |                | С              | С              | С              | С              | С             | С              |                |               |                   |                |               |               |                   |                |               |               |

|        | -6   |                | CI             | CI             | CI             | CI             |               | CI             | CI             | CI            |                   | CI             |               |               |                   |                |               |               |

| XC5206 | -5   |                | CI             | CI             | CI             | CI             |               | CI             | CI             | CI            |                   | CI             |               |               |                   |                |               |               |

|        | -4   |                | С              | С              | С              | С              |               | С              | С              | С             |                   | С              |               |               |                   |                |               |               |

|        | -3   |                | С              | С              | С              | С              |               | С              | С              | С             |                   | С              |               |               |                   |                |               |               |

|        | -6   |                | CI             |                |                | CI             |               | CI             | CI             |               |                   | CI             | CI            | CI            |                   | CI             |               |               |

| XC5210 | -5   |                | CI             |                |                | CI             |               | CI             | CI             |               |                   | CI             | CI            | CI            |                   | CI             |               |               |

|        | -4   |                | С              |                |                | С              |               | С              | С              |               |                   | С              | С             | С             |                   | С              |               | <u> </u>      |

|        | -3   |                | С              |                |                | С              |               | C              | С              |               |                   | С              | С             | C             |                   | С              |               |               |