# E·XFL

#### AMD Xilinx - XC5206-5PQ160C Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 196                                                        |

| Number of Logic Elements/Cells | 784                                                        |

| Total RAM Bits                 | -                                                          |

| Number of I/O                  | 133                                                        |

| Number of Gates                | 10000                                                      |

| Voltage - Supply               | 4.75V ~ 5.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 160-BQFP                                                   |

| Supplier Device Package        | 160-PQFP (28x28)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc5206-5pq160c |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **XILINX**<sup>®</sup>

#### **XC5200 Series Field Programmable Gate Arrays**

*XC3000 family:* XC5200 devices support an additional programming mode: Peripheral Synchronous.

*XC3000 family:* The XC5200 family does not support Power-down, but offers a Global 3-state input that does not reset any flip-flops.

*XC3000 family:* The XC5200 family does not provide an on-chip crystal oscillator amplifier, but it does provide an internal oscillator from which a variety of frequencies up to 12 MHz are available.

# **Architectural Overview**

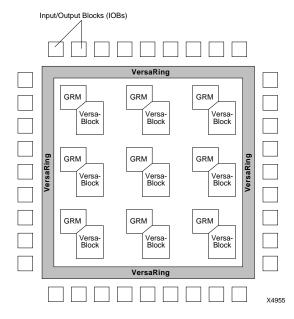

Figure 1 presents a simplified, conceptual overview of the XC5200 architecture. Similar to conventional FPGAs, the XC5200 family consists of programmable IOBs, programmable logic blocks, and programmable interconnect. Unlike other FPGAs, however, the logic and local routing resources of the XC5200 family are combined in flexible VersaBlocks (Figure 2). General-purpose routing connects to the VersaBlock through the General Routing Matrix (GRM).

#### VersaBlock: Abundant Local Routing Plus Versatile Logic

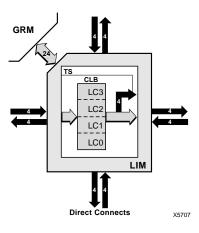

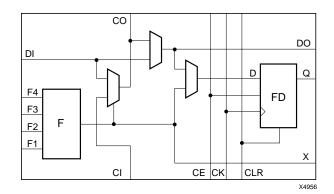

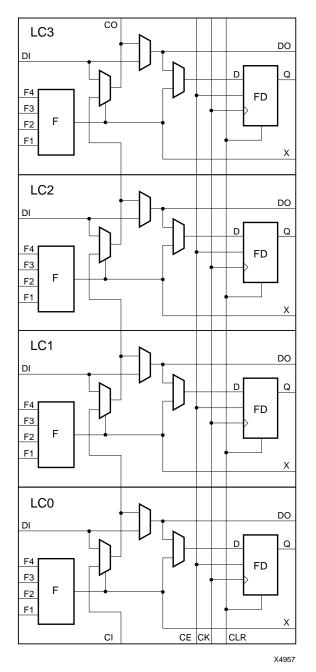

The basic logic element in each VersaBlock structure is the Logic Cell, shown in Figure 3. Each LC contains a 4-input function generator (F), a storage device (FD), and control logic. There are five independent inputs and three outputs to each LC. The independence of the inputs and outputs allows the software to maximize the resource utilization within each LC. Each Logic Cell also contains a direct feedthrough path that does not sacrifice the use of either the function generator or the register; this feature is a first for FPGAs. The storage device is configurable as either a D flip-flop or a latch. The control logic consists of carry logic for fast implementation of arithmetic functions, which can also be configured as a cascade chain allowing decode of very wide input functions.

Figure 1: XC5200 Architectural Overview

Figure 2: VersaBlock

Figure 3: XC5200 Logic Cell (Four LCs per CLB)

The XC5200 CLB consists of four LCs, as shown in Figure 4. Each CLB has 20 independent inputs and 12 independent outputs. The top and bottom pairs of LCs can be configured to implement 5-input functions. The challenge of FPGA implementation software has always been to maximize the usage of logic resources. The XC5200 family addresses this issue by surrounding each CLB with two types of local interconnect — the Local Interconnect Matrix (LIM) and direct connects. These two interconnect resources, combined with the CLB, form the VersaBlock, represented in Figure 2.

The LIM provides 100% connectivity of the inputs and outputs of each LC in a given CLB. The benefit of the LIM is that no general routing resources are required to connect feedback paths within a CLB. The LIM connects to the GRM via 24 bidirectional nodes.

The direct connects allow immediate connections to neighboring CLBs, once again without using any of the general interconnect. These two layers of local routing resource improve the granularity of the architecture, effectively making the XC5200 family a "sea of logic cells." Each Versa-Block has four 3-state buffers that share a common enable line and directly drive horizontal and vertical Lonalines, creating robust on-chip bussing capability. The VersaBlock allows fast, local implementation of logic functions, effectively implementing user designs in a hierarchical fashion. These resources also minimize local routing congestion and improve the efficiency of the general interconnect, which is used for connecting larger groups of logic. It is this combination of both fine-grain and coarse-grain architecture attributes that maximize logic utilization in the XC5200 family. This symmetrical structure takes full advantage of the third metal layer, freeing the placement software to pack user logic optimally with minimal routing restrictions.

### VersaRing I/O Interface

The interface between the IOBs and core logic has been redesigned in the XC5200 family. The IOBs are completely decoupled from the core logic. The XC5200 IOBs contain dedicated boundary-scan logic for added board-level testability, but do not include input or output registers. This approach allows a maximum number of IOBs to be placed around the device, improving the I/O-to-gate ratio and decreasing the cost per I/O. A "freeway" of interconnect cells surrounding the device forms the VersaRing, which provides connections from the IOBs to the internal logic. These incremental routing resources provide abundant connections from each IOB to the nearest VersaBlock, in addition to Longline connections surrounding the device. The VersaRing eliminates the historic trade-off between high logic utilization and pin placement flexibility. These incremental edge resources give users increased flexibility in preassigning (i.e., locking) I/O pins before completing their logic designs. This ability accelerates time-to-market, since PCBs and other system components can be manufactured concurrent with the logic design.

### **General Routing Matrix**

The GRM is functionally similar to the switch matrices found in other architectures, but it is novel in its tight coupling to the logic resources contained in the VersaBlocks. Advanced simulation tools were used during the development of the XC5200 architecture to determine the optimal level of routing resources required. The XC5200 family contains six levels of interconnect hierarchy — a series of

segments span the width and height of the chip, respectively.

Two low-skew horizontal and vertical unidirectional global-line segments span each row and column of the chip, respectively.

#### Single- and Double-Length Lines

The single- and double-length bidirectional line segments make up the bulk of the routing channels. The double-length lines hop across every other CLB to reduce the propagation delays in speed-critical nets. Regenerating the signal strength is recommended after traversing three or four such segments. Xilinx place-and-route software automatically connects buffers in the path of the signal as necessary. Single- and double-length lines cannot drive onto Longlines and global lines; Longlines and global lines can, however, drive onto single- and double-length lines. As a general rule, Longline and global-line connections to the general routing matrix are unidirectional, with the signal direction from these lines toward the routing matrix.

#### Longlines

Longlines are used for high-fan-out signals, 3-state busses, low-skew nets, and faraway destinations. Row and column splitter PIPs in the middle of the array effectively double the total number of Longlines by electrically dividing them into two separated half-lines. Longlines are driven by the 3-state buffers in each CLB, and are driven by similar buffers at the periphery of the array from the VersaRing I/O Interface.

Bus-oriented designs are easily implemented by using Longlines in conjunction with the 3-state buffers in the CLB and in the VersaRing. Additionally, weak keeper cells at the periphery retain the last valid logic level on the Longlines when all buffers are in 3-state mode.

Longlines connect to the single-length or double-length lines, or to the logic inside the CLB, through the General Routing Matrix. The only manner in which a Longline can be driven is through the four 3-state buffers; therefore, a Longline-to-Longline or single-line-to-Longline connection through PIPs in the General Routing Matrix is not possible. Again, as a general rule, long- and global-line connections to the General Routing Matrix are unidirectional, with the signal direction from these lines toward the routing matrix.

The XC5200 family has no pull-ups on the ends of the Longlines sourced by TBUFs, unlike the XC4000 Series. Consequently, wired functions (i.e., WAND and WORAND) and wide multiplexing functions requiring pull-ups for undefined states (i.e., bus applications) must be implemented in a different way. In the case of the wired functions, the same functionality can be achieved by taking advantage of the carry/cascade logic described above, implementing a wide logic function in place of the wired function. In the case of 3-state bus applications, the user must insure that all states of the multiplexing function are defined. This process is as simple as adding an additional TBUF to drive the bus High when the previously undefined states are activated.

#### **Global Lines**

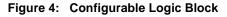

Global buffers in Xilinx FPGAs are special buffers that drive a dedicated routing network called Global Lines, as shown in Figure 16. This network is intended for high-fanout clocks or other control signals, to maximize speed and minimize skewing while distributing the signal to many loads.

The XC5200 family has a total of four global buffers (BUFG symbol in the library), each with its own dedicated routing channel. Two are distributed vertically and two horizontally throughout the FPGA.

The global lines provide direct input only to the CLB clock pins. The global lines also connect to the General Routing Matrix to provide access from these lines to the function generators and other control signals.

Four clock input pads at the corners of the chip, as shown in Figure 16, provide a high-speed, low-skew clock network to each of the four global-line buffers. In addition to the dedicated pad, the global lines can be sourced by internal logic. PIPs from several routing channels within the VersaRing can also be configured to drive the global-line buffers.

Details of all the programmable interconnect for a CLB is shown in Figure 17.

Figure 16: Global Lines

XC5200-Series devices can also be configured through the boundary scan logic. See XAPP 017 for more information.

### **Data Registers**

The primary data register is the boundary scan register. For each IOB pin in the FPGA, bonded or not, it includes three bits for In, Out and 3-State Control. Non-IOB pins have appropriate partial bit population for In or Out only. PROGRAM, CCLK and DONE are not included in the boundary scan register. Each EXTEST CAPTURE-DR state captures all In, Out, and 3-State pins.

The data register also includes the following non-pin bits: TDO.T, and TDO.O, which are always bits 0 and 1 of the data register, respectively, and BSCANT.UPD, which is always the last bit of the data register. These three boundary scan bits are special-purpose Xilinx test signals.

The other standard data register is the single flip-flop BYPASS register. It synchronizes data being passed through the FPGA to the next downstream boundary scan device.

The FPGA provides two additional data registers that can be specified using the BSCAN macro. The FPGA provides two user pins (BSCAN.SEL1 and BSCAN.SEL2) which are the decodes of two user instructions, USER1 and USER2. For these instructions, two corresponding pins (BSCAN.TDO1 and BSCAN.TDO2) allow user scan data to be shifted out on TDO. The data register clock (BSCAN.DRCK) is available for control of test logic which the user may wish to implement with CLBs. The NAND of TCK and RUN-TEST-IDLE is also provided (BSCAN.IDLE).

#### Instruction Set

The XC5200-Series boundary scan instruction set also includes instructions to configure the device and read back the configuration data. The instruction set is coded as shown in Table 7.

| Instr<br>I | ruction<br>1 IC |   | Test<br>Selected   | TDO Source         | I/O Data<br>Source |

|------------|-----------------|---|--------------------|--------------------|--------------------|

| 0          | 0               | 0 | EXTEST             | DR                 | DR                 |

| 0          | 0               | 1 | SAMPLE/PR<br>ELOAD | DR                 | Pin/Logic          |

| 0          | 1               | 0 | USER 1             | BSCAN.<br>TDO1     | User Logic         |

| 0          | 1               | 1 | USER 2             | BSCAN.<br>TDO2     | User Logic         |

| 1          | 0               | 0 | READBACK           | Readback<br>Data   | Pin/Logic          |

| 1          | 0               | 1 | CONFIGURE          | DOUT               | Disabled           |

| 1          | 1               | 0 | Reserved           | —                  | _                  |

| 1          | 1               | 1 | BYPASS             | Bypass<br>Register | —                  |

#### Table 7: Boundary Scan Instructions

#### Bit Sequence

The bit sequence within each IOB is: 3-State, Out, In. The data-register cells for the TAP pins TMS, TCK, and TDI have an OR-gate that permanently disables the output buffer if boundary-scan operation is selected. Consequently, it is impossible for the outputs in IOBs used by TAP inputs to conflict with TAP operation. TAP data is taken directly from the pin, and cannot be overwritten by injected boundary-scan data.

The primary global clock inputs (PGCK1-PGCK4) are taken directly from the pins, and cannot be overwritten with boundary-scan data. However, if necessary, it is possible to drive the clock input from boundary scan. The external clock source is 3-stated, and the clock net is driven with boundary scan data through the output driver in the clock-pad IOB. If the clock-pad IOBs are used for non-clock signals, the data may be overwritten normally.

Pull-up and pull-down resistors remain active during boundary scan. Before and during configuration, all pins are pulled up. After configuration, the choice of internal pull-up or pull-down resistor must be taken into account when designing test vectors to detect open-circuit PC traces.

From a cavity-up view of the chip (as shown in XDE or Epic), starting in the upper right chip corner, the boundary scan data-register bits are ordered as shown in Table 8. The device-specific pinout tables for the XC5200 Series include the boundary scan locations for each IOB pin.

**Table 8: Boundary Scan Bit Sequence**

| Bit Position | I/O Pad Location                     |

|--------------|--------------------------------------|

| Bit 0 (TDO)  | Top-edge I/O pads (right to left)    |

| Bit 1        |                                      |

|              | Left-edge I/O pads (top to bottom)   |

|              | Bottom-edge I/O pads (left to right) |

|              | Right-edge I/O pads (bottom to top)  |

| Bit N (TDI)  | BSCANT.UPD                           |

BSDL (Boundary Scan Description Language) files for XC5200-Series devices are available on the Xilinx web site in the File Download area.

#### **Including Boundary Scan**

If boundary scan is only to be used during configuration, no special elements need be included in the schematic or HDL code. In this case, the special boundary scan pins TDI, TMS, TCK and TDO can be used for user functions after configuration.

To indicate that boundary scan remain enabled after configuration, include the BSCAN library symbol and connect pad symbols to the TDI, TMS, TCK and TDO pins, as shown in Figure 20.

tions During Configuration" on page 124, in the "Configuration Timing" section.

**Table 9: Pin Descriptions**

| Pin Name<br>Permanently I | I/O<br>During<br>Config.<br>Dedicated | I/O<br>After<br>Config.<br>I Pins | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------|---------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC                       | I                                     | 1                                 | Five or more (depending on package) connections to the nominal +5 V supply voltage. All must be connected, and each must be decoupled with a 0.01 - 0.1 $\mu$ F capacitor to Ground.                                                                                                                                                                                                                                                                                                                                                            |

| GND                       | I                                     | I                                 | Four or more (depending on package type) connections to Ground. All must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CCLK                      | l or O                                | I                                 | During configuration, Configuration Clock (CCLK) is an output in Master modes or Asyn-<br>chronous Peripheral mode, but is an input in Slave mode, Synchronous Peripheral<br>mode, and Express mode. After configuration, CCLK has a weak pull-up resistor and<br>can be selected as the Readback Clock. There is no CCLK High time restriction on<br>XC5200-Series devices, except during Readback. See "Violating the Maximum High<br>and Low Time Specification for the Readback Clock" on page 113 for an explanation of<br>this exception. |

| DONE                      | I/O                                   | 0                                 | DONE is a bidirectional signal with an optional internal pull-up resistor. As an output, it indicates the completion of the configuration process. As an input, a Low level on DONE can be configured to delay the global logic initialization and the enabling of outputs.<br>The exact timing, the clock source for the Low-to-High transition, and the optional pull-up resistor are selected as options in the program that creates the configuration bit-stream. The resistor is included by default.                                      |

| PROGRAM                   | I                                     | I                                 | PROGRAM is an active Low input that forces the FPGA to clear its configuration mem-<br>ory. It is used to initiate a configuration cycle. When PROGRAM goes High, the FPGA<br>executes a complete clear cycle, before it goes into a WAIT state and releases INIT.<br>The PROGRAM pin has an optional weak pull-up after configuration.                                                                                                                                                                                                         |

| User I/O Pins             | That Can                              | Have Sp                           | ecial Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RDY/BUSY                  | 0                                     | I/O                               | During Peripheral mode configuration, this pin indicates when it is appropriate to write<br>another byte of data into the FPGA. The same status is also available on D7 in Asyn-<br>chronous Peripheral mode, if a read operation is performed when the device is selected.<br>After configuration, RDY/BUSY is a user-programmable I/O pin.<br>RDY/BUSY is pulled High with a high-impedance pull-up prior to INIT going High.                                                                                                                 |

| RCLK                      | 0                                     | I/O                               | During Master Parallel configuration, each change on the A0-A17 outputs is preceded<br>by a rising edge on RCLK, a redundant output signal. RCLK is useful for clocked<br>PROMs. It is rarely used during configuration. After configuration, RCLK is a user-pro-<br>grammable I/O pin.                                                                                                                                                                                                                                                         |

| M0, M1, M2                | I                                     | I/O                               | As Mode inputs, these pins are sampled before the start of configuration to determine the configuration mode to be used. After configuration, M0, M1, and M2 become user-programmable I/O. During configuration, these pins have weak pull-up resistors. For the most popular configuration mode, Slave Serial, the mode pins can thus be left unconnected. A pull-down resistor value of 3.3 k $\Omega$ is recommended for other modes.                                                                                                        |

| TDO                       | 0                                     | 0                                 | If boundary scan is used, this pin is the Test Data Output. If boundary scan is not used, this pin is a 3-state output, after configuration is completed.<br>This pin can be user output only when called out by special schematic definitions. To use this pin, place the library component TDO instead of the usual pad symbol. An output buffer must still be used.                                                                                                                                                                          |

**∑**XILINX<sup>®</sup>

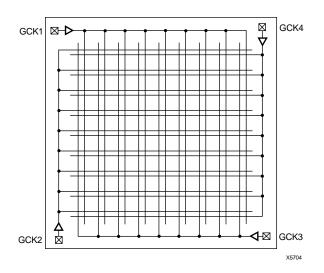

Figure 22: CCLK Generation for XC3000 Master Driving an XC5200-Series Slave

#### Express Mode

Express mode is similar to Slave Serial mode, except the data is presented in parallel format, and is clocked into the target device a byte at a time rather than a bit at a time. The data is loaded in parallel into eight different columns: it is not internally serialized. Eight bits of configuration data are loaded with every CCLK cycle, therefore this configuration mode runs at eight times the data rate of the other six modes. In this mode the XC5200 family is capable of supporting a CCLK frequency of 10 MHz, which is equivalent to an 80 MHz serial rate, because eight bits of configuration data are being loaded per CCLK cycle. An XC5210 in the Express mode, for instance, can be configured in about 2 ms. The Express mode does not support CRC error checking, but does support constant-field error checking. A length count is not used in Express mode.

In the Express configuration mode, an external signal drives the CCLK input(s). The first byte of parallel configuration data must be available at the D inputs of the FPGA devices a short set-up time before the second rising CCLK edge. Subsequent data bytes are clocked in on each consecutive rising CCLK edge. See Figure 38 on page 123.

Bitstream generation currently generates a bitstream sufficient to program in all configuration modes except Express. Extra CCLK cycles are necessary to complete the configuration, since in this mode data is read at a rate of eight bits per CCLK cycle instead of one bit per cycle. Normally the entire start-up sequence requires a number of bits that is equal to the number of CCLK cycles needed. An additional five CCLKs (equivalent to 40 extra bits) will guarantee completion of configuration, regardless of the start-up options chosen.

Multiple slave devices with identical configurations can be wired with parallel D0-D7 inputs. In this way, multiple devices can be configured simultaneously.

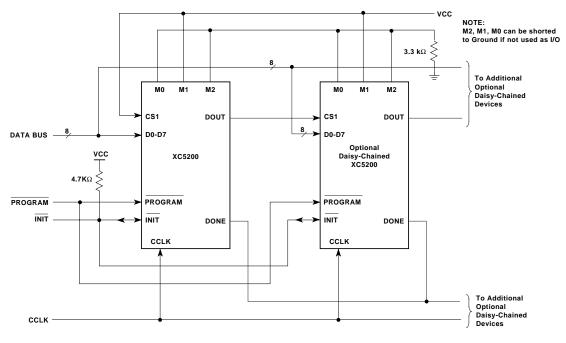

#### **Pseudo Daisy Chain**

Multiple devices with different configurations can be connected together in a pseudo daisy chain, provided that all of the devices are in Express mode. A single combined bitstream is used to configure the chain of Express mode devices, but the input data bus must drive D0-D7 of each device. Tie High the CS1 pin of the first device to be configured, or leave it floating in the XC5200 since it has an internal pull-up. Connect the DOUT pin of each FPGA to the CS1 pin of the next device in the chain. The D0-D7 inputs are wired to each device in parallel. The DONE pins are wired together, with one or more internal DONE pull-ups activated. Alternatively, a 4.7 k $\Omega$  external resistor can be used, if desired. (See Figure 37 on page 122.) CCLK pins are tied together.

The requirement that all DONE pins in a daisy chain be wired together applies only to Express mode, and only if all devices in the chain are to become active simultaneously. All devices in Express mode are synchronized to the DONE pin. User I/O for each device become active after the DONE pin for that device goes High. (The exact timing is determined by options to the bitstream generation software.) Since the DONE pin is open-drain and does not drive a High value, tying the DONE pins of all devices together prevents all devices in the chain from going High until the last device in the chain has completed its configuration cycle.

The status pin DOUT is pulled LOW two internal-oscillator cycles (nominally 1 MHz) after INIT is recognized as High, and remains Low until the device's configuration memory is full. Then DOUT is pulled High to signal the next device in the chain to accept the configuration data on the D7-D0 bus. All devices receive and recognize the six bytes of preamble and length count, irrespective of the level on CS1; but subsequent frame data is accepted only when CS1 is High and the device's configuration memory is not already full.

#### Setting CCLK Frequency

For Master modes, CCLK can be generated in one of three frequencies. In the default slow mode, the frequency is nominally 1 MHz. In fast CCLK mode, the frequency is nominally 12 MHz. In medium CCLK mode, the frequency is nominally 6 MHz. The frequency range is -50% to +50%. The frequency is selected by an option when running the bitstream generation software. If an XC5200-Series Master is driving an XC3000- or XC2000-family slave, slow CCLK mode must be used. Slow mode is the default.

#### Table 11: XC5200 Bitstream Format

| Data Type      | Value       | Occurrences   |

|----------------|-------------|---------------|

| Fill Byte      | 11111111    | Once per bit- |

| Preamble       | 11110010    | stream        |

| Length Counter | COUNT(23:0) |               |

| Fill Byte      | 11111111    |               |

#### **XC5200 Series Field Programmable Gate Arrays**

Note that in XC5200-Series devices, configuration data is *not* inverted with respect to configuration as it is in XC2000 and XC3000 families.

Readback of Express mode bitstreams results in data that does not resemble the original bitstream, because the bitstream format differs from other modes.

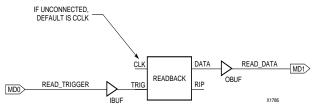

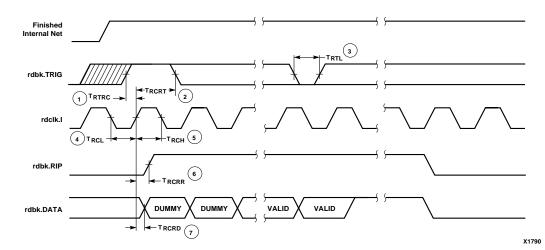

XC5200-Series Readback does not use any dedicated pins, but uses four internal nets (RDBK.TRIG, RDBK.DATA, RDBK.RIP and RDBK.CLK) that can be routed to any IOB. To access the internal Readback signals, place the READBACK library symbol and attach the appropriate pad symbols, as shown in Figure 27.

After Readback has been initiated by a Low-to-High transition on RDBK.TRIG, the RDBK.RIP (Read In Progress) output goes High on the next rising edge of RDBK.CLK. Subsequent rising edges of this clock shift out Readback data on the RDBK.DATA net.

Readback data does not include the preamble, but starts with five dummy bits (all High) followed by the Start bit (Low) of the first frame. The first two data bits of the first frame are always High.

Each frame ends with four error check bits. They are read back as High. The last seven bits of the last frame are also read back as High. An additional Start bit (Low) and an 11-bit Cyclic Redundancy Check (CRC) signature follow, before RDBK.RIP returns Low.

Figure 27: Readback Schematic Example

#### **Readback Options**

Readback options are: Read Capture, Read Abort, and Clock Select. They are set with the bitstream generation software.

#### **Read Capture**

When the Read Capture option is selected, the readback data stream includes sampled values of CLB and IOB signals. The rising edge of RDBK.TRIG latches the inverted values of the CLB outputs and the IOB output and input signals. Note that while the bits describing configuration (interconnect and function generators) are *not* inverted, the CLB and IOB output signals *are* inverted.

When the Read Capture option is not selected, the values of the capture bits reflect the configuration data originally written to those memory locations. The readback signals are located in the lower-left corner of the device.

#### **Read Abort**

When the Read Abort option is selected, a High-to-Low transition on RDBK.TRIG terminates the readback operation and prepares the logic to accept another trigger.

After an aborted readback, additional clocks (up to one readback clock per configuration frame) may be required to re-initialize the control logic. The status of readback is indicated by the output control net RDBK.RIP. RDBK.RIP is High whenever a readback is in progress.

#### **Clock Select**

CCLK is the default clock. However, the user can insert another clock on RDBK.CLK. Readback control and data are clocked on rising edges of RDBK.CLK. If readback must be inhibited for security reasons, the readback control nets are simply not connected.

# Violating the Maximum High and Low Time Specification for the Readback Clock

The readback clock has a maximum High and Low time specification. In some cases, this specification cannot be met. For example, if a processor is controlling readback, an interrupt may force it to stop in the middle of a readback. This necessitates stopping the clock, and thus violating the specification.

The specification is mandatory only on clocking data at the end of a frame prior to the next start bit. The transfer mechanism will load the data to a shift register during the last six clock cycles of the frame, prior to the start bit of the following frame. This loading process is dynamic, and is the source of the maximum High and Low time requirements.

Therefore, the specification only applies to the six clock cycles prior to and including any start bit, including the clocks before the first start bit in the readback data stream. At other times, the frame data is already in the register and the register is not dynamic. Thus, it can be shifted out just like a regular shift register.

The user must precisely calculate the location of the readback data relative to the frame. The system must keep track of the position within a data frame, and disable interrupts before frame boundaries. Frame lengths and data formats are listed in Table 11 and Table 12.

#### Readback with the XChecker Cable

The XChecker Universal Download/Readback Cable and Logic Probe uses the readback feature for bitstream verification. It can also display selected internal signals on the PC or workstation screen, functioning as a low-cost in-circuit emulator.

### **XC5200 Series Field Programmable Gate Arrays**

TO DIN OF OPTIONAL HIGH DAISY-CHAINED FPGAS or LOW 3.3 K N/C  $\sim$ N/C M1 M2 M0 TO CCLK OF OPTIONAL DAISY-CHAINED FPGAS CCLK DOUT NOTE:M0 can be shorted to Ground if not used as I/O. MO M1 M2 A17 XC5200 A16 DOUT DIN VCC Master EPROM Parallel A15 (8K x 8) (OR LARGER) CCLK ≶ X 4.7K A14 XC5200/ USER CONTROL OF HIGHER INIT A13 ORDER PROM ADDRESS BITS XC4000E/EX/ Spartan SLAVE CAN BE USED TO SELECT BETWEEN A12 A12 ALTERNATIVE CONFIGURATIONS A11 A11 PROGRAM A10 A10 PROGRAM A9 A9 DONE INIT  $\leftrightarrow$ D7 A8 A8 D6 A7 A7 D7 D5 A6 A6 D6 D4 A5 D5 A5 D3 A4 > A4 D4 D2 A3 D3 A3 D1 A2 D2 A2 D0 A1 A1 D1 A0 D0 A0 ŌE DONE > CE DATA BUS / 8 PROGRAM

Figure 31: Master Parallel Mode Circuit Diagram

X9004\_01

**XILINX<sup>®</sup>**

### **Express Mode**

Express mode is similar to Slave Serial mode, except that data is processed one byte per CCLK cycle instead of one bit per CCLK cycle. An external source is used to drive CCLK, while byte-wide data is loaded directly into the configuration data shift registers. A CCLK frequency of 10 MHz is equivalent to an 80 MHz serial rate, because eight bits of configuration data are loaded per CCLK cycle. Express mode does not support CRC error checking, but does support constant-field error checking.

In Express mode, an external signal drives the CCLK input of the FPGA device. The first byte of parallel configuration data must be available at the D inputs of the FPGA a short setup time before the second rising CCLK edge. Subsequent data bytes are clocked in on each consecutive rising CCLK edge.

If the first device is configured in Express mode, additional devices may be daisy-chained only if every device in the chain is also configured in Express mode. CCLK pins are tied together and D0-D7 pins are tied together for all devices along the chain. A status signal is passed from DOUT to CS1 of successive devices along the chain. The lead device in the chain has its CS1 input tied High (or floating, since there is an internal pullup). Frame data is accepted only when CS1 is High and the device's configu-

ration memory is not already full. The status <u>pin</u> DOUT is pulled Low two internal-oscillator cycles after INIT is recognized as High, and remains Low until the device's configuration memory is full. DOUT is then pulled High to signal the next device in the chain to accept the configuration data on the D0-D7 bus.

The DONE pins of all devices in the chain should be tied together, with one or more active internal pull-ups. If a large number of devices are included in the chain, deactivate some of the internal pull-ups, since the Low-driving DONE pin of the last device in the chain must sink the current from all pull-ups in the chain. The DONE pull-up is activated by default. It can be deactivated using an option in the bitstream generation software.

XC5200 devices in Express mode are always synchronized to DONE. The device becomes active after DONE goes High. DONE is an open-drain output. With the DONE pins tied together, therefore, the external DONE signal stays low until all devices are configured, then all devices in the daisy chain become active simultaneously. If the DONE pin of a device is left unconnected, the device becomes active as soon as that device has been configured.

Express mode is selected by a <010> on the mode pins (M2, M1, M0).

X6611\_01

Figure 37: Express Mode Circuit Diagram

### XC5200 Program Readback Switching Characteristic Guidelines

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Internal timing parameters are not measured directly. They are derived from benchmark timing patterns that are taken at device introduction, prior to any process improvements.

The following guidelines reflect worst-case values over the recommended operating conditions.

|           | Description                                    | S | Symbol            | Min | Max | Units |

|-----------|------------------------------------------------|---|-------------------|-----|-----|-------|

| rdbk.TRIG | rdbk.TRIG setup to initiate and abort Readback | 1 | T <sub>RTRC</sub> | 200 | -   | ns    |

|           | rdbk.TRIG hold to initiate and abort Readback  | 2 | T <sub>RCRT</sub> | 50  | -   | ns    |

| rdclk.1   | rdbk.DATA delay                                | 7 | T <sub>RCRD</sub> | -   | 250 | ns    |

|           | rdbk.RIP delay                                 | 6 | T <sub>RCRR</sub> | -   | 250 | ns    |

|           | High time                                      | 5 | T <sub>RCH</sub>  | 250 | 500 | ns    |

|           | Low time                                       | 4 | T <sub>RCL</sub>  | 250 | 500 | ns    |

Note 1: Timing parameters apply to all speed grades.

Note 2: rdbk.TRIG is High prior to Finished, Finished will trigger the first Readback

| <7 | VII | Ð |

|----|-----|---|

| <⊾ | ЛΙ  |   |

| Pin | Description            | VQ64* | PC84     | PQ100 | VQ100    | TQ144 | PG156 | Boundary Scan Order |

|-----|------------------------|-------|----------|-------|----------|-------|-------|---------------------|

| 35. | I/O (HDC)              | 19    | 36       | 31    | 28       | 40    | D14   | 204                 |

| 36. | I/O                    | -     | -        | 32    | 29       | 43    | E14   | 207                 |

| 37. | I/O (LDC)              | 20    | 37       | 33    | 30       | 44    | C16   | 210                 |

|     | GND                    | -     | -        | -     | -        | 45    | F14   | -                   |

| 38. | I/O                    | -     | 38       | 34    | 31       | 48    | F16   | 216                 |

| 39. | I/O                    | 21    | 39       | 35    | 32       | 49    | G14   | 219                 |

| 40. | I/O                    | -     | -        | 36    | 33       | 50    | G15   | 222                 |

| 41. | I/O                    | -     | -        | 37    | 34       | 51    | G16   | 228                 |

| 42. | I/O                    | 22    | 40       | 38    | 35       | 52    | H16   | 231                 |

| 43. | I/O (ERR, INIT)        | 23    | 41       | 39    | 36       | 53    | H15   | 234                 |

|     | VCC                    | 24    | 42       | 40    | 37       | 54    | H14   | -                   |

|     | GND                    | 25    | 43       | 41    | 38       | 55    | J14   | -                   |

| 44. | I/O                    | 26    | 44       | 42    | 39       | 56    | J15   | 240                 |

| 45. | I/O                    | 27    | 45       | 43    | 40       | 57    | J16   | 243                 |

| 46. | I/O                    | -     | -        | 44    | 41       | 58    | K16   | 246                 |

| 47. | I/O                    | -     | -        | 45    | 42       | 59    | K15   | 252                 |

| 48. | I/O                    | 28    | 46       | 46    | 43       | 60    | K14   | 255                 |

| 49. | I/O                    | 29    | 47       | 47    | 44       | 61    | L16   | 258                 |

|     | GND                    | -     | -        | -     | -        | 64    | L14   | -                   |

| 50. | 1/0                    | -     | 48       | 48    | 45       | 65    | P16   | 264                 |

| 51. | I/O                    | 30    | 49       | 49    | 46       | 66    | M14   | 267                 |

| 52. | I/O                    | -     | 50       | 50    | 40       | 69    | N14   | 276                 |

| 53. | I/O                    | 31    | 50       | 50    | 48       | 70    | R16   | 279                 |

| 55. | GND                    | -     | 52       | 52    | 49       | 70    | P14   | -                   |

|     | DONE                   | 32    | 53       | 53    | 49<br>50 | 71    | R15   | -                   |

|     | VCC                    | 32    | 53<br>54 | 53    | 50       | 72    | P13   | -                   |

|     | PROG                   | 33    | 55       | 55    | 52       | 73    | R14   | -                   |

| E 4 |                        |       |          |       | 52       |       |       |                     |

| 54. | I/O (D7)               | 35    | 56       | 56    |          | 75    | T16   | 288                 |

| 55. | GCK3 (I/O)             | 36    | 57       | 57    | 54       | 76    | T15   | 291                 |

| 56. | I/O (D6)               | 37    | 58       | 58    | 55       | 79    | T14   | 300                 |

| 57. | I/O                    | -     | -        | 59    | 56       | 80    | T13   | 303                 |

|     | GND                    | -     | -        | -     | -        | 81    | P11   | -                   |

| 58. | I/O (D5)               | 38    | 59       | 60    | 57       | 84    | T10   | 306                 |

| 59. | I/O (CS0)              | -     | 60       | 61    | 58       | 85    | P10   | 312                 |

| 60. | I/O                    | -     | -        | 62    | 59       | 86    | R10   | 315                 |

| 61. | I/O                    | -     | -        | 63    | 60       | 87    | T9    | 318                 |

| 62. | I/O (D4)               | 39    | 61       | 64    | 61       | 88    | R9    | 324                 |

| 63. | I/O                    | -     | 62       | 65    | 62       | 89    | P9    | 327                 |

|     | VCC                    | 40    | 63       | 66    | 63       | 90    | R8    | -                   |

|     | GND                    | 41    | 64       | 67    | 64       | 91    | P8    | -                   |

| 64. | I/O (D3)               | 42    | 65       | 68    | 65       | 92    | Т8    | 336                 |

| 65. | I/O (RS)               | 43    | 66       | 69    | 66       | 93    | T7    | 339                 |

| 66. | I/O                    | -     | -        | 70    | 67       | 94    | Т6    | 342                 |

| 67. | I/O                    | -     | -        | -     | -        | 95    | R7    | 348                 |

| 68. | I/O (D2)               | 44    | 67       | 71    | 68       | 96    | P7    | 351                 |

| 69. | I/O                    | -     | 68       | 72    | 69       | 97    | T5    | 360                 |

|     | GND                    | -     | -        | -     | -        | 100   | P6    | -                   |

| 70. | I/O (D1)               | 45    | 69       | 73    | 70       | 101   | T3    | 363                 |

| 71. | I/O<br>(RCLK-BUSY/RDY) | -     | 70       | 74    | 71       | 102   | P5    | 366                 |

| 72. | I/O (D0, DIN)          | 46    | 71       | 75    | 72       | 105   | P4    | 372                 |

| 73. | I/O (DOUT)             | 47    | 72       | 76    | 73       | 106   | T2    | 375                 |

### Pin Locations for XC5206 Devices

The following table may contain pinout information for unsupported device/package combinations. Please see the availability charts elsewhere in the XC5200 Series data sheet for availability information.

| Pin | Description     | PC84 | PQ100 | VQ100 | TQ144 | PQ160 | TQ176 | PG191     | PQ208 | Boundary Scan Order |

|-----|-----------------|------|-------|-------|-------|-------|-------|-----------|-------|---------------------|

|     | VCC             | 2    | 92    | 89    | 128   | 142   | 155   | J4        | 183   | -                   |

| 1.  | I/O (A8)        | 3    | 93    | 90    | 129   | 143   | 156   | J3        | 184   | 87                  |

| 2.  | I/O (A9)        | 4    | 94    | 91    | 130   | 144   | 157   | J2        | 185   | 90                  |

| 3.  | I/O             | -    | 95    | 92    | 131   | 145   | 158   | J1        | 186   | 93                  |

| 4.  | I/O             | -    | 96    | 93    | 132   | 146   | 159   | H1        | 187   | 99                  |

| 5.  | I/O             | -    | -     | -     | -     | -     | 160   | H2        | 188   | 102                 |

| 6.  | I/O             | -    | -     | -     | -     | -     | 161   | H3        | 189   | 105                 |

| 7.  | I/O (A10)       | 5    | 97    | 94    | 133   | 147   | 162   | G1        | 190   | 111                 |

| 8.  | I/O (A11)       | 6    | 98    | 95    | 134   | 148   | 163   | G2        | 191   | 114                 |

| 9.  | I/O             | -    | -     | -     | 135   | 149   | 164   | F1        | 192   | 117                 |

| 10. | I/O             | -    | -     | -     | 136   | 150   | 165   | E1        | 193   | 123                 |

|     | GND             | -    | -     | -     | 137   | 151   | 166   | G3        | 194   | -                   |

| 11. | I/O             | -    | -     | -     | -     | 152   | 168   | C1        | 197   | 126                 |

| 12. | I/O             | -    | -     | -     | -     | 153   | 169   | E2        | 198   | 129                 |

| 13. | I/O (A12)       | 7    | 99    | 96    | 138   | 154   | 170   | F3        | 199   | 138                 |

| 14. | I/O (A13)       | 8    | 100   | 97    | 139   | 155   | 171   | D2        | 200   | 141                 |

| 15. | I/O             | -    | -     | -     | 140   | 156   | 172   | B1        | 201   | 150                 |

| 16. | I/O             | -    | -     | -     | 141   | 157   | 173   | E3        | 202   | 153                 |

| 17. | I/O (A14)       | 9    | 1     | 98    | 142   | 158   | 174   | C2        | 203   | 162                 |

| 18. | I/O (A15)       | 10   | 2     | 99    | 143   | 159   | 175   | B2        | 204   | 165                 |

|     | VCC             | 11   | 3     | 100   | 144   | 160   | 176   | D3        | 205   | -                   |

|     | GND             | 12   | 4     | 1     | 1     | 1     | 1     | D4        | 2     | -                   |

| 19. | GCK1 (A16, I/O) | 13   | 5     | 2     | 2     | 2     | 2     | C3        | 4     | 174                 |

| 20. | I/O (A17)       | 14   | 6     | 3     | 3     | 3     | 3     | C4        | 5     | 177                 |

| 21. | I/O             | -    | -     | -     | 4     | 4     | 4     | B3        | 6     | 183                 |

| 22. | I/O             | -    | -     | -     | 5     | 5     | 5     | C5        | 7     | 186                 |

| 23. | I/O (TDI)       | 15   | 7     | 4     | 6     | 6     | 6     | A2        | 8     | 189                 |

| 24. | I/O (TCK)       | 16   | 8     | 5     | 7     | 7     | 7     | B4        | 9     | 195                 |

| 25. | I/O             | -    | -     | -     | -     | 8     | 8     | C6        | 10    | 198                 |

| 26. | I/O             | -    | -     | -     | -     | 9     | 9     | A3        | 11    | 201                 |

| -   | GND             | _    | -     | -     | 8     | 10    | 10    | C7        | 14    | -                   |

| 27. | I/O             | -    | -     | -     | 9     | 11    | 11    | A4        | 15    | 207                 |

| 28. | I/O             | -    | -     | -     | 10    | 12    | 12    | A5        | 16    | 210                 |

| 29. | I/O (TMS)       | 17   | 9     | 6     | 11    | 13    | 13    | B7        | 17    | 213                 |

| 30. | I/O             | 18   | 10    | 7     | 12    | 14    | 14    | A6        | 18    | 219                 |

| 31. | I/O             | -    | -     | -     | -     | -     | 15    | C8        | 19    | 222                 |

| 32. | I/O             | -    | -     | -     | -     | -     | 16    | A7        | 20    | 225                 |

| 33. | I/O             | -    | -     | -     | 13    | 15    | 17    | B8        | 21    | 234                 |

| 34. | 1/O             | -    | 11    | 8     | 10    | 16    | 18    | A8        | 22    | 237                 |

| 35. | 1/O             | 19   | 12    | 9     | 15    | 10    | 19    | B9        | 23    | 246                 |

| 36. | 1/O             | 20   | 12    | 10    | 16    | 18    | 20    | C9        | 24    | 249                 |

|     | GND             | 20   | 10    | 10    | 10    | 19    | 20    | D9        | 25    | -                   |

|     | VCC             | 22   | 15    | 12    | 18    | 20    | 21    | D10       | 26    | -                   |

| 37. | 1/O             | 23   | 16    | 12    | 10    | 20    | 22    | C10       | 20    | 255                 |

| 38. | 1/O             | 23   | 10    | 13    | 20    | 21    | 23    | B10       | 28    | 258                 |

| 39. | 1/O             | -    | 17    | 14    | 20    | 22    | 24    | A9        | 28    | 258                 |

| 40. | 1/O             | -    | -     | -     | 21    | 23    | 25    | A9<br>A10 | 30    | 267                 |

| 40. | 1/O             |      |       |       |       |       | 20    |           | 31    | 270                 |

| 41. | 1/0             | -    | -     | -     | -     | -     | 21    | A11       | 31    | 270                 |

| Pin  | Description                | PC84 | PQ100 | VQ100 | TQ144 | PQ160 | TQ176 | PG191 | PQ208 | Boundary Scan Order |

|------|----------------------------|------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| 87.  | I/O                        | -    | -     | -     | -     | 72    | 80    | P17   | 94    | 468                 |

| 88.  | I/O                        | 48   | 48    | 45    | 65    | 73    | 81    | N16   | 95    | 471                 |

| 89.  | I/O                        | 49   | 49    | 46    | 66    | 74    | 82    | T17   | 96    | 480                 |

| 90.  | I/O                        | -    | -     | -     | 67    | 75    | 83    | R17   | 97    | 483                 |

| 91.  | I/O                        | -    | -     | -     | 68    | 76    | 84    | P16   | 98    | 486                 |

| 92.  | I/O                        | 50   | 50    | 47    | 69    | 77    | 85    | U18   | 99    | 492                 |

| 93.  | I/O                        | 51   | 51    | 48    | 70    | 78    | 86    | T16   | 100   | 495                 |

|      | GND                        | 52   | 52    | 49    | 71    | 79    | 87    | R16   | 101   | -                   |

|      | DONE                       | 53   | 53    | 50    | 72    | 80    | 88    | U17   | 103   | -                   |

|      | VCC                        | 54   | 54    | 51    | 73    | 81    | 89    | R15   | 106   | -                   |

|      | PROG                       | 55   | 55    | 52    | 74    | 82    | 90    | V18   | 108   | -                   |

| 94.  | I/O (D7)                   | 56   | 56    | 53    | 75    | 83    | 91    | T15   | 109   | 504                 |

| 95.  | GCK3 (I/O)                 | 57   | 57    | 54    | 76    | 84    | 92    | U16   | 110   | 507                 |

| 96.  | I/O                        | -    | -     | -     | 77    | 85    | 93    | T14   | 111   | 516                 |

| 97.  | I/O                        | -    | -     | -     | 78    | 86    | 94    | U15   | 112   | 519                 |

| 98.  | I/O (D6)                   | 58   | 58    | 55    | 79    | 87    | 95    | V17   | 113   | 522                 |

| 99.  | I/O                        | -    | 59    | 56    | 80    | 88    | 96    | V16   | 114   | 528                 |

| 100. | I/O                        | -    | -     | -     | -     | 89    | 97    | T13   | 115   | 531                 |

| 101. | I/O                        | -    | -     | -     | -     | 90    | 98    | U14   | 116   | 534                 |

|      | GND                        | -    | -     | -     | 81    | 91    | 99    | T12   | 119   | -                   |

| 102. | I/O                        | -    | -     | -     | 82    | 92    | 100   | U13   | 120   | 540                 |

| 103. | I/O                        | -    | -     | -     | 83    | 93    | 101   | V13   | 121   | 543                 |

| 104. | I/O (D5)                   | 59   | 60    | 57    | 84    | 94    | 102   | U12   | 122   | 552                 |

| 105. | I/O ( <u>CS0</u> )         | 60   | 61    | 58    | 85    | 95    | 103   | V12   | 123   | 555                 |

| 106. | I/O                        | -    | -     | -     | -     | -     | 104   | T11   | 124   | 558                 |

| 107. | I/O                        | -    | -     | -     | -     | -     | 105   | U11   | 125   | 564                 |

| 108. | I/O                        | -    | 62    | 59    | 86    | 96    | 106   | V11   | 126   | 567                 |

| 109. | I/O                        | -    | 63    | 60    | 87    | 97    | 107   | V10   | 127   | 570                 |

| 110. | I/O (D4)                   | 61   | 64    | 61    | 88    | 98    | 108   | U10   | 128   | 576                 |

| 111. | I/O                        | 62   | 65    | 62    | 89    | 99    | 109   | T10   | 129   | 579                 |

|      | VCC                        | 63   | 66    | 63    | 90    | 100   | 110   | R10   | 130   | -                   |

|      | GND                        | 64   | 67    | 64    | 91    | 101   | 111   | R9    | 131   | -                   |

| 112. | I/O (D3)                   | 65   | 68    | 65    | 92    | 102   | 112   | T9    | 132   | 588                 |

| 113. | I/O (RS)                   | 66   | 69    | 66    | 93    | 103   | 113   | U9    | 133   | 591                 |

| 114. | 1/O                        | -    | 70    | 67    | 94    | 104   | 114   | V9    | 134   | 600                 |

| 115. | I/O                        | -    | -     | -     | 95    | 105   | 115   | V8    | 135   | 603                 |

| 116. | I/O                        | -    | -     | -     | -     | -     | 116   | U8    | 136   | 612                 |

| 117. | I/O                        | -    | -     | -     | -     | -     | 117   | Т8    | 137   | 615                 |

| 118. | I/O (D2)                   | 67   | 71    | 68    | 96    | 106   | 118   | V7    | 138   | 618                 |

| 119. | I/O                        | 68   | 72    | 69    | 97    | 107   | 119   | U7    | 139   | 624                 |

| 120. | I/O                        | -    | -     | -     | 98    | 108   | 120   | V6    | 140   | 627                 |

| 121. | 1/O                        | -    | -     | -     | 99    | 109   | 121   | U6    | 141   | 630                 |

|      | GND                        | -    | -     | -     | 100   | 110   | 122   | T7    | 142   | -                   |

| 122. | I/O                        | -    | -     | -     | -     | 111   | 123   | U5    | 145   | 636                 |

| 123. | 1/O                        | -    | -     | -     | -     | 112   | 124   | T6    | 146   | 639                 |

| 124. | I/O (D1)                   | 69   | 73    | 70    | 101   | 113   | 125   | V3    | 147   | 642                 |

| 125. | I/O<br>(RCLK-BUSY/RD<br>Y) | 70   | 74    | 71    | 102   | 114   | 126   | V2    | 148   | 648                 |

| 126. | I/O                        | -    | -     | -     | 103   | 115   | 127   | U4    | 149   | 651                 |

| 127. | I/O                        | _    | -     | -     | 104   | 116   | 128   | T5    | 150   | 654                 |

| 128. | I/O (D0, DIN)              | 71   | 75    | 72    | 105   | 117   | 129   | U3    | 151   | 660                 |

| 129. | I/O (DOUT)                 | 72   | 76    | 73    | 106   | 118   | 130   | T4    | 152   | 663                 |

| Pin        | Description     | PC84 | TQ144   | PQ160    | TQ176    | PQ208    | PG223    | BG225    | PQ240 | Boundary Scan<br>Order |

|------------|-----------------|------|---------|----------|----------|----------|----------|----------|-------|------------------------|

| 7.         | I/O (A10)       | 5    | 133     | 147      | 162      | 190      | G1       | A6       | 220   | 135                    |

| 8.         | I/O (A11)       | 6    | 134     | 148      | 163      | 191      | G2       | B6       | 221   | 138                    |

|            | VCC             | -    | -       | -        | -        | -        | -        | VCC*     | 222   | -                      |

| 9.         | I/O             | -    | -       | -        | -        | -        | H4       | C6       | 223   | 141                    |

| 10.        | I/O             | -    | -       | -        | -        | -        | G4       | F7       | 224   | 150                    |

| 11.        | I/O             | -    | 135     | 149      | 164      | 192      | F1       | A5       | 225   | 153                    |

| 12.        | I/O             | -    | 136     | 150      | 165      | 193      | E1       | B5       | 226   | 162                    |

|            | GND             | -    | 137     | 151      | 166      | 194      | G3       | GND*     | 227   | -                      |

| 13.        | I/O             | -    | -       | -        | -        | 195      | F2       | D6       | 228   | 165                    |

| 14.        | I/O             | -    | -       | -        | 167      | 196      | D1       | C5       | 229   | 171                    |

| 15.        | I/O             | -    | -       | 152      | 168      | 197      | C1       | A4       | 230   | 174                    |

| 16.        | I/O             | -    | -       | 153      | 169      | 198      | E2       | E6       | 231   | 177                    |

| 17.        | I/O (A12)       | 7    | 138     | 154      | 170      | 199      | F3       | B4       | 232   | 183                    |

| 18.        | I/O (A13)       | 8    | 139     | 155      | 171      | 200      | D2       | D5       | 233   | 186                    |

| 19.        | I/O             | -    | -       | -        | -        | -        | F4       | A3       | 234   | 189                    |

| 20.        | I/O             | -    | -       | -        | -        | -        | E4       | C4       | 235   | 195                    |

| 21.        | I/O             | -    | 140     | 156      | 172      | 201      | B1       | B3       | 236   | 198                    |

| 22.        | 1/0             | -    | 141     | 157      | 173      | 202      | E3       | F6       | 237   | 201                    |

| 23.        | I/O (A14)       | 9    | 142     | 158      | 174      | 203      | C2       | A2       | 238   | 210                    |

| 24.        | I/O (A15)       | 10   | 143     | 159      | 175      | 204      | B2       | C3       | 239   | 213                    |

|            | VCC             | 11   | 144     | 160      | 176      | 205      | D3       | VCC*     | 240   | -                      |

|            | GND             | 12   | 1       | 1        | 1        | 2        | D4       | GND*     | 1     | -                      |

| 25.        | GCK1 (A16, I/O) | 13   | 2       | 2        | 2        | 4        | C3       | D4       | 2     | 222                    |

| 26.        | I/O (A17)       | 14   | 3       | 3        | 3        | 5        | C4       | B1       | 3     | 225                    |

| 27.        | I/O             | -    | 4       | 4        | 4        | 6        | B3       | C2       | 4     | 231                    |

| 28.        | 1/O             | -    | 5       | 5        | 5        | 7        | C5       | E5       | 5     | 234                    |

| 29.        | I/O (TDI)       | 15   | 6       | 6        | 6        | 8        | A2       | D3       | 6     | 237                    |

| 30.        | I/O (TCK)       | 16   | 7       | 7        | 7        | 9        | B4       | C1       | 7     | 243                    |

| 31.        | I/O             | -    | -       | 8        | 8        | 10       | C6       | D2       | 8     | 246                    |

| 32.        | I/O             | _    | -       | 9        | 9        | 10       | A3       | G6       | 9     | 249                    |

| 33.        | I/O             |      | _       | -        | -        | 12       | B5       | E4       | 10    | 243                    |

| 34.        | I/O             |      | _       | _        | _        | 12       | B6       | D1       | 10    | 258                    |

| 34.        | I/O             | -    |         | -        |          | -        | D5       | E3       | 11    | 238                    |

| 35.<br>36. | 1/O             | -    | -       | -        | -        | -        | D5<br>D6 | E3<br>E2 | 12    | 267                    |

| 30.        | GND             |      | - 8     | - 10     | - 10     | - 14     | C7       | GND*     | 13    | 207                    |

| 27         | I/O             | -    | 9       |          |          |          |          |          |       | 270                    |

| 37.        | 1/O             |      | 9<br>10 | 11<br>12 | 11<br>12 | 15       | A4       | F5<br>E1 | 15    | 270                    |

| 38.        | I/O (TMS)       | -    | 10      | 12       | 12       | 16<br>17 | A5<br>B7 | E1<br>F4 | 16    | 273                    |

| 39.        |                 | 17   |         |          |          |          |          |          | 17    |                        |

| 40.        | I/O             | 18   | 12      | 14       | 14       | 18       | A6       | F3       | 18    | 282                    |

| 44         | VCC             | -    | -       | -        | -        | -        | -        | VCC*     | 19    | -                      |

| 41.        | I/O             | -    | -       | -        | -        | -        | D7       | F2       | 20    | 285                    |

| 42.        | I/O             | -    | -       | -        | -        | -        | D8       | F1       | 21    | 291                    |

| 43.        | I/O             | -    | -       | -        | 15       | 19       | C8       | G4       | 23    | 294                    |

| 44.        | I/O             | -    | -       | -        | 16       | 20       | A7       | G3       | 24    | 297                    |

| 45.        | I/O             | -    | 13      | 15       | 17       | 21       | B8       | G2       | 25    | 306                    |

| 46.        | I/O             | -    | 14      | 16       | 18       | 22       | A8       | G1       | 26    | 309                    |

| 47.        | I/O             | 19   | 15      | 17       | 19       | 23       | B9       | G5       | 27    | 318                    |

| 48.        | I/O             | 20   | 16      | 18       | 20       | 24       | C9       | H3       | 28    | 321                    |

|            | GND             | 21   | 17      | 19       | 21       | 25       | D9       | GND*     | 29    | -                      |

|            | VCC             | 22   | 18      | 20       | 22       | 26       | D10      | VCC*     | 30    | -                      |

| 49.        | I/O             | 23   | 19      | 21       | 23       | 27       | C10      | H4       | 31    | 327                    |

| Pin        | Description | PC84 | TQ144    | PQ160    | TQ176    | PQ208    | PG223      | BG225    | PQ240    | Boundary Scan<br>Order |

|------------|-------------|------|----------|----------|----------|----------|------------|----------|----------|------------------------|

| 50.        | I/O         | 24   | 20       | 22       | 24       | 28       | B10        | H5       | 32       | 330                    |

| 51.        | I/O         | -    | 21       | 23       | 25       | 29       | A9         | J2       | 33       | 333                    |

| 52.        | I/O         | -    | 22       | 24       | 26       | 30       | A10        | J1       | 34       | 339                    |

| 53.        | I/O         | -    | -        | -        | 27       | 31       | A11        | J3       | 35       | 342                    |

| 54.        | I/O         | -    | -        | -        | 28       | 32       | C11        | J4       | 36       | 345                    |

| 55.        | I/O         | -    | -        | -        | -        | -        | D11        | J5       | 38       | 351                    |

| 56.        | I/O         | -    | -        | -        | -        | -        | D12        | K1       | 39       | 354                    |

|            | VCC         | -    | -        | -        | -        | -        | -          | VCC*     | 40       | -                      |

| 57.        | I/O         | 25   | 23       | 25       | 29       | 33       | B11        | K2       | 41       | 357                    |

| 58.        | I/O         | 26   | 24       | 26       | 30       | 34       | A12        | K3       | 42       | 363                    |

| 59.        | I/O         | -    | 25       | 27       | 31       | 35       | B12        | J6       | 43       | 366                    |

| 60.        | I/O         | -    | 26       | 28       | 32       | 36       | A13        | L1       | 44       | 369                    |

|            | GND         | -    | 27       | 29       | 33       | 37       | C12        | GND*     | 45       | -                      |

| 61.        | 1/0         | -    | -        | -        | -        | -        | D13        | L2       | 46       | 375                    |

| 62.        | 1/O         | -    | -        | -        | -        | -        | D13        | K4       | 47       | 378                    |

| 63.        | I/O         |      | -        | -        | -        | 38       | B13        | L3       | 47       | 381                    |

| 64.        | 1/O         |      | -        | -        | -        | 39       | A14        | M1       | 40       | 387                    |

| 65.        | 1/O         |      | -        | - 30     | - 34     | 40       | A14<br>A15 | K5       | 49<br>50 | 390                    |

| 65.<br>66. | 1/O         | -    |          | 30<br>31 | 34<br>35 | 40       | C13        | K5<br>M2 | 50<br>51 | 390                    |

|            |             | -    | -        |          |          |          |            |          |          |                        |

| 67.        | I/O         | 27   | 28       | 32       | 36       | 42       | B14        | L4       | 52       | 399                    |

| 68.        | I/O         | -    | 29       | 33       | 37       | 43       | A16        | N1       | 53       | 402                    |

| 69.        | I/O         | -    | 30       | 34       | 38       | 44       | B15        | M3       | 54       | 405                    |

| 70.        | I/O         | -    | 31       | 35       | 39       | 45       | C14        | N2       | 55       | 411                    |

| 71.        | I/O         | 28   | 32       | 36       | 40       | 46       | A17        | K6       | 56       | 414                    |

| 72.        | I/O         | 29   | 33       | 37       | 41       | 47       | B16        | P1       | 57       | 417                    |

| 73.        | M1 (I/O)    | 30   | 34       | 38       | 42       | 48       | C15        | N3       | 58       | 426                    |

|            | GND         | 31   | 35       | 39       | 43       | 49       | D15        | GND*     | 59       | -                      |

| 74.        | M0 (I/O)    | 32   | 36       | 40       | 44       | 50       | A18        | P2       | 60       | 429                    |

|            | VCC         | 33   | 37       | 41       | 45       | 55       | D16        | VCC*     | 61       | -                      |

| 75.        | M2 (I/O)    | 34   | 38       | 42       | 46       | 56       | C16        | M4       | 62       | 432                    |

| 76.        | GCK2 (I/O)  | 35   | 39       | 43       | 47       | 57       | B17        | R2       | 63       | 435                    |

| 77.        | I/O (HDC)   | 36   | 40       | 44       | 48       | 58       | E16        | P3       | 64       | 444                    |

| 78.        | I/O         | -    | 41       | 45       | 49       | 59       | C17        | L5       | 65       | 447                    |

| 79.        | I/O         | -    | 42       | 46       | 50       | 60       | D17        | N4       | 66       | 450                    |

| 80.        | I/O         | -    | 43       | 47       | 51       | 61       | B18        | R3       | 67       | 456                    |

| 81.        | I/O (LDC)   | 37   | 44       | 48       | 52       | 62       | E17        | P4       | 68       | 459                    |

| 82.        | I/O         | -    | -        | 49       | 53       | 63       | F16        | K7       | 69       | 462                    |

| 83.        | 1/0         | -    | -        | 50       | 54       | 64       | C18        | M5       | 70       | 468                    |

| 84.        | 1/O         | -    | -        | -        | -        | 65       | D18        | R4       | 71       | 471                    |

| 85.        | I/O         | _    | -        | -        | -        | 66       | F17        | N5       | 72       | 474                    |

| 86.        | I/O         | -    | -        | _        | -        | -        | E15        | P5       | 72       | 480                    |

| 87.        | 1/O         |      | -        | _        | -        | -        | F15        | L6       | 73       | 480                    |

| 07.        | GND         | -    | - 45     | - 51     | - 55     | 67       | G16        | GND*     | 74       | - 403                  |

| 00         | I/O         |      | 45<br>46 |          |          |          |            |          |          |                        |

| 88.        |             | -    |          | 52       | 56       | 68<br>60 | E18        | R5       | 76       | 486                    |

| 89.        | I/O         | -    | 47       | 53       | 57       | 69<br>70 | F18        | M6       | 77       | 492                    |

| 90.        | I/O         | 38   | 48       | 54       | 58       | 70       | G17        | N6       | 78       | 495                    |

| 91.        | I/O         | 39   | 49       | 55       | 59       | 71       | G18        | P6       | 79       | 504                    |

|            | VCC         | -    | -        | -        | -        | -        | -          | VCC*     | 80       | -                      |

| 92.        | I/O         | -    | -        | -        | 60       | 72       | H16        | R6       | 81       | 507                    |

| 93.        | I/O         | -    | -        | -        | 61       | 73       | H17        | M7       | 82       | 510                    |

| 94.        | I/O         | -    | -        | -        | -        | -        | G15        | N7       | 84       | 516                    |

#### **XC5200 Series Field Programmable Gate Arrays**

| Pin  | Description | PC84 | TQ144 | PQ160 | TQ176 | PQ208 | PG223 | BG225 | PQ240 | Boundary Scan<br>Order |

|------|-------------|------|-------|-------|-------|-------|-------|-------|-------|------------------------|

| 180. | I/O         | -    | -     | -     | -     | -     | N4    | D11   | 190   | 39                     |

| 181. | I/O         | -    | 117   | 129   | 141   | 167   | P2    | A12   | 191   | 42                     |

| 182. | I/O         | -    | -     | 130   | 142   | 168   | T1    | C11   | 192   | 45                     |

| 183. | I/O         | -    | -     | -     | -     | 169   | R1    | B11   | 193   | 51                     |

| 184. | I/O         | -    | -     | -     | -     | 170   | N2    | E10   | 194   | 54                     |

|      | -           | -    | -     | -     | -     | -     | -     | GND*  |       | -                      |

|      | GND         | -    | 118   | 131   | 143   | 171   | M3    | -     | 196   | -                      |

| 185. | I/O         | -    | 119   | 132   | 144   | 172   | P1    | A11   | 197   | 57                     |

| 186. | I/O         | -    | 120   | 133   | 145   | 173   | N1    | D10   | 198   | 66                     |

| 187. | I/O         | -    | -     | -     | -     | -     | M4    | C10   | 199   | 69                     |

| 188. | I/O         | -    | -     | -     | -     | -     | L4    | B10   | 200   | 75                     |

|      | VCC         | -    | -     | -     | -     | -     | -     | VCC*  | 201   | -                      |

| 189. | I/O (A4)    | 81   | 121   | 134   | 146   | 174   | M2    | A10   | 202   | 78                     |

| 190. | I/O (A5)    | 82   | 122   | 135   | 147   | 175   | M1    | D9    | 203   | 81                     |

| 191. | I/O         | -    | -     | -     | 148   | 176   | L3    | C9    | 205   | 87                     |

| 192. | I/O         | -    | -     | 136   | 149   | 177   | L2    | B9    | 206   | 90                     |

| 193. | I/O         | -    | 123   | 137   | 150   | 178   | L1    | A9    | 207   | 93                     |

| 194. | I/O         | -    | 124   | 138   | 151   | 179   | K1    | E9    | 208   | 99                     |

| 195. | I/O (A6)    | 83   | 125   | 139   | 152   | 180   | K2    | C8    | 209   | 102                    |

| 196. | I/O (A7)    | 84   | 126   | 140   | 153   | 181   | K3    | B8    | 210   | 105                    |

|      | GND         | 1    | 127   | 141   | 154   | 182   | K4    | GND*  | 211   | -                      |

#### Additional No Connect (N.C.) Connections for PQ208 and PQ240 Packages

|    |     | PQ208 |     | PQ240 |    |     |     |

|----|-----|-------|-----|-------|----|-----|-----|

| 1  | 53  | 105   | 157 | 208   | 22 | 143 | 219 |

| 3  | 54  | 107   | 158 |       | 37 | 158 |     |

| 51 | 102 | 155   | 206 |       | 83 | 195 |     |

| 52 | 104 | 156   | 207 |       | 98 | 204 |     |

**Notes:** \* Pins labeled VCC\* are internally bonded to a VCC plane within the BG225 package. The external pins are: B2, D8, H15, R8, B14, R1, H1, and R15.

Pins labeled GND\* are internally bonded to a ground plane within the BG225 package. The external pins are: A1, D12, G7, G9, H6, H8, H10, J8, K8, A8, F8, G8, H2, H7, H9, J7, J9, M8.

Boundary Scan Bit 0 = TDO.T Boundary Scan Bit 1 = TDO.O

Boundary Scan Bit 1056 = BSCAN.UPD

#### **Pin Locations for XC5215 Devices**

The following table may contain pinout information for unsupported device/package combinations. Please see the availability charts elsewhere in the XC5200 Series data sheet for availability information.

| Pin | Description | PQ160 | HQ208 | HQ240 | PG299 | BG225 | BG352 | Boundary Scan Order |

|-----|-------------|-------|-------|-------|-------|-------|-------|---------------------|

|     | VCC         | 142   | 183   | 212   | K1    | VCC*  | VCC*  | -                   |

| 1.  | I/O (A8)    | 143   | 184   | 213   | K2    | E8    | D14   | 138                 |

| 2.  | I/O (A9)    | 144   | 185   | 214   | K3    | B7    | C14   | 141                 |