#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SCI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 31                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | ·                                                                            |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-LQFP                                                                      |

| Supplier Device Package    | 64-LFQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36094gfzv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| Secti | on 1   | Overview                                       | 1    |

|-------|--------|------------------------------------------------|------|

| 1.1   | Featu  | res                                            | 1    |

| 1.2   | Intern | al Block Diagram                               | 3    |

| 1.3   | Pin A  | ssignments                                     | 4    |

| 1.4   | Pin F  | unctions                                       | 6    |

| Secti | on 2   | CPU                                            | 9    |

| 2.1   | Addre  | ess Space and Memory Map                       | . 10 |

| 2.2   | Regis  | ter Configuration                              | .11  |

|       | 2.2.1  | General Registers                              | . 12 |

|       | 2.2.2  | Program Counter (PC)                           | . 13 |

|       | 2.2.3  | Condition-Code Register (CCR)                  | . 13 |

| 2.3   | Data 1 | Formats                                        | . 15 |

|       | 2.3.1  | General Register Data Formats                  | . 15 |

|       | 2.3.2  | Memory Data Formats                            | .17  |

| 2.4   | Instru | ction Set                                      | . 18 |

|       | 2.4.1  | Table of Instructions Classified by Function   | .18  |

|       | 2.4.2  | Basic Instruction Formats                      | . 27 |

| 2.5   | Addre  | essing Modes and Effective Address Calculation | . 28 |

|       | 2.5.1  | Addressing Modes                               | . 28 |

|       | 2.5.2  | Effective Address Calculation                  | . 32 |

| 2.6   | Basic  | Bus Cycle                                      | . 34 |

|       | 2.6.1  | Access to On-Chip Memory (RAM, ROM)            | . 34 |

|       | 2.6.2  | On-Chip Peripheral Modules                     | . 35 |

| 2.7   | CPU    | States                                         | . 36 |

| 2.8   | Usage  | e Notes                                        | . 37 |

|       | 2.8.1  | Notes on Data Access to Empty Areas            | . 37 |

|       | 2.8.2  | EEPMOV Instruction                             | . 37 |

|       | 2.8.3  | Bit Manipulation Instruction                   | . 37 |

| Secti | on 3   | Exception Handling                             | .43  |

| 3.1   |        | ption Sources and Vector Address               |      |

| 3.2   | -      | ter Descriptions                               |      |

|       | 3.2.1  | Interrupt Edge Select Register 1 (IEGR1)       |      |

|       | 3.2.2  | Interrupt Edge Select Register 2 (IEGR2)       |      |

|       | 3.2.3  | Interrupt Enable Register 1 (IENR1)            |      |

# RENESAS

- General I/O ports

- I/O pins: 31 I/O pins, including 8 large current ports ( $I_{oL} = 20 \text{ mA}, @V_{oL} = 1.5 \text{ V}$ )

- Input-only pins: 8 input pins (also used for analog input)

- Frequency accuracy:

| $20~\text{MHz} \pm 1.5\%$ | $V_{cc} = 4.0$ to 5.0 V, $T_a = 25^{\circ}C$ |

|---------------------------|----------------------------------------------|

| $16~\text{MHz} \pm 1.5\%$ | $V_{cc} = 4.0$ to 5.0 V, $T_a = 25^{\circ}C$ |

| $20 \text{ MHz} \pm 3\%$  | $V_{cc} = 4.0$ to 5.5 V, $T_a = -20$ to 75°C |

| $16 \text{ MHz} \pm 3\%$  | $V_{cc} = 4.0$ to 5.5 V, $T_a = -20$ to 75°C |

| $20 \text{ MHz} \pm 4\%$  | $V_{cc} = 3.0$ to 5.5 V, $T_a = -20$ to 75°C |

| $16 \text{ MHz} \pm 4\%$  | $V_{cc} = 3.0$ to 5.5 V, $T_a = -20$ to 75°C |

• Supports various power-down modes

Note: F-ZTAT<sup>™</sup> is a trademark of Renesas Technology Corp.

• Compact package

| Package | Code   | Body Size           | Pin Pitch |

|---------|--------|---------------------|-----------|

| LQFP-64 | FP-64K | 10.0 	imes 10.0  mm | 0.5 mm    |

| QFP-64  | FP-64A | 14.0 × 14.0 mm      | 0.8 mm    |

| LQFP-48 | FP-48F | 10.0 × 10.0 mm      | 0.65 mm   |

| LQFP-48 | FP-48B | 7.0 	imes 7.0  mm   | 0.5 mm    |

| QFN-48  | TNP-48 | 7.0 	imes 7.0  mm   | 0.5 mm    |

3. Finally, the CPU writes H'41 to PDR5, completing execution of BSET instruction. As a result of the BSET instruction, bit 0 in PDR5 becomes 1, and P50 outputs a high-level signal. However, bits 7 and 6 of PDR5 end up with different values. To prevent this problem, store a copy of the PDR5 data in a work area in memory. Perform the bit manipulation on the data in the work area, then write this data to PDR5.

#### • Prior to executing BSET instruction

| MOV.B | #80, | ROL   |

|-------|------|-------|

| MOV.B | ROL, | @RAM0 |

| MOV.B | ROL, | @PDR5 |

The PDR5 value (H'80) is written to a work area in memory (RAM0) as well as to PDR5.

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50          |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output       |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1            |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0            |

| RAM0         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0            |

• BSET instruction executed

BSET #0, @RAMO

The BSET instruction is executed designating the PDR5 work area (RAM0).

### • After executing BSET instruction

| MOV.B | @RAM0, | ROL   |

|-------|--------|-------|

| MOV.B | ROL,   | @PDR5 |

The work area (RAM0) value is written to PDR5.

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50           |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output        |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | High<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1             |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 1             |

| RAM0         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 1             |

### 3.2.3 Interrupt Enable Register 1 (IENR1)

IENR1 enables direct transition interrupts, timer A overflow interrupts, and external pin interrupts.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                               |

|-----|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IENDT    | 0                | R/W | Direct Transfer Interrupt Enable                                                                                                                          |

|     |          |                  |     | When this bit is set to 1, direct transition interrupt requests are enabled.                                                                              |

| 6   | IENTA    | 0                | R/W | Timer A Interrupt Enable                                                                                                                                  |

|     |          |                  |     | When this bit is set to 1, timer A overflow interrupt requests are enabled.                                                                               |

| 5   | IENWP    | 0                | R/W | Wakeup Interrupt Enable                                                                                                                                   |

|     |          |                  |     | This bit is an enable bit, which is common to the pins $\overline{WKP5}$ to $\overline{WKP0}$ . When the bit is set to 1, interrupt requests are enabled. |

| 4   | _        | 1                |     | Reserved                                                                                                                                                  |

|     |          |                  |     | This bit is always read as 1.                                                                                                                             |

| 3   | IEN3     | 0                | R/W | IRQ3 Interrupt Enable                                                                                                                                     |

|     |          |                  |     | When this bit is set to 1, interrupt requests of the $\overline{IRQ3}$ pin are enabled.                                                                   |

| 2   | IEN2     | 0                | R/W | IRQ2 Interrupt Enable                                                                                                                                     |

|     |          |                  |     | When this bit is set to 1, interrupt requests of the $\overline{IRQ2}$ pin are enabled.                                                                   |

| 1   | IEN1     | 0                | R/W | IRQ1 Interrupt Enable                                                                                                                                     |

|     |          |                  |     | When this bit is set to 1, interrupt requests of the $\overline{IRQ1}$ pin are enabled.                                                                   |

| 0   | IEN0     | 0                | R/W | IRQ0 Interrupt Enable                                                                                                                                     |

|     |          |                  |     | When this bit is set to 1, interrupt requests of the $\overline{IRQ0}$ pin are enabled.                                                                   |

When disabling interrupts by clearing bits in an interrupt enable register, or when clearing bits in an interrupt flag register, always do so while interrupts are masked (I = 1). If the above clear operations are performed while I = 0, and as a result a conflict arises between the clear instruction and an interrupt request, exception handling for the interrupt will be executed after the clear instruction has been executed.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                     |  |

|-----|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------|--|

| 3   | IWPF3    | 0                | R/W | WKP3 Interrupt Request Flag                                                                                     |  |

|     |          |                  |     | [Setting condition]                                                                                             |  |

|     |          |                  |     | When $\overline{WKP3}$ pin is designated for interrupt input and the designated signal edge is detected.        |  |

|     |          |                  |     | [Clearing condition]                                                                                            |  |

|     |          |                  |     | When IWPF3 is cleared by writing 0.                                                                             |  |

| 2   | IWPF2    | 0                | R/W | WKP2 Interrupt Request Flag                                                                                     |  |

|     |          |                  |     | [Setting condition]                                                                                             |  |

|     |          |                  |     | When $\overline{\text{WKP2}}$ pin is designated for interrupt input and the designated signal edge is detected. |  |

|     |          |                  |     | [Clearing condition]                                                                                            |  |

|     |          |                  |     | When IWPF2 is cleared by writing 0.                                                                             |  |

| 1   | IWPF1    | 0                | R/W | WKP1 Interrupt Request Flag                                                                                     |  |

|     |          |                  |     | [Setting condition]                                                                                             |  |

|     |          |                  |     | When $\overline{WKP1}$ pin is designated for interrupt input and the designated signal edge is detected.        |  |

|     |          |                  |     | [Clearing condition]                                                                                            |  |

|     |          |                  |     | When IWPF1 is cleared by writing 0.                                                                             |  |

| 0   | IWPF0    | 0                | R/W | WKP0 Interrupt Request Flag                                                                                     |  |

|     |          |                  |     | [Setting condition]                                                                                             |  |

|     |          |                  |     | When $\overline{WKP0}$ pin is designated for interrupt input and the designated signal edge is detected.        |  |

|     |          |                  |     | [Clearing condition]                                                                                            |  |

|     |          |                  |     | When IWPF0 is cleared by writing 0.                                                                             |  |

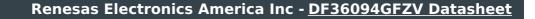

# Section 5 Clock Pulse Generators

The clock pulse generator (CPG) consists of a system clock generating circuitry, a subclock generating circuitry, and two prescalers. The system clock generating circuitry includes an external clock oscillator, a duty correction circuit, an on-chip oscillator, an RC clock divider, a clock select circuit, and a system clock divider. The subclock generating circuitry includes a subclock oscillator, and a subclock divider. The CPG can function as a clock generating circuitry itself or in combination with an external oscillator. Figure 5.1 shows a block diagram of the clock pulse generator.

Figure 5.1 Block Diagram of Clock Pulse Generators

The system clock ( $\phi$ ) and subclock ( $\phi_{sub}$ ) are basic clocks on which the CPU and on-chip peripheral modules operate. The system clock is divided into from  $\phi/2$  to  $\phi/8192$  by prescaler S. The subclock is divided into from  $\phi_w/8$  to  $\phi_w/128$  by prescaler W. These divided clocks are supplied to respective peripheral modules.

| Possible      |                                     |

|---------------|-------------------------------------|

| Host Bit Rate | System Clock Frequency Range of LSI |

| 9,600 bps     | 10 MHz                              |

| 4,800 bps     |                                     |

# Table 7.3 System Clock Frequencies for which Automatic Adjustment of LSI Bit Rate is Possible

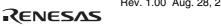

### 7.3.2 Programming/Erasing in User Program Mode

On-board programming/erasing of an individual flash memory block can also be performed in user program mode by branching to a user program/erase control program. The user must set branching conditions and provide on-board means of supplying programming data. The flash memory must contain the user program/erase control program or a program that provides the user program/erase control program from external memory. As the flash memory itself cannot be read during programming/erasing, transfer the user program/erase control program to on-chip RAM, as in boot mode. Figure 7.2 shows a sample procedure for programming/erasing in user program mode. Prepare a user program/erase control program in accordance with the description in section 7.4, Flash Memory Programming/Erasing.

Figure 7.2 Programming/Erasing Flowchart Example in User Program Mode

- 5. For a dummy write to a verify address, write 1-byte data H'FF to an address whose lower two bits are B'00. Verify data can be read in longwords from the address to which a dummy write was performed.

- 6. If the read data is not erased successfully, set erase mode again, and repeat the erase/erase-verify sequence as before. The maximum number of repetitions of the erase/erase-verify sequence is 100.

### 7.4.3 Interrupt Handling when Programming/Erasing Flash Memory

All interrupts, including the NMI interrupt, are disabled while flash memory is being programmed or erased, or while the boot program is executing, for the following three reasons:

- 1. Interrupt during programming/erasing may cause a violation of the programming or erasing algorithm, with the result that normal operation cannot be assured.

- 2. If interrupt exception handling starts before the vector address is written or during programming/erasing, a correct vector cannot be fetched and the CPU malfunctions.

- 3. If an interrupt occurs during boot program execution, normal boot mode sequence cannot be carried out.

#### P20/SCK3 pin

| Register      |      | SCR3 | SMR | PCR2  |                 |

|---------------|------|------|-----|-------|-----------------|

| Bit Name      | CKE1 | CKE0 | COM | PCR20 | Pin Function    |

| Setting Value | 0    | 0    | 0   | 0     | P20 input pin   |

|               |      |      |     | 1     | P20 output pin  |

|               | 0    | 0    | 1   | Х     | SCK3 output pin |

|               | 0    | 1    | Х   | Х     | SCK3 output pin |

|               | 1    | Х    | Х   | Х     | SCK3 input pin  |

Legend X: Don't care.

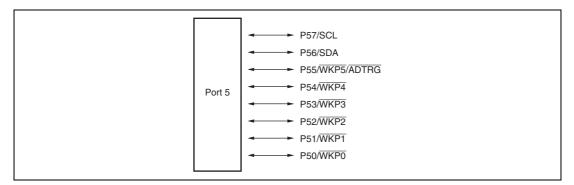

### 9.3 Port 5

Port 5 is a general I/O port also functioning as an I<sup>2</sup>C bus interface I/O pin, an A/D trigger input pin, wakeup interrupt input pin. Each pin of the port 5 is shown in figure 9.3. The register setting of the I<sup>2</sup>C bus interface register has priority for functions of the pins P57/SCL and P56/SDA. Since the output buffer for pins P56 and P57 has the NMOS push-pull structure, it differs from an output buffer with the CMOS structure in the high-level output characteristics (see section 20, Electrical Characteristics).

Figure 9.3 Port 5 Pin Configuration

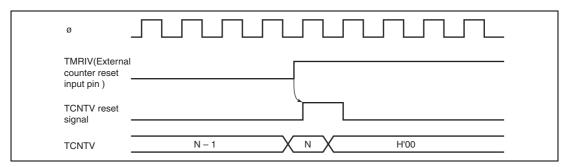

Figure 11.8 Clear Timing by TMRIV Input

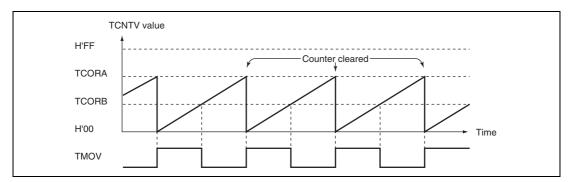

## **11.5** Timer V Application Examples

### 11.5.1 Pulse Output with Arbitrary Duty Cycle

Figure 11.9 shows an example of output of pulses with an arbitrary duty cycle.

- 1. Set bits CCLR1 and CCLR0 in TCRV0 so that TCNTV will be cleared by compare match with TCORA.

- 2. Set bits OS3 to OS0 in TCSRV so that the output will go to 1 at compare match with TCORA and to 0 at compare match with TCORB.

- 3. Set bits CKS2 to CKS0 in TCRV0 and bit ICKS0 in TCRV1 to select the desired clock source.

- 4. With these settings, a waveform is output without further software intervention, with a period determined by TCORA and a pulse width determined by TCORB.

Figure 11.9 Pulse Output Example

RENESAS

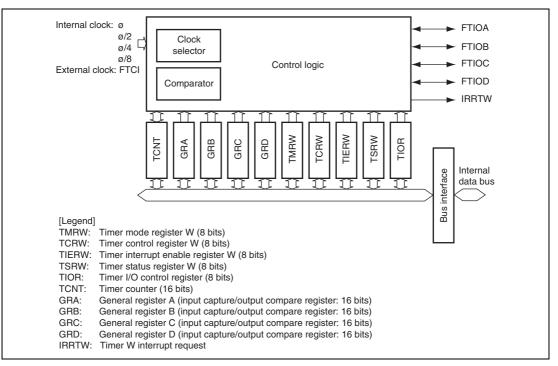

Figure 12.1 Timer W Block Diagram

# 12.4 Operation

The timer W has the following operating modes.

- Normal Operation

- PWM Operation

### 12.4.1 Normal Operation

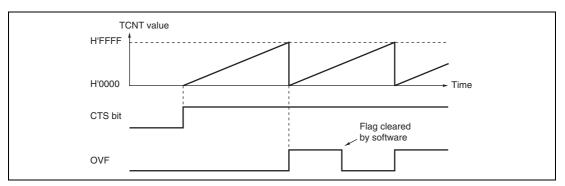

TCNT performs free-running or periodic counting operations. After a reset, TCNT is set as a freerunning counter. When the CTS bit in TMRW is set to 1, TCNT starts incrementing the count. When the count overflows from H'FFFF to H'0000, the OVF flag in TSRW is set to 1. If the OVIE in TIERW is set to 1, an interrupt request is generated. Figure 12.2 shows free-running counting.

Figure 12.2 Free-Running Counter Operation

# 12.6 Usage Notes

The following types of contention or operation can occur in timer W operation.

- 1. The pulse width of the input clock signal and the input capture signal must be at least two system clock ( $\phi$ ) cycles; shorter pulses will not be detected correctly.

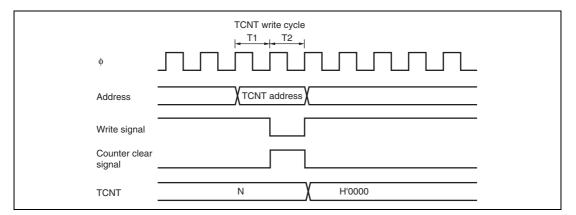

- 2. Writing to registers is performed in the T2 state of a TCNT write cycle. If counter clear signal occurs in the T2 state of a TCNT write cycle, clearing of the counter takes priority and the write is not performed, as shown in figure 12.24. If counting-up is generated in the TCNT write cycle to contend with the TCNT counting-up, writing takes precedence.

- 3. Depending on the timing, TCNT may be incremented by a switch between different internal clock sources. When TCNT is internally clocked, an increment pulse is generated from the rising edge of an internal clock signal, that is divided system clock (φ). Therefore, as shown in figure 12.25 the switch is from a low clock signal to a high clock signal, the switchover is seen as a rising edge, causing TCNT to increment.

- 4. If timer W enters module standby mode while an interrupt request is generated, the interrupt request cannot be cleared. Before entering module standby mode, disable interrupt requests.

Figure 12.24 Contention between TCNT Write and Clear

# 15.4 Operation

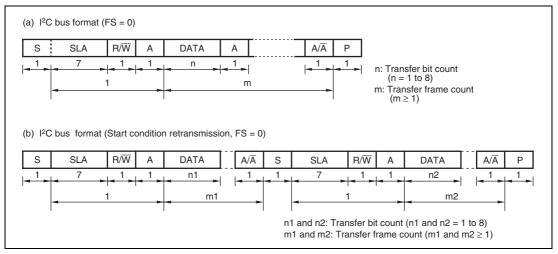

The  $I^2C$  bus interface can communicate either in  $I^2C$  bus mode or clocked synchronous serial mode by setting FS in SAR.

### 15.4.1 I<sup>2</sup>C Bus Format

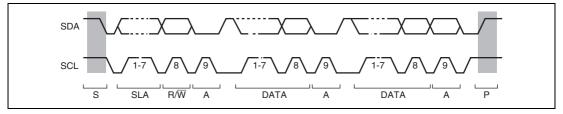

Figure 15.3 shows the  $I^2C$  bus formats. Figure 15.4 shows the  $I^2C$  bus timing. The first frame following a start condition always consists of 8 bits.

Figure 15.3 I<sup>2</sup>C Bus Formats

Figure 15.4 I<sup>2</sup>C Bus Timing

RENESAS

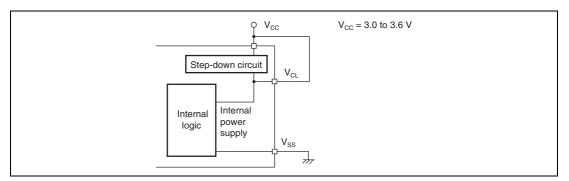

# 18.2 When Not Using Internal Power Supply Step-Down Circuit

When the internal power supply step-down circuit is not used, connect the external power supply to the  $V_{cL}$  pin and  $V_{cc}$  pin, as shown in figure 18.2. The external power supply is then input directly to the internal power supply. The permissible range for the power supply voltage is 3.0 V to 3.6 V. Operation cannot be guaranteed if a voltage outside this range (less than 3.0 V or more than 3.6 V) is input.

Figure 18.2 Power Supply Connection when Internal Step-Down Circuit is Not Used

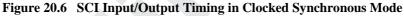

# 20.4 Output Load Condition

Figure 20.7 Output Load Circuit

| Table A.3 | Number of Cycles in Each Instruction |

|-----------|--------------------------------------|

|-----------|--------------------------------------|

|                | Access Location                                             |                                                                                                                                                       |  |

|----------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                | On-Chip Memory                                              | On-Chip Peripheral Module                                                                                                                             |  |

| S,             | 2                                                           | _                                                                                                                                                     |  |

| SJ             | _                                                           |                                                                                                                                                       |  |

| Sκ             | _                                                           |                                                                                                                                                       |  |

| S              | _                                                           | 2 or 3*                                                                                                                                               |  |

| S <sub>м</sub> | _                                                           | 2 or 3*                                                                                                                                               |  |

| S <sub>N</sub> |                                                             | 1                                                                                                                                                     |  |

|                | S <sub>J</sub> S <sub>κ</sub> S <sub>L</sub> S <sub>M</sub> | On-Chip Memory           S <sub>1</sub> 2           S <sub>3</sub> 2           S <sub>k</sub> 2           S <sub>L</sub> 5           S <sub>M</sub> 2 |  |

Note: \* Depends on which on-chip peripheral module is accessed. See section 19.1, Register Addresses (Address Order).

#### RenesasTechnologyCorp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

#### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852- 2265-6688, Fax: <852- 2730-6071

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65- 6213-0200, Fax: <65- 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603- 7955-9309, Fax: <603- 7955-9310

http://www.renesas.com