# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                               |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 64                                                                |

| Program Memory Size        | 64KB (64K × 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                |                                                                   |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 8x8b, 13x12b; D/A 2x10b, 2x12b                                |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 100-TQFP                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f040-gqr   |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Registers

| SFR | Definition 5 | 5.1. AMX0CF: AMUX0 Configuration                       | 19 |

|-----|--------------|--------------------------------------------------------|----|

|     |              | 5.2. AMX0SL: AMUX0 Channel Select                      |    |

| SFR | Definition 5 | 5.3. AMX0PRT: Port 3 Pin Selection                     | 51 |

| SFR | Definition 5 | 5.4. HVA0CN: High Voltage Difference Amplifier Control | 53 |

|     |              | 5.5. ADC0CF: ADC0 Configuration Register               |    |

|     |              | 5.6. ADC0CN: ADC0 Control                              |    |

| SFR | Definition 5 | 5.7. ADC0H: ADC0 Data Word MSB                         | 60 |

| SFR | Definition 5 | 5.8. ADC0L: ADC0 Data Word LSB                         | 60 |

| SFR | Definition 5 | 5.9. ADC0GTH: ADC0 Greater-Than Data High Byte         | 62 |

| SFR | Definition 5 | 5.10. ADC0GTL: ADC0 Greater-Than Data Low Byte         | 62 |

| SFR | Definition 5 | 5.11. ADC0LTH: ADC0 Less-Than Data High Byte           | 62 |

|     |              | 5.12. ADC0LTL: ADC0 Less-Than Data Low Byte            |    |

|     |              | 6.1. AMX0CF: AMUX0 Configuration                       |    |

| SFR | Definition 6 | 6.2. AMX0SL: AMUX0 Channel Select                      | 71 |

|     |              | 6.3. AMX0PRT: Port 3 Pin Selection                     |    |

| SFR | Definition 6 | 6.4. HVA0CN: High Voltage Difference Amplifier Control | 75 |

| SFR | Definition 6 | S.5. ADC0CF: ADC0 Configuration       8                | 30 |

|     |              | δ.6. ADC0CN: ADC0 Control 8                            |    |

|     |              | 6.7. ADC0H: ADC0 Data Word MSB                         |    |

|     |              | S.8. ADC0L: ADC0 Data Word LSB       8                 |    |

|     |              | S.9. ADC0GTH: ADC0 Greater-Than Data High Byte       6 |    |

|     |              | 6.10. ADC0GTL: ADC0 Greater-Than Data Low Byte         |    |

|     |              | 6.11. ADC0LTH: ADC0 Less-Than Data High Byte           |    |

|     |              | 6.12. ADC0LTL: ADC0 Less-Than Data Low Byte 8          |    |

|     |              | 7.1. AMX2CF: AMUX2 Configuration                       |    |

|     |              | 7.2. AMX2SL: AMUX2 Channel Select                      |    |

|     |              | 7.3. ADC2CF: ADC2 Configuration                        |    |

|     |              | 7.4. ADC2CN: ADC2 Control                              |    |

|     |              | 7.5. ADC2: ADC2 Data Word                              |    |

|     |              | 7.6. ADC2GT: ADC2 Greater-Than Data                    |    |

|     |              | 7.7. ADC2LT: ADC2 Less-Than Data                       |    |

|     |              | 3.1. DAC0H: DAC0 High Byte                             |    |

|     |              | 3.2. DAC0L: DAC0 Low Byte                              |    |

|     |              | 3.3. DAC0CN: DAC0 Control                              |    |

|     |              | 3.4. DAC1H: DAC1 High Byte                             |    |

|     |              | 3.5. DAC1L: DAC1 Low Byte                              |    |

|     |              | 3.6. DAC1CN: DAC1 Control1                             |    |

|     |              | 0.1. REF0CN: Reference Control1                        |    |

|     |              | 10.1. REF0CN: Reference Control1                       |    |

| SFR | Definition 1 | 11.1. CPTnCN: Comparator 0, 1, and 2 Control           | 24 |

|     |              | 11.2. CPTnMD: Comparator Mode Selection                |    |

|     |              | 12.1. SFR Page Control Register: SFRPGCN               |    |

| SFR | Definition 1 | 12.2. SFR Page Register: SFRPAGE                       | 12 |

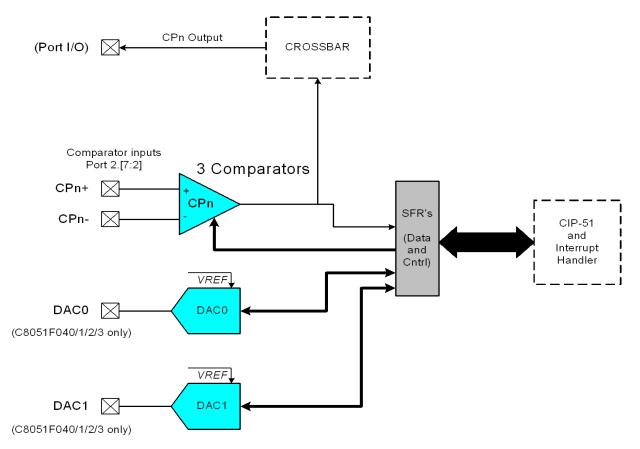

#### 1.10. Comparators and DACs

Each C8051F040/1/2/3 MCU has two 12-bit DACs, and all C8051F04x devices have three comparators on chip. The MCU data and control interface to each comparator and DAC is via the Special Function Registers. The MCU can place any DAC or comparator in low power shutdown mode.

The comparators have software programmable hysteresis and response time. Each comparator can generate an interrupt on its rising edge, falling edge, or both; these interrupts are capable of waking up the MCU from sleep mode. The comparators' output state can also be polled in software. The comparator outputs can be programmed to appear on the Port I/O pins via the Crossbar.

The DACs are voltage output mode and include a flexible output scheduling mechanism. This scheduling mechanism allows DAC output updates to be forced by a software write or a Timer 2, 3, or 4 overflow. The DAC voltage reference is supplied via the dedicated VREFD input pin on C8051F040/2 devices or via the internal voltage reference on C8051F041/3 devices. The DACs are especially useful as references for the comparators or offsets for the differential inputs of the ADC.

Figure 1.14. Comparator and DAC Diagram

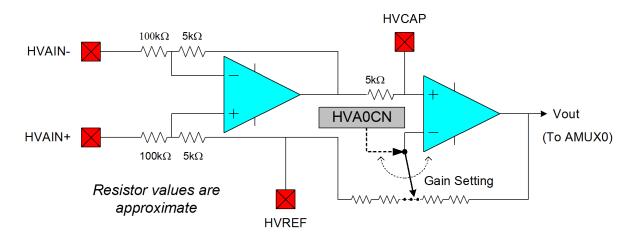

### 5.2. High-Voltage Difference Amplifier

The High Voltage Difference Amplifier (HVDA) can be used to measure high differential voltages up to 60 V peak-to-peak, reject high common-mode voltages up to ±60 V, and condition the signal voltage range to be suitable for input to ADC0. The input signal to the HVDA may be below AGND to –60 volts, and as high as +60 volts, making the device suitable for both single and dual supply applications. The HVDA provides a common-mode signal for the ADC via the High Voltage Reference Input (HVREF), allowing measurement of signals outside the specified ADC input range using on-chip circuitry. The HVDA has a gain of 0.05 V/V to 14 V/V. The first stage 20:1 difference amplifier has a gain of 0.05 V/V when the output amplifier is used as a unity gain buffer. When the output amplifier is set to a gain of 280 (selected using the HVGAIN bits in the High Voltage Control Register), an overall gain of 14 can be attained.

The HVDA uses four available external pins: +HVAIN, –HVAIN, HVCAP, and HVREF. HVAIN+ and HVAINserve as the differential inputs to the HVDA. HVREF should be used to provide a common mode reference for input to ADC0, and to prevent the output of the HVDA circuit from saturating. The output from the HVDA circuit as calculated by Equation 5.1 must remain within the "Output Voltage Range" specification listed in Table 5.3. The ideal value for HVREF in most applications is equal to 1/2 the supply voltage for the device. When the ADC is configured for differential measurement, the HVREF signal is applied to the AINinput of the ADC, thereby removing HVREF from the measurement. HVCAP facilitates the use of a capacitor for noise filtering in conjunction with R7 (see Figure 5.3 for R7 and other approximate resistor values). Alternatively, the HVCAP could also be used to access amplification of the first stage of the HVDA at an external pin. (See Table 5.3 on page 68 for electrical specifications of the HVDA.)

$$V_{OUT} = [(HVAIN+) - (HVAIN-)] \cdot Gain + HVREF$$

**Note:** The output voltage of the HVDA is selected as an input to the AIN+ input of ADC0 via its analog multiplexer (AMUX0). HVDA output voltages outside the ADC's input range will result in saturation of the ADC input. Allow for adequate settle/tracking time for proper voltage measurements.

Equation 5.1. Calculating HVDA Output Voltage to AIN+

### Figure 5.3. High Voltage Difference Amplifier Functional Diagram

## C8051F040/1/2/3/4/5/6/7

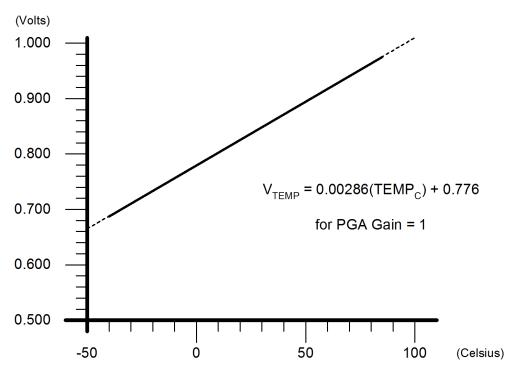

Figure 5.6. Temperature Sensor Transfer Function

#### SFR Definition 5.6. ADC0CN: ADC0 Control

| R/W     | R/W           | R/W         | R/W            | R/W          | R/W           | R/W            | R/W           | Reset Valu       |

|---------|---------------|-------------|----------------|--------------|---------------|----------------|---------------|------------------|

| AD0EN   | AD0TM         | AD0INT      | AD0BUSY        | AD0CM1       | AD0CM0        | AD0WINT        | AD0LJST       |                  |

| Bit7    | Bit6          | Bit5        | Bit4           | Bit3         | Bit2          | Bit1           | Bit0          | Bit<br>Addressab |

|         |               |             |                |              |               |                | SFR Address   |                  |

|         |               |             |                |              |               |                | SFR Page      | e: 0             |

| Bit7:   | AD0EN: AD     | DC0 Enable  | e Bit.         |              |               |                |               |                  |

|         | 0: ADC0 D     | isabled. AD | C0 is in low   | -power shu   | tdown.        |                |               |                  |

|         |               |             | C0 is active   | and ready    | for data con  | versions.      |               |                  |

| Bit6:   | ADOTM: AD     |             |                | kina in nant |               |                | ion io in nu  |                  |

|         |               |             | y AD0CM1-0     | -            | inuous unie:  | ss a convers   | ion is in pro | ocess            |

| Bit5:   |               |             | rsion Comp     |              | ot Flag.      |                |               |                  |

|         |               |             | red by softw   |              | it ingi       |                |               |                  |

|         | 0: ADCO ha    | as not com  | oleted a data  | a conversio  | n since the   | last time this | flag was cl   | eared.           |

|         |               | •           | ed a data co   | nversion.    |               |                |               |                  |

| Bit4:   | AD0BUSY:      | ADC0 Bus    | sy Bit.        |              |               |                |               |                  |

|         | Read:         | onversion i | s complete (   | or a conver  | sion is not c | urrently in pr | oares AD      |                  |

|         |               |             | g edge of AE   |              |               |                | Ugress. AD    | 01111 15 50      |

|         |               |             | s in progres   |              |               |                |               |                  |

|         | Write:        |             |                |              |               |                |               |                  |

|         | 0: No Effect  |             |                |              |               |                |               |                  |

|         |               |             | version if AD  |              |               |                |               |                  |

| Bit3-2: | If AD0CM1-0   |             | art of Convei  | rsion iviode | Select.       |                |               |                  |

|         |               |             | initiated on   | everv write  | of '1' to AD( | BUSY.          |               |                  |

|         |               |             | initiated on   |              |               |                |               |                  |

|         |               |             | initiated on   |              |               | CNVSTR0.       |               |                  |

|         |               |             | initiated on o | overflow of  | Timer 2.      |                |               |                  |

|         | If ADOTM =    |             | h tha write a  |              |               | lasta far 2 C  | ND alaaka f   |                  |

|         | conversion    |             | in the write c |              | BUSY and      | lasts for 3 SA | AR CIOCKS, I  |                  |

|         |               |             | v the overflo  | w of Timer   | 3 and last fo | or 3 SAR clo   | cks. followe  | ed by con-       |

|         | version.      | 5           | ,              |              |               |                |               | <b>,</b>         |

|         | 10: ADC0 t    | racks only  | when CNVS      | TR0 input    | s logic low;  | conversion s   | starts on ris | ing              |

|         | CNVSTR0       |             |                | <i>.</i> –   |               |                |               |                  |

|         |               | g started b | y the overflo  | w of Timer   | 2 and last fo | or 3 SAR clo   | cks, followe  | ed by con-       |

| Bit1:   |               |             | dow Compa      | re Interrunt | Flag          |                |               |                  |

| 51(1.   |               |             | ed by softwa   |              | r lag.        |                |               |                  |

|         |               |             |                |              | is not occur  | red since this | s flag was la | ast cleared      |

|         | 1: ADC0 W     | /indow Con  | nparison Dat   | ta match ha  |               |                | -             |                  |

| Bit0:   |               |             | Justify Selec  |              |               |                |               |                  |

|         | (). Data in / |             | COL register   | o oro right  |               |                |               |                  |

|         |               |             | COL register   | s are right- |               |                |               |                  |

#### Table 5.2. 12-Bit ADC0 Electrical Characteristics

$V_{DD}$  = 3.0 V, AV+ = 3.0 V, VREF = 2.40 V (REFBE = 0), PGA Gain = 1, -40 to +85 °C unless otherwise specified.

| Parameter                                                                      | Conditions                         | Min      | Тур             | Мах     | Units  |

|--------------------------------------------------------------------------------|------------------------------------|----------|-----------------|---------|--------|

| DC Accuracy                                                                    | 1                                  | 1        | 1               |         |        |

| Resolution                                                                     |                                    |          | 12              |         | bits   |

| Integral Nonlinearity                                                          |                                    |          | _               | ±1      | LSB    |

| Differential Nonlinearity                                                      | Guaranteed Monotonic               | —        |                 | ±1      | LSB    |

| Offset Error                                                                   | Note 1                             |          | 0.5±3           | _       | LSB    |

| Full Scale Error                                                               | Differential mode; See Note 1      |          | 0.4±3           | _       | LSB    |

| Offset Temperature Coefficient                                                 |                                    |          | ±0.25           | _       | ppm/°C |

| Dynamic Performance (10 kHz s                                                  | sine-wave input, 0 to 1 dB belo    | w Full S | cale, 10        | 0 ksps) |        |

| Signal-to-Noise Plus Distortion                                                |                                    | 66       | _               | —       | dB     |

| Total Harmonic Distortion                                                      | Up to the 5 <sup>th</sup> harmonic | _        | -75             | _       | dB     |

| Spurious-Free Dynamic Range                                                    |                                    | - 1      | 80              | _       | dB     |

| Conversion Rate                                                                |                                    |          |                 |         |        |

| Maximum SAR Clock Frequency                                                    |                                    | —        |                 | 2.5     | MHz    |

| Conversion Time in SAR Clocks                                                  |                                    | 16       |                 | _       | clocks |

| Track/Hold Acquisition Time                                                    |                                    | 1.5      |                 | —       | μs     |

| Throughput Rate                                                                |                                    | -        |                 | 100     | ksps   |

| Analog Inputs                                                                  |                                    |          |                 |         |        |

| Input Voltage Range                                                            | Single-ended operation             | 0        | —               | VREF    | V      |

| Common-mode Voltage Range                                                      | Differential operation             | AGND     | —               | AV+     | V      |

| Input Capacitance                                                              |                                    |          | 10              | —       | pF     |

| Temperature Sensor                                                             |                                    | 1        |                 |         |        |

| Nonlinearity                                                                   | Notes 1, 2                         | —        | ±1              | —       | °C     |

| Absolute Accuracy                                                              | Notes 1, 2                         |          | ±3              | —       | °C     |

| Gain                                                                           | Notes 1, 2                         | _        | 2.86<br>±0.034  | _       | mV/°C  |

| Offset                                                                         | Notes 1, 2 (Temp = 0 °C)           | _        | 0.776<br>±0.009 | _       | V      |

| Power Specifications                                                           |                                    |          |                 |         |        |

| Power Supply Current (AV+ sup-<br>plied to ADC)                                | Operating Mode, 100 ksps           | _        | 450             | 900     | μA     |

| Power Supply Rejection                                                         |                                    |          | ±0.3            |         | mV/V   |

| Notes:<br>1. Represents one standard devi<br>2. Includes ADC offset, gain, and |                                    | 1        | 1               | ı       |        |

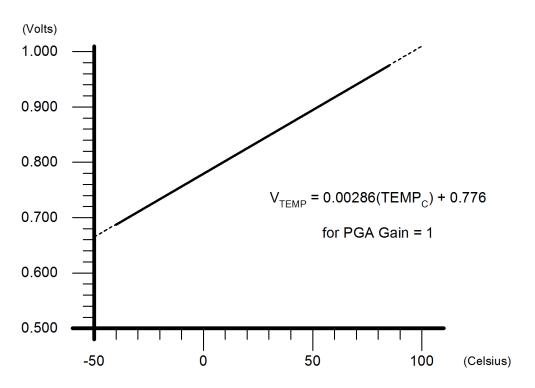

Figure 6.6. Temperature Sensor Transfer Function

#### SFR Definition 6.6. ADC0CN: ADC0 Control

| R/W     | R/W                     | R/W           | R/W                       | R/W            | R/W           | R/W            | R/W                 | Reset Value |

|---------|-------------------------|---------------|---------------------------|----------------|---------------|----------------|---------------------|-------------|

| AD0EN   | AD0TM                   | AD0INT        | AD0BUSY                   | AD0CM1         | AD0CM0        | AD0WINT        | AD0LJST             | 00000000    |

| Bit7    | Bit6                    | Bit5          | Bit4                      | Bit3           | Bit2          | Bit1           | Bit0<br>SFR Address |             |

|         |                         |               |                           |                |               |                | SFR Page            | 9: 0        |

| Bit7:   | AD0EN: AD               | DC0 Enable    | e Bit.                    |                |               |                |                     |             |

|         |                         |               | C0 is in low              |                |               |                |                     |             |

| DitC    | 1: ADC0 Ei<br>AD0TM: AE |               | C0 is active              | and ready      | for data con  | versions.      |                     |             |

| Bit6:   |                         |               |                           | kina is cont   | inuous unle   | ss a convers   | ion is in nro       | ncess       |

|         |                         |               | y AD0CM1-0                |                |               |                |                     | 0000        |

| Bit5:   | •                       |               | rsion Comp                |                | pt Flag.      |                |                     |             |

|         |                         |               | red by softw              |                |               |                |                     |             |

|         |                         |               |                           |                | n since the   | last time this | flag was cl         | eared.      |

| Bit4:   |                         | •             | ed a data co              | nversion.      |               |                |                     |             |

| DIL4.   | AD0BUSY:<br>Read:       | ADC0 Bus      | бу Біі.                   |                |               |                |                     |             |

|         |                         | onversion i   | s complete                | or a conver    | sion is not c | urrently in pr | ogress. AD          | 0INT is set |

|         | to logic 1 o            | n the falling | g edge of AE              | OBUSY.         |               |                | U U                 |             |

|         |                         | onversion i   | s in progres              | S.             |               |                |                     |             |

|         | Write:                  |               |                           |                |               |                |                     |             |

|         | 0: No Effect            |               | version if AE             | 00CM1_0 =      | 00b           |                |                     |             |

| Bit3-2: |                         |               | art of Conve              |                |               |                |                     |             |

|         | If AD0TM =              |               |                           |                |               |                |                     |             |

|         |                         |               | initiated on              |                |               | BUSY.          |                     |             |

|         |                         |               | initiated on              |                |               |                |                     |             |

|         |                         |               | initiated on initiated on |                |               | CNVSTR0.       |                     |             |

|         | If ADOTM =              |               |                           |                | TITTEL Z.     |                |                     |             |

|         | 00: Trackin             | g starts wit  | h the write o             | of '1' to ADO  | BUSY and      | lasts for 3 SA | AR clocks, f        | ollowed by  |

|         |                         |               | y the overflo             | w of Timer     | 3 and last fo | or 3 SAR clo   | cks, followe        | ed by con-  |

|         | version.<br>10: ADC0 t  | racks only    | when CNVS                 | STR0 input     | is logic low; | conversion s   | starts on ris       | ing         |

|         | CNVSTR0                 | •             |                           |                |               |                |                     |             |

|         | 11: Trackin version.    | g started b   | y the overflo             | w of Timer     | 2 and last fo | or 3 SAR clo   | cks, followe        | d by con-   |

| Bit1:   |                         |               | dow Compa<br>ed by softwa | •              | Flag.         |                |                     |             |

|         |                         |               | •                         |                | as not occur  | red since this | s flag was la       | ast cleared |

|         |                         |               | nparison Da               |                |               |                |                     |             |

| Bit0:   | AD0LJST: A              | ADC0 Left     | Justify Seleo             | ct.            |               |                |                     |             |

|         |                         |               | COL register              |                |               |                |                     |             |

|         | 1: Data in A            | ADCUH:AD      | C0L register              | 's are left-ju | istified.     |                |                     |             |

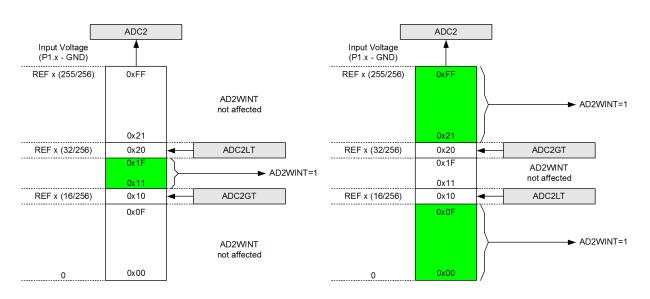

Figure 7.5. ADC Window Compare Examples, Single-Ended Mode

#### 12.3. Interrupt Handler

The CIP-51 includes an extended interrupt system supporting a total of 20 interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interruptpending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE-EIE2). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

**Note:** Any instruction that clears the EA bit should be immediately followed by an instruction that has two or more opcode bytes. For example:

// in 'C': EA = 0; // clear EA bit EA = 0; // ... followed by another 2-byte opcode ; in assembly: CLR EA ; clear EA bit CLR EA ; ... followed by another 2-byte opcode

If an interrupt is posted during the execution phase of a "CLR EA" opcode (or any instruction which clears the EA bit), and the instruction is followed by a single-cycle instruction, the interrupt may be taken. However, a read of the EA bit will return a '0' inside the interrupt service routine. When the "CLR EA" opcode is followed by a multi-cycle instruction, the interrupt will not be taken.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

#### 12.3.1. MCU Interrupt Sources and Vectors

The MCUs support 20 interrupt sources. Software can simulate an interrupt event by setting any interruptpending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 12.4. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

#### 12.3.2. External Interrupts

The external interrupt sources (/INT0 and /INT1) are configurable as active-low level-sensitive or activelow edge-sensitive inputs depending on the setting of bits IT0 (TCON.0) and IT1 (TCON.2). IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flag for the /INT0 and /INT1 external interrupts, respectively. If an /INT0 or /INT1 external interrupt is configured as edge-sensitive, the corresponding interruptpending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag follows the state of the external interrupt's input pin. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

| Interrupt Source                | Interrupt<br>Vector | Priority<br>Order | Pending Flag                                                                  | Bit addressable? | Cleared by HW? | SFRPAGE (SFRPGEN = 1) | Enable<br>Flag     | Priority<br>Control |

|---------------------------------|---------------------|-------------------|-------------------------------------------------------------------------------|------------------|----------------|-----------------------|--------------------|---------------------|

| Reset                           | 0x0000              | Тор               | None                                                                          | N/A              | N/A            | 0                     | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0<br>(/INT0) | 0x0003              | 0                 | IE0 (TCON.1)                                                                  | Y                | Y              | 0                     | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow                | 0x000B              | 1                 | TF0 (TCON.5)                                                                  | Y                | Y              | 0                     | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1<br>(/INT1) | 0x0013              | 2                 | IE1 (TCON.3)                                                                  | Y                | Y              | 0                     | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow                | 0x001B              | 3                 | TF1 (TCON.7)                                                                  | Y                | Y              | 0                     | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                           | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                                | Y                |                | 0                     | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2                         | 0x002B              | 5                 | TF2 (TMR2CN.7)                                                                | Y                |                | 0                     | ET2 (IE.5)         | PT2 (IP.5)          |

| Serial Peripheral<br>Interface  | 0x0033              | 6                 | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN<br>(SPI0CN.4) | Y                |                | 0                     | ESPI0<br>(EIE1.0)  | PSPI0<br>(EIP1.0)   |

| SMBus Interface                 | 0x003B              | 7                 | SI (SMB0CN.3)                                                                 | Y                |                | 0                     | ESMB0<br>(EIE1.1)  | PSMB0<br>(EIP1.1)   |

| ADC0 Window<br>Comparator       | 0x0043              | 8                 | AD0WINT<br>(ADC0CN.2)                                                         | Y                |                | 0                     | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2)  |

| Programmable<br>Counter Array   | 0x004B              | 9                 | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)                                              | Y                |                | 0                     | EPCA0<br>(EIE1.3)  | PPCA0<br>(EIP1.3)   |

| Comparator 0                    | 0x0053              | 10                | CP0FIF/CP0RIF<br>(CPT0CN.4/.5)                                                |                  |                | 1                     | CP0IE<br>(EIE1.4)  | PCP0<br>(EIP1.4)    |

#### Table 12.4. Interrupt Summary

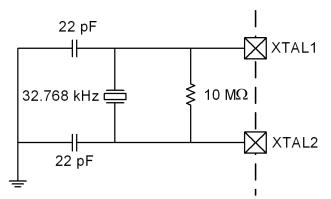

#### 14.4. External Crystal Example

If a crystal or ceramic resonator is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 14.1, Option 1. The External Oscillator Frequency Control value (XFCN) should be chosen from the Crystal column of the table in SFR Definition 14.4 (OSCXCN register). For example, an 11.0592 MHz crystal requires an XFCN setting of 111b.

When the crystal oscillator is enabled, the oscillator amplitude detection circuit requires a settle time to achieve proper bias. Introducing a delay of at least 1 ms between enabling the oscillator and checking the XTLVLD bit will prevent a premature switch to the external oscillator as the system clock. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure is:

- Step 1. Enable the external oscillator in crystal oscillator mode.

- Step 2. Wait at least 1 ms.

- Step 3. Poll for XTLVLD => '1'.

- Step 4. Switch the system clock to the external oscillator.

Note: Tuning-fork crystals may require additional settling time before XTLVLD returns a valid result.

The capacitors shown in the external crystal configuration provide the load capacitance required by the crystal for correct oscillation. These capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins.

**Note:** The load capacitance depends upon the crystal and the manufacturer. Please refer to the crystal data sheet when completing these calculations.

For example, a tuning-fork crystal of 32.768 kHz with a recommended load capacitance of 12.5 pF should use the configuration shown in Figure 14.1, Option 1. The total value of the capacitors and the stray capacitance of the XTAL pins should equal 25 pF. With a stray capacitance of 3 pF per pin, the 22 pF capacitors yield an equivalent capacitance of 12.5 pF across the crystal, as shown in Figure 14.2.

Figure 14.2. 32.768 kHz External Crystal Example

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

#### SFR Definition 15.3. PSCTL: Program Store Read/Write Control

| R/W      | D/M/                            |               |               |               | R/W          | R/W           | R/W                     | Reset Value  |

|----------|---------------------------------|---------------|---------------|---------------|--------------|---------------|-------------------------|--------------|

| K/W      | R/W                             | R/W           | R/W           | R/W           | SFLE         | PSEE          | PSWE                    |              |

| -        | -                               | -             | -             | -             |              | -             | -                       | 00000000     |

| Bit7     | Bit6                            | Bit5          | Bit4          | Bit3          | Bit2         | Bit1          | Bit0                    | SFR Address: |

|          |                                 |               |               |               |              |               | SFR Address<br>SFR Page | • • • • • •  |

|          |                                 |               |               |               |              |               | or itt age              |              |

| Bits7-3: | UNUSED. R                       | ead = 0000    | 00b, Write =  | don't care.   |              |               |                         |              |

| Bit2:    | SFLE: Scrat                     |               |               |               |              |               |                         |              |

|          | When this bi                    |               |               |               |              |               |                         | -            |

|          | Scratchpad                      |               |               |               |              |               |                         |              |

|          | range 0x00-                     |               | d not be atte | empted. Re    | ads/Writes   | out of this r | ange will yie           | eld unde-    |

|          | 0: Flash acc                    | -             | or coffwara   | diracted to   | the Progra   | m/Data Ela    | sh soctor               |              |

|          | 1: Flash acc                    |               |               |               | •            |               |                         |              |

| Bit1:    | PSEE: Prog                      |               |               |               | 110 120 by   | to oblationp  |                         |              |

|          | Setting this t                  |               |               |               | sh program   | memorv to     | be erased               | provided     |

|          | the PSWE b                      |               |               |               |              |               |                         |              |

|          | instruction w                   | ill erase the | e entire pag  | e that conta  | ins the loca | ation addres  | ssed by the             | MOVX         |

|          | instruction. 7                  | The value of  | f the data b  | yte written o | loes not ma  | atter. Note:  | The Flash               | page con-    |

|          | taining the                     | Read Lock     | Byte and N    | Nrite/Erase   | e Lock Byte  | es cannot b   | be erased b             | y soft-      |

|          | ware.                           |               |               |               |              |               |                         |              |

|          | 0: Flash prog                   |               | 2             |               |              |               |                         |              |

| D:10.    | 1: Flash prog                   |               |               |               |              |               |                         |              |

| Bit0:    | PSWE: Prog                      |               |               |               | ha Elach ar  | ogrom mon     | non / uning t           |              |

|          | Setting this the write instruct |               |               |               | •            | -             | nory using t            |              |

|          | 0: Write to F                   |               |               |               |              |               | target Exter            | nal RAM      |

|          | 1: Write to F                   | • •           | •             |               |              | •             | -                       |              |

|          |                                 |               |               |               |              |               | 5                       | j.           |

|          |                                 |               |               |               |              |               |                         |              |

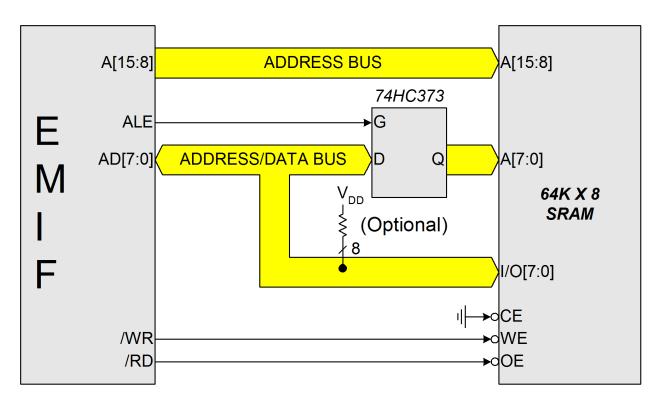

#### 16.4. Multiplexed and Non-multiplexed Selection

The External Memory Interface is capable of acting in a Multiplexed mode or a Non-multiplexed mode, depending on the state of the EMD2 (EMI0CF.4) bit.

#### 16.4.1. Multiplexed Configuration

In Multiplexed mode, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. In this mode, an external latch (74HC373 or equivalent logic gate) is used to hold the lower 8-bits of the RAM address. The external latch is controlled by the ALE (Address Latch Enable) signal, which is driven by the External Memory Interface logic. An example of a Multiplexed Configuration is shown in Figure 16.1.

In Multiplexed mode, the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the 'Q' outputs reflect the states of the 'D' inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time /RD or /WR is asserted.

Figure 16.1. Multiplexed Configuration Example

#### **19.4. SMBus Special Function Registers**

The SMBus0 serial interface is accessed and controlled through five SFRs: SMB0CN Control Register, SMB0CR Clock Rate Register, SMB0ADR Address Register, SMB0DAT Data Register and SMB0STA Status Register. The five special function registers related to the operation of the SMBus0 interface are described in the following sections.

#### 19.4.1. Control Register

The SMBus0 Control register SMB0CN is used to configure and control the SMBus0 interface. All of the bits in the register can be read or written by software. Two of the control bits are also affected by the SMBus0 hardware. The Serial Interrupt flag (SI, SMB0CN.3) is set to logic 1 by the hardware when a valid serial interrupt condition occurs. It can only be cleared by software. The Stop flag (STO, SMB0CN.4) is set to logic 1 by software. It is cleared to logic 0 by hardware when a STOP condition is detected on the bus.

Setting the ENSMB flag to logic 1 enables the SMBus0 interface. Clearing the ENSMB flag to logic 0 disables the SMBus0 interface and removes it from the bus. Momentarily clearing the ENSMB flag and then resetting it to logic 1 will reset SMBus0 communication. However, ENSMB should not be used to temporarily remove a device from the bus since the bus state information will be lost. Instead, the Assert Acknowledge (AA) flag should be used to temporarily remove the device from the bus (see description of AA flag below).

Setting the Start flag (STA, SMB0CN.5) to logic 1 will put SMBus0 in a master mode. If the bus is free, SMBus0 will generate a START condition. If the bus is not free, SMBus0 waits for a STOP condition to free the bus and then generates a START condition after a 5 µs delay per the SMB0CR value (In accordance with the SMBus protocol, the SMBus0 interface also considers the bus free if the bus is idle for 50 µs and no STOP condition was recognized). If STA is set to logic 1 while SMBus0 is in master mode and one or more bytes have been transferred, a repeated START condition will be generated.

When the Stop flag (STO, SMB0CN.4) is set to logic 1 while the SMBus0 interface is in master mode, the interface generates a STOP condition. In a slave mode, the STO flag may be used to recover from an error condition. In this case, a STOP condition is not generated on the bus, but the SMBus hardware behaves as if a STOP condition has been received and enters the "not addressed" slave receiver mode. Note that this simulated STOP will not cause the bus to appear free to SMBus0. The bus will remain occupied until a STOP appears on the bus or a Bus Free Timeout occurs. Hardware automatically clears the STO flag to logic 0 when a STOP condition is detected on the bus.

The Serial Interrupt flag (SI, SMB0CN.3) is set to logic 1 by hardware when the SMBus0 interface enters any one of the 28 possible states except the Idle state. If interrupts are enabled for the SMBus0 interface, an interrupt request is generated when the SI flag is set. The SI flag must be cleared by software.

**Important Note:** If SI is set to logic 1 while the SCL line is low, the clock-low period of the serial clock will be stretched and the serial transfer is suspended until SI is cleared to logic 0. A high level on SCL is not affected by the setting of the SI flag.

The Assert Acknowledge flag (AA, SMB0CN.2) is used to set the level of the SDA line during the acknowledge clock cycle on the SCL line. Setting the AA flag to logic 1 will cause an ACK (low level on SDA) to be sent during the acknowledge cycle if the device has been addressed. Setting the AA flag to logic 0 will cause a NACK (high level on SDA) to be sent during acknowledge cycle. After the transmission of a byte in slave mode, the slave can be temporarily removed from the bus by clearing the AA flag. The slave's own address and general call address will be ignored. To resume operation on the bus, the AA flag must be reset to logic 1 to allow the slave's address to be recognized.

| Mode               | Status<br>Code | SMBus State                                   | Typical Action                                                                                                                   |

|--------------------|----------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Ъъ                 | 0x08           | START condition transmitted.                  | Load SMB0DAT with Slave Address +<br>R/W. Clear STA.                                                                             |

| MT                 | 0x10           | Repeated START condition transmitted.         | Load SMB0DAT with Slave Address +<br>R/W. Clear STA.                                                                             |

|                    | 0x18           | Slave Address + W transmitted. ACK received.  | Load SMB0DAT with data to be transmit-<br>ted.                                                                                   |

| mitter             | 0x20           | Slave Address + W transmitted. NACK received. | Acknowledge poll to retry. Set STO + STA.                                                                                        |

| Master Transmitter | 0x28           | Data byte transmitted. ACK received.          | <ol> <li>Load SMB0DAT with next byte, OR</li> <li>Set STO, OR</li> <li>Clear STO then set STA for repeated<br/>START.</li> </ol> |

| Mas                | 0x30           | Data byte transmitted. NACK received.         | 1) Retry transfer OR<br>2) Set STO.                                                                                              |

|                    | 0x38           | Arbitration Lost.                             | Save current data.                                                                                                               |

| eiver              | 0x40           | Slave Address + R transmitted. ACK received.  | If only receiving one byte, clear AA (send NACK after received byte). Wait for received data.                                    |

| r Rec              | 0x48           | Slave Address + R transmitted. NACK received. | Acknowledge poll to retry. Set STO + STA.                                                                                        |

| Master Receiver    | 0x50           | Data byte received. ACK transmitted.          | Read SMB0DAT. Wait for next byte. If next byte is last byte, clear AA.                                                           |

|                    | 0x58           | Data byte received. NACK transmitted.         | Set STO.                                                                                                                         |

#### Table 19.1. SMB0STA Status Codes and States

| Frequency: 22.1184 MHz       Target<br>Baud Rate<br>(bps)     Baud Rate<br>% Error     Oscillator<br>Divide<br>Factor     Timer Clock<br>Source<br>Factor     SCA1-SCA0<br>(pre-scale<br>select)*     T1N | 1* Timer 1            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Baud Rate<br>(bps)         % Error<br>Factor         Divide<br>Source<br>Factor         Source<br>(pre-scale<br>select)*                                                                                  | Timer 1               |

|                                                                                                                                                                                                           | Reload<br>Value (hex) |

| 230400 0.00% 96 SYSCLK XX 1                                                                                                                                                                               | 0xD0                  |

| 115200 0.00% 192 SYSCLK XX 1                                                                                                                                                                              | 0xA0                  |

| 57600 0.00% 384 SYSCLK XX 1                                                                                                                                                                               | 0x40                  |

| 28800 0.00% 768 SYSCLK / 12 00 0                                                                                                                                                                          | 0xE0                  |

| 14400 0.00% 1536 SYSCLK / 12 00 0                                                                                                                                                                         | 0xC0                  |

| 9600 0.00% 2304 SYSCLK / 12 00 0                                                                                                                                                                          | 0xA0                  |

| 2400 0.00% 9216 SYSCLK / 48 10 0                                                                                                                                                                          | 0xA0                  |

| 1200 0.00% 18432 SYSCLK / 48 10 0                                                                                                                                                                         | 0x40                  |

| 230400 0.00% 96 EXTCLK / 8 11 0                                                                                                                                                                           | 0xFA                  |

| 115200 0.00% 192 EXTCLK / 8 11 0                                                                                                                                                                          | 0xF4                  |

| 57600 0.00% 384 EXTCLK / 8 11 0                                                                                                                                                                           | 0xE8                  |

| 28800 0.00% 768 EXTCLK / 8 11 0                                                                                                                                                                           | 0xD0                  |

| 14400 0.00% 1536 EXTCLK / 8 11 0                                                                                                                                                                          | 0xA0                  |

| 9600 0.00% 2304 EXTCLK / 8 11 0                                                                                                                                                                           | 0x70                  |

# Table 22.3. Timer Settings for Standard Baud Rates Using an External22.1184 MHz Oscillator

X = Don't care

\*Note: SCA1-SCA0 and T1M bit definitions can be found in Section 23.1.

#### SFR Definition 23.8. TMRnCN: Timer n Control

| R/W              | R/W                          | R/W           | R/W           | R/W             | R/W          | R/W          | R/W            | _ Reset Valu      |

|------------------|------------------------------|---------------|---------------|-----------------|--------------|--------------|----------------|-------------------|

| TFn              | EXFn                         | -             | -             | EXENn           | TRn          | C/Tn         | CP/RLn         | 0000000           |

| Bit7             | Bit6                         | Bit5          | Bit4          | Bit3            | Bit2         | Bit1         | Bit0           | Bit<br>Addressabl |

| SFR Addre        | ess: TMR2CN:0xC              | 8:TMR3CN:0    | xC8:TMR4CN    | 1:0xC8          |              |              |                | Addressabi        |

|                  | ige: TMR2CN: pag             |               |               |                 |              |              |                |                   |

|                  |                              |               |               |                 |              |              |                |                   |

| Bit7:            | TFn: Timer n                 | Overflow/U    | Inderflow F   | lag.            |              |              |                |                   |

|                  | Set by hardwa                | are when e    | ither the T   | imer overflow   | /s from 0xF  | FFF to 0x0   | 0000, under    | flows from        |

|                  | the value place              |               |               |                 |              |              |                |                   |

|                  | 0x0000 to 0xF                |               |               |                 |              |              |                |                   |

|                  | causes the CI                |               |               | •               |              | utine. This  | bit is not au  | tomatically       |

|                  | cleared by ha                |               |               | •               | oftware.     |              |                |                   |

| Bit6:            | EXFn: Timer 2                |               |               | -               |              |              |                |                   |

|                  | Set by hardwa                |               |               |                 |              |              |                |                   |

|                  | TnEX input pi                |               | •             |                 |              | •            |                | •                 |

|                  | causes the CI                |               |               | •               |              | utine. This  | bit is not au  | itomaticall       |

|                  | cleared by ha                | roware and    | a must be o   | cleared by so   | mware.       |              |                |                   |

| Bit5-4:<br>Bit3: | Reserved.                    | r n Evtorna   | l Enchlo      |                 |              |              |                |                   |

| ອແວ.             | EXENn: Time<br>Enables high- |               |               | ToEV to triac   | or conturo   | o roloado    | and control    | the diree         |

|                  | tion of the tim              |               |               |                 |              |              |                |                   |

|                  | counts up or c               |               |               |                 |              |              |                |                   |

|                  | a digital input.             |               |               |                 |              | 1, THEA 31   |                | iniguieu a        |

|                  | 0: Transitions               |               | X pin are     | ianored.        |              |              |                |                   |

|                  | 1: Transitions               |               |               |                 | eload. or co | ontrol the d | lirection of t | imer coun         |

|                  | (up or down) a               |               | P             | ,               | ,            |              |                |                   |

|                  | Capture Mode                 |               | Transition    | on TnEX pin     | causes RC    | CAPnH:RC     | APnL to cap    | oture timer       |

|                  | value.                       |               |               |                 |              |              |                |                   |

|                  | Auto-Reload N                | Mode:         |               |                 |              |              |                |                   |

|                  | DCEN                         | N = 0: '1'-to | -'0' transiti | on causes re    | eload of tim | er and sets  | s the EXFn     | Flag.             |

|                  |                              |               | -             | el controls dir | ection of ti | mer (up or   | down).         |                   |

| Bit2:            | TRn: Timer n                 |               | -             |                 |              |              |                |                   |

|                  | This bit enable              |               | s the respe   | ctive Timer.    |              |              |                |                   |

|                  | 0: Timer disat               |               | . ,           |                 |              |              |                |                   |

|                  | 1: Timer enab                |               |               | iting.          |              |              |                |                   |

| Bit1:            | C/Tn: Counter                |               |               | ad by alask     | defined by   | TnN11.TnN1   | 0              |                   |

|                  | 0: Timer Func                |               |               |                 | Jenned by    |              | 0              |                   |

|                  | (TMRnCF.4:T<br>1: Counter Fu |               |               | ented by high   | -to-low tra  | nsitions on  | external in    | out nin           |

| BitO:            | CP/RLn: Capt                 |               |               | ented by high   |              |              | external in    | put pin.          |

|                  | This bit select              |               |               | functions in a  | antura ar a  | uto-reload   | mode           |                   |

|                  |                              |               |               | UNCHORS IN C    | adiure or a  |              |                |                   |

|                  | 0: Timer is in /             |               |               |                 | apture or a  |              |                |                   |

#### 24.3. Register Descriptions for PCA0

Following are detailed descriptions of the special function registers related to the operation of PCA0.

|                         | R/W                                                                                                                                                                | R/W                                                                                                                                                                                          | R/W                                                                                                                                                                                      | R/W                                                                                                                                                                                   | R/W                                                                                                                                                                                       | R/W                                                                                                                                                       | R/W                                                                                                                                                  | Reset Valu                                                               |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| CF                      | CR                                                                                                                                                                 | CCF5                                                                                                                                                                                         | CCF4                                                                                                                                                                                     | CCF3                                                                                                                                                                                  | CCF2                                                                                                                                                                                      | CCF1                                                                                                                                                      | CCF0                                                                                                                                                 | 0000000                                                                  |

| Bit7                    | Bit6                                                                                                                                                               | Bit5                                                                                                                                                                                         | Bit4                                                                                                                                                                                     | Bit3                                                                                                                                                                                  | Bit2                                                                                                                                                                                      | Bit1                                                                                                                                                      | Bit0                                                                                                                                                 |                                                                          |

|                         |                                                                                                                                                                    |                                                                                                                                                                                              |                                                                                                                                                                                          |                                                                                                                                                                                       |                                                                                                                                                                                           |                                                                                                                                                           | SFR Address<br>SFR Page                                                                                                                              |                                                                          |

| t7:                     | CF: PCA Co                                                                                                                                                         |                                                                                                                                                                                              |                                                                                                                                                                                          |                                                                                                                                                                                       |                                                                                                                                                                                           |                                                                                                                                                           |                                                                                                                                                      |                                                                          |

|                         | Set by hardw                                                                                                                                                       |                                                                                                                                                                                              |                                                                                                                                                                                          |                                                                                                                                                                                       |                                                                                                                                                                                           |                                                                                                                                                           |                                                                                                                                                      |                                                                          |

|                         | the Counter/<br>tor to the CF                                                                                                                                      |                                                                                                                                                                                              |                                                                                                                                                                                          |                                                                                                                                                                                       |                                                                                                                                                                                           |                                                                                                                                                           |                                                                                                                                                      |                                                                          |

|                         | must be clea                                                                                                                                                       |                                                                                                                                                                                              |                                                                                                                                                                                          | ie. This bit                                                                                                                                                                          | is not auton                                                                                                                                                                              |                                                                                                                                                           | areu by har                                                                                                                                          | uware and                                                                |

| it6:                    | CR: PCA0 C                                                                                                                                                         |                                                                                                                                                                                              |                                                                                                                                                                                          | trol                                                                                                                                                                                  |                                                                                                                                                                                           |                                                                                                                                                           |                                                                                                                                                      |                                                                          |

|                         | This bit enab                                                                                                                                                      |                                                                                                                                                                                              |                                                                                                                                                                                          |                                                                                                                                                                                       | mer.                                                                                                                                                                                      |                                                                                                                                                           |                                                                                                                                                      |                                                                          |