Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                          |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 64                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 8x8b, 13x12b; D/A 2x10b, 2x12b                                |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 100-TQFP                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f040       |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F040/1/2/3/4/5/6/7

|    | 7.3.2. Window Detector in Differential Mode      | 102 |  |

|----|--------------------------------------------------|-----|--|

| 8  | DACs, 12-Bit Voltage Mode (C8051F040/1/2/3 Only) |     |  |

| 0. | 8.1. DAC Output Scheduling                       |     |  |

|    | 8.1.1. Update Output On-Demand                   | 106 |  |

|    | 8.1.2. Update Output Based on Timer Overflow     |     |  |

|    | 8.2. DAC Output Scaling/Justification            |     |  |

| 9. | Voltage Reference (C8051F040/2/4/6)              |     |  |

|    | Voltage Reference (C8051F041/3/5/7)              |     |  |

|    | . Comparators                                    |     |  |

|    | 11.1.Comparator Inputs                           | 123 |  |

| 12 | CIP-51 Microcontroller                           | 127 |  |

|    | 12.1.Instruction Set                             |     |  |

|    | 12.1.1.Instruction and CPU Timing                | 129 |  |

|    | 12.1.2.MOVX Instruction and Program Memory       | 129 |  |

|    | 12.2.Memory Organization                         |     |  |

|    | 12.2.1.Program Memory                            | 133 |  |

|    | 12.2.2.Data Memory                               | 134 |  |

|    | 12.2.3.General Purpose Registers                 |     |  |

|    | 12.2.4.Bit Addressable Locations                 | 134 |  |

|    | 12.2.5.Stack                                     |     |  |

|    | 12.2.6.Special Function Registers                |     |  |

|    | 12.2.7.Register Descriptions                     |     |  |

|    | 12.3.Interrupt Handler                           |     |  |

|    | 12.3.1.MCU Interrupt Sources and Vectors         |     |  |

|    | 12.3.2.External Interrupts                       |     |  |

|    | 12.3.3.Interrupt Priorities                      |     |  |

|    | 12.3.4.Interrupt Latency                         |     |  |

|    | 12.3.5.Interrupt Register Descriptions           |     |  |

|    | 12.4.Power Management Modes                      |     |  |

|    | 12.4.1.Idle Mode                                 |     |  |

|    | 12.4.2.Stop Mode                                 |     |  |

| 13 | Reset Sources                                    |     |  |

|    | 13.1.Power-On Reset                              |     |  |

|    | 13.2.Power-Fail Reset                            |     |  |

|    | 13.3.External Reset                              |     |  |

|    | 13.4.Missing Clock Detector Reset                |     |  |

|    | 13.5.Comparator0 Reset                           | 167 |  |

|    | 13.6.External CNVSTR0 Pin Reset                  |     |  |

|    | 13.7.Watchdog Timer Reset                        | 167 |  |

|    | 13.7.1.Enable/Reset WDT                          |     |  |

|    | 13.7.2.Disable WDT                               |     |  |

|    | 13.7.3.Disable WDT Lockout                       |     |  |

| _  | 13.7.4.Setting WDT Interval                      |     |  |

| 14 | 14. Oscillators                                  |     |  |

|    | 14.1.Programmable Internal Oscillator            | 173 |  |

# C8051F040/1/2/3/4/5/6/7

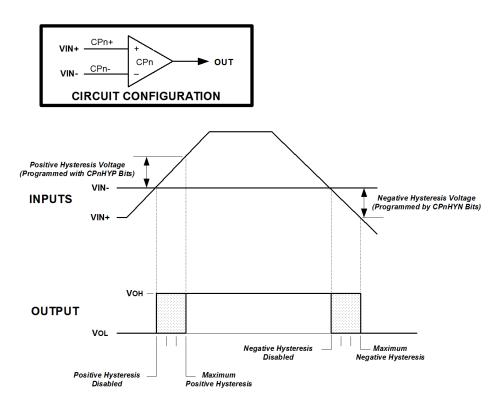

Figure 11.2. Comparator Hysteresis Plot

The hysteresis of the Comparator is software-programmable via its Comparator Control register (CPTnCN). The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The Comparator hysteresis is programmed using Bits3-0 in the Comparator Control Register CPTnCN (shown in SFR Definition 11.1). The amount of negative hysteresis voltage is determined by the settings of the CPnHYN bits. As shown in Table 11.1, settings of approximately 20, 10 or 5 mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CPnHYP bits.

Comparator interrupts can be generated on either rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see **Section "12.3. Interrupt Handler" on page 153**). The rising and/ or falling -edge interrupts are enabled using the comparator's Rising/Falling Edge Interrupt Enable Bits (CPnRIE and CPnFIE) in their respective Comparator Mode Selection Register (CPTnMD), shown in SFR Definition 11.2. These bits allow the user to control which edge (or both) will cause a comparator interrupt. However, the comparator interrupt must also be enabled in the Extended Interrupt Enable Register (EIE1). The CPnFIF flag is set to logic 1 upon a Comparator falling-edge interrupt, and the CPnRIF flag is set to logic 1 upon the Comparator can be obtained at any time by reading the CPnOUT bit. A Comparator is enabled by setting its respective CPnEN bit to logic 1, and is disabled by clearing this bit to logic 0.Upon enabling a comparator, the output of the comparator is not immediately valid. Before using a comparator as an interrupt or reset source, software should wait for a minimum of the specified "Power-up time" as specified in Table 11.1, "Comparator Electrical Characteristics," on page 126.

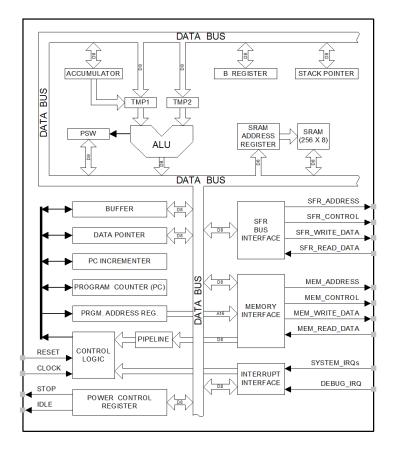

## 12. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. Included are five 16-bit counter/timers (see description in Section 23), two full-duplex UARTs (see description in Section 21 and Section 22), 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space (see Section 12.2.6), and 8/4 byte-wide I/O Ports (see description in Section 17). The CIP-51 also includes on-chip debug hardware (see description in Section 25), and interfaces directly with the MCUs' analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 12.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput with 25 MHz Clock

- 0 to 25 MHz Clock Frequency

- 256 Bytes of Internal RAM

- 8/4 Byte-Wide I/O Ports

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

Figure 12.1. CIP-51 Block Diagram

# C8051F040/1/2/3/4/5/6/7

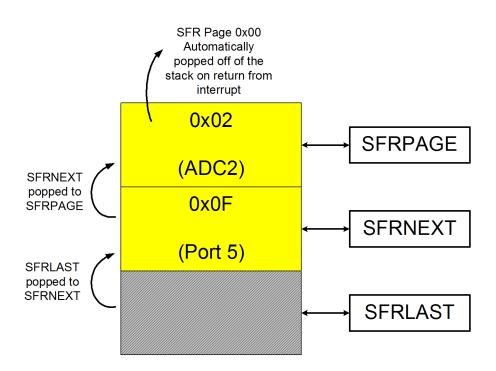

### Figure 12.7. SFR Page Stack Upon Return From PCA Interrupt

On the execution of the RETI instruction in the ADC2 Window Comparator ISR, the value in SFRPAGE register is overwritten with the contents of SFRNEXT. The CIP-51 may now access the Port 5 SFR bits as it did prior to the interrupts occurring. See Figure 12.8 below.

140

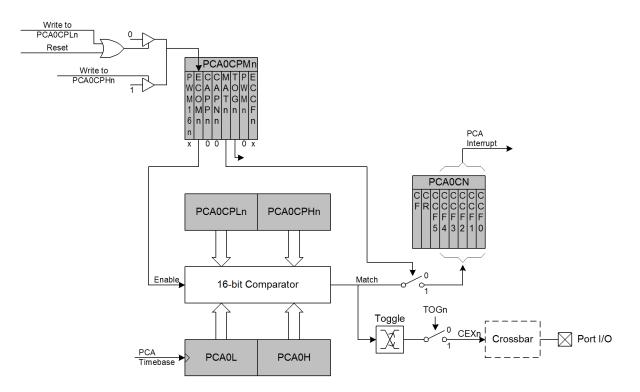

### 24.2.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode.

**Important Note About Capture/Compare Registers:** When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 24.6. PCA High-Speed Output Mode Diagram