Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                               |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 32                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 8x8b, 13x12b; D/A 2x10b, 2x12b                                |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 64-TQFP                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f041-gqr   |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 14.2.External Oscillator Drive Circuit                    | 175   |

|-----------------------------------------------------------|-------|

| 14.3.System Clock Selection                               |       |

| 14.4.External Crystal Example                             |       |

| 14.5.External RC Example                                  |       |

| 14.6.External Capacitor Example                           |       |

| 15. Flash Memory                                          |       |

| 15.1.Programming The Flash Memory                         |       |

| 15.2.Non-volatile Data Storage                            |       |

| 15.3.Security Options                                     |       |

| 15.3.1.Summary of Flash Security Options                  |       |

| 16. External Data Memory Interface and On-Chip XRAM       |       |

| 16.1.Accessing XRAM                                       |       |

| 16.1.1.16-Bit MOVX Example                                |       |

| 16.1.2.8-Bit MOVX Example                                 |       |

| 16.2.Configuring the External Memory Interface            | 188   |

| 16.3.Port Selection and Configuration                     | 188   |

| 16.4.Multiplexed and Non-multiplexed Selection            |       |

| 16.4.1.Multiplexed Configuration                          |       |

| 16.4.2.Non-multiplexed Configuration                      |       |

| 16.5.Memory Mode Selection                                |       |

| 16.5.1.Internal XRAM Only                                 |       |

| 16.5.2.Split Mode without Bank Select                     |       |

| 16.5.3.Split Mode with Bank Select                        |       |

| 16.5.4.External Only                                      |       |

| 16.6.Timing                                               |       |

| 16.6.1.Non-multiplexed Mode                               |       |

| 16.6.2.Multiplexed Mode                                   |       |

| 17. Port Input/Output                                     |       |

| 17.1.Ports 0 through 3 and the Priority Crossbar Decoder  |       |

| 17.1.1.Crossbar Pin Assignment and Allocation             |       |

| 17.1.2.Configuring the Output Modes of the Port Pins      |       |

| 17.1.3.Configuring Port Pins as Digital Inputs            |       |

| 17.1.4.Weak Pullups                                       |       |

| 17.1.5.Configuring Port 1, 2, and 3 Pins as Analog Inputs |       |

| 17.1.6.External Memory Interface Pin Assignments          |       |

| 17.1.7.Crossbar Pin Assignment Example                    |       |

| 17.2.Ports 4 through 7                                    |       |

| 17.2.1.Configuring Ports Which are Not Pinned Out         | . 221 |

| 17.2.2.Configuring the Output Modes of the Port Pins      |       |

| 17.2.3.Configuring Port Pins as Digital Inputs            |       |

| 17.2.4.Weak Pullups                                       |       |

| 17.2.5.External Memory Interface                          | . 221 |

| 18. Controller Area Network (CAN0)                        |       |

| 18.1.Bosch CAN Controller Operation                       |       |

| 18.1.1.CAN Controller Timing                              |       |

|                                                           |       |

| 18.Controller Area Network (CAN0)                                                                          |     |

|------------------------------------------------------------------------------------------------------------|-----|

| Table 18.1. Background System Information                                                                  | 229 |

| Table 18.2. CAN Register Index and Reset Values                                                            | 233 |

| 19. System Management BUS/I <sup>2</sup> C BUS (SMBUS0)                                                    |     |

| Table 19.1. SMB0STA Status Codes and States 2                                                              | 252 |

| 20. Enhanced Serial Peripheral Interface (SPI0)                                                            |     |

| 21.UART0                                                                                                   |     |

| Table 21.1. UART0 Modes 2                                                                                  | 266 |

| Table 21.2. Oscillator Frequencies for Standard Baud Rates                                                 | 273 |

| 22.UART1                                                                                                   |     |

| Table 22.1. Timer Settings for Standard Baud Rates Using the Internal 24.5 MHz C         cillator       2  |     |

| Table 22.2. Timer Settings for Standard Baud Rates Using an External 25.0 MHz C         cillator       2   |     |

| Table 22.3. Timer Settings for Standard Baud Rates Using an External 22.1184 MI         Oscillator       2 | Hz  |

| Table 22.4. Timer Settings for Standard Baud Rates Using an External 18.432 MH         Oscillator       2  |     |

| Table 22.5. Timer Settings for Standard Baud Rates Using an External 11.0592 MF<br>Oscillator              |     |

| Table 22.6. Timer Settings for Standard Baud Rates Using an External 3.6864 MH         Oscillator       2  |     |

| 23. Timers                                                                                                 |     |

| 24. Programmable Counter Array                                                                             |     |

| Table 24.1. PCA Timebase Input Options                                                                     | 306 |

| Table 24.2. PCA0CPM Register Settings for PCA Capture/Compare Modules 3<br>25. JTAG (IEEE 1149.1)          | 307 |

| Table 25.1. Boundary Data Register Bit Definitions         3                                               | 320 |

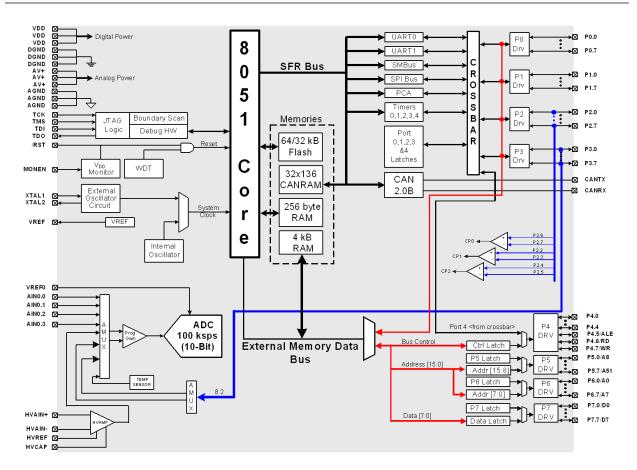

Figure 1.3. C8051F044/6 Block Diagram

## 4. Pinout and Package Definitions

|                 | Pin Nu     | mbers      |       | Description                                                                                                                                                                                                                                                                                       |  |  |

|-----------------|------------|------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name            | F040/2/4/6 | F041/3/5/7 | Туре  |                                                                                                                                                                                                                                                                                                   |  |  |

| V <sub>DD</sub> | 37, 64, 90 | 24, 41, 57 |       | Digital Supply Voltage. Must be tied to +2.7 to +3.6 V.                                                                                                                                                                                                                                           |  |  |

| DGND            | 38, 63, 89 | 25, 40, 56 |       | Digital Ground. Must be tied to Ground.                                                                                                                                                                                                                                                           |  |  |

| AV+             | 8, 11, 14  | 3, 6       |       | Analog Supply Voltage. Must be tied to +2.7 to +3.6 V.                                                                                                                                                                                                                                            |  |  |

| AGND            | 9, 10, 13  | 4, 5       |       | Analog Ground. Must be tied to Ground.                                                                                                                                                                                                                                                            |  |  |

| TMS             | 1          | 58         | D In  | JTAG Test Mode Select with internal pullup.                                                                                                                                                                                                                                                       |  |  |

| TCK             | 2          | 59         | D In  | JTAG Test Clock with internal pullup.                                                                                                                                                                                                                                                             |  |  |

| TDI             | 3          | 60         | D In  | JTAG Test Data Input with internal pullup. TDI is latched on the rising edge of TCK.                                                                                                                                                                                                              |  |  |

| TDO             | 4          | 61         | D Out | JTAG Test Data Output with internal pullup. Data is shifted out on TDO on the falling edge of TCK. TDO output is a tri-state driver.                                                                                                                                                              |  |  |

| /RST            | 5          | 62         | D I/O | Device Reset. Open-drain output of internal $V_{DD}$ monitor.<br>Is driven low when $V_{DD}$ is < 2.7 V and MONEN is high. An<br>external source can initiate a system reset by driving this<br>pin low.                                                                                          |  |  |

| XTAL1           | 26         | 17         | A In  | Crystal Input. This pin is the return for the internal oscilla-<br>tor circuit for a crystal or ceramic resonator. For a preci-<br>sion internal clock, connect a crystal or ceramic resonator<br>from XTAL1 to XTAL2. If overdriven by an external CMOS<br>clock, this becomes the system clock. |  |  |

| XTAL2           | 27         | 18         | A Out | Crystal Output. This pin is the excitation driver for a crystal or ceramic resonator.                                                                                                                                                                                                             |  |  |

| MONEN           | 28         | 19         | D In  | $V_{DD}$ Monitor Enable. When tied high, this pin enables the internal $V_{DD}$ monitor, which forces a system reset when $V_{DD}$ is < 2.7 V. When tied low, the internal $V_{DD}$ monitor is disabled.<br>In most applications, MONEN should be connected directly to $V_{DD}$ .                |  |  |

| VREF            | 12         | 7          | A I/O | Bandgap Voltage Reference Output (all devices).<br>DAC Voltage Reference Input (C8051F041/3 only).                                                                                                                                                                                                |  |  |

| VREFA           |            | 8          | A In  | ADC0 (C8051F041/3/5/7) and ADC2 (C8051F041/3 only) Voltage Reference Input.                                                                                                                                                                                                                       |  |  |

| VREF0           | 16         |            | A In  | ADC0 Voltage Reference Input.                                                                                                                                                                                                                                                                     |  |  |

| VREF2           | 17         |            | A In  | ADC2 Voltage Reference Input (C8051F040/2 only).                                                                                                                                                                                                                                                  |  |  |

| VREF            | 15         |            | A In  | DAC Voltage Reference Input (C8051F040/2 only).                                                                                                                                                                                                                                                   |  |  |

| AIN0.0          | 18         | 9          | A In  | ADC0 Input Channel 0 (See ADC0 Specification for complete description).                                                                                                                                                                                                                           |  |  |

## Table 4.1. Pin Definitions

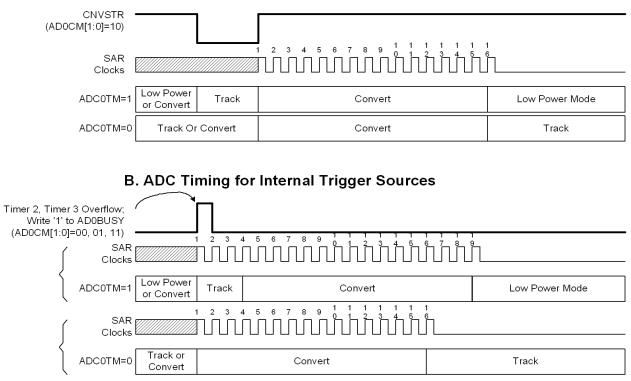

#### A. ADC Timing for External Trigger Source

## Figure 5.4. 12-Bit ADC Track and Conversion Example Timing

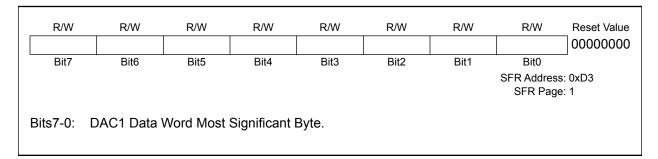

## SFR Definition 8.4. DAC1H: DAC1 High Byte

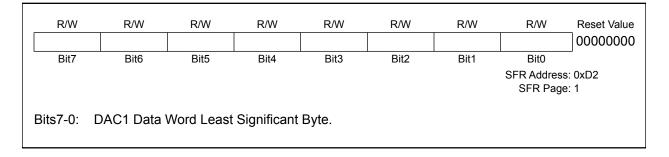

## SFR Definition 8.5. DAC1L: DAC1 Low Byte

## Table 11.1. Comparator Electrical Characteristics

| Parameter                                         | Conditions           | Min   | Тур   | Max                    | Units |

|---------------------------------------------------|----------------------|-------|-------|------------------------|-------|

| Response Time,                                    | CPn+ – CPn– = 100 mV | —     | 100   | _                      | ns    |

| Mode 0                                            | CPn+ – CPn– = 10 mV  |       | 250   | _                      | ns    |

| Response Time,                                    | CPn+ – CPn– = 100 mV |       | 175   | _                      | ns    |

| Mode 1                                            | CPn+ – CPn– = 10 mV  |       | 500   | _                      | ns    |

| Response Time,                                    | CPn+ – CPn– = 100 mV |       | 320   | _                      | ns    |

| Mode 2                                            | CPn+ – CPn– = 10 mV  |       | 1100  | _                      | ns    |

| Response Time,                                    | CPn+ – CPn– = 100 mV |       | 1050  | _                      | ns    |

| Mode 3                                            | CPn+ – CPn– = 10 mV  | -     | 5200  | _                      | ns    |

| Common-Mode Rejection<br>Ratio                    |                      | _     | 1.5   | 4                      | mV/V  |

| Positive Hysteresis 1                             | CPnHYP1-0 = 00       |       | 0     | 1                      | mV    |

| Positive Hysteresis 2                             | CPnHYP1-0 = 01       | 2     | 4.5   | 7                      | mV    |

| Positive Hysteresis 3                             | CPnHYP1-0 = 10       | 4     | 9     | 13                     | mV    |

| Positive Hysteresis 4                             | CPnHYP1-0 = 11       | 10    | 17    | 25                     | mV    |

| Negative Hysteresis 1                             | CPnHYN1-0 = 00       |       | 0     | 1                      | mV    |

| Negative Hysteresis 2                             | CPnHYN1-0 = 01       | 2     | 4.5   | 7                      | mV    |

| Negative Hysteresis 3                             | CPnHYN1-0 = 10       | 4     | 9     | 13                     | mV    |

| Negative Hysteresis 4                             | CPnHYN1-0 = 11       | 10    | 17    | 25                     | mV    |

| Inverting or Non-Inverting<br>Input Voltage Range |                      | -0.25 |       | V <sub>DD</sub> + 0.25 | V     |

| Input Capacitance                                 |                      |       | 7     |                        | pF    |

| Input Bias Current                                |                      | -5    | 0.001 | +5                     | nA    |

| Input Offset Voltage                              |                      | -5    |       | +5                     | mV    |

| Power Supply                                      |                      |       |       |                        |       |

| Power Supply Rejection                            |                      | _     | 0.1   | 1                      | mV/V  |

| Power-up Time                                     |                      |       | 10    | _                      | μs    |

|                                                   | Mode 0               | —     | 7.6   |                        | μA    |

| Supply Current at DC                              | Mode 1               | - 1   | 3.2   | _                      | μA    |

| Supply Current at DC                              | Mode 2               | —     | 1.3   |                        | μA    |

|                                                   | Mode 3               |       | 0.4   |                        | μA    |

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise specified.

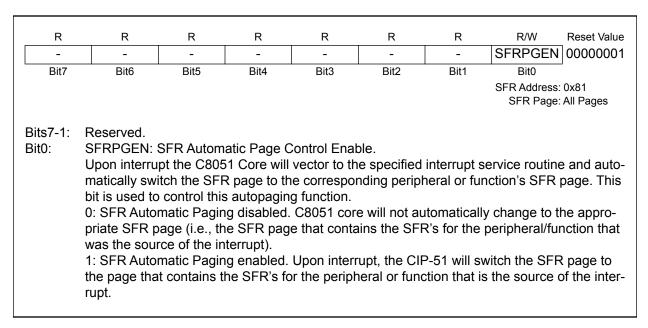

## SFR Definition 12.1. SFR Page Control Register: SFRPGCN

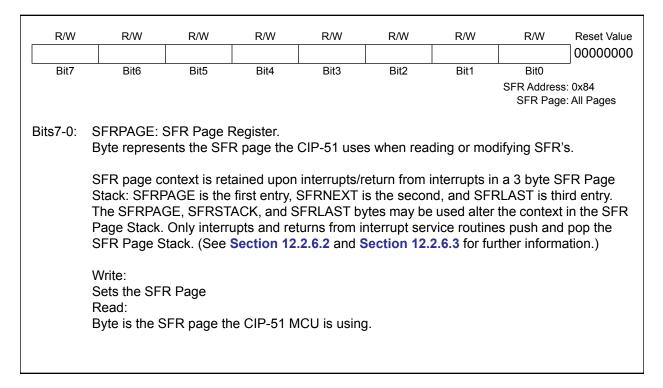

## SFR Definition 12.2. SFR Page Register: SFRPAGE

### Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register             | Address | SFR Page  | Description                           | Page No.                                    |

|----------------------|---------|-----------|---------------------------------------|---------------------------------------------|

| DAC1L <sup>3</sup>   | 0xD2    | 1         | DAC1 Low Byte                         | page 109                                    |

| DPH                  | 0x83    | All Pages | Data Pointer High                     | page 150                                    |

| DPL                  | 0x82    | All Pages | Data Pointer Low                      | page 150                                    |

| EIE1                 | 0xE6    | All Pages | Extended Interrupt Enable 1           | page 159                                    |

| EIE2                 | 0xE7    | All Pages | Extended Interrupt Enable 2           | page 160                                    |

| EIP1                 | 0xF6    | All Pages | Extended Interrupt Priority 1         | page 161                                    |

| EIP2                 | 0xF7    | All Pages | Extended Interrupt Priority 2         | page 162                                    |

| EMI0CF               | 0xA3    | 0         | EMIF Configuration                    | page 190                                    |

| EMI0CN               | 0xA2    | 0         | External Memory Interface Control     | page 189                                    |

| EMI0TC               | 0xA1    | 0         | EMIF Timing Control                   | page 195                                    |

| FLACL                | 0xB7    | F         | Flash Access Limit                    | page 184                                    |

| FLSCL                | 0xB7    | 0         | Flash Scale                           | page 184                                    |

| HVA0CN               | 0xD6    | 0         | High Voltage Differential Amp Control | page 53 <sup>1</sup> , page 75 <sup>2</sup> |

| IE                   | 0xA8    | All Pages | Interrupt Enable                      | page 157                                    |

| IP                   | 0xB8    | All Pages | Interrupt Priority                    | page 158                                    |

| OSCICL               | 0x8B    | F         | Internal Oscillator Calibration       | page 174                                    |

| OSCICN               | 0x8A    | F         | Internal Oscillator Control           | page 174                                    |

| OSCXCN               | 0x8C    | F         | External Oscillator Control           | page 176                                    |

| P0                   | 0x80    | All Pages | Port 0 Latch                          | page 215                                    |

| POMDOUT              | 0xA4    | F         | Port 0 Output Mode Configuration      | page 216                                    |

| P1                   | 0x90    | All Pages | Port 1 Latch                          | page 216                                    |

| P1MDIN               | 0xAD    | F         | Port 1 Input Mode Configuration       | page 217                                    |

| P1MDOUT              | 0xA5    | F         | Port 1 Output Mode Configuration      | page 217                                    |

| P2                   | 0xA0    | All Pages | Port 2 Latch                          | page 218                                    |

| P2MDIN               | 0xAE    | F         | Port 2 Input Mode Configuration       | page 218                                    |

| P2MDOUT              | 0xA6    | F         | Port 2 Output Mode Configuration      | page 219                                    |

| P3                   | 0xB0    | All Pages | Port 3 Latch                          | page 219                                    |

| P3MDIN               | 0xAF    | F         | Port 3 Input Mode Configuration       | page 220                                    |

| P3MDOUT              | 0xA7    | F         | Port 3 Output Mode Configuration      | page 220                                    |

| P4 <sup>4</sup>      | 0xC8    | F         | Port 4 Latch                          | page 222                                    |

| P4MDOUT <sup>4</sup> | 0x9C    | F         | Port 4 Output Mode Configuration      | page 222                                    |

| P5 <sup>4</sup>      | 0xD8    | F         | Port 5 Latch                          | page 223                                    |

| P5MDOUT <sup>4</sup> | 0x9D    | F         | Port 5 Output Mode Configuration      | page 223                                    |

| P6 <sup>4</sup>      | 0xE8    | F         | Port 6 Latch                          | page 224                                    |

| P6MDOUT <sup>4</sup> | 0x9E    | F         | Port 6 Output Mode Configuration      | page 224                                    |

| P7 <sup>4</sup>      | 0xF8    | F         | Port 7 Latch                          | page 225                                    |

| P7MDOUT <sup>4</sup> | 0x9F    | F         | Port 7 Output Mode Configuration      | page 225                                    |

| PCA0CN               | 0xD8    | 0         | PCA Control                           | page 314                                    |

| PCA0CPH0             | 0xFC    | 0         | PCA Capture 0 High                    | page 318                                    |

| PCA0CPH1             | 0xFE    | 0         | PCA Capture 1 High                    | page 318                                    |

| PCA0CPH2             | 0xEA    | 0         | PCA Capture 2 High                    | page 318                                    |

| PCA0CPH3             | 0xEC    | 0         | PCA Capture 3 High                    | page 318                                    |

# C8051F040/1/2/3/4/5/6/7

### SFR Definition 12.9. ACC: Accumulator

| R/W<br>ACC.7                                                                              | R/W<br>ACC.6 | R/W<br>ACC.5 | R/W<br>ACC.4 | R/W<br>ACC.3 | R/W<br>ACC.2 | R/W<br>ACC.1 | R/W<br>ACC.0            | Reset Value             |

|-------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|-------------------------|-------------------------|

| Bit7                                                                                      | Bit6         | Bit5         | Bit4         | Bit3         | Bit2         | Bit1         | Bit0                    | Bit<br>Addressable      |

|                                                                                           |              |              |              |              |              |              | SFR Address<br>SFR Page | s: 0xE0<br>e: All Pages |

| Bits7-0: ACC: Accumulator.<br>This register is the accumulator for arithmetic operations. |              |              |              |              |              |              |                         |                         |

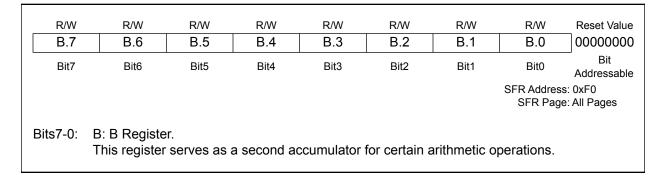

#### SFR Definition 12.10. B: B Register

#### 12.3.3. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP-EIP2) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 12.4.

#### 12.3.4. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. The fastest possible response time is 5 system clock cycles: 1 clock cycle to detect the interrupt and 4 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the slowest response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 18 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 4 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

#### 12.3.5. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described below. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

#### 12.17.2.Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes. In Stop mode, the CPU and internal oscillators are stopped, effectively shutting down all digital peripherals. Each analog peripheral must be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to sleep for longer than the MCD timeout of 100  $\mu$ s.

| R/W              | R/W                                                                                                                                        | R/W                                                                                                                                                                                                                                                                                                                                                                                           | R/W  | R/W  | R/W  | R/W  | R/W                    | Reset Value             |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------------------------|-------------------------|--|

| _                | _                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                               | _    | —    | —    | STOP | IDLE                   | 00000000                |  |

| Bit7             | Bit6                                                                                                                                       | Bit5                                                                                                                                                                                                                                                                                                                                                                                          | Bit4 | Bit3 | Bit2 | Bit1 | Bit0                   |                         |  |

|                  |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                               |      |      |      |      | SFR Address<br>SFR Pag | s: 0x87<br>e: All Pages |  |

| Bits7-3<br>Bit1: | STOP: STOP Mode Select.<br>Writing a '1' to this bit will place the CIP-51 into STOP mode. This bit will always read '0'.<br>0: No effect. |                                                                                                                                                                                                                                                                                                                                                                                               |      |      |      |      |                        |                         |  |

| Bit0:            | Writing a '1'<br>0: No effect.<br>1: CIP-51 fo                                                                                             | <ol> <li>CIP-51 forced into power-down mode. (Turns off internal oscillator).</li> <li>IDLE: IDLE Mode Select.</li> <li>Writing a '1' to this bit will place the CIP-51 into IDLE mode. This bit will always read '0'.</li> <li>O: No effect.</li> <li>CIP-51 forced into idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts, and all peripherals remain active.)</li> </ol> |      |      |      |      |                        |                         |  |

#### SFR Definition 12.18. PCON: Power Control

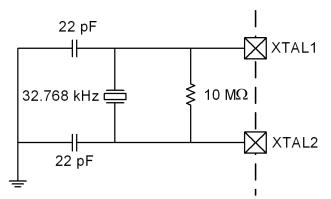

### 14.4. External Crystal Example

If a crystal or ceramic resonator is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 14.1, Option 1. The External Oscillator Frequency Control value (XFCN) should be chosen from the Crystal column of the table in SFR Definition 14.4 (OSCXCN register). For example, an 11.0592 MHz crystal requires an XFCN setting of 111b.

When the crystal oscillator is enabled, the oscillator amplitude detection circuit requires a settle time to achieve proper bias. Introducing a delay of at least 1 ms between enabling the oscillator and checking the XTLVLD bit will prevent a premature switch to the external oscillator as the system clock. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure is:

- Step 1. Enable the external oscillator in crystal oscillator mode.

- Step 2. Wait at least 1 ms.

- Step 3. Poll for XTLVLD => '1'.

- Step 4. Switch the system clock to the external oscillator.

Note: Tuning-fork crystals may require additional settling time before XTLVLD returns a valid result.

The capacitors shown in the external crystal configuration provide the load capacitance required by the crystal for correct oscillation. These capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins.

**Note:** The load capacitance depends upon the crystal and the manufacturer. Please refer to the crystal data sheet when completing these calculations.

For example, a tuning-fork crystal of 32.768 kHz with a recommended load capacitance of 12.5 pF should use the configuration shown in Figure 14.1, Option 1. The total value of the capacitors and the stray capacitance of the XTAL pins should equal 25 pF. With a stray capacitance of 3 pF per pin, the 22 pF capacitors yield an equivalent capacitance of 12.5 pF across the crystal, as shown in Figure 14.2.

Figure 14.2. 32.768 kHz External Crystal Example

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

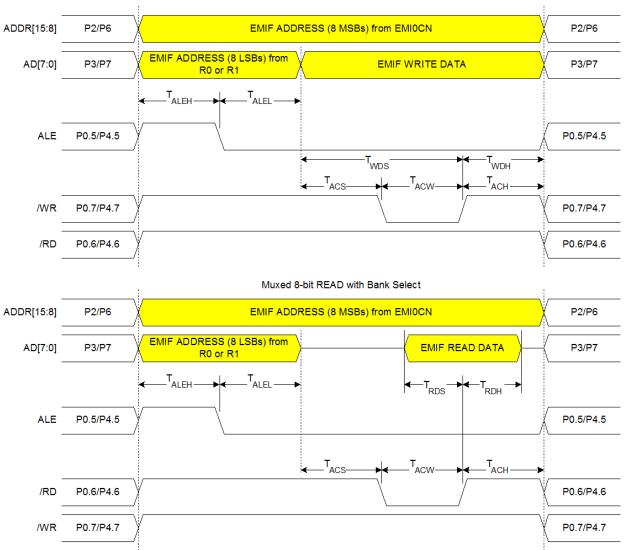

#### 16.6.2.3.8-bit MOVX with Bank Select: EMI0CF[4:2] = '010'.

Muxed 8-bit WRITE with Bank Select

Figure 16.9. Multiplexed 8-bit MOVX with Bank Select Timing

# C8051F040/1/2/3/4/5/6/7

SFR Definition 17.7, SFR Definition 17.10, and SFR Definition 17.13), a set of SFRs which are both byteand bit-addressable. The output states of Port pins that are allocated by the Crossbar are controlled by the digital peripheral that is mapped to those pins. Writes to the Port Data registers (or associated Port bits) will have no effect on the states of these pins.

A Read of a Port Data register (or Port bit) will always return the logic state present at the pin itself, regardless of whether the Crossbar has allocated the pin for peripheral use or not. An exception to this occurs during the execution of a *read-modify-write* instruction (ANL, ORL, XRL, CPL, INC, DEC, DJNZ, JBC, CLR, SET, and the bitwise MOV operation). During the *read* cycle of the *read-modify-write* instruction, it is the contents of the Port Data register, not the state of the Port pins themselves, which is read.

Because the Crossbar registers affect the pinout of the peripherals of the device, they are typically configured in the initialization code of the system before the peripherals themselves are configured. Once configured, the Crossbar registers are typically left alone.

Once the Crossbar registers have been properly configured, the Crossbar is enabled by setting XBARE (XBR2.4) to a logic 1. Until XBARE is set to a logic 1, the output drivers on Ports 0 through 3 are explicitly disabled in order to prevent possible contention on the Port pins while the Crossbar registers and other registers which can affect the device pinout are being written.

The output drivers on Crossbar-assigned input signals (like RX0, for example) are explicitly disabled; thus the values of the Port Data registers and the PnMDOUT registers have no effect on the states of these pins.

#### 17.1.2. Configuring the Output Modes of the Port Pins

The output drivers on Ports 0 through 3 remain disabled until the Crossbar is enabled by setting XBARE (XBR2.4) to a logic 1.

The output mode of each port pin can be configured to be either Open-Drain or Push-Pull. In the Push-Pull configuration, writing a logic 0 to the associated bit in the Port Data register will cause the Port pin to be driven to GND, and writing a logic 1 will cause the Port pin to be driven to  $V_{DD}$ . In the Open-Drain configuration, writing a logic 0 to the associated bit in the Port Data register will cause the Port pin to be driven to GND, and a logic 1 will cause the Port pin to assume a high-impedance state. The Open-Drain configuration is useful to prevent contention between devices in systems where the Port pin participates in a shared interconnection in which multiple outputs are connected to the same physical wire (like the SDA signal on an SMBus connection).

The output modes of the Port pins on Ports 0 through 3 are determined by the bits in the associated PnMDOUT registers (See SFR Definition 17.6, SFR Definition 17.9, SFR Definition 17.12, and SFR Definition 17.15). For example, a logic 1 in P3MDOUT.7 will configure the output mode of P3.7 to Push-Pull; a logic 0 in P3MDOUT.7 will configure the output mode of P3.7 to Open-Drain. All Port pins default to Open-Drain output.

The PnMDOUT registers control the output modes of the port pins regardless of whether the Crossbar has allocated the Port pin for a digital peripheral or not. The exceptions to this rule are: the Port pins connected to SDA, SCL, RX0 (if UART0 is in Mode 0), and RX1 (if UART1 is in Mode 0) are always configured as Open-Drain outputs, regardless of the settings of the associated bits in the PnMDOUT registers.

#### 17.1.3. Configuring Port Pins as Digital Inputs

A Port pin is configured as a digital input by setting its output mode to "Open-Drain" in the PnMDOUT register and writing a logic 1 to the associated bit in the Port Data register. For example, P3.7 is configured as

#### 18.2.3. Message Handler Registers

The Message Handler Registers are *read only* registers. Their flags can be read via the indexed access method with CAN0ADR, CAN0DATH, and CAN0DATL. The message handler registers provide interrupt, error, transmit/receive requests, and new data information.

Please refer to the Bosch CAN User's Guide for information on the function and use of the Message Handler Registers.

#### 18.2.4. CIP-51 MCU Special Function Registers

C8051F04x family peripherals are modified, monitored, and controlled using Special Function Registers (SFR's). Only three of the CAN Controller's registers may be accessed directly with SFR's. However, all CAN Controller registers can be accessed indirectly using three CIP-51 MCU SFR's: the CAN Data Registers (CAN0DATH and CAN0DATL) and CAN Address Register (CAN0ADR).

#### 18.2.5. Using CAN0ADR, CAN0DATH, and CANDATL to Access CAN Registers

Each CAN Controller Register has an index number (see Table 18.2). The CAN register address space is 128 words (256 bytes). A CAN register is accessed via the CAN Data Registers (CAN0DATH and CAN0-DATL) when a CAN register's index number is placed into the CAN Address Register (CAN0ADR). For example, if the Bit Timing Register is to be configured with a new value, CAN0ADR is loaded with 0x03. The low byte of the desired value is accessed using CAN0DATL and the high byte of the bit timing register is accessed using CAN0DATL is bit addressable for convenience. To load the value 0x2304 into the Bit Timing Register:

CANOADR = 0x03; // Load Bit Timing Register's index (Table 18.1) CANODATH = 0x23; // Move the upper byte into data reg high byte CANODATL = 0x04; // Move the lower byte into data reg low byte

<u>Note:</u> CAN0CN, CAN0STA, and CAN0TST may be accessed either by using the index method, or by direct access with the CIP-51 MCU SFR's. CAN0CN is located at SFR location 0xF8/SFR page 1 (SFR Definition 18.3), CAN0TST at 0xDB/SFR page 1 (SFR Definition 18.4), and CAN0STA at 0xC0/SFR page 1 (SFR Definition 18.5).

#### 18.2.6. CAN0ADR Autoincrement Feature

For ease of programming message objects, CAN0ADR features autoincrementing for the index ranges 0x08 to 0x12 (Interface Registers 1) and 0x20 to 0x2A (Interface Registers 2). When the CAN0ADR register has an index in these ranges, the CAN0ADR will autoincrement by 1 to point to the next CAN register 16-bit word upon a read/write of <u>CAN0DATL</u>. This speeds programming of the frequently-accessed interface registers when configuring message objects.

<u>NOTE:</u> Table 18.2 below supersedes Figure 5 in Section 3, "Programmer's Model" of the Bosch CAN User's Guide.

#### 21.3. Configuration of a Masked Address

The UART0 address is configured via two SFRs: SADDR0 (Serial Address) and SADEN0 (Serial Address Enable). SADEN0 sets the bit mask for the address held in SADDR0: bits set to logic 1 in SADEN0 correspond to bits in SADDR0 that are checked against the received address byte; bits set to logic 0 in SADEN0 correspond to "don't care" bits in SADDR0.

| Example 1, SLAVE #1 |            | Example 2, S  | LAVE #2    | Example 3, S  | Example 3, SLAVE #3 |  |  |

|---------------------|------------|---------------|------------|---------------|---------------------|--|--|

| SADDR0              | = 00110101 | SADDR0        | = 00110101 | SADDR0        | = 00110101          |  |  |

| SADEN0              | = 00001111 | SADEN0        | = 11110011 | SADEN0        | = 11000000          |  |  |

| UART0 Address       | = xxxx0101 | UART0 Address | = 0011xx01 | UART0 Address | = 00xxxxxx          |  |  |

Setting the SM20 bit (SCON0.5) configures UART0 such that when a stop bit is received, UART0 will generate an interrupt only if the ninth bit is logic 1 (RB80 = '1') and the received data byte matches the UART0 slave address. Following the received address interrupt, the slave will clear its SM20 bit to enable interrupts on the reception of the following data byte(s). Once the entire message is received, the addressed slave resets its SM20 bit to ignore all transmissions until it receives the next address byte. While SM20 is logic 1, UART0 ignores all bytes that do not match the UART0 address and include a ninth bit that is logic 1.

#### 21.4. Broadcast Addressing

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The broadcast address is the logical OR of registers SADDR0 and SADEN0, and '0's of the result are treated as "don't cares". Typically a broadcast address of 0xFF (hexadecimal) is acknowledged by all slaves, assuming "don't care" bits as '1's. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

| Example 4, SI     | _AVE #1    | Example 5, SL     | AVE #2     | Example 6, SLAVE #3 |            |  |

|-------------------|------------|-------------------|------------|---------------------|------------|--|

| SADDR0            | = 00110101 | SADDR0            | = 00110101 | SADDR0              | = 00110101 |  |

| SADEN0            | = 00001111 | SADEN0            | = 11110011 | SADEN0              | = 11000000 |  |

| Broadcast Address | = 00111111 | Broadcast Address | = 11110111 | Broadcast Address   | = 11110101 |  |

|                   |            |                   |            | denth conce         |            |  |

Where all ZEROES in the Broadcast address are don't cares.

Note in the above examples 4, 5, and 6, each slave would recognize as "valid" an address of 0xFF as a broadcast address. Also note that examples 4, 5, and 6 uses the same SADDR0 and SADEN0 register values as shown in the examples 1, 2, and 3 respectively (slaves #1, 2, and 3). Thus, a master could address each slave device individually using a masked address, and also broadcast to all three slave devices. For example, if a Master were to send an address of "11110101", only slave #1 would recognize the address as valid. If a master were to then send an address of "1111111", all three slave devices would recognize the address as a valid broadcast address.

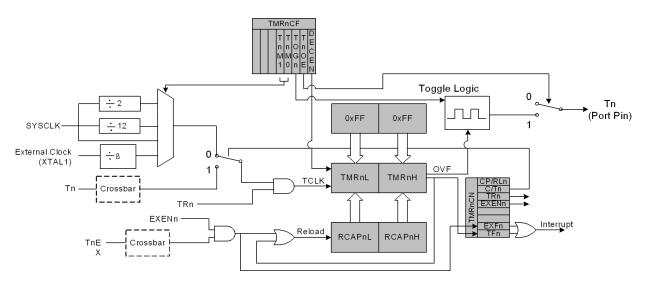

#### 23.2.3. Auto-Reload Mode

In Auto-Reload Mode, the counter/timer can be configured to count up or down and cause an interrupt/flag to occur upon an overflow/underflow event. When counting up, the counter/timer will set its overflow/underflow flag (TFn) and cause an interrupt (if enabled) upon overflow/underflow, the values in the Reload/Capture Registers (RCAPnH and RCAPnL) are loaded into the timer, and the timer is restarted. When the Timer External Enable Bit (EXENn) bit is set to '1' and the Decrement Enable Bit (DCEN) is '0', a '1'-to-'0' transition on the TnEX pin (configured as an input in the digital crossbar) will cause a timer reload (in addition to timer overflows causing auto-reloads). When DCEN is set to '1', the state of the TnEX pin controls whether the counter/timer counts *up* (increments) or *down* (decrements), and will not cause an auto-reload or interrupt event. See Section 23.2.1 for information concerning configuration of a timer to count down.

When counting down, the counter/timer will set its overflow/underflow flag (TFn) and cause an interrupt (if enabled) when the value in the timer (TMRnH and TMRnL registers) matches the 16-bit value in the Reload/Capture Registers (RCAPnH and RCAPnL). This is considered an underflow event, and will cause the timer to load the value 0xFFFF. The timer is automatically restarted when an underflow occurs.

Counter/Timer with Auto-Reload mode is selected by clearing the CP/RLn bit. Setting TRn to logic 1 enables and starts the timer.

In Auto-Reload Mode, the External Flag (EXFn) toggles upon every overflow or underflow and does not cause an interrupt. The EXFn flag can be thought of as the most significant bit (MSB) of a 17-bit counter.

Figure 23.5. Tn Auto-reload Mode and Toggle Mode Block Diagram

# C8051F040/1/2/3/4/5/6/7

## SFR Definition 23.9. TMRnCF: Timer n Configuration

|         | _                                                                                                                                   |                                                                                                 | R/W<br>TnM1   | R/W<br>TnM0   | R/W<br>TOGn  | R/W<br>TnOE  | R/W<br>DCEN | Reset Value |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------|---------------|--------------|--------------|-------------|-------------|--|--|--|--|

| Bit7    | Bit6                                                                                                                                | Bit5                                                                                            | Bit4          | Bit3          | Bit2         | Bit1         | Bit0        | Bit         |  |  |  |  |

|         |                                                                                                                                     |                                                                                                 |               |               | DILL         | Ditt         | Dito        | Addressable |  |  |  |  |

|         | ess: TMR2CF:0xC<br>age TMR2CF: pag                                                                                                  | -                                                                                               |               |               |              |              |             |             |  |  |  |  |

| Bit7-5: | Reserved.                                                                                                                           |                                                                                                 |               |               |              |              |             |             |  |  |  |  |

| Bit4-3: | TnM1 and Tr                                                                                                                         | M0: Timer                                                                                       | Clock Mode    | e Select Bit  | S.           |              |             |             |  |  |  |  |

|         | Bits used to s                                                                                                                      | select the T                                                                                    | imer clock s  | source. The   | sources ca   | an be the Sy | stem Cloc   | k           |  |  |  |  |

|         | (SYSCLK), S                                                                                                                         | YSCLK div                                                                                       | ided by 2 o   | r 12, or an o | external clo | ck signal ro | uted to Tn  | (port pin)  |  |  |  |  |

|         | divided by 8.                                                                                                                       |                                                                                                 | rce is select | ed as follov  | /S:          |              |             |             |  |  |  |  |

|         | 00: SYSCLK                                                                                                                          |                                                                                                 |               |               |              |              |             |             |  |  |  |  |

|         | 01: SYSCLK                                                                                                                          |                                                                                                 | (10)          |               |              |              |             |             |  |  |  |  |

|         | 10: EXTERN                                                                                                                          |                                                                                                 | 8/8           |               |              |              |             |             |  |  |  |  |

| Bit2:   | 11: SYSCLK                                                                                                                          |                                                                                                 | ato hit       |               |              |              |             |             |  |  |  |  |

| DILZ.   | TOGn: Toggle output state bit.<br>When timer is used to toggle a port pin, this bit can be used to read the state of the output, or |                                                                                                 |               |               |              |              |             |             |  |  |  |  |

|         | can be writte                                                                                                                       |                                                                                                 |               |               |              |              |             | c output, o |  |  |  |  |

| Bit1:   |                                                                                                                                     |                                                                                                 |               |               | lo output.   |              |             |             |  |  |  |  |

|         | TnOE: Timer output enable bit.<br>This bit enables the timer to output a 50% duty cycle output to the timer's assigned external     |                                                                                                 |               |               |              |              |             |             |  |  |  |  |

|         | port pin.                                                                                                                           |                                                                                                 | •             | ,             | , ,          |              | Ũ           |             |  |  |  |  |

|         | NOTE: A time                                                                                                                        | er is config                                                                                    | ured for Squ  | uare Wave     | Output as fo | ollows:      |             |             |  |  |  |  |

|         | CP/RLn = 0                                                                                                                          |                                                                                                 |               |               |              |              |             |             |  |  |  |  |

|         | C/Tn = 0                                                                                                                            |                                                                                                 |               |               |              |              |             |             |  |  |  |  |

|         | TnOE = 1                                                                                                                            |                                                                                                 |               |               |              |              |             |             |  |  |  |  |

|         | Load RCAPnH:RCAPnL (See Section "Equation 23.1. Square Wave Frequency" on                                                           |                                                                                                 |               |               |              |              |             |             |  |  |  |  |

|         | page 300).<br>Configure Po                                                                                                          | rt Din for o                                                                                    | utnut (Soo    | Section #15   | 7 Port Innu  | ut/Output"   | 00 0000 2   | 02)         |  |  |  |  |

|         | 0: Output of t                                                                                                                      |                                                                                                 |               |               |              |              | on page z   | 03).        |  |  |  |  |

|         |                                                                                                                                     |                                                                                                 |               |               | •            | • •          |             |             |  |  |  |  |

| Bit0:   | •                                                                                                                                   | 1: Output of toggle mode available at Timers' assigned port pin.<br>DCEN: Decrement Enable Bit. |               |               |              |              |             |             |  |  |  |  |

|         | This bit enab                                                                                                                       | les the time                                                                                    | er to count u | up or down    | as determin  | ed by the s  | tate of TnE | EX.         |  |  |  |  |

|         | 0: Timer will (                                                                                                                     | count up, re                                                                                    | egardless of  | f the state c | f TnEX.      | •            |             |             |  |  |  |  |

|         | 1: Timer will o                                                                                                                     |                                                                                                 |               | •             | e state of T | nEX as foll  | ows:        |             |  |  |  |  |

|         |                                                                                                                                     |                                                                                                 | timer count   |               |              |              |             |             |  |  |  |  |

|         | if Tnl                                                                                                                              | _X = 1, the                                                                                     | timer count   | ts UP.        |              |              |             |             |  |  |  |  |

|         |                                                                                                                                     |                                                                                                 |               |               |              |              |             |             |  |  |  |  |

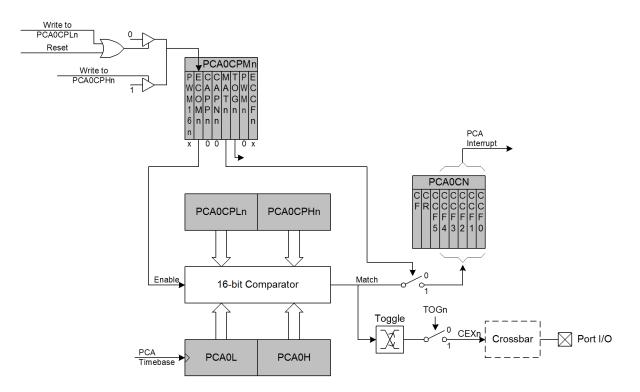

#### 24.2.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode.

**Important Note About Capture/Compare Registers:** When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 24.6. PCA High-Speed Output Mode Diagram